1.本发明涉及一种半导体器件及其制备方法,具体涉及一种sic mosfet器件及其制备方法,属于半导体功率器件制备技术领域。

背景技术:

2.sic mosfet作为一种重要的开关型功率器件,兼备了硅mosfet的高频开关特性及硅igbt的高电压阻断和低导通损耗能力,且易于驱动控制,是sic功率器件领域内研究的重点。

3.sic mosfet器件技术不断推陈出新,据报导目前阻断电压超过10kv,单芯片通流能力超过200a。在器件结构上已经发展出了平面栅、沟槽栅等传统硅功率器件的关键技术;其中,平面栅技术的大部分结构都处于同一平面上,元胞尺寸受限,且导电沟道处于表面,沟道迁移率受限于现有工艺,沟道电阻降低的幅度有限;沟槽栅技术则需要单独对沟槽栅底部进行合适的电场屏蔽,以确保栅氧不会暴露在过强的电场下,难以兼顾强场屏蔽和低阻电流通路。

技术实现要素:

4.本发明提供了一种半导体器件及其制备方法,解决了背景技术中披露的问题。

5.为了解决上述技术问题,本发明所采用的技术方案是:一种半导体器件,包括sic单晶衬底,sic单晶衬底的背面设置有漏极金属电极,sic单晶衬底正面外延有第一掺杂外延层,第一掺杂外延层的顶面外延有第二掺杂外延层,第二掺杂外延层的顶面两侧均注入有第二掺杂类型杂质,形成第二重掺杂基区,第二重掺杂基区延伸至第一掺杂外延层内,第二重掺杂基区的顶面和第二掺杂外延层的顶面构成注入面,注入面的部分区域注入有第一掺杂类型杂质,形成第一重掺杂源区,第一重掺杂源区的顶面和第二重掺杂基区的顶面构成刻蚀面,刻蚀面上刻蚀有沟槽,沟槽的两侧延伸至第二重掺杂基区内,沟槽的中部延伸至第一掺杂外延层内,沟槽的内壁上氧化有栅氧介质,沟槽内从上往下依次设置有栅极金属电极、栅-源隔离介质和多晶硅栅,刻蚀面上设置有源极金属电极。

6.sic单晶衬底正面和第一掺杂外延层之间设置有第一掺杂缓冲层。

7.第一掺杂为n掺杂,第二掺杂为p掺杂。

8.第一掺杂为p掺杂,第二掺杂为n掺杂。

9.所有沟槽相互平行,沟槽横穿刻蚀面,沟槽与所述半导体器件的纵向线垂直或有一定夹角。

10.多晶硅栅覆盖整个沟槽槽底和槽壁、或者部分覆盖沟槽槽底和槽壁。

11.一种半导体器件的制备方法,包括:准备sic单晶衬底,在sic单晶衬底正面外延形成第一掺杂外延层;在第一掺杂外延层上,外延形成第二掺杂外延层;

在第二掺杂外延层上形成掩蔽层,图形化去除掩蔽层两侧部分,离子注入第二掺杂类型杂质,形成第二重掺杂基区,去除剩余掩蔽层;在第二重掺杂基区的顶面和第二掺杂外延层的顶面形成掩蔽层,图形化去除部分区域的掩蔽层,离子注入第一掺杂类型杂质,形成第一重掺杂源区,去除剩余掩蔽层;退火,以激活注入的掺杂杂质;在第一重掺杂源区的顶面和第二重掺杂基区的顶面形成掩蔽层,并刻蚀形成沟槽;牺牲氧化,在沟槽的内壁形成栅氧介质;淀积掺杂多晶硅填充沟槽,图形化形成多晶硅栅;淀积栅-源隔离介质,并图形化形成接触孔;淀积金属,退火形成源极接触,图形化形成栅极金属电极和源极金属电极;制作sic单晶衬底背面漏电极,并退火形成漏极金属电极;制作正面钝化保护介质,并图形化形成栅极金属电极和源极金属电极接触窗口。

12.本发明所达到的有益效果:1、本发明刻蚀的沟槽结构使得导电沟道位于沟槽的侧壁之上,元胞尺寸取决于sic刻蚀精细程度,不受沟道长度、栅-源隔离和jfet区宽度的限制,可实现元胞尺寸减小、沟道密度提高、导通电阻下降的有益效果,并且本发明的基区位于沟槽之下,具有屏蔽强电场,保护栅氧介质的有益效果,且不增加源区到漏区的导通电阻;2、本发明的沟槽方向可以与基区成一定的偏角,使得位于沟槽侧壁的导电沟道可以在特定偏角的晶向上,以取得更高的沟道迁移率,而不牺牲电压阻断能力。

附图说明

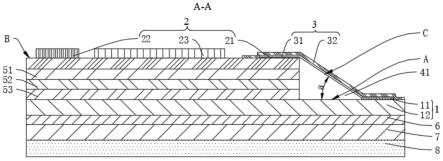

13.图1为本发明第一实例的俯视图;图2为本发明第一实例的内部结构图;图3为本发明第二实例的俯视图。

具体实施方式

14.下面结合附图对本发明作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本发明的保护范围。

15.如图1和2所示,一种半导体器件,包括sic单晶衬底、漏极金属电极8、第一掺杂外延层1、第二掺杂外延层2、第二重掺杂基区4、第一重掺杂源区3、沟槽5、栅氧介质、栅极金属电极、栅-源隔离介质、多晶硅栅6和源极金属电极7。

16.sic单晶衬底的背面设置漏极金属电极8,sic单晶衬底的正面具有一定厚度的第一掺杂缓冲层,在第一掺杂缓冲层上外延,形成第一掺杂外延层1。

17.第一掺杂可以为n掺杂,那么相应的第二掺杂为p掺杂,当然第一掺杂也可以为p掺杂,那么相应的第二掺杂就为n掺杂,这里的实施例中以第一掺杂为n掺杂,第二掺杂为p掺杂为例,即上述第一掺杂缓冲层为n掺杂缓冲层,即n掺杂外延层(4h-sic层),n掺杂外延层的厚度在2~200μm之间,掺杂浓度在1

×

10

15

cm-3

~1

×

10

17

cm-3

之间,n掺杂外延层的掺杂浓度小于n掺杂缓冲层的掺杂浓度。

18.在第一掺杂外延层1的顶面外延形成第二掺杂外延层2,即低掺杂浓度的p掺杂外

延层(4h-sic层),外延厚度在0.1~2μm之间,掺杂浓度在1

×

10

16

cm-3

~1

×

10

18

cm-3

之间。可选的,在此之前在第一掺杂外延层1的顶面外延一层高掺杂浓度外延层,即n型掺杂的4h-sic层,掺杂浓度大于第一掺杂外延层1。

19.第二掺杂外延层2的顶面两侧均离子注入第二掺杂类型杂质,形成第二重掺杂基区4,即p 基区,p 基区延伸至第一掺杂外延层1内,第一掺杂外延层1内两侧的p 基区之间为jfet区。

20.定义第二重掺杂基区4的顶面和第二掺杂外延层2的顶面构成注入面,注入面的部分区域注入第一掺杂类型杂质,形成第一重掺杂源区3,即n 源区,n 源区整体呈n形。

21.定义第一重掺杂源区3的顶面和第二重掺杂基区4的顶面构成刻蚀面,刻蚀面上刻蚀若干沟槽5,所有沟槽5相互平行,沟槽5的两侧延伸至第二重掺杂基区4内,沟槽5的中部延伸至第一掺杂外延层1内,沟槽5横穿刻蚀面,沟槽5与所述半导体器件的纵向线垂直(见图1)或有一定夹角(见图3),存在偏角的结构,使得位于沟槽5侧壁的导电沟道(图2中箭头)可以在特定偏角的晶向上,以取得更高的沟道迁移率,而不牺牲电压阻断能力。

22.沟槽5的槽壁上制作有栅氧介质,沟槽5内从上往下依次设置有栅极金属电极、栅-源隔离介质和多晶硅栅6,多晶硅栅6覆盖整个沟槽5槽底和槽壁、或者部分覆盖沟槽5槽底和槽壁,刻蚀面上设置源极金属电极7。

23.上述器件的导电沟道位于沟槽5的侧壁之上,元胞尺寸取决于sic刻蚀精细程度,不受沟道长度、栅-源隔离和jfet区宽度的限制,可实现元胞尺寸减小、沟道密度提高、导通电阻下降的有益效果,并且上述器件的基区位于沟槽5之下,具有屏蔽强电场,保护栅氧介质的有益效果,且不增加源区到漏区的导通电阻。

24.进一步,本发明还公开了上述器件的制备方法,包括以下步骤:步骤1,准备sic单晶片,包括sic单晶衬底,sic单晶衬底的正面具有一定厚度的n掺杂缓冲层,在n掺杂缓冲层上外延形成具有一定厚度、更低掺杂浓度的n掺杂外延层。

25.步骤2,在n掺杂外延层上外延一层更高掺杂浓度外延层,然后再外延形成p掺杂外延层。

26.步骤3,在p掺杂外延层上形成掩蔽层,图形化去除掩蔽层两侧部分,离子注入p型掺杂杂质,形成p 基区,去除剩余掩蔽层;其中,掩蔽层可通过化学气相沉积或其他合适的方式制作,注入的温度可以在300℃~600℃,注入的掺杂杂质可以是铝、硼或其他合适的p型掺杂杂质。

27.步骤4,在p 基区的顶面和p掺杂外延层的顶面形成掩蔽层,图形化去除部分区域的掩蔽层,离子注入n型掺杂杂质,形成n 源区,去除剩余掩蔽层。

28.步骤5,退火,以激活注入的掺杂杂质;例如,通过在单晶片表面覆盖一层保护性碳膜,将sic单晶片置于惰性保护气体中,在1500~2000℃温度下退火1~60min,随后去除保护性碳膜。

29.步骤6,n 源区的顶面和p 基区的顶面形成掩蔽层,并刻蚀形成沟槽5。

30.步骤7,牺牲氧化,在沟槽5的内壁上制作栅氧介质。

31.首先对刻蚀后的沟槽5进行牺牲氧化,例如,通过在1100℃~1500℃温度下氧化sic晶片,随后去除氧化层,随后通过在1100℃~1500℃温度下氧化sic晶片形成栅氧介质,栅氧介质的厚度可以是10nm~100nm,栅氧介质的形成也可以是其他方法。

32.步骤8,淀积掺杂多晶硅填充沟槽5,图形化形成多晶硅栅6。

33.在氧化后的sic单晶片上通过合适的方法形成多晶硅层,例如化学气相沉积,并通过合适的方法图形化形成多晶硅栅6。可选的,图形化后对多晶硅进行氧化处理。

34.步骤9,淀积栅-源隔离介质,并图形化形成接触孔。

35.通过合适的方法在上表面形成隔离介质并图形化;隔离介质可以是氧化硅或其他合适的材料。

36.步骤10,淀积金属,退火形成源极接触,图形化形成栅极金属电极和源极金属电极7。

37.步骤11,制作sic单晶衬底背面背面漏电极,并退火形成漏极金属电极8,例如在900℃~1100℃温度惰性气体保护下退火1~10min。

38.可以在形成漏电极之前对sic单晶衬底进行减薄,并结合合适的方法形成欧姆接触,例如激光退火,可选的在退火完成后对金属电极进行加厚。

39.步骤12,制作正面钝化保护介质,并图形化形成栅极金属电极和源极金属电极7接触窗口;其中,钝化保护介质可以是氮化硅、氧化硅或其他合适的材料中的一种或多种复合。

40.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。