技术特征:

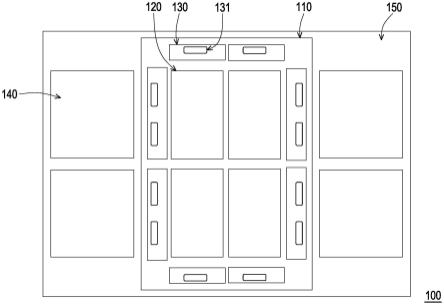

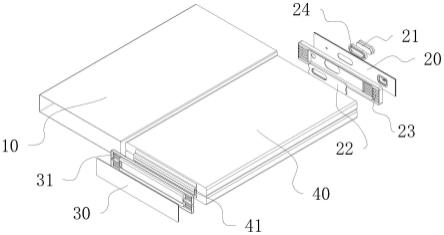

1.一种芯片组,其特征在于,包括:第一线路层;多个第一裸晶,包括多个第一键合组件;多个输入输出裸晶,包括多个第二键合组件;以及顶部逻辑裸晶,包括多个第三键合组件,其中所述多个第一裸晶以及所述多个输入输出裸晶分别通过所述多个第一键合组件以及所述多个第二键合组件以接垫对接垫的方式直接接合所述顶部逻辑裸晶的所述多个第三键合组件,并且所述多个第一裸晶以及所述多个输入输出裸晶分别通过多个第一凸块封装在所述第一线路层上。2.根据权利要求1所述的芯片组,其特征在于,所述多个第一裸晶、所述多个输入输出裸晶以及所述顶部逻辑裸晶分别是以不同的工艺节点的制程所制造的。3.根据权利要求1所述的芯片组,其特征在于,所述多个第一裸晶以及所述多个输入输出裸晶分别的工艺节点的最小线宽大于或等于顶部逻辑裸晶的工艺节点的最小线宽。4.根据权利要求1所述的芯片组,其特征在于,所述多个第一裸晶分别包括逻辑芯片及/或存储芯片,所述接垫对接垫的方式为混合键合。5.根据权利要求1所述的芯片组,其特征在于,还包括:多个第二裸晶,分别包括高带宽存储芯片,其中所述多个第二裸晶通过多个第二凸块封装在所述第一线路层上,并且所述多个第一裸晶以及所述多个输入输出裸晶分别通过所述多个第一凸块、所述第一线路层以及所述多个第二凸块与所述多个第二裸晶电性连接。6.根据权利要求5所述的芯片组,其特征在于,还包括:第二线路层,其中所述第一线路层为中介板,并且所述第一线路层通过多个第三凸块封装在所述第二线路层上。7.根据权利要求6所述的芯片组,其特征在于,所述多个第一凸块以及所述多个第二凸块分别为微凸块,并且所述多个第三凸块分别为焊球或锡球凸块。8.根据权利要求5所述的芯片组,其特征在于,所述多个第一凸块以及所述多个第二凸块分别为焊球或锡球凸块,并且所述多个第一裸晶、所述多个第二裸晶以及所述多个输入输出裸晶分别以覆晶封装的方式封装在所述第一线路层上。9.根据权利要求8所述的芯片组,其特征在于,还包括:重分布层,设于所述多个第一裸晶、所述多个输入输出裸晶以及所述多个第二裸晶上靠近所述第一线路层的一侧,其中所述多个第一裸晶、所述多个输入输出裸晶以及所述多个第二裸晶分别通过所述重分布层连接所述多个第一凸块以及所述多个第二凸块。10.根据权利要求1所述的芯片组,其特征在于,所述多个第一裸晶以及所述多个输入输出裸晶包括多个第一微型输入输出电路分别对应于所述多个第一键合组件的一部分以及所述多个第二键合组件的一部分,并且所述顶部逻辑裸晶包括多个第二微型输入输出电路分别对应于所述多个第三键合组件的一部分。11.根据权利要求10所述的芯片组,其特征在于,所述多个第一微型输入输出电路通过所述多个第一键合组件的所述一部分、所述多个第二键合组件的所述一部分以及所述多个第三键合组件的所述一部分与所述多个第二微型输入输出电路进行通信,并且所述多个第

一键合组件的另一部分、所述多个第二键合组件的另一部分以及所述多个第三键合组件的另一部分分别用于传输电源信号。12.根据权利要求1所述的芯片组,其特征在于,所述多个第一裸晶包括多个第一有源电路设置在靠近于所述顶部逻辑裸晶的一侧,并且所述多个输入输出裸晶包括多个第二有源电路设置在靠近于所述顶部逻辑裸晶的所述一侧,所述顶部逻辑裸晶包括多个第三有源电路设置在靠近于所述多个第一裸晶以及所述多个输入输出裸晶的一侧。13.根据权利要求12所述的芯片组,其特征在于,所述多个第一裸晶包括多个第一硅通孔连接所述多个第一有源电路,并且所述多个输入输出裸晶包括多个第二硅通孔连接所述多个第二有源电路,并且所述多个第一硅通孔以及所述多个第二硅通孔还分别连接所述多个第一凸块。14.一种芯片组的制造方法,包括:形成多个第一裸晶、多个输入输出裸晶以及顶部逻辑裸晶;将所述多个第一裸晶的多个第一键合组件以及所述多个输入输出裸晶的多个第二键合组件以接垫对接垫的方式直接接合于所述顶部逻辑裸晶的多个第三键合组件;以及通过多个第一凸块将所述多个第一裸晶以及所述多个输入输出裸晶封装在第一线路层上。15.根据权利要求14所述的芯片组,其特征在于,所述多个第一裸晶、所述多个输入输出裸晶以及所述顶部逻辑裸晶分别是以不同的工艺节点的制程所制造的。16.根据权利要求14所述的芯片组,其特征在于,所述多个第一裸晶以及所述多个输入输出裸晶分别的工艺节点的最小线宽大于或等于顶部逻辑裸晶的工艺节点的最小线宽。17.根据权利要求14所述的制造方法,其特征在于,所述多个第一裸晶分别包括逻辑芯片及/或存储芯片,所述接垫对接垫的方式为混合键合。18.根据权利要求14所述的制造方法,其特征在于,还包括:形成多个第二裸晶,其中所述多个第二裸晶分别包括高带宽存储芯片;以及通过多个第二凸块将所述多个第二裸晶封装在所述第一线路层上,其中所述多个第一裸晶以及所述多个输入输出裸晶分别通过所述多个第一凸块、所述第一线路层以及所述多个第二凸块与所述多个第二裸晶电性连接。19.根据权利要求18所述的制造方法,其特征在于,还包括:形成第二线路层;以及通过多个第三凸块将所述第一线路层封装在所述第二线路层上,其中所述第一线路层为中介板,其中所述多个第一凸块以及所述多个第二凸块分别为微凸块,并且所述多个第三凸块分别为焊球或锡球凸块。20.根据权利要求18所述的制造方法,其特征在于,还包括:在所述多个第一裸晶、所述多个输入输出裸晶以及所述多个第二裸晶上靠近所述第一线路层的一侧形成重分布层,其中所述多个第一裸晶、所述多个输入输出裸晶以及所述多个第二裸晶分别通过所述重分布层连接所述多个第一凸块以及所述多个第二凸块,其中所述多个第一凸块以及所述多个第二凸块分别为焊球或锡球凸块,并且所述多个第一裸晶、所述多个第二裸晶以及所述多个输入输出裸晶分别以覆晶封装的方式封装在所

述第一线路层上。

技术总结

本发明提供一种芯片组及其制造方法。所述芯片组包括第一线路层、多个第一裸晶、多个输入输出裸晶以及顶部逻辑裸晶。多个第一裸晶包括多个第一键合组件。多个输入输出裸晶包括多个第二键合组件。顶部逻辑裸晶包括多个第三键合组件。多个第一裸晶以及多个输入输出裸晶分别通过多个第一键合组件以及多个第二键合组件以接垫对接垫的方式直接接合顶部逻辑裸晶的多个第三键合组件,并且多个第一裸晶以及多个输入输出裸晶分别通过多个第一凸块封装在第一线路层上。因此,本发明的芯片组可实现具有较高运算能力以及较高制造良率的特点。有较高运算能力以及较高制造良率的特点。有较高运算能力以及较高制造良率的特点。

技术研发人员:ꢀ(74)专利代理机构

受保护的技术使用者:上海壁仞智能科技有限公司

技术研发日:2022.03.24

技术公布日:2022/7/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。