1.本发明涉及一种半导体装置,尤其是指一种芯片组及其制造方法。

背景技术:

2.对于传统的芯片组而言,传统的芯片组中所设置的逻辑芯片以及输入输出芯片之间通常需要设置连接接口电路,例如裸片对裸片(die to die,d2d)接口电路、高带宽存储器(high bandwidth memory,hbm)实体接口电路,因此随着目前芯片设计朝向高频宽及高密度芯片的趋势发展,传统的芯片组的芯片面积(或芯片体积)也往往会因设置这些连接接口电路的数量增加的影响,而使得传统的芯片组的芯片面积过大且具有高功耗的问题。

技术实现要素:

3.根据本发明的实施例,本发明的芯片组包括第一线路层、多个第一裸晶、多个输入输出裸晶以及顶部逻辑裸晶。多个第一裸晶包括多个第一键合组件。多个输入输出裸晶包括多个第二键合组件。顶部逻辑裸晶包括多个第三键合组件。多个第一裸晶以及多个输入输出裸晶分别通过多个第一键合组件以及多个第二键合组件以接垫对接垫的方式直接接合顶部逻辑裸晶的多个第三键合组件。多个第一裸晶以及多个输入输出裸晶分别通过多个第一凸块封装在第一线路层上。

4.根据本发明的实施例,本发明的芯片组的制造方法包括以下步骤:形成多个第一裸晶、多个输入输出裸晶以及顶部逻辑裸晶;将多个第一裸晶的多个第一键合组件以及多个输入输出裸晶的多个第二键合组件以接垫对接垫的方式直接接合于顶部逻辑裸晶的多个第三键合组件;以及通过多个第一凸块将多个第一裸晶以及多个输入输出裸晶封装在第一线路层上。

5.基于上述,本发明的芯片组及其制造方法,可有效地增加裸晶及芯片密度。

6.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

7.图1是本发明的一实施例的芯片组的结构俯视图;

8.图2是本发明的一实施例的芯片组的结构侧视图;

9.图3是本发明的一实施例的芯片组的结构透视图;

10.图4是本发明的一实施例的芯片组的封装后的结构侧视图;

11.图5是本发明的另一实施例的芯片组的封装后的结构侧视图;

12.图6是本发明的一实施例的芯片组的制造方法的流程图;

13.图7是本发明的一实施例的输入输出裸晶的结构侧视图;

14.图8a以及图8b分别是本发明的一实施例的第一裸晶在制造过程中的结构变化侧视图;

15.图9是本发明的一实施例的顶部逻辑裸晶的结构侧视图;

16.图10a至图10c分别是本发明的一实施例的芯片组在制造过程中的结构变化侧视图;

17.图11是本发明的一实施例的线路层的结构侧视图;

18.图12a至图12d分别是本发明的另一实施例的芯片组在制造过程中的结构变化侧视图;

19.图13是本发明的另一实施例的重分布层的结构侧视图;

20.图14a至图14d分别是本发明的又一实施例的芯片组在制造过程中的结构变化侧视图。

具体实施方式

21.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在图式和描述中用来表示相同或相似部分。

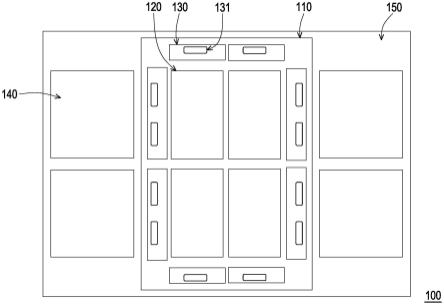

22.图1是本发明的一实施例的芯片组的结构俯视图。参考图1,芯片组100包括顶部逻辑裸晶(top logic die)110、多个第一裸晶120、多个输入输出裸晶(input/output die,i/o die)130、多个第二裸晶140以及线路层150。在本实施例中,第一裸晶120以及输入输出裸晶130设置在顶部逻辑裸晶110上,并且多个输入输出裸晶130可沿着顶部逻辑裸晶110的边缘设置,以环绕多个第一裸晶120。顶部逻辑裸晶110以及第二裸晶140设置在线路层150上,并且多个第二裸晶140可设置在顶部逻辑裸晶110的两侧或至少一侧。

23.在本实施例中,多个输入输出裸晶130分别包括多个输入输出电路(端口)131,并且输入输出裸晶130可通过输入输出电路131以及线路层150上的线路与第二裸晶140电性连接,以进行通信。

24.在本实施例中,第一裸晶120为一种小芯片(chiplet),并且第一裸晶120可包括逻辑芯片(logic chip)及/或存储芯片(memory chip),其中存储芯片可为静态随机存取存储器(static random-access memory,sram)芯片。第二裸晶140可包括高带宽存储(high bandwidth memory,hbm)芯片。

25.在本实施例中,顶部逻辑裸晶110、第一裸晶120以及输入输出裸晶130分别是以不同的工艺节点的制程所制造的。在一实施例中,第一裸晶120以及输入输出裸晶130分别的工艺节点的最小线宽大于或等于顶部逻辑裸晶110的工艺节点的最小线宽。在另一实施例中,顶部逻辑裸晶110的工艺节点的最小线宽可例如是小于或等于5纳米(nm)。第一裸晶120的工艺节点的最小线宽可例如是介于5纳米至7纳米之间。输入输出裸晶130的工艺节点的最小线宽可例如是大于或等于5纳米。

26.在本实施例中,由于第一裸晶120以及输入输出裸晶130是透过顶部逻辑裸晶110中的线路进行电性连接,因此可有效节省第一裸晶120以及输入输出裸晶130之间的裸晶对裸晶的输入输出电路与线路的配置,以增加第一裸晶120的数量(即增加逻辑密度)。如此一来,本实施例的芯片组100可实现具有较高运算能力以及较高制造良率(因为可节省裸晶对裸晶的电路与线路制造)的特点。

27.图2是本发明的一实施例的芯片组的结构侧视图。参考图2,顶部逻辑裸晶110包括有源电路(active circuit)111以及键合组件112。有源电路111设置在靠近于第一裸晶120

以及输入输出裸晶130的一侧。第一裸晶120包括有源电路121、键合组件122、硅通孔(through silicon via,tsv)123以及凸块(bump)124。有源电路121设置在靠近于顶部逻辑裸晶110的一侧。输入输出裸晶130包括有源电路131、键合组件132、硅通孔133以及凸块134。有源电路131设置在靠近于顶部逻辑裸晶110的一侧。在本实施例中,有源电路111、121、131可例如分别包括由多个晶体管以及线路所组成的电路。凸块124、134可为微凸块(μbump,micro bump)、焊球(ball)或锡球凸块(solder ball)。

28.在本实施例中,第一裸晶120以及输入输出裸晶130分别通过键合组件122、132以接垫对接垫(pad to pad)的方式直接接合顶部逻辑裸晶110的键合组件112,并且第一裸晶120以及输入输出裸晶130分别通过凸块124、134封装在如图1所示的线路层150上。在本实施例中,键合组件112、122、132的每一个可包括键合接垫、支柱(pillar)以及金属接垫,其中键合接垫用于与另一个键合组件的键合接垫连接(直接接触),支柱用于连接键合接垫以及金属接垫,并且金属接垫用于与内部电路连接。两个键合组件之间的键合接垫可以是以混合键合(hybrid bonding)的方式接合。

29.在本实施例中,第一裸晶120以及输入输出裸晶130的有源电路121、131可通过硅通孔123、133以及凸块124、134与线路层150电性连接。硅通孔123连接有源电路121。硅通孔133连接有源电路131。硅通孔123、133分别连接凸块124、134。并且,第一裸晶120以及输入输出裸晶130的有源电路121、131可通过键合组件112、122、132实现电性连接以及通信功能。因此,本实施例的组件可有效节省第一裸晶120以及输入输出裸晶130之间的裸晶对裸晶的输入输出电路与线路的配置。

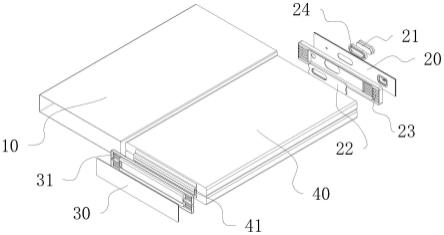

30.图3是本发明的一实施例的芯片组的结构透视图。参考图3,本实施例以一个第一裸晶320以及一个输入输出裸晶330来说明设置在顶部逻辑裸晶310上的方式。在本实施例中,顶部逻辑裸晶310在邻近第一裸晶320以及输入输出裸晶330的一侧表面可设置有多个微型输入输出(tiny i/o)电路312以及网格(mesh)线路或片上网路(network on chip,noc)的金属走线315,其中金属走线315连接微型输入输出电路312。顶部逻辑裸晶310包括微型输入输出电路322,并且第一裸晶320的微型输入输出电路322通过第一裸晶320的键合组件以及顶部逻辑裸晶310的对应的键合组件,与顶部逻辑裸晶310的对应的微型输入输出电路312电性连接。输入输出裸晶330包括微型输入输出电路332,并且输入输出裸晶330的微型输入输出电路332通过输入输出裸晶330的键合组件以及顶部逻辑裸晶310的对应的键合组件,与顶部逻辑裸晶310的另对应的微型输入输出电路312电性连接。在本实施例中,输入输出裸晶330的另一侧还可包括输入输出电路335,并且输入输出电路335用于通过凸块与线路层上的线路电性连接。

31.图4是本发明的一实施例的芯片组的封装后的结构侧视图。参考图4,芯片组400包括顶部逻辑裸晶410、第一裸晶420、输入输出裸晶430以及第二裸晶440、线路层450、460。在本实施例中,第一裸晶420以及输入输出裸晶430可通过多个键合组件以接垫对接垫的方式设置在顶部逻辑裸晶410上。第一裸晶420、输入输出裸晶430以及第二裸晶440可通过多个凸块401封装在线路层460的一侧。凸块401可分别为微凸块。线路层460可为中介板(interposer)。第一裸晶420、输入输出裸晶430以及第二裸晶440通过凸块401以及线路层460进行电性连接以及通信。线路层460的另一侧可通过多个凸块402封装在线路层450的一侧。线路层450可例如是芯片基板、封装基板或电路基板,并且线路层450的另一侧可设置多

个凸块403。凸块402、403可分别为焊球或锡球凸块。例如,多个凸块402可由可控坍塌芯片连接(controlled collapse chip connection,c4)的制程技术所形成,多个凸块403可由球栅阵列封装(ball grid array,bga)的制程技术所形成,但本发明并不以此为限。芯片组400可通过凸块403进一步封装至其他电路基板上。

32.图5是本发明的另一实施例的芯片组的封装后的结构侧视图。参考图5,芯片组500包括顶部逻辑裸晶510、第一裸晶520、输入输出裸晶530以及第二裸晶540、线路层550、重分布层(rdl,redistribution layer)560。在本实施例中,第一裸晶520以及输入输出裸晶530可通过多个键合组件以接垫对接垫的方式设置在顶部逻辑裸晶510上。第一裸晶520、输入输出裸晶530以及第二裸晶540可封装在线路层550的一侧。对此,第一裸晶520、输入输出裸晶530以及第二裸晶540分别以覆晶封装(flip chip)的方式封装在线路层550上。重分布层560可以设于第一裸晶520、输入输出裸晶530以及第二裸晶540上靠近线路层550的一侧。第一裸晶520、输入输出裸晶530以及第二裸晶540可通过重分布层560的多个金属走线501与重分布层560的靠近线路层550一侧的多个凸块502电性连接,并通过线路层550与多个凸块503电性连接。重分布层560可通过多个凸块502封装在线路层550的一侧。线路层550可例如是芯片基板、封装基板或电路基板,并且线路层550的另一侧可设置多个凸块503。凸块502、503可分别为焊球或锡球凸块。例如,多个凸块502可由可控坍塌芯片连接(controlled collapse chip connection,c4)的制程技术所形成,多个凸块503可由球栅阵列封装(ball grid array,bga)的制程技术所形成,但本发明并不以此为限。芯片组500可通过凸块503进一步封装至其他电路基板上。此外,重分布层560可以通过金属走线以及微凸块(图未示)与第一裸晶520、输入输出裸晶530以及第二裸晶540封装结合并实现电性连接。

33.图6是本发明的一实施例的芯片组的制造方法的流程图。参考图1、图2以及图6,芯片组100可利用相对应的各式制造设备,并依照以下步骤s610~s630来制造之。在步骤s610,形成多个第一裸晶120、多个输入输出裸晶130以及顶部逻辑裸晶110。在步骤s620,将多个第一裸晶120的多个第一键合组件(键合组件122)以及多个输入输出裸晶130的多个第二键合组件(键合组件132)以接垫对接垫的方式直接接合于顶部逻辑裸晶110的多个第三键合组件(键合组件112)。在步骤s630,通过多个第一凸块(凸块124、134)将多个第一裸晶120以及多个输入输出裸晶130封装在第一线路层(线路层150)上。因此,本实施例的制造方法可有效节省裸晶对裸晶的电路与线路制造,而可实现较高制造良率。并且,以下将由几个实施例的结构说明来进一步描述各步骤的实施方式。

34.图7是本发明的一实施例的输入输出裸晶的结构侧视图。对应于上述步骤s610,如图7所示,可形成输入输出裸晶730。输入输出裸晶730包括装置层730a以及基板层730b。详细而言,输入输出裸晶730的基板层730b上可先分别形成金属走线、硅通孔733、驱动电路735以及相关输入输出电路,并形成氧化物钝化层覆盖金属走线、硅通孔733、驱动电路735以及相关逻辑电路,以形成装置层730a。接着,可形成多个键合组件732在装置层730a的远离基板层730b的一侧的表面上,并且再次形成氧化物钝化层在多个键合组件732的周围,其中多个键合组件732的键合面分别与装置层730a的表面同高且裸露。

35.图8a以及图8b分别是本发明的一实施例的第一裸晶在制造过程中的结构变化侧视图。对应于上述步骤s610,如图8a所示,可形成第一裸晶820。第一裸晶820包括装置层820a以及基板层820b。详细而言,第一裸晶820的基板层820b上可先分别形成金属走线、硅

通孔823、驱动电路825以及相关输入输出电路,并形成氧化物钝化层覆盖金属走线、硅通孔823、驱动电路825以及相关逻辑电路,以形成装置层830a。如图8b所示,可形成多个键合组件822在装置层820a的远离基板层820b的一侧的表面上,并且再次形成氧化物钝化层在多个键合组件822的周围,其中多个键合组件822的键合面分别与装置层820a的表面同高且裸露。

36.图9是本发明的一实施例的顶部逻辑裸晶的结构侧视图。对应于上述步骤s610,如图9所示,可形成顶部逻辑裸晶910。顶部逻辑裸晶910包括装置层910a以及基板层910b。详细而言,顶部逻辑裸晶910的基板层910b上可先分别形成金属走线、驱动电路915以及相关输入输出电路,并形成氧化物钝化层覆盖金属走线、驱动电路915以及相关逻辑电路,以形成装置层910a。接着,可形成多个键合组件912在装置层910a的远离基板层910b的一侧的表面上,并且再次形成氧化物钝化层在多个键合组件912的周围,其中多个键合组件912的键合面分别与装置层910a的表面同高且裸露。

37.图10a至图10c分别是本发明的一实施例的芯片组在制造过程中的结构变化侧视图。对应于上述步骤s620,如图10a所示,将上述图7、8a、8b、9实施例中所形成的多个输入输出裸晶730、多个第一裸晶820以及顶部逻辑裸晶910结合。详细而言,将多个第一裸晶820的多个键合组件822以及多个输入输出裸晶730的多个键合组件732以接垫对接垫的方式直接接合于顶部逻辑裸晶910的多个键合组件912。并且,多个输入输出裸晶730以及多个第一裸晶820之间的间隙可填充钝化保护层(passivation),其中钝化保护层可为有机材料或氧化物。如图10b所示,可打磨输入输出裸晶730以及第一裸晶820的基板层730b、820b,以使输入输出裸晶730以及第一裸晶820的多个硅通孔733、823可裸露。如图10c所示,可形成多个金属走线1001以及多个(微)凸块1002,以分别连接输入输出裸晶730以及第一裸晶820所裸露的多个硅通孔733、823上,并完成芯片组1000的制造。

38.图11是本发明的一实施例的线路层的结构侧视图。对应于上述步骤s630,在一实施例中,如图11所示,可形成线路层1100。线路层1100为中介板,并且包括基板层1100a以及装置层1100b。详细而言,线路层1100的基板层1100a上可先形成多个硅通孔1103贯通基板层1100a,并且形成多个深沟槽电容(deep trench capacitor,dtc)1105在基板层1100a的邻近于装置层1100b的一侧。接着,可形成金属走线1101,以连接多个深沟槽电容1105以及多个硅通孔1103,并且形成氧化物钝化层覆盖金属走线1101、多个深沟槽电容1105以及多个硅通孔1103,以形成装置层1100b。接着,可形成金属走线1102以及(微)凸块1104裸露出装置层1100b的远离基板层1100a的一侧的表面,并完成线路层1100的制造。

39.图12a至图12d分别是本发明的另一实施例的芯片组在制造过程中的结构变化侧视图。对应于上述步骤s630,在一实施例中,如图12a所示,将上述图10c、11实施例中所形成的芯片组1000以及线路层1100结合。详细而言,通过多个凸块1002和/或多个凸块1104将芯片组1000(包括顶部逻辑裸晶、多个第一裸晶以及多个输入输出裸晶)封装在线路层1100上,并且于芯片组1000周围的至少一侧,通过多个(微)凸块1213将芯片1210封装在线路层1100上。芯片1210包括裸晶1211以及形成在裸晶1211一侧的金属走线1212,其中芯片1210可为高带宽存储芯片(hbm,high bandwidth memory)。芯片1210通过金属走线1212以及凸块1213来电性连接至线路层1100,以使芯片组1000可通过线路层1100与芯片1210进行通信。

40.接着,如图12b所示,将底部填充(underfill)材料1201填充至芯片组1000与线路层1100之间的间隙以及芯片1210与线路层1100之间的间隙,并且将封胶(molding)材料1202填充至芯片组1000与芯片1210之间。接着,如图12c所示,形成临时载板1203于芯片组1000与芯片1210分别远离线路层1100的一侧,以固定芯片组1000、芯片1210以及线路层1100。接着,如图12d所示,形成金属走线1204以及多个凸块1205,以连接线路层1100的基板层1100a中的多个硅通孔1103,并且移除临时载板1203及进行切割,以完成芯片组1200的封装程序。此外,芯片组1200还可进一步通过多个凸块1205来封装至如上述图4所示的线路层450。线路层450可例如是芯片基板、封装基板或电路基板,并且线路层450的另一侧可设置多个凸块(即图4所示的多个凸块403),以进一步封装至其他电路基板上。例如,多个凸块1205(即图4所示的多个凸块402)可由可控坍塌芯片连接(controlled collapse chip connection,c4)的制程技术所形成,线路层450另一侧的多个凸块(即图4所示的多个凸块403)可由球栅阵列封装(ball grid array,bga)的制程技术所形成,但本发明并不以此为限。

41.图13是本发明的另一实施例的重分布层的结构侧视图。对应于上述步骤s630,在另一实施例中,如图13所示,可形成重分布层1300a。详细而言,可首先形成临时载板1300b,然后可通过扇出型(fanout)封装技术形成重分布层1300a于临时载板1300b上方。对此,可形成氧化物钝化层覆盖金属走线1301,以形成重分布层1300a,其中至少一部分的金属走线1301裸露出重分布层1300a的表面,并完成重分布层1300a的制造。例如,金属走线1301裸露出重分布层1300a的表面的部分可以为微凸块。

42.图14a至图14d分别是本发明的又一实施例的芯片组在制造过程中的结构变化侧视图。对应于上述步骤s630,在另一实施例中,如图14a所示,将上述图10c、13实施例中所形成的芯片组1000以及由重分布层1300a和临时载板1300b组成的组合体1300结合。详细而言,通过多个凸块1002将芯片组1000(包括顶部逻辑裸晶、多个第一裸晶以及多个输入输出裸晶)封装在组合体1300上,并且于芯片组1000周围的至少一侧,通过多个(微)凸块1213将芯片1210封装在组合体1300上。芯片1210包括裸晶1211以及形成在裸晶1211一侧的金属走线1212,其中芯片1210可为高带宽存储芯片。芯片1210通过金属走线1212以及凸块1213来电性连接至重分布层1300a,以使芯片组1000可通过重分布层1300a与芯片1210进行通信。

43.接着,如图14b所示,将底部填充材料1401填充至芯片组1000与组合体1300之间的间隙以及芯片1210与组合体1300之间的间隙,并且将封胶材料1402填充至芯片组1000与芯片1210之间。接着,如图14c所示,形成临时载板1403于芯片组1000与芯片1210分别远离重分布层1300a的一侧,以固定芯片组1000、芯片1210以及组合体1300。并且,移除组合体1300的临时载板1300b,以保留重分布层1300a。接着,如图14d所示,形成金属走线1404以及多个凸块1405,以连接重分布层1300a,并且完成芯片组1400的封装程序。此外,芯片组1400还可通过多个凸块1405来封装至如上述图5所示的线路层550。线路层550可例如是芯片基板、封装基板或电路基板,并且线路层550的另一侧可设置多个凸块(即图5所示的多个凸块503),以进一步封装至其他电路基板上。例如,芯片组1400可以覆晶封装的方式封装在线路层550上,多个凸块1405(即图5所示的多个凸块502)可由可控坍塌芯片连接(controlled collapse chip connection,c4)的制程技术所形成,线路层550另一侧的多个凸块(即图5所示的多个凸块503)可由球栅阵列封装(ball grid array,bga)的制程技术所形成,但本

发明并不以此为限。

44.综上所述,本发明的芯片组及其制造方法,可通过将多个第一裸晶(分别包括逻辑芯片及/或存储芯片)以及多个输入输出芯片的一侧以接垫对接垫的方式直接接合至顶部逻辑裸晶,以节省裸晶对裸晶的电路配置。并且,本发明的芯片组的多个第一裸晶以及多个输入输出芯片的另一侧还可通过线路层来电性连接至芯片组的多个第二裸晶(分别包括高带宽存储芯片),以进一步节省裸晶对裸晶的电路配置。因此,本发明的芯片组及其制造方法同时运用了2.5d封装技术以及3d封装技术来实现高逻辑密度的结构特性,并且可实现具有较高运算能力以及较高制造良率的特点。

45.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。