1.本发明涉及一种电子装置及具有其电子装置的透明显示器。

背景技术:

2.近来,人们对于透明显示器的需求日益增加,且为了能够享有更佳的显示品质,对于提升开口率的需求也随之提高。然而,传统的走线设计需要较多的走线数量及较大的走线面积,从而限制透明显示器的开口率。

3.因此,提供一种具有高开口率及良好显示品质的透明显示器,为相关业者努力的课题之一。

技术实现要素:

4.本发明实施例是关于一种电子装置及具有其电子装置的透明显示器,可有效抑制绕射效应或干涉效应,降低走线数量,减少走线面积,进一步提升开口率。

5.根据本发明的一方面,提出一种电子装置。所述电子装置包括透明基板、多个像素结构及第一走线结构。此透明基板包括透明区与走线区。此些像素结构的各者至少具有第一颜色的子像素结构与第二颜色的子像素结构,此第一颜色的子像素结构具有第一颜色的发光元件,此第二颜色的子像素结构具有第二颜色的发光元件。此第一走线结构包括第一主要走线、第一辅助走线与第二辅助走线,此第一主要走线配置于此走线区并环绕至少部分的此透明区,此第一辅助走线与此第二辅助走线是与此第一主要走线电连接,并分别与对应的此第一颜色的子像素结构与对应的此第二颜色的子像素结构电连接。

6.根据本发明的另一方面,提出一种透明显示器,包括电子装置。所述电子装置包括透明基板、多个像素结构及第一走线结构。透明基板包括透明区与走线区。多个像素结构的各者至少具有第一颜色的子像素结构与第二颜色的子像素结构。第一颜色的子像素结构具有第一颜色的发光元件,第二颜色的子像素结构具有第二颜色的发光元件。第一走线结构包括第一主要走线、第一辅助走线、与第二辅助走线。第一主要走线配置于走线区并环绕至少部分的透明区。第一辅助走线与第二辅助走线是与第一主要走线电连接,并分别与对应的第一颜色的子像素结构与对应的第二颜色的子像素结构电连接。

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下。

附图说明

8.图1为本发明的一实施例的电子装置的示意图;

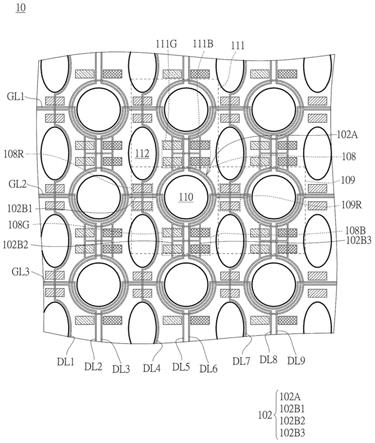

9.图2为图1的一像素结构的放大示意图;

10.图3为沿着图2的切线3-3’的剖面示意图;

11.图4为对应于上述实施例的各子像素结构所对应的电路的一例的示意图;

12.图5为另一种电子装置的示意图;

13.图6为本发明的另一实施例的电子装置的示意图;

14.图7为本发明的再另一实施例的电子装置的示意图;

15.图8为本发明的更另一实施例的电子装置的示意图;

16.图9为本发明的再另一实施例的电子装置的示意图;

17.图10为本发明的更另一实施例的电子装置的示意图;

18.图11为本发明的再另一实施例的电子装置的示意图;

19.图12为本发明的更另一实施例的电子装置的示意图。

20.符号说明

21.10,50,60,70,80,90,100,1100,1200:电子装置

22.102,502a,602,802,902,1002,1102,1202:第一走线结构

23.222,502b,804,1204:第二走线结构

24.232,502c,1206:第三走线结构

25.502d:第四走线结构

26.102a,222a,232a,602a,802a,804a,902a,1002a,1102a,1202a,1204a,1206a:第一主要走线

27.1202b,1204b,1206b:第二主要走线

28.1202c,1206c:第三主要走线

29.1202d:第四主要走线

30.102b1,222b1,232b1,602b1,802b1,804b,902b1,1002b1,1102b1:第一辅助走线

31.102b2,222b2,232b2,602b2,802b2,902b2,1002b2,1102b2:第二辅助走线

32.102b3,222b3,232b3,602b3,802b3,902b3,1002b3,1102b3:第三辅助走线

33.1002b4,1102b4:第四辅助走线

34.1002b5,1102b5:第五辅助走线

35.1002b6,1102b6:第六辅助走线

36.108,109,111,608,609,611,708,808,809,1007~1009,1107~1109,1212,1214,1216,1218:像素结构

37.108r,109r,608r,609r,708r,808r,809r,1007r,1008r,1009r,1107r,1108r,1109r,1212r,1216r:第一颜色的子像素结构

38.108g,111g,608g,611g,808g,1007g,1008g,1009g,1107g,1108g,1109g,1212g,1216g:第二颜色的子像素结构

39.108b,111b,608b,611b,708b,808b,1008b,1108b,1212b,1214b,1216b,1218b:第三颜色的子像素结构

40.110,112,510,512,610,612,710,712,810,910,1010,1110,1207,1208,1210:透明区

41.312:透明基板

42.314:多晶硅层

43.316a,316b,316c:导电层

44.318:第一金属层

45.320a:第一接触电极

46.320b:第二接触电极

47.322:发光元件

48.3-3’:切线

49.40:电路

50.c:储存电容

51.d:发光二极管

52.dl,dl1~dl9:数据线

53.g:栅极

54.gl,gl1~gl3:栅极线

55.gi:绝缘层

56.ild1:第一层间介电层

57.ild2:第二层间介电层

58.opv:有机保护层

59.pv:保护层

60.t1,t2,tft:晶体管

具体实施方式

61.在下文的详细描述中,为了便于解释,提供各种的特定细节以整体理解本发明的实施例。然而,应理解的是,一或多个实施例能够在不采用这些特定细节的情况下实现。在其他情况下,为了简化附图,已知的结构及元件以示意图表示。

62.另外,说明书与权利要求中所使用的序数例如「第一」、「第二」、「第三」等的用词,以修饰权利要求的元件,其本身并不意含及代表此元件有任何之前的序数,也不代表某一元件与另一元件的顺序、或是制造方法上的顺序,此些序数的使用仅用来使具有某命名的一元件得以和另一具有相同命名的元件能作出清楚区分。

63.图1绘示依照本发明的一实施例的电子装置10的示意图。请参照图1,电子装置10可包括一透明基板(未绘示)、至少一像素结构(例如是像素结构108)及一第一走线结构102。

64.一实施例中,像素结构108可具有一第一颜色的子像素结构108r、一第二颜色的子像素结构108g及/或一第三颜色的子像素结构108b。第一颜色的子像素结构108r具有一第一颜色的发光元件,第二颜色的子像素结构108g具有一第二颜色的发光元件,第三颜色的子像素结构108b具有一第三颜色的发光元件。本实施例中,前述的第一颜色、第二颜色及第三颜色可例如是红色、绿色及蓝色,但本发明不限于此。举例而言,第一颜色的发光元件、第二颜色的发光元件及第三颜色的发光元件可以各自是发光二极管(led)、迷你发光二极管(mini led)、有机发光二极管(organic light-emitting diode,oled)或微型发光二极管(micro led)等。请参照图1,第一颜色的子像素结构108r、第二颜色的子像素结构108g及第三颜色的子像素结构108b可各自具有二个发光元件。在一实施例中,各子像素结构使用二个发光元件中的一个发光元件进行发光。当此发光元件无法正常运作时,另一发光元件可以取代此发光元件。在另一实施例中,各子像素结构也可只具有一个发光元件。

65.一实施例中,第一颜色的子像素结构108r、第二颜色的子像素结构108g及第三颜

色的子像素结构108b的尺寸可以是相同或不同。第一颜色的子像素结构108r、第二颜色的子像素结构108g及第三颜色的子像素结构108b的形状可以是相同或不同。

66.一实施例中,透明基板包括多个透明区(例如是多个透明区110及多个透明区112)与走线区。此处所述的走线区是指电子装置10中多个透明区以外而可配置走线的区域,例如包括两个透明区110之间的区域、两个透明区112之间的区域及透明区110与透明区112之间的区域。此走线区之内可包括其他半透明或非透明元件,例如电容、走线或薄膜晶体管等。本实施例中,透明区110为圆形区域,透明区112为椭圆形区域,但本发明不限于此。透明区110、112也可都是圆形区域或椭圆形区域。或者,透明区110可为圆形区域或椭圆形区域的其中一者,透明区112可为圆形区域或椭圆形区域的另一者。另一实施例中,透明区110或透明区112可以是近似圆形的多边形区域。

67.一实施例中,第一走线结构102可包括一第一主要走线102a、一第一辅助走线102b1、一第二辅助走线102b2及/或一第三辅助走线102b3。第一主要走线102a配置于走线区并环绕至少部分的透明区110。图1以第一主要走线102a环绕整个透明区110为例做说明。第一主要走线102a对应于透明区110的形状延伸而为圆形或椭圆形。第一辅助走线102b1、第二辅助走线102b2及第三辅助走线102b3电连接于第一主要走线102a。第一辅助走线102b1、第二辅助走线102b2及第三辅助走线102b3分别电连接于第一颜色的子像素结构108r、第二颜色的子像素结构108g及第三颜色的子像素结构108b。

68.一实施例中,第一主要走线102a具有一环状结构,第一辅助走线102b1、第二辅助走线102b2及第三辅助走线102b3可具有一线段结构。第一辅助走线102b1与第二辅助走线102b2位于第一主要走线102a的环状结构的不同侧,且第一辅助走线102b1与第三辅助走线102b3位于第一主要走线102a的环状结构的不同侧。例如第一辅助走线102b1位于第一主要走线102a的环状结构的左侧,第二辅助走线102b2与第三辅助走线102b3可位于第一主要走线102a的环状结构的下侧。第一走线结构102的材料可包括导电金属,例如是铜,但本发明不以此为限。

69.在一实施例中,第二辅助走线102b2实质上平行于第三辅助走线102b3,且第二辅助走线102b2可选择性地通过另一走线线段电连接于第三辅助走线102b3。

70.一实施例中,第一主要走线102a可提供电压或信号予至少2个子像素结构。本实施例中,第一主要走线102a可提供电压或信号至6个子像素结构,但本发明不以此为限。举例而言,位于像素结构108之中的第一主要走线102a可提供电压或信号至6个子像素结构,此6个子像素结构例如包括像素结构108的第一颜色的子像素结构108r、像素结构108的第二颜色的子像素结构108g、像素结构108的第三颜色的子像素结构108b、像素结构109的第一颜色的子像素结构109r、像素结构111的第二颜色的子像素结构111g、像素结构111的第三颜色的子像素结构111b。其中,像素结构109位于像素结构108的右侧,像素结构111位于像素结构108的上侧。

71.请参照图1,电子装置10可还包括一数据线走线结构及一栅极线走线结构。在一实施例中,数据线走线结构可包括数据线dl1~dl9,栅极线走线结构可包括栅极线gl1~gl3。数据线走线结构配置于走线区且环绕至少部分的透明区110、112,而栅极线走线结构配置于走线区且环绕至少部分的透明区110。数据线走线结构沿着一第一方向延伸(例如是垂直方向),栅极线走线结构沿着一第二方向延伸(例如是水平方向),第一方向与第二方向可实

质上相互垂直。数据线走线结构具有至少一半环状结构与至少一线段结构,且数据线走线结构的半环状结构沿着透明区110及112的边界延伸。栅极线走线结构具有至少一半环状结构与至少一线段结构,且栅极线走线结构的半环状结构沿着透明区110的边界延伸。

72.为了简洁且清楚说明的目的,图1仅绘示一层走线结构。实际应用中,电子装置10可包括二层以上的走线结构。

73.图2绘示图1的一像素结构108的放大示意图。图2以电子装置10包括了三层的走线结构为例做说明。请参照图2,电子装置10除了包括第一走线结构102之外,电子装置10可还包括第二走线结构222及第三走线结构232。第二走线结构222包括一第一主要走线222a、一第一辅助走线222b1、一第二辅助走线222b2及/或一第三辅助走线222b3。第一主要走线222a配置于走线区并环绕至少部分的透明区110。第一主要走线222a对应于透明区110的形状延伸而为圆形或椭圆形。第一辅助走线222b1、第二辅助走线222b2及第三辅助走线222b3电连接于第一主要走线222a。第一辅助走线222b1、第二辅助走线222b2及第三辅助走线222b3分别电连接于第一颜色的子像素结构108r、第二颜色的子像素结构108g及第三颜色的子像素结构108b。

74.第三走线结构232包括一第一主要走线232a、一第一辅助走线232b1、一第二辅助走线232b2及/或一第三辅助走线232b3。第一主要走线232a配置于走线区并环绕至少部分的透明区110。第一主要走线232a对应于透明区110的形状延伸而为圆形或椭圆形。第一辅助走线232b1、第二辅助走线232b2及第三辅助走线232b3电连接于第一主要走线232a。第一辅助走线232b1、第二辅助走线232b2及第三辅助走线232b3分别电连接于第一颜色的子像素结构108r、第二颜色的子像素结构108g及第三颜色的子像素结构108b。

75.第一走线结构102的第一主要走线102a、第二走线结构222的第一主要走线222a及第三走线结构232的第一主要走线232a的投影彼此不重叠。另一实施例中,第一走线结构102的第一主要走线102a、第二走线结构222的第一主要走线222a及第三走线结构232的第一主要走线232a的至少任二者的投影彼此部分重叠。又一实施例中,第一走线结构102的第一主要走线102a、第二走线结构222的第一主要走线222a及第三走线结构232的第一主要走线232a的投影彼此重叠。

76.第一走线结构102、第二走线结构222及第三走线结构232可以各自是高电位电源线走线结构、低电位电源线走线结构及补偿设定走线结构的其中一者。其中,高电位电源线走线结构用以传送高电位电压(vdd)、低电位电源线走线结构用以传送低电位电压(vss),而补偿设定走线结构则是用以传送补偿设定电压(vint)。补偿设定电压(vint)例如是用以调整像素结构中的晶体管的临界电压(threshold voltage,vth)。本实施例中,第一走线结构102可例如是高电位电源线走线结构,第二走线结构222可例如是低电位电源线走线结构,第三走线结构232可例如是补偿设定走线结构,但本发明不以此为限。

77.请参照图3,其绘示沿着图2的切线3-3’的剖面示意图。为了清楚说明的目的,图3仅绘示一个发光元件。电子装置10’可还包括透明基板312、绝缘层gi、第一层间介电层ild1、第二层间介电层ild2及保护层(可包括保护层pv及有机保护层opv)。

78.绝缘层gi可覆盖于透明基板312上,第一层间介电层ild1可覆盖于绝缘层gi上,第二层间介电层ild2可覆盖于第一层间介电层ild1上,保护层pv可覆盖于第二层间介电层ild2上,有机保护层opv可覆盖于保护层pv上。前述元件的叠置关系也可变更,图3的实施例

仅为例示说明,本发明不以此为限。

79.第一走线结构102可例如是由保护层pv所覆盖,第二走线结构222可例如是由第二层间介电层ild2所覆盖,第三走线结构232可例如是由第一层间介电层ild1所覆盖。

80.请参照图3,电子装置10可还包括多晶硅层314、导电层316a、导电层316b、导电层316c、第一金属层318、第一接触电极320a、第二接触电极320b及晶体管tft。

81.多晶硅层314由绝缘层gi所覆盖,栅极g由第一层间介电层ild1所覆盖,第一金属层318由第二层间介电层ild2所覆盖。

82.导电层316a延伸通过第二层间介电层ild2、第一层间介电层ild1及绝缘层gi,以电连接于多晶硅层314。导电层316b延伸通过第二层间介电层ild2、第一层间介电层ild1及绝缘层gi,以电连接于多晶硅层314。导电层316c延伸通过第二层间介电层ild2,以电连接于第一金属层318。导电层316a例如用以作为晶体管tft的漏极和源极二者之一,而导电层316b则例如用以作为晶体管tft的漏极和源极二者之另一。

83.一实施例中,第一接触电极320a设置于有机保护层opv之上,用以电连接至一发光元件322,发光元件322例如是有机发光二极管或微型发光二极管。晶体管tft电连接于第一走线结构102、第二走线结构222或第三走线结构232,且晶体管tft电连接于第一接触电极320a。

84.一实施例中,第一接触电极320a延伸通过有机保护层opv及保护层pv,以电连接于导电层316a。第二接触电极320b延伸通过有机保护层opv及保护层pv,以电连接于导电层316c。

85.一实施例中,第一金属层318与导电层316c之间例如可作为储存电容,第一接触电极320a可与发光二极管的阳极电连接,而第二接触电极320b可与发光二极管的阴极电连接。

86.图4绘示依照对应于上述实施例的各子像素结构所对应的电路40之一例。

87.一实施例中,本发明的一像素结构可对应于二个晶体管一个储存电容(2t1c)电路,但本发明不以此为限。另一些实施例中,一像素结构可对应于二个晶体管以上及至少一储存电容的电路,或其它合适数目的晶体管及储存电容的电路。

88.电路40中使用两个晶体管t1及t2来控制流经发光二极管d的电流。晶体管t1耦接于晶体管t2、储存电容c及发光二极管d。晶体管t2耦接于储存电容c、栅极线gl及数据线dl。由栅极线gl传送的电压将决定晶体管t2是否开启,而由数据线dl传送的电压将决定流经晶体管t1与发光二极管d的电流,而发光二极管d的发光强度则与流经发光二极管d的电流相关。在其他数目的晶体管及储存电容的电路中,更可接收补偿设定电压(vint),以对某个晶体管的临界电压进行补偿或调整,以进一步调整流经发光二极管d的电流,并改变发光二极管d的发光强度。

89.图5绘示另一种电子装置50的示意图。本实施例的电子装置50与第一实施例的电子装置10的主要差异在于,电子装置50可具有4个走线结构,包括第一走线结构502a、第二走线结构502b、第三走线结构502c及第四走线结构502d。第一走线结构502a、第二走线结构502b及第四走线结构502d配置于走线区并环绕至少部分的透明区510。第三走线结构502c配置于走线区并环绕至少部分的透明区512。第一走线结构502a用以提供同一行的子像素结构(例如为绿色子像素结构)所需的电压,第二走线结构502b用以提供同一行的子像素结

构(例如为蓝色子像素结构)所需的电压,第三走线结构502c用以提供同一行的子像素结构(例如为红色子像素结构)所需的电压,而第四走线结构502d则用以提供同一列的红色子像素结构、绿色子像素结构、或蓝色子像素结构所需的电压。

90.兹将具有图1所示的电子装置10的透明显示器,具有与图5所示的电子装置50的透明显示器相较,在图5所示的电子装置50中,一行的一种颜色的像素结构就需使用一个走线结构。而于图1所示的电子装置10中,通过使高电位电源线走线结构、低电位电源线走线结构或补偿设定走线结构采用图1所示的环状结构与线段结构(如图1所示,第一主要走线102a是圆形或椭圆形,第一辅助走线102b1与第二辅助走线102b2为线段结构,可以使1个走线结构的1个主要走线同时与多个不同颜色的子像素结构电连接)。如此,可以减少所需的走线结构的数量,进而提高开口率,例如可提高14%的开口率。

91.也就是说,将图1及图2所示的透明显示器与图5所示的透明显示器相较,图1及图2所示的透明显示器通过使走线结构同时具有环状结构的主要走线与线段结构的辅助走线,使得一个走线结构即可与多个子像素结构电连接,以提供多个子像素结构所需的电源电压或补偿设定电压。如此,可降低走线数量,减少走线面积,进一步提升开口率。由此可提高透明显示器的透明度,以增进透明显示器的品质。

92.图6绘示依照本发明的另一实施例的电子装置60的示意图。本实施例中与前述实施例相同或相似的元件是沿用同样或相似的元件标号,且相同或相似元件的相关说明请参考前述,在此不再赘述。

93.如图6所示,本实施例的电子装置60的第一走线结构602的第一主要走线602a为具有一开口的圆形或椭圆形。

94.请参照图6,电子装置60可包括一透明基板(未绘示)、至少一像素结构(例如是像素结构608)及一第一走线结构602。

95.透明基板包括透明区610、612与走线区。像素结构608可至少具有一第一颜色的子像素结构608r、一第二颜色的子像素结构608g及/或一第三颜色的子像素结构608b。第一走线结构602包括一第一主要走线602a、一第一辅助走线602b1、一第二辅助走线602b2及/或一第三辅助走线602b3。第一主要走线602a配置于走线区并环绕至少部分的透明区610。第一主要走线602a对应于透明区610的形状延伸。第一辅助走线602b1、第二辅助走线602b2及第三辅助走线602b3电连接于第一主要走线602a。第一辅助走线602b1、第二辅助走线602b2及第三辅助走线602b3分别电连接于第一颜色的子像素结构608r、第二颜色的子像素结构608g及第三颜色的子像素结构608b。

96.一实施例中,第一主要走线602a具有一部分环状结构,第一辅助走线602b1、第二辅助走线602b2及第三辅助走线602b3可具有一线段结构。第一辅助走线602b1与第二辅助走线602b2位于第一主要走线602a的部分环状结构的不同侧,且第一辅助走线602b1与第三辅助走线602b3位于第一主要走线602a的部分环状结构的不同侧。

97.一实施例中,第一主要走线602a可提供电压或信号予至少2个子像素结构。本实施例中,第一主要走线602a可提供电压或信号至6个子像素结构,但本发明不以此为限。举例而言,位于像素结构608之中的第一主要走线602a可提供电压或信号至6个子像素结构,此6个子像素结构例如包括像素结构608的第一颜色的子像素结构608r、像素结构608的第二颜色的子像素结构608g、像素结构608的第三颜色的子像素结构608b、像素结构609的第一颜

色的子像素结构609r、像素结构611的第二颜色的子像素结构611g、像素结构611的第三颜色的子像素结构611b。其中,像素结构609位于像素结构608的右侧,像素结构611位于像素结构608的上侧。

98.一实施例中,电子装置60可还包括一数据线走线结构及一栅极线走线结构。

99.请参照图6,电子装置60可还包括一数据线走线结构及一栅极线走线结构。在一实施例中,数据线走线结构可包括数据线dl1~dl9,栅极线走线结构可包括栅极线gl1~gl3。数据线走线结构配置于走线区且环绕至少部分的透明区610、612,而栅极线走线结构配置于走线区且环绕至少部分的透明区610。数据线走线结构沿着一第一方向延伸(例如是垂直方向),栅极线走线结构沿着一第二方向延伸(例如是水平方向),第一方向与第二方向可实质上相互垂直。数据线走线结构具有至少一半环状结构与至少一线段结构,且数据线走线结构的半环状结构沿着透明区610及612的边界延伸。栅极线走线结构具有至少一半环状结构与至少一线段结构,且栅极线走线结构的半环状结构沿着透明区610的边界延伸。

100.一实施例中,第一主要走线602a的开口位置可不被限定,以使电子装置60的信号能够正常传送为原则。为了清楚说明的目的,图6的电子装置60仅绘示一层走线结构,但电子装置60可具有多层走线结构。

101.相较于如图5所示的电子装置50,通过使高电位电源线走线结构、低电位电源线走线结构及补偿设定走线结构三者之一采用本实施例的部分环状结构(亦即,第一主要走线602a是具有开口的圆形或椭圆形),可以提高开口率6%。若使高电位电源线走线结构、低电位电源线走线结构及补偿设定走线结构三者之二采用本实施例的部分环状结构,可以提高开口率12.5%。若使高电位电源线走线结构、低电位电源线走线结构及补偿设定走线结构三者均采用本实施例的部分环状结构,可以提高开口率19.4%。

102.图7绘示依照本发明的再另一实施例的电子装置70的示意图。本实施例中与前述实施例相同或相似的元件是沿用同样或相似的元件标号,且相同或相似元件的相关说明请参考前述,在此不再赘述。

103.如图7所示,本实施例的电子装置70采用子像素渲染(sub-pixel rendering)技术,以使一像素结构708对应两个不同颜色的子像素与两条数据线(例如数据线dl3、dl4)。

104.本实施例的走线结构可采用前述实施例的第一走线结构的布局设计。其余关于第一走线结构的相关说明,请参照前述实施例,在此不再赘述。

105.一实施例中,像素结构708至少具有一第一颜色的子像素结构708r及一第三颜色的子像素结构708b。其余关于第一颜色的子像素结构708r及第三颜色的子像素结构708b的相关说明,请参照前述实施例,在此不再赘述。

106.请参照图7,电子装置70可还包括一数据线走线结构及一栅极线走线结构(未绘示)。

107.一实施例中,数据线走线结构包括数据线dl1~dl6。像素结构708对应两条数据线dl3、dl4。数据线走线结构配置于走线区且环绕至少部分的透明区710、712。数据线走线结构具有至少一半环状结构与至少一线段结构,且数据线走线结构的半环状结构沿着透明区710及712的边界延伸。

108.相较于图5所示的电子装置50,通过使用本实施例的电子装置的布局设计,可以提高开口率3.1%。

109.图8绘示依照本发明的更另一实施例的电子装置80的示意图。本实施例中与前述实施例相同或相似的元件是沿用同样或相似的元件标号,且相同或相似元件的相关说明请参考前述,在此不再赘述。

110.如图8所示,本实施例的电子装置80的第一走线结构802的第一主要走线802a的形状为三角形。

111.请参照图8,电子装置80可包括一透明基板(未绘示)、至少一像素结构(例如是像素结构808)及一第一走线结构802。

112.一实施例中,像素结构808至少具有一第一颜色的子像素结构808r、一第二颜色的子像素结构808g及/或一第三颜色的子像素结构808b。其余关于第一颜色的子像素结构808r、第二颜色的子像素结构808g及第三颜色的子像素结构808b的相关说明,请参照图1所示的实施例,在此不再赘述。

113.一实施例中,透明基板包括透明区810与走线区。此处所述的走线区是指电子装置80中透明区810以外的区域。此走线区之内包括其他半透明或非透明元件,例如电容、走线或薄膜晶体管等。本实施例中,透明区810为三角形区域。

114.一实施例中,第一走线结构802包括一第一主要走线802a、一第一辅助走线802b1、一第二辅助走线802b2及一第三辅助走线802b3。第一主要走线802a配置于走线区并环绕至少部分的透明区810。第一主要走线802a对应于透明区810的形状延伸而为三角形。第一辅助走线802b1、第二辅助走线802b2及第三辅助走线802b3电连接于第一主要走线802a。第一辅助走线802b1电连接于第一颜色的子像素结构808r。第二辅助走线802b2电连接于第二颜色的子像素结构808g。第三辅助走线802b3电连接于第一颜色的子像素结构809r。本实施例中,前述的第一颜色、第二颜色例如是红色、绿色,但本发明不限于此。

115.一实施例中,第一主要走线802a具有一环状结构,第一辅助走线802b1、第二辅助走线802b2及第三辅助走线802b3可具有一线段结构。第一辅助走线802b1与第二辅助走线802b2位于第一主要走线802a的环状结构的不同侧,且第二辅助走线802b2与第三辅助走线802b3位于第一主要走线802a的环状结构的不同侧。第一辅助走线802b1与第二辅助走线802b2例如分别位于第一主要走线802a的环状结构的左侧与右侧,而第三辅助走线802b3例如位于第一主要走线802a的环状结构的左侧。

116.一实施例中,第一辅助走线802b1可实质上平行于第二辅助走线802b2及第三辅助走线802b3。

117.一实施例中,第一主要走线802a可提供电压或信号予至少2个子像素结构。本实施例中,第一主要走线802a可提供电压或信号至3个子像素结构,但本发明不以此为限。举例而言,位于像素结构808之中的第一主要走线802a可提供电压或信号至3个子像素结构,此3个子像素结构例如包括像素结构808的第一颜色的子像素结构808r、像素结构808的第二颜色的子像素结构808g及像素结构809的第一颜色的子像素结构809r。其中,像素结构808位于像素结构809的上侧。

118.请参照图8,电子装置80可还包括一第二走线结构804。

119.一实施例中,第二走线结构804包括一第一主要走线804a及/或一第一辅助走线804b。第一主要走线804a配置于走线区并环绕至少部分的透明区810。第一主要走线804a对应于透明区810的形状延伸而为三角形。第一辅助走线804b电连接于第一主要走线804a。第

一辅助走线804b电连接于像素结构808的第三颜色的子像素结构808b。本实施例中,前述的第三颜色例如是蓝色,但本发明不限于此。

120.一实施例中,第一主要走线804a具有一环状结构,第一辅助走线804b可具有一线段结构。第一辅助走线804b例如位于第一主要走线804a的环状结构的右侧。

121.电子装置80可还包括一数据线走线结构(未绘示)及一栅极线走线结构(未绘示)。

122.一实施例中,数据线走线结构及栅极线走线结构配置于走线区且环绕至少部分的透明区810。数据线走线结构沿着一第一方向延伸,栅极线走线结构沿着一第二方向延伸,第一方向与第二方向可实质上相互垂直。数据线走线结构及栅极线走线结构沿着透明区810的边界延伸。

123.为了简洁且清楚说明的目的,图8仅绘示一层走线结构。实际应用中,电子装置80可包括二层以上的走线结构。

124.图9绘示依照本发明的再另一实施例的电子装置90的示意图。本实施例中与前述实施例相同或相似的元件是沿用同样或相似的元件标号,且相同或相似元件的相关说明请参考前述,在此不再赘述。

125.如图9所示,本实施例的电子装置90的第一走线结构902的第一主要走线902a为具有一开口的三角形。

126.一实施例中,第一主要走线902a具有一部分环状结构,第一辅助走线902b1、第二辅助走线902b2及第三辅助走线902b3可具有一线段结构。第一辅助走线902b1与第二辅助走线902b2位于第一主要走线902a的部分环状结构的不同侧,且第二辅助走线902b2与第三辅助走线902b3位于第一主要走线902a的部分环状结构的不同侧。例如,第一辅助走线902b1与第二辅助走线902b2分别位于第一主要走线902a的部分环状结构的左侧与右侧,而第三辅助走线902b3则位于第一主要走线902a的部分环状结构的左侧。

127.一实施例中,第一主要走线902a的开口位置可不被限定,以使电子装置90的信号能够正常传送为原则。图9的实施例以开口位置位于三角形的右上方的侧边为例做说明。为了清楚说明的目的,图9的电子装置90仅绘示一层走线结构,但电子装置90也可具有多层走线结构。

128.图10绘示依照本发明的更另一实施例的电子装置100的示意图。本实施例中与前述实施例相同或相似的元件是沿用同样或相似的元件标号,且相同或相似元件的相关说明请参考前述,在此不再赘述。

129.如图10所示,本实施例的电子装置100的第一走线结构1002的第一主要走线1002a的形状为六边形。

130.请参照图10,电子装置100可包括一透明基板(未绘示)、至少一像素结构(例如是像素结构1008)及一第一走线结构1002。

131.一实施例中,像素结构1008至少具有一第一颜色的子像素结构1008r、一第二颜色的子像素结构1008g及/或一第三颜色的子像素结构1008b。其余关于第一颜色的子像素结构1008r、第二颜色的子像素结构1008g及第三颜色的子像素结构1008b的相关说明,请参照图1所示的实施例,在此不再赘述。

132.一实施例中,透明基板包括透明区1010与走线区。此处所述的走线区是指电子装置100中透明区1010以外的区域。此走线区之内包括其他半透明或非透明元件,例如电容、

走线或薄膜晶体管等。本实施例中,透明区1010为六边形区域。

133.一实施例中,第一走线结构1002包括一第一主要走线1002a、一第一辅助走线1002b1、一第二辅助走线1002b2、一第三辅助走线1002b3、一第四辅助走线1002b4、一第五辅助走线1002b5及一第六辅助走线1002b6。第一主要走线1002a配置于走线区并环绕至少部分的透明区1010。第一主要走线1002a对应于透明区1010的形状延伸而为六边形。第一辅助走线1002b1、第二辅助走线1002b2、第三辅助走线1002b3、第四辅助走线1002b4、第五辅助走线1002b5及第六辅助走线1002b6电连接于第一主要走线1002a。第一辅助走线1002b1电连接于像素结构1008的第一颜色的子像素结构1008r。第二辅助走线1002b2电连接于像素结构1008的第二颜色的子像素结构1008g。第三辅助走线1002b3电连接于像素结构1007的第一颜色的子像素结构1007r。第四辅助走线1002b4电连接于像素结构1007的第二颜色的子像素结构1007g。第五辅助走线1002b5电连接于像素结构1009的第一颜色的子像素结构1009r。第六辅助走线1002b6电连接于像素结构1009的第二颜色的子像素结构1009g。本实施例中,前述的第一颜色、第二颜色例如是红色、绿色,但本发明不限于此。

134.一实施例中,第一主要走线1002a具有一环状结构,第一辅助走线1002b1、第二辅助走线1002b2、第三辅助走线1002b3、第四辅助走线1002b4、第五辅助走线1002b5及第六辅助走线1002b6可具有一线段结构。第一辅助走线1002b1、第三辅助走线1002b3、第五辅助走线1002b5与第二辅助走线1002b2、第四辅助走线1002b4、第六辅助走线1002b6位于第一主要走线1002a的环状结构的不同侧,例如是左侧与右侧。

135.一实施例中,第一主要走线1002a可提供电压或信号予至少2个子像素结构。本实施例中,第一主要走线1002a可提供电压或信号至6个子像素结构,但本发明不以此为限。举例而言,位于像素结构1008之中的第一主要走线1002a可提供电压或信号至6个子像素结构,此6个子像素结构例如包括像素结构1007的第一颜色的子像素结构1007r、像素结构1007的第二颜色的子像素结构1007g、像素结构1008的第一颜色的子像素结构1008r、像素结构1008的第二颜色的子像素结构1008g、像素结构1009的第一颜色的子像素结构1009r及像素结构1009的第二颜色的子像素结构1009g。其中,像素结构1007位于像素结构1008的上侧,像素结构1009位于像素结构1008的下侧。

136.电子装置100可还包括一数据线走线结构(未绘示)及一栅极线走线结构(未绘示)。

137.一实施例中,数据线走线结构及栅极线走线结构配置于走线区且环绕至少部分的透明区1010。数据线走线结构沿着一第一方向延伸,栅极线走线结构沿着一第二方向延伸,第一方向与第二方向可实质上相互垂直。数据线走线结构及栅极线走线结构沿着透明区1010的边界延伸。另一实施例中,数据线走线结构及栅极线走线结构各自具有一半六边形结构与一线段结构,且沿着透明区1010的边界延伸。

138.为了简洁且清楚说明的目的,图10仅绘示一层走线结构。实际应用中,电子装置100可包括二层以上的走线结构。

139.图11绘示依照本发明的再另一实施例的电子装置1100的示意图。本实施例中与前述实施例相同或相似的元件是沿用同样或相似的元件标号,且相同或相似元件的相关说明请参考前述,在此不再赘述。

140.如图11所示,本实施例的电子装置1100的第一走线结构1102的第一主要走线

1102a为具有一开口的六边形。

141.一实施例中,第一主要走线1102a具有一部分环状结构,第一辅助走线1102b1、第二辅助走线1102b2、第三辅助走线1102b3、第四辅助走线1102b4、第五辅助走线1102b5及第六辅助走线1102b6可具有一线段结构。第一辅助走线1102b1、第三辅助走线1102b3、第五辅助走线1102b5与第二辅助走线1102b2、第四辅助走线1102b4、第六辅助走线1102b6位于第一主要走线1102a的部分环状结构的不同侧,例如是左侧与右侧。

142.一实施例中,第一主要走线1102a的开口位置可不被限定,以使电子装置1100的信号能够正常传送为原则,本实施例中以开口位于六边形的右上角为例做说明。为了清楚说明的目的,图11的电子装置1100仅绘示一层走线结构,但电子装置1100可具有多层走线结构。

143.图12绘示依照本发明的更另一实施例的电子装置1200的示意图。本实施例中与前述实施例相同或相似的元件是沿用同样或相似的元件标号,且相同或相似元件的相关说明请参考前述,在此不再赘述。

144.如图12所示,本实施例的电子装置1200的第一走线结构1202的形状为矩形。

145.请参照图12,电子装置1200可包括一透明基板(未绘示)、至少一像素结构(例如是像素结构1212、1214、1216或1218)及一第一走线结构1202。

146.一实施例中,第一走线结构1202可提供电压或信号予至少2个子像素结构。本实施例中,第一走线结构1202可提供电压或信号至4个子像素结构,但本发明不以此为限。举例而言,位于像素结构1212之中的第一走线结构1202可提供电压或信号至4个子像素结构,此4个子像素结构例如包括像素结构1212的第一颜色的子像素结构1212r、像素结构1214的第三颜色的子像素结构1214b、像素结构1216的第一颜色的子像素结构1216r、像素结构1218的第三颜色的子像素结构1218b。其中,像素结构1214位于像素结构1212的左侧,像素结构1216位于像素结构1212的上侧,像素结构1218位于像素结构1216的左侧。

147.一实施例中,透明基板包括透明区1207、1208、1210与走线区。像素结构1212可具有一第一颜色的子像素结构1212r、一第二颜色的子像素结构1212g及/或一第三颜色的子像素结构1212b。第一走线结构1202包括一第一主要走线1202a、一第二主要走线1202b、一第三主要走线1202c及/或一第四主要走线1202d。第一主要走线1202a、第二主要走线1202b、第三主要走线1202c及第四主要走线1202d配置于走线区并环绕至少部分的透明区1210。第一主要走线1202a电连接于像素结构1216的第一颜色的子像素结构1216r及像素结构1218的第三颜色的子像素结构1218b。第二主要走线1202b电连接于像素结构1214的第三颜色的子像素结构1214b及像素结构1218的第三颜色的子像素结构1218b。第三主要走线1202c电连接于像素结构1212的第一颜色的子像素结构1212r及像素结构1214的第三颜色的子像素结构1214b。第四主要走线1202d电连接于像素结构1212的第一颜色的子像素结构1212r及像素结构1216的第一颜色的子像素结构1216r。

148.电子装置1200可还包括一第二走线结构1204和/或一第三走线结构1206。其中,第二走线结构1204及第三走线结构1206为具有一开口的矩形。

149.一实施例中,第二走线结构1204包括一第一主要走线1204a及/或一第二主要走线1204b。第一主要走线1204a及第二主要走线1204b配置于走线区并环绕至少部分的透明区1208。第一主要走线1204a电连接于像素结构1216的第一颜色的子像素结构1216r及像素结

构1216的第二颜色的子像素结构1216g。第二主要走线1204b电连接于像素结构1212的第一颜色的子像素结构1212r及像素结构1212的第二颜色的子像素结构1212g。

150.一实施例中,第三走线结构1206包括一第一主要走线1206a、一第二主要走线1206b及/或一第三主要走线1206c。第一主要走线1206a、第二主要走线1206b及第三主要走线1206c配置于走线区并环绕至少部分的透明区1207。第一主要走线1206a电连接于像素结构1216的第二颜色的子像素结构1216g及像素结构1216的第三颜色的子像素结构1216b。第二主要走线1206b电连接于像素结构1212的第二颜色的子像素结构1212g及像素结构1212的第三颜色的子像素结构1212b。第三主要走线1206c电连接于像素结构1212的第三颜色的子像素结构1212b及像素结构1216的第三颜色的子像素结构1216b。

151.电子装置1200可还包括一数据线走线结构及一栅极线走线结构。

152.一实施例中,数据线走线结构可包括数据线dl1~dl9,栅极线走线结构可包括栅极线gl1~gl3。数据线走线结构沿着一第一方向延伸(例如是垂直方向),栅极线走线结构沿着一第二方向延伸(例如是水平方向),第一方向与第二方向可实质上相互垂直。数据线走线结构配置和栅极线走线结构配置于走线区。

153.一实施例中,第二走线结构1204的开口位置及第三走线结构1206的开口位置可不被限定,以使电子装置1200的信号能够正常传送为原则。为了清楚说明的目的,图12的电子装置1200仅绘示一层走线结构,但电子装置1200可具有多层走线结构。

154.根据上述实施例,本发明提供一种电子装置。所述电子装置包括一透明基板、多个像素结构及一第一走线结构。此透明基板包括一透明区与一走线区。此些像素结构的各者至少具有一第一颜色的子像素结构与一第二颜色的子像素结构,此第一颜色的子像素结构具有一第一颜色的发光元件,此第二颜色的子像素结构具有一第二颜色的发光元件。此第一走线结构包括一第一主要走线、一第一辅助走线与一第二辅助走线,此第一主要走线配置于此走线区并环绕至少部分的此透明区,此第一辅助走线与此第二辅助走线是与此第一主要走线电连接,并分别与对应的此第一颜色的子像素结构与对应的此第二颜色的子像素结构电连接。

155.根据上述实施例,本发明提供一种透明显示器。所述透明显示器包括根据上述的电子装置。举例而言,所述透明显示器可为微型发光二极管显示器或有机发光二极管显示器,但本发明不以此为限。

156.本发明实施例可有效抑制绕射效应或干涉效应,降低走线数量,减少走线面积,进一步提升开口率。

157.综上所述,虽然结合以上实施例公开了本发明,然而其并非用以限定本发明。本发明所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作各种的更动与润饰。因此,本发明的保护范围应当以附上的权利要求及其均等范围所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。