应用于射频放大的沟道掺杂调制rfldmos器件及制法

技术领域

1.本发明涉及一种rfldmos器件,特别涉及一种应用于射频放大的沟道掺杂调制rfldmos器件及制法,属于半导体技术领域。

背景技术:

2.rf ldmos是为射频功率放大器而设计的n型mosfet器件,具有横向沟道结构,漏极、源极和栅极都在芯片表面,源极一般由体内高杂质浓度通道与衬底底部相连接并接地,在沟道与漏极之间有一个低浓度的n型漂移区,ldmos采用双扩散技术,在同一光刻窗口相继进行硼磷两次扩散,由两次杂质扩散横向结深之差可精确地决定沟道长度。

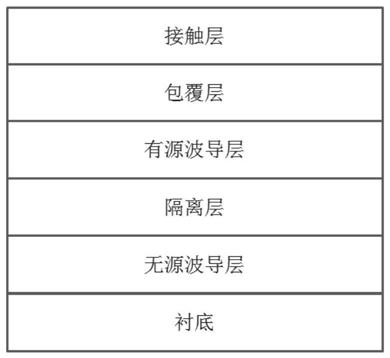

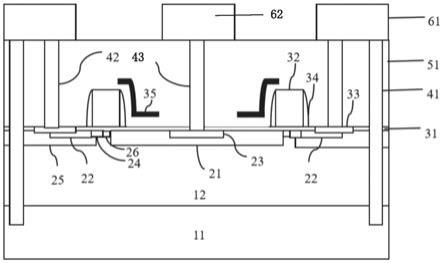

3.图1为发明人提供的一种rfldmos器件结构,其中,11为p型重掺杂衬底,12为p型外延层,21为n型漂移区,22为n型重掺杂源区,23为n型重掺杂漏区,25为p型深阱区,31为栅氧化层,32为多晶硅栅极,33为用于连接源区和源区金属电极的金属硅化物,34为栅极侧壁,35为场板,41为连接源极和衬底的导电通道(例如钨塞通孔等),42为第一接触孔金属,43为第二接触孔金属,51为绝缘介质层,61为源极,62为漏极。

4.如图1所示的一种rfldmos器件结构采用p型沟道,通过向栅极施加正电压而使沟道表面反型形成导电沟道,靠近栅氧化层的表面沟道是强反型的,在沟道中具有最高的电流密度;然而,由于电流集中在沟道表面,会带来如下几个方面的缺点:一是由于表面散射效应的存在,会使沟道迁移率下降,导致沟道饱和电流降低,同时表面散射会引起较大的噪声,影响器件线性度;二是强的表面电流密度会引起沟道热载流子注入(hci);三是强的表面反型会导致器件开启时cgd较大,影响器件射频性能。

技术实现要素:

5.本发明的主要目的在于提供一种应用于射频放大的沟道掺杂调制rfldmos器件及制法,以克服现有技术中的不足。

6.为实现前述发明目的,本发明采用的技术方案包括:

7.本发明实施例提供了一种应用于射频放大的沟道掺杂调制rfldmos器件,其包括沿器件纵向依次叠层设置的衬底和外延层,所述外延层内分布有多层沟道区、漂移区和深阱区,所述漂移区内形成有漏区,所述深阱区内形成有源区,所述多层沟道区包括沿器件横向依次设置的多个沟道,所述多个沟道中的至少一个沟道与所述源区电连接,至少一个沟道与所述漂移区电连接;以及,

8.源极、栅极和漏极,所述栅极对应设置在所述多层沟道区的上方,所述源极与所述源区电连接,所述漏极与所述漏区电连接,并且,所述源极还经导电通道与所述衬底连接;

9.其中,所述衬底、外延层和深阱区均为第一掺杂类型,所述漂移区、多层沟道区、源区、漏区均为第二掺杂类型。

10.本发明实施例还提供了所述应用于射频放大的rfldmos器件的制作方法,其包括:

11.提供衬底,并在所述衬底上形成外延层;

12.通过离子注入和热扩散工艺在所述外延层内加工形成漂移区和深阱区,通过离子注入和热扩散工艺在所述外延层内加工形成包含多个沟道的多层沟道区,所述多个沟道沿器件横向依次设置,且使至少一个沟道与所述漂移区电连接;

13.通过离子注入和热扩散工艺在所述漂移区内加工形成漏区,在所述深阱区内加工形成源区,并使所述源区与至少一个沟道电连接;

14.以及,制作形成源极、漏极和栅极,使所述源极分别与所述衬底、源区连接,使所述漏极与所述漏区连接,其中,所述栅极对应设置在所述多层沟道区的上方。

15.与现有技术相比,本发明的优点包括:

16.1)本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,将沟道通道(即沟道)从器件表面转移至器件体内形成埋沟,使沟道通道的有效电子迁移率提升了30%以上;

17.2)本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,将碰撞电离的中心从栅氧化层与si外延层的界面处转移至si外延层内部,由此产生的热载流子在到达栅氧化层与硅外延层界面与其他原子碰撞,能量耗散后无法到达界面或者到达界面时能量不足以注入栅氧化层;

18.3)本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,通过优化沟道通道的注入,使得栅极电压降低至约0v或者负压,由于电势的降低使得热电子产生后无法到达栅氧化层,因此可以在同等hci条件下,提高漂移区的注入浓度或者缩减漂移区长度,得以提高饱和电流以及导通电阻,进而提高了器件的功率密度以及效率。

附图说明

19.图1是发明人提供一种现有rfldmos器件结构的结构示意图;

20.图2是本发明一典型实施案例中一种应用于射频放大的沟道掺杂调制rfldmos器件的结构示意图;

21.附图标记说明:11-p型重掺杂衬底,12-p型外延层,21-n型漂移区,22-n型重掺杂源区,23-n型重掺杂漏区,24-n型第一沟道,25-p型深阱区,26-n型第二沟道,31-栅氧化层,32-多晶硅栅极,33-金属硅化物,34-栅极侧壁,35-场板,41-导电通道,42-第一接触孔金属,43-第二接触孔金属51-绝缘介质层,61-源极,62-漏极。

具体实施方式

22.鉴于现有技术中的不足,本案发明人经长期研究和大量实践,得以提出本发明的技术方案。如下将对该技术方案、其实施过程及原理等作进一步的解释说明。

23.射频(rf)横向扩散金属氧化物半导体(ldmos)功率晶体管具有非常好的功率容量、增益、线性、效率和可靠性,在用于通信系统(gsm、edge、w-cdma)的基站、移动通讯终端、雷达、射频加热和照明领域等,是rf功率放大器(pa)的关键部件。

24.rf ldmos是为射频功率放大器而设计的n型mosfet器件,具有横向沟道结构,漏极、源极和栅极都在芯片表面,源极一般由体内高杂质浓度通道与衬底底部相连接并接地,在沟道与漏极之间有一个低浓度的n型漂移区。

25.本发明增加沟道注入通过将沟道通道从氧化层与外延层界面转移至器件体内,可

以大幅提升沟道的电子迁移率、降低沟道的电子散射噪声、抑制热载流子注入效应、降低cgs(栅源电容)和cgd(栅漏电容),从而大幅提升器件射频功率密度、效率和改善线性度。

26.本发明通过离子注入的方式形成沿器件横向依次设置的多个沟道,其中一沟道与源区相接,其注入深度较浅,浅结可以提高栅极对沟道的控制,可以保证器件不穿通,同时可以调节芯片vth,优化线性度;一沟道与漂移区相接,其深度较深,等效于增加了栅极电容的介质厚度,在提高饱和电流的同时可以降低cgd与cgs,使得碰撞电离距离栅氧化层距离更远,更加能够抑制热载流子注入效应。

27.本发明提供的一种应用于射频功率放大沟道浓度调制的rfldmos器件,采用n型掺杂沟道形成耗尽型nldmos器件,并应用于射频功率放大rf ldmos,以及,本发明分别对不同横向设置的多个沟道进行不同的优化,如靠近源区的沟道掺杂能量减少,靠近漂移区的沟道掺杂能量提高,可以实现对产品的开启电压vth、导通电阻rdson、跨导gm、埋沟深度以及栅极电容cgs和栅漏电容cgd进行调整,优化产品性能,提高产品寿命。

28.为了克服现有技术中的问题,本发明实施例提供了一种应用于射频放大的沟道掺杂调制rfldmos器件,其包括沿器件纵向依次叠层设置的衬底和外延层,所述外延层内分布有多层沟道区、漂移区和深阱区,所述漂移区内形成有漏区,所述深阱区内形成有源区,所述多层沟道区包括沿器件横向依次设置的多个沟道,所述多个沟道中的至少一个沟道与所述源区电连接,至少一个沟道与所述漂移区电连接;以及,

29.源极、栅极和漏极,所述栅极对应设置在所述多层沟道区的上方,所述源极与所述源区电连接,所述漏极与所述漏区电连接,并且,所述源极还经导电通道与所述衬底连接;

30.其中,所述衬底、外延层和深阱区均为第一掺杂类型,所述漂移区、多层沟道区、源区、漏区均为第二掺杂类型。

31.进一步的,与所述源区连接的沟道于外延层内的深度小于与所述漂移区连接的沟道的深度,与所述源区连接的沟道的掺杂浓度小于与所述漂移区连接的沟道的掺杂浓度。

32.进一步的,所述多个沟道于外延层内的深度沿器件横向依次增加,所述多个沟道掺杂浓度沿器件横向依次增大。

33.进一步的,在所述外延层内,相邻两个沟道于器件纵向上的深度差为0-0.5μm,相邻两个沟道的掺杂浓度差为1e

10-1e

15

cm-2

。

34.进一步的,所述多个沟道的顶部表面与外延层的顶部表面齐平,与所述源区连接的沟道的厚度为外延层厚度的0-0.5μm,与所述漂移区连接的沟道的厚度为外延层厚度的0-0.5μm。

35.进一步的,相邻两个沟道于器件横向上直接接触,或者,相邻两个沟道于器件横向上间隔设置。

36.进一步的,与所述源区连接的沟道的掺杂浓度为1e

10-1e

15

cm-2

,与所述漂移区连接的沟道的掺杂浓度为1e

10-1e

15

。

37.进一步的,所述深阱区、漂移区的顶部表面与外延层的顶部表面相平。

38.进一步的,所述深阱区的深度为0-5μm。

39.进一步的,所述漂移区的深度为0-5μm。

40.进一步的,所述外延层的厚度范围为1-50μm。

41.进一步的,所述深阱区、多层沟道区、漂移区是通过离子注入和热扩散工艺对所述

外延层的局部区域加工形成的。

42.进一步的,所述深阱区的离子注入浓度参数范围为1e

11-1e

16

cm-2

,所述漂移区的离子注入浓度参数范围为何1e

11-2e

16

。

43.更进一步的,所述源区的顶部表面与深阱区的顶部表面相平,所述源区的厚度参数为0.01-0.5μm。

44.进一步的,所述漏区的顶部表面与漂移区的顶部表面相平,所述漏区的厚度参数为0.01-0.5μm

45.进一步的,所述源区是通过离子注入和热扩散工艺对所述深阱区的局部区域加工形成的,所述漏区是通过离子注入和热扩散工艺对所述漂移区的局部区域加工形成的。

46.进一步的,所述外延层上还设置有栅氧化层,所述栅极设置在所述栅氧化层上。

47.进一步的,所述栅氧化层的材质包括二氧化硅。

48.进一步的,所述外延层上还设置有绝缘介质层,所述绝缘介质层位于所述源极、漏极与栅极之间。

49.进一步的,所述导电通道连续贯穿所述绝缘介质层、外延层并与所述衬底连接。

50.进一步的,所述导电通道包括重掺杂p型或n型深阱、金属通孔、硅片通道中的任意一种,但不限于此。

51.进一步的,所述绝缘介质层的材质包括二氧化硅,但不限于此。

52.进一步的,所述应用于射频放大的沟道掺杂调制rfldmos器件还包括与所述栅极相匹配的场板,所述场板对应设置在所述漂移区的上方。

53.进一步的,所述场板分布在所述绝缘介质层内。

54.进一步的,所述第一掺杂类型为p型,所述第二掺杂类型为n型。

55.在一些较为具体的实施方案中,所述应用于射频放大的沟道掺杂调制rfldmos器件包括沿器件纵向依次设置的p型重掺杂衬底、p型外延层、栅氧化层和栅极,

56.所述p型外延层内分布有n型漂移区、p型深阱区、n型多层沟道区,所述n型漂移区内形成有n型重掺杂漏区,所述p型深阱区内形成有n型重掺杂源区,所述n型多层沟道区对应设置在所述栅极下方;

57.所述n型多层沟道区包括沿器件横向依次设置的多个沟道,所述多个沟道中包括与n型重掺杂源区电连接的第一沟道、与n型漂移区电连接的第二沟道,所述第一沟道于p型外延层内的深度小于第二沟道的深度,第一沟道的掺杂浓度小于第二沟道的掺杂浓度;

58.以及,源极、漏极和场板,所述栅极位于所述第一沟道和第二沟道的上方,所述源极、漏极、场板设置在所述栅氧化层的上方,其中,所述源极、漏极与栅极之间还设置有绝缘介质层,所述场板分布在所述绝缘介质层内,并且,所述源极还分别经导电通道、第一接触孔金属与n型重掺杂源区、p型重掺杂衬底连接,所述漏极经第二接触孔金属与n型重掺杂漏区连接。

59.本发明实施例还提供了所述应用于射频放大的rfldmos器件的制作方法,其包括:

60.提供衬底,并在所述衬底上形成外延层;

61.通过离子注入和热扩散工艺在所述外延层内加工形成漂移区和深阱区,通过离子注入和热扩散工艺在所述外延层内加工形成包含多个沟道的多层沟道区,所述多个沟道沿器件横向依次设置,且使至少一个沟道与所述漂移区电连接;

62.通过离子注入和热扩散工艺在所述漂移区内加工形成漏区,在所述深阱区内加工形成源区,并使所述源区与至少一个沟道电连接;

63.以及,制作形成源极、漏极和栅极,使所述源极分别与所述衬底、源区连接,使所述漏极与所述漏区连接,其中,所述栅极对应设置在所述多层沟道区的上方。

64.进一步的,所述制作方法具体包括:分别通过对所述外延层的指定区域进行多次离子注入以形成所述多个沟道,且通过调节离子注入和热扩散工艺的参数以使所述多个沟道的掺杂浓度、深度不同。

65.如下将结合附图以及具体实施例对该技术方案、其实施过程及原理等作进一步的解释说明。如下若非特别说明,则其中所采用的各类原料、加工设备、加工方法均可以是本领域已知的。

66.实施例1

67.请参阅图2,一种应用于射频放大的沟道掺杂调制rfldmos器件,包括沿指定方向依次设置的p型重掺杂衬底11、p型外延层12、栅氧化层31和多晶硅栅极32(所述多晶硅栅极具有栅极侧壁34),

68.所述p型外延层12内分布有n型漂移区21、p型深阱区25、n型的第一沟道24和n型的第二沟道26,所述n型漂移区21内形成有n型重掺杂漏区23,所述p型深阱区25内形成有n型重掺杂源区22,所述第一沟道24和第二沟道26对应设置在所述多晶硅栅极32的下方,所述第一沟道24与所述n型重掺杂源区24电性连接,所述第二沟道26与n型漂移区21电连接,其中,所述第一沟道24于外延层内的深度小于第二沟道26的深度,第一沟道24的n型掺杂浓度小于第二沟道26的掺杂浓度;

69.以及,源极61、漏极62和场板35,所述源极61、漏极62、场板35设置在所述栅氧化层31的上方,其中,所述源极61、漏极62与多晶硅栅极32之间还设置有绝缘介质层51,所述场板35分布在所述绝缘介质层51内,并且,所述源极61还经第一接触孔金属42、金属硅化物(层)33与n型重掺杂源区22电连接,所述源极61还经导电通道(例如可以是为钨塞通孔)41与p型重掺杂衬底11连接,所述漏极62经第二接触孔金属43与n型重掺杂漏区23连接。

70.具体的,所述n型漂移区21于器件横向上的长度为0.1-10μm,第一沟道24和第二沟道26于器件横向上的长度均为0.01-1μm。

71.具体的,所述n型漂移区21、p型深阱区25、n型第一沟道24和n型第二沟道26是通过离子注入和热扩散的方式对p型外延层12进行加工处理后获得的,所述n型重掺杂漏区23是通过离子注入和热扩散的方式对n型漂移区21进行加工处理后获得的,所述n型重掺杂源区22是通过离子注入和热扩散的方式对p型深阱区25进行加工处理后获得的。

72.一种rfldmos器件的制作方法,包括制作形成外延层以及在外延层内制作形成n型掺杂类型的沟道区、漂移区、源区和漏区的步骤、制作形成p型掺杂类型的深阱区的步骤以及制作形成源极、漏极和栅极的步骤,具体包括:

73.通过光刻工艺分别在外延层定义注入n型掺杂的区域、注入p型掺杂的区域;

74.采用离子注入的方式在外延层内同时注入加工形成第二沟道和漂移区,注入能量为10-1000kev;

75.采用离子注入的方式在外延层内同时注入加工形成第一沟道和源区,注入能量为10-500kev;

76.源区和漏区,形成沟道区的注入能量为10-500kev,形成漂移区的注入能量为10-1000kev,形成源区的注入能量为10-500kev。

77.需要说明的是,制作外延层、沟道区、漂移区、源区和漏区、深阱区、源极、漏极、栅极以及导电通道等的工艺可以采用本领域技术人员已知工艺,其他未提及的具体工艺参数步骤等在此不作具体的限定。

78.对比例1

79.请参阅图1,一种rfldmos器件,包括沿指定方向依次设置的p型重掺杂衬底11、p型外延层12、栅氧化层31和多晶硅栅极32(所述多晶硅栅极具有栅极侧壁34),

80.所述p型外延层12内分布有n型漂移区21、p型深阱区25,所述n型漂移区21与p型深阱区25电性接触或电性结合,所述n型漂移区21内形成有n型重掺杂漏区23,所述p型深阱区25内形成有n型重掺杂源区22;

81.以及,源极61、漏极62和场板35,所述源极61、漏极62、场板35设置在所述栅氧化层31的上方,其中,所述源极61、漏极62与多晶硅栅极32之间还设置有绝缘介质层51,所述场板35分布在所述绝缘介质层51内,并且,所述源极61还经第一接触孔金属42、金属硅化物(层)33与n型重掺杂源区22电连接,所述源极61还经导电通道(例如可以是为钨塞通孔)41与p型重掺杂衬底11连接,所述漏极62经第二接触孔金属43与n型重掺杂漏区23连接。

82.具体的,对比例1中的rfldmos器件的制作方法与实施例1中的基本一致,对比例1rfldmos器件的制作方法可以采用本领域技术人员已知的现有工艺制作形成,其与实施例1的不同之处在于分别在外延层内注入加工形成沟道区、漂移区和源区,具体包括:

83.通过光刻工艺在外延层内定义n掺杂沟道区,并采用离子注入工艺加工形成n掺杂沟道区,n掺杂沟道区的注入能量为10-500kev;

84.通过光刻定义工艺在外延层内定义漂移区,并采用离子注入工艺加工形成漂移区,漂移区的注入能量为10kev-1000kev;

85.通过光刻工艺在外延层内定义源区,并采用离子注入工艺加工形成源区,源区的注入能量为10-500kev。

86.通过对实施例1和对比例1中的器件进行测试获知,对比例1中的器件有效功率密度满足hot carrier injection 10年使用后性能条件下,其最大功率为1.4w/mm,其导通电阻可做到11ohm*mm,当采用实施例1中的器件结构后,在满足相同hci的条件下,其功率密度可达2w/mm,其导通电阻降低至7ohm*mm。

87.本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,将沟道通道(即沟道)从器件表面转移至器件体内形成埋沟,沟道通道的有效电子迁移率提升了30%以上,从而有效抑制了沟道通道的热载流子注入效应,使得相同hci寿命下可以提升30%以上电流密度,并且,在低漏压区(vds<5v)时,器件的cgd电容降低50%以上。

88.本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,将沟道区部分变为多个沟道掺杂区(即前述多个沟道),一沟道掺杂区与源极相接,其注入深度较浅,同时注入浓度较低,可以保证器件不穿通,一沟道掺杂区与漂移区相接,其浓度较高且深度较深,在提高饱和电流的同时由于增加了深度,可以降低cgd与cgs、减小表面电场,抑制热载流子注入效应。

89.本发明通过优化沟道通道的注入,使器件的穿通电压提高5v以上,热载流子注入

效应进一步得到抑制,相同hci寿命下使器件的电流密度提升50%以上,器件的cgd得到进一步的优化。

90.本发明采用了包含多个沟道的多层沟道区,使得沟道区得以存在多个不同的导电沟道,当提高栅压时,多个导电沟道依次开启,从而可以有效提高线性工作区;另外,在制作中将漂移区与沟道区的离子注入过程、源区注入与沟道区的离子注入过程合并,使得channel注入的对准问题得到改善。

91.本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,将沟道通道(即沟道)从器件表面转移至器件体内形成埋沟,使沟道通道的有效电子迁移率提升了30%以上。

92.本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,将碰撞电离的中心从栅氧化层与si外延层的界面处转移至si外延层内部,由此产生的热载流子在到达栅氧化层与硅外延层界面与其他原子碰撞,能量耗散后无法到达界面或者到达界面时能量不足以注入栅氧化层。

93.另外,本发明实施例提供的一种应用于射频放大的沟道掺杂调制rfldmos器件,通过优化沟道通道的注入,使得栅极电压降低至约0v或者负压,由于电势的降低使得热电子产生后无法到达栅氧化层,因此可以在同等hci条件下,提高漂移区的注入浓度或者缩减漂移区长度,得以提高饱和电流以及导通电阻,进而提高了器件的功率密度以及效率。

94.应当理解,上述实施例仅为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。