1.本发明涉及一种显示装置。

背景技术:

2.在专利文献1中,公开了一种在包含控制发光元件的亮度的驱动晶体管、保持电容器、以及初始化晶体管的像素电路中,经由保持电容器连接驱动晶体管的栅极以及电源布线的结构。现有技术文献专利文献

3.专利文献1:日本国公开特许公报「特开2015-49335」

技术实现要素:

发明要解决的问题

4.在电源布线的布线电阻较大的情况下,电源电压产生变动,对发光元件的亮度控制造成不良影响。用于解决问题的手段

5.本发明的一方面涉及的显示装置,具有多个像素电路,所述像素电路包括保持电容器、驱动晶体管以及初始化晶体管,具备半导体层、栅极绝缘膜、第一布线层、第一无机绝缘膜、第二布线层、第二无机绝缘膜、第三布线层,各像素电路包括:对应所述驱动晶体管设置的电容电极;与所述初始化晶体管的一个导通端子电连接的连接布线,在行方向相邻的两个像素电路共用电容布线,所述电容电极包含在第一布线层中,所述电容布线包含在第二布线层中,所述连接布线包含在第三布线层中,所述连接布线经由设置在所述第一无机绝缘膜和所述第二无机绝缘膜中的第一接触孔与所述电容电极电连接,在所述两个像素电路的各个中,在所述电容布线上形成有俯视时包围所述第一接触孔的第一开口,并且在所述电容电极和所述电容布线的重叠部构成所述保持电容器的至少一部分,所述电容布线包括位于相邻的两个第一开口之间的第二开口;和通过所述第二开口在列方向上相对的第一连接布线和第二连接布线。发明效果

6.根据本发明的一方面,能够减少由所述电容布线的布线电阻。

附图说明

7.图1的(a)是表示第一实施方式的显示装置的结构的平面图,图1的(b)是表示第一实施方式的显示装置的结构的截面图。图2是表示第一实施方式的像素电路的结构的电路图。图3的(a)是表示像素电路的结构的平面图,图3的(b)是表示电容布线的结构的平面图。

图4的(a)为图3的a-a线的截面图,图4的(b)为图3的b-b线的截面图,图4的(c)为图3的c-c线的截面图。图5的(a)是表示保持电容器的平面图,图5的(b)是表示驱动晶体管的平面图。图6的(a)是表示电容布线的变形例的平面图,图6的(b)是表示电容布线的比较例的平面图。图7是表示第二实施方式的像素电路的结构的电路图。图8的(a)是表示像素电路的结构的平面图,图8的(b)是表示电容布线的结构的平面图。图9的(a)是表示保持电容器的平面图,图9的(b)是表示多个驱动晶体管的平面图。图10的(a)是表示第二实施方式的电容布线的平面图,图10的(b)是表示比较例的电容布线的平面图。

具体实施方式

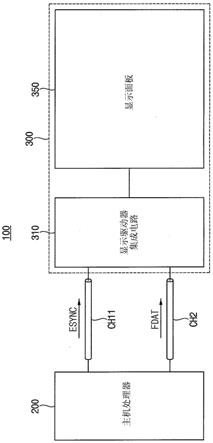

8.〔第一实施方式〕图1的(a)是表示第一实施方式的显示装置的结构的示意图,图1的(b)是表示第一实施方式的显示装置的结构的截面图。如图1所示,在显示装置2中,在基板12上依次形成有阻挡层3、薄膜晶体管层4、顶部发光(向上层侧发光)型的发光元件层5以及密封层6,在显示区域da中设置有分别包含发光元件ex的多个像素电路pk1,pk2以及多个布线(包括扫描信号线gn、数据信号线dl、电容布线cs。在包围显示区域da的边框区域na设置端子部和各种驱动器等。

9.基板12是玻璃基板或以聚酰亚胺等树脂为主要成分的柔性基材,例如,也可以由2层聚酰亚胺膜及夹在该些之间的无机膜构成基板12。阻挡层(底涂层)3是防止水、氧等异物的侵入的无机绝缘层,例如能够使用氮化硅、氧化硅等构成。

10.薄膜晶体管层4包括:比阻挡层3更上层的半导体层ps;比半导体层ps更上层的栅极绝缘膜16;比栅极绝缘膜16更上层的第一布线层m1(包括扫描信号线gn);比第一布线层m1更上层的第一无机绝缘膜18;比第一无机绝缘膜18更上层的第二布线层m2(包括电容布线、初始化电源线il);比第二布线层m2更上层的第二无机绝缘膜20;比第二无机绝缘膜20更上层的第三布线层m3(包括数据信号线dl);以及比第三布线层m3更上层的平坦化膜21。

11.半导体层ps例如是低温形成的多晶硅(ltps),晶体管构成为第一布线层m1中包含的栅极与半导体层ps的沟道夹着栅极绝缘膜16。关于半导体层ps,可以将晶体管的沟道以外的区域导体化。

12.第一布线层、第二布线层及第三布线层例如由包含铝、钨、钼、钽、铬、钛及铜中的至少一种的金属的单层膜或多层膜构成。

13.栅极绝缘膜16、第一无机绝缘膜18以及第二无机绝缘膜20可以由例如通过cvd法形成的氧化硅(siox)膜、氮化硅(sinx)膜或它们的层叠膜构成。平坦化膜21能够由例如聚酰亚胺、丙烯酸树脂等能够涂布的有机材料构成。

14.发光元件层5包括:比平坦化膜21更上层的第一电极(下部电极)22、覆盖第一电极22的边缘的绝缘性的边缘覆盖膜23、比边缘覆盖膜23更上层的el(电致发光)层24、比el层

24更上层的第二电极(上部电极)25。边缘覆盖膜23例如通过在涂覆了聚酰亚胺、丙烯酸树脂等有机材料后利用光刻进行图案化而形成。

15.发光元件层5例如形成发射不同颜色的光的多个发光元件ex,各发光元件包括岛状的第一电极22、el层24(包括发光层ek)和第二电极25。第二电极25是多个发光元件共用的整体状的共用电极。

16.发光元件ex例如可以是包含有机层作为发光层的oled(有机发光二极管),也可以是包含量子点层作为发光层的qled(量子点发光二极管)。

17.el层24例如构成为从下层侧依次层叠空穴注入层、空穴传输层、发光层ek、电子传输层、电子注入层。发光层通过蒸镀法或喷墨法、光刻法,在边缘覆盖膜23的开口(每个子像素)形成岛状。其他层为岛状或整体(共用层)地形成。另外,也可以构成为不形成空穴注入层、空穴输送层、电子输送层、电子注入层中的一个以上的层。

18.第一电极22(阳极)由例如ito(indium tin oxide)和ag(银)或包含ag的合金的层叠构成,为光反射性电极。第二电极25(阴极)例如由镁银合金等金属薄膜构成,具有透光性。

19.在发光元件ex为oled的情况下,通过第一电极22和第二电极25间的驱动电流,空穴和电子在发光层ek内复合,在由此产生的激子迁移到基底状态的过程中发射光。在发光元件ex为qled的情况下,通过第一电极22以及第二电极25之间的驱动电流使空穴和电子在发光层ek内复合,由此产生的激子从量子点的导带能级(conduction band)向价带能级(valence band)跃迁的过程中发出光(荧光)。

20.覆盖发光元件层5的密封层6是防止水、氧等异物渗入发光元件层5的层,例如可以由两层无机密封膜26、28和在它们之间形成的有机膜27构成。

21.功能膜39例如具有触摸传感器功能、光学补偿功能、保护功能的至少一种。

22.图2是示出像素电路pk的结构的电路图。图3的(a)是表示像素电路pk的结构的平面图,图3的(b)是表示电容布线的结构的平面图。图4的(a)为图3的a-a线的截面图,图4的(b)为图3的b-b线的截面图,图4的(c)为图3的c-c线的截面图。图5的(a)是表示保持电容器的平面图,图5的(b)是表示驱动晶体管的平面图。

23.在图3中,关于像素电路pk,从左开始示出了3个像素电路pk-1、pk-2、pk-3。以下,有时将

“‑

1”、

“‑

2”和

“‑

3”分别表示为与第一子像素、第二子像素、第三子像素对应的符号。这些像素电路pk分别对应于第一子像素、第二子像素、第三子像素,这些子像素分别独立地发出例如红色、绿色、蓝色的颜色的光,作为一个像素显示颜色。将与第一子像素、第二子像素、第三子像素对应的第一电极22在图3(a)中分别表示为22-1、22-2、22-3。

24.像素电路pk包括:发光元件ex、保持电容器cp、栅极与前级的放电控制线fn-1连接的初始化晶体管ti、栅极与本级的扫描信号线gn连接的阈值控制晶体管ts、栅极与本级的扫描信号线gn连接的写入控制晶体管tw、驱动晶体管td、栅极与本级的发光控制线en连接的电源供给晶体管tp、栅极与本级的发光控制线en连接的发光控制晶体管te、栅极与本级的放电控制线fn连接的放电晶体管tf。

25.放电控制线fn-1

·

fn、扫描信号线gn及发光控制线en在行方向(x方向)上延伸。这些布线形成于第一布线层m1或第二布线层m2或m1、m2两者。另外,在形成于第二布线层m2的情况下,至少作为栅极发挥作用的部分更换为第一布线层m1。在本实施方式中,如图4的(a)

以及图4的(b)所示,成为隔着第一无机绝缘膜而形成在第一布线层m1以及第二布线层m2的双方的层叠布线(下侧布线以及上侧布线),下侧布线以及上侧布线经由未图示的接触孔电连接。

26.初始化晶体管ti由栅极彼此电连接的串联连接的2个p型晶体管构成。阈值控制晶体管ts由栅极彼此电连接的串联连接的2个p型晶体管构成。电源供给晶体管tp由栅极彼此电连接的并联连接的2个p型晶体管构成。发光控制晶体管te由栅极彼此电连接的并联连接的2个p型晶体管构成。写入控制晶体管tw、驱动晶体管td和放电晶体管tf分别是p型晶体管。

27.驱动晶体管td的栅极经由电容元件cp与电容布线cs连接,并且经由初始化晶体管ti与初始化电源线il连接。

28.驱动晶体管td的源极经由写入控制晶体管tw与数据信号线dl连接,并且经由电源供给晶体管tp与第一电源布线pl连接。驱动晶体管td的漏极经由发光控制晶体管te而与发光元件ex的阳极连接,并且经由阈值控制晶体管ts而与驱动晶体管td的栅极连接。发光元件ex的节点经由放电晶体管tf与初始化电源线il连接。发光元件ex的阴极与低电压(elvss)侧的第二电源布线ql电连接。

29.初始化电源线il形成于第二布线层m2,沿行方向(x方向)延伸。数据信号线dl、第一电源布线pl以及第二电源布线ql分别形成于第三布线层m3,并沿列方向(y方向)延伸。

30.像素电路pk具有将与驱动晶体管td对应地设置的电容电极ce和初始化晶体管ti的一个导通端子(半导体层ps的导体区域)电连接的连接布线sh。而且,还具有将放电晶体管tf的一个导通端子与发光控制晶体管te的一个导通端子电连接的连接电极se,如后所述,连接电极se与第一电极22电连接。电容电极ce也作为驱动晶体管td的栅极(控制电极)发挥功能。

31.在行方向(x方向)上相邻的3个像素电路pk-1、pk-2、pk-3共用电容布线cs。电容电极ce包含于第一布线层m1,电容布线cs包含于第二布线层m2,连接布线sh及连接电极se包含于第三布线层m3。

32.连接布线sh经由设置于第一无机绝缘膜18和第二无机绝缘膜20的第一接触孔h1与电容电极ce电连接,并且经由栅极绝缘膜16、设置于第一无机绝缘膜18和第二无机绝缘膜20的第四接触孔h4与阈值控制晶体管ts的一个导通端子(半导体层ps的导体区域)电连接。另外,连接布线sh经由第四接触孔h4与初始化晶体管ti的一个导通端子(半导体层ps的导体区域)电连接。

33.电容布线cs经由设置于第二无机绝缘膜20的第二接触孔h2与高电压(elvdd)侧的第一电源布线pl连接,作为elvdd布线发挥功能。连接电极se通过设置于平坦化膜21的第三接触孔h3与第一电极22(发光元件ex的阳极)电连接。

34.在通过像素电路pk-1、pk-2、pk-3的电容布线cs中,形成有俯视时包围第一接触孔h1的第一开口k1,并且在电容电极ce和电容布线cs的重叠部(图5的(a)的阴影区域)构成保持电容器cp。

35.如图3(b)及图4所示,梯子形状的电容布线cs包括:位于相邻的两个第一开口k1之间的第二开口k2;以及经由第二开口k2与列方向(y方向)相对的第一连接布线cj1及第二连接布线cj2。图3(b)中,左侧的第一开口kl(kl-l)与第一子像素对应,右侧的第一开口kl

(kl-2)与第二子像素对应。左侧的第二开口k2(k2-1)夹在第一子像素的第一开口k1(k1-1)与第二子像素的第一开口k1(k1-2)之间,右侧的第二开口k2(k2-2)夹在第二子像素的第一开口k1(k1-2)与第三子像素的第一开口k1(k1-3)之间。

36.如图3所示,电容布线cs包括比第一开口k1位于更外侧且在列方向上相对的第一对置部ct1和第二对置部ct2,第一连接布线cj1的外侧边缘(外侧面)和在行方向上与第一连接布线cj1相邻的两个第一对置部ct1的外侧边缘(外侧面)分别共面,第二连接布线cj2的外侧边缘(外侧面)和在行方向上与第二连接布线cj2相邻的两个第二对置部ct2的外侧边缘(外侧面)分别共面。所谓共面,是指在两条布线的外侧面没有阶差,平坦地连接。第一连接布线cj1与第一对置部ct1的宽度(y方向的尺寸)相同,第二连接布线cj2与第二对置部ct2的宽度相同。

37.第一电源布线pl构成为与第一开口k1重叠的部分的宽度wb大于位于列方向上相邻的两个像素电路之间的部分的宽度ws。通过该结构,能够减少寄生电容,并且能够减小电流较多地流动的第一电源布线pl的布线电阻。数据信号线dl与第二开口k2重叠。根据该结构,由于不与相当于电容布线cs的整个宽度的区域重叠,因此能够降低寄生电容,并能够降低信号的波动。

38.如图4、图5所示,关于驱动晶体管td的沟道cn(半导体层ps与电容电极ce的重叠部),沟道宽度cw(列方向的尺寸)大于沟道长度cl(行方向的尺寸)(例如cw>cl

×

2)。电容电极ce为矩形,沟道宽度的方向(列方向)的尺寸比沟道长度的方向(行方向)大。由此,能够使大的电流在驱动晶体管td流动。

39.图6的(a)是表示电容布线的变形例的平面图,图6的(b)是表示电容布线的比较例的平面图。通过形成第一连接布线cj1及第二连接布线cj2,与如图6的(b)所示的使电容布线的外侧边缘的一部分向内侧凹陷的比较例相比,能够使电容布线cs的布线电阻降低,即使在驱动晶体管td流动大电流的情况下,也能够使电容布线cs的电位(elvdd)稳定化。

40.图3(b)中,第一连接布线cj1的宽度(y方向的尺寸)和第一对置部ct1的宽度(y方向的尺寸)相等,第二连接布线cj2的宽度(y方向的尺寸)和第二对置部ct2的宽度(y方向的尺寸)相等,但并不限于此。为了降低数据信号线dl与电容布线cs之间的寄生电容,如图6的(a)所示,也能够使第一连接布线cj1的宽度(y方向的尺寸)比第一对置部ct1的宽度(y方向的尺寸)小,使第二连接布线cj2的宽度(y方向的尺寸)比第二对置部ct2的宽度(y方向的尺寸)小。

41.〔第二实施方式〕图7是表示第二实施方式的像素电路的结构的电路图。图8的(a)是表示像素电路的结构的平面图,图8的(b)是表示电容布线的结构的平面图。图9的(a)是表示保持电容器的平面图,图9的(b)是表示多个驱动晶体管的平面图。第二实施方式中的像素电路(pk1、pk2)具有并联连接的多个驱动晶体管(第一晶体管td1、第二晶体管td2、第三晶体管td3、第四晶体管td4)和与第一晶体管td1~第四晶体管td4对应地设置的多个电容电极ce1~ce4,在行方向上相邻的2个像素电路pk1、pk2共用与电容电极ce1~ce4分别重叠的4条电容布线cs1~cs4。

42.具体而言,初始化晶体管ti的一个导通端子与连接布线sh电连接,在列方向上排列的电容电极ce1~ce4经由4个接触孔h1与连接布线sh电连接。

43.在作为第一晶体管td1的栅极的电容电极ce1与电容布线cs1的重叠部形成电容c1,作为第二晶体管td2的栅极的电容电极ce2与电容布线cs2重叠,作为第三晶体管td3的栅极的电容电极ce3与电容布线cs3重叠,作为第四晶体管td4的栅极的电容电极ce4与电容布线cs4重叠。

44.此外,电容布线cs1、电容布线cs2、电容布线cs3、电容布线cs4经由第二接触孔h2与第一电源布线pl电连接。如图9的(a)所示,通过形成于电容电极ce1与电容布线cs1的重叠部((图9(a)的阴影区域)的电容器c1、形成于电容电极ce2与电容布线cs2的重叠部((图9(a)的阴影区域)的电容器c2、形成于电容电极ce3与电容布线cs3的重叠部((图9(a)的阴影区域)的电容器c3、形成于电容电极ce4与电容布线cs4的重叠部((图9(a)的阴影区域)的电容器c4的合成(4个电容器c1~c4的并联连接),构成像素电路pk的电容器cp。

45.如图8所示,梯子形状的电容布线cs1包括:在俯视中包围第一接触孔h1的第一开口k1、位于相邻的两个第一开口k1之间的第二开口k2、经由第二开口k2与列方向(y方向)相对的第一连接布线cj1和第二连接布线cj2。

46.电容布线cs1包括比第一开口k1位于更外侧且在列方向上相对的第一对置部ct1和第二对置部ct2,第一连接布线cj1的外侧边缘(外侧面)和在行方向上与第一连接布线cj1相邻的两个第一对置部ct1的外侧边缘(外侧面)分别共面,第二连接布线cj2的外侧边缘(外侧面)和在行方向上与第二连接布线cj2相邻的两个第二对置部ct2的外侧边缘(外侧面)分别共面。第一连接布线cj1与第一对置部ct1的宽度(y方向的尺寸)相同(例如4.5μm),第二连接布线cj2与第二对置部ct2的宽度相同(例如4.5μm)。

47.第一电源布线pl构成为与第一开口k1重叠的部分的宽度大于位于列方向上相邻的两个像素电路之间的部分的宽度。数据信号线dl与第二开口k2重叠。

48.如图8以及图9所示,关于驱动晶体管td1的沟道cn(半导体层ps和电容电极ce1的重叠部),沟道宽度cw(列方向的尺寸,例如22.7μm)大于沟道长度cl(行方向的尺寸,例如20.5μm)。电容电极ce为矩形,沟道宽度的方向(列方向)的尺寸比沟道长度的方向(行方向)大。第一开口k1为矩形,沟道宽度的方向的尺寸(例如30.1μm)大于沟道长度的方向的尺寸(例如14.5μm)。

49.电容电极ce2~ce4也与电容电极ce1为相同结构,电容布线cs2~cs4也与电容布线cs1为相同结构,第二晶体管td2~第四晶体管td4也与第一晶体管td1为相同结构。

50.并联连接的第一晶体管td1~第四晶体管td4在列方向上排列,栅极彼此相互连接,源极彼此相互连接,漏极彼此相互连接。具体而言,第一晶体管td1和第二晶体管td2共用半导体层ps的源极区域ssa,第二晶体管td2和第三晶体管td3共用半导体层ps的漏极区域sd,第三晶体管td3和第四晶体管td4共用半导体层ps的源极区域ssb。由此,能使大电流流过第一晶体管td1第四晶体管td4。

51.如图8的(b)所示,通过在各电容布线cs1~cs4形成第一连接布线cj1及第二连接布线cj2,与图9那样的比较例相比,能够降低电容布线cs1~cs4的布线电阻,即使在第一晶体管td1~第四晶体管td4流过大的电流的情况下,也能够使电容布线cs1~cs4的电位(elvdd)稳定化。

52.图10的(a)是表示第二实施方式的电容布线的平面图,图10的(b)是表示比较例的电容布线的平面图。图10的(a)的第二实施方式(梯子型的电容布线)以及图10的(b)的比较

例(使外侧边缘的一部分向内侧凹陷而成的电容布线)中,例如,通过构成为a2=b2、a3=b3、a4=b4、a5=b5、a6=b6、a7=b7、b1 b8(外侧边缘的凹陷量) b9(外侧边缘的凹陷量)=b2=a2、b1=a3

×

2,能够使第二实施方式的电容布线cs1的电阻值与比较例的电容布线的电阻值低5%左右。

53.上述的各实施方式以例示及说明为目的,并非以限定为目的。基于这些例示及说明,本领域技术人员应当明白能够进行多种变形方式。

54.〔总结〕〔方面1〕一种显示装置,具有多个像素电路,所述像素电路包括保持电容器、驱动晶体管以及初始化晶体管,从基板依次具备半导体层、栅极绝缘膜、第一布线层、第一无机绝缘膜、第二布线层、第二无机绝缘膜、第三布线层,各像素电路包括:第一布线层中包含的岛状的电容电极;第二布线层中包含的沿行方向延伸的电容布线;第三布线层中包含的、与所述初始化晶体管的一个导通端子和所述电容电极电连接的连接布线,所述电容布线与在行方向上相邻的两个像素电路的电容布线电连接,所述连接布线通过设置于所述第一无机绝缘膜以及所述第二无机绝缘膜的第一接触孔与所述电容电极电连接,在所述两个像素电路的各个中,在所述电容布线上形成有俯视时包围所述第一接触孔的第一开口,并且在所述电容电极和所述电容布线隔着所述第一无机绝缘膜重叠的重叠部构成所述保持电容器,所述电容布线包括位于在行方向相邻的两个第一开口之间的第二开口;和通过所述第二开口在列方向上相对的第一连接布线和第二连接布线。

55.〔方面2〕如方面1所述的显示装置,其中,所述电容布线包括俯视时隔着所述第一开口在列方向上相对的第一对置部和第二对置部,所述第一连接布线的外侧边缘与在行方向上相邻的所述第一对置部的外侧边缘共面,所述第二连接布线的外侧边缘与在行方向上相邻的所述第二对置部的外侧边缘共面。

56.〔方面3〕如方面2所述的显示装置,其中,所述第一连接布线的宽度与所述第一对置部的宽度相等,所述第二连接布线的宽度与所述第二对置部的宽度相等。

57.〔方面4〕如方面2所述的显示装置,所述第一连接布线的宽度比所述第一对置部的宽度小,所述第二连接布线的宽度比所述第二对置部的宽度小。

58.〔方面5〕如方面3或者4所述的显示装置,所述第一连接布线的宽度与所述第二连接布线的宽度相等。

59.〔方面6〕如方面1至5中任一项所述的显示装置,具备与所述第二开口重叠的数据信号线。

60.〔方面7〕如方面1至6中任一项所述的显示装置,所述电容电极为所述驱动晶体管的控制电极,所述驱动晶体管的沟道宽度大于沟道长度。

61.〔方面8〕如方面7所述的显示装置,所述电容电极在所述沟道宽度的方向上的尺寸比所述沟道长度的方向上的尺寸大。

62.〔方面9〕如方面7所述的显示装置,所述第一开口在所述沟道宽度的方向上的尺寸比所述沟道长度的方向的尺寸大。

63.〔方面10〕如方面1至9中任一项所述的显示装置,在所述第三布线层中包括第一电源布线,所述电容布线通过设置于所述第二无机绝缘膜的第二接触孔与所述第一电源布线电连接。

64.〔方面11〕如方面10所述的显示装置,在列方向上延伸的所述第一电源布线的与所述第一开口重叠的部分的宽度比与在列方向上与相邻的两个像素电路之间重叠的部分的宽度大。

65.〔方面12〕如方面1至11中任一项所述的显示装置,各像素电路具有:包括上述驱动晶体管且并联连接的多个驱动晶体管;以及与所述多个驱动晶体管对应地设置并包含所述电容电极的多个电容电极,在行方向上相邻的两个像素电路共用与所述多个电容电极重叠的多个电容布线。

66.〔方面13〕如方面12所述的显示装置,所述多个电容电极与所述连接布线电连接。

67.〔方面14〕如方面12所述的显示装置,所述多个驱动晶体管包括沿列方向排列的第一晶体管和第二晶体管,所述第一晶体管和所述第二晶体管共用半导体层的源极区域。

68.〔方面15〕如方面14述的显示装置,所述多个驱动晶体管包括沿列方向排列的第一晶体管、第二晶体管和第三晶体管,所述第二晶体管和所述第三晶体管共用半导体层的漏极区域。

69.〔方面16〕如方面15述的显示装置,所述多个驱动晶体管包括沿列方向排列的第一晶体管、第二晶体管、第三晶体管和第四三晶体管,所述第三晶体管和所述第四晶体管共用半导体层的源极区域。附图标记说明

[0070]2ꢀꢀ

显示装置4

ꢀꢀ

薄膜晶体管层;5

ꢀꢀ

发光元件层6

ꢀꢀ

密封层12 基板16 栅极绝缘膜18 第一无机绝缘膜20 第二无机绝缘膜21 平坦化膜22 第一电极23 边缘覆盖膜24 el层25 第二电极ce 电容电极cs 电容布线cs1~cs4 电容布线k1 第一开口k2 第二开口cj1 第一连接布线cj2 第二连接布线ct1 第一对置部ct2 第二对置部td 驱动晶体管td1~td4 第一晶体管~第四晶体管cp 保持电容器dl 数据信号线pl 第一电源布线

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。