1.本技术涉及显示技术领域,具体涉及一种阵列基板及显示面板。

背景技术:

2.目前,在显示面板产品中,显示区的正常显示由扫描线和数据线共同控制,扫描线控制像素薄膜晶体管的开关,数据线承载像素需要输入的电压信号。

3.其中,在goa产品中,扫描线的信号经基板走线、时钟信号线以及连接线传递给goa电路,再通过goa电路输入至显示区的扫描线。现有产品在设计的过程中,为了保证传递至goa电路的时钟信号相同,会对不同时钟信号线的阻值进行调整,调整至不同时钟信号线之间电阻值的差值接近于0,从而保证每条时钟信号线传输的电流值相同。但是时钟信号的传输,不仅同电流相关,也同电压相关。但是由于不同时钟信号线过孔位置对应的电阻存在差异,从而导致电压出现差异,进而导致显示面板出现水平线现象。

4.因此,如何保证每条时钟信号线传输的电流值以及电压值均相当,以避免显示面板出现水平线现象是现有面板厂家需要努力攻克的难关。

技术实现要素:

5.本技术实施例的目的在于提供一种阵列基板及显示面板,能够解决现有的不同信号线传输的电压值存在差异,从而导致显示面板出现水平线现象的技术问题。

6.本技术实施例提供一种阵列基板,包括goa电路、多条连接线以及多条时钟信号线,所述时钟信号线用于经所述连接线向所述goa电路提供时钟信号;其中,

7.每条所述时钟信号线均包括相连的第一子时钟信号线以及第二子时钟信号线,所述第一子时钟信号线与所述第二子时钟信号线的交接处为所述时钟信号线与所述连接线的连接处,且每条所述第一子时钟信号线的阻值均相等,每条所述第二子时钟信号线的阻值均相等。

8.在本技术所述的阵列基板中,所述时钟信号线与所述连接线一一对应连接,所述时钟信号线沿着所述第一方向排列,所述连接线沿着与所述第一方向垂直的第二方向排列。

9.在本技术所述的阵列基板中,所述第一子时钟信号线的长度沿着所述第一方向越来越大,所述第一子时钟信号线的宽度沿着所述第一方向越来越大。

10.在本技术所述的阵列基板中,所述第一子时钟信号线的宽度沿着所述第一方向不变,所述第一子时钟信号线的长度沿着所述第一方向不变。

11.在本技术所述的阵列基板中,所述第一子时钟信号线的长度沿着所述第一方向越来越大,所述第一子时钟信号上设置有多个第一挖空部。

12.在本技术所述的阵列基板中,所述第二子时钟信号线的长度沿着所述第一方向越来越小,所述第二子时钟信号线的宽度沿着所述第一方向越来越小。

13.在本技术所述的阵列基板中,所述第二子时钟信号线的宽度沿着所述第一方向不

变,所述第二子时钟信号线的长度沿着所述第一方向不变。

14.在本技术所述的阵列基板中,所述第二子时钟信号线的长度沿着所述第一方向不变,所述第二子时钟信号线上设置有多个第二挖空部。

15.在本技术所述的阵列基板中,每条所述时钟信号线均与多条所述连接线连接,每条所述时钟信号线均包括多条第三子时钟信号线,多条所述第三子时钟信号线依次连接,且所述第三子时钟信号线与所述第一子时钟信号线连接,所述第三子时钟信号线与所述第二子时钟线连接,所述第三子时钟信号线与所述第一子时钟信号线的交接处为所述时钟信号线与所述连接线的连接处,相邻的两条所述第三子时钟信号线的交接处为所述时钟信号线与所述连接线的连接处,所述第三子时钟信号线与所述第二子时钟信号线的交接处为所述时钟信号线与所述连接线的连接处,所述时钟信号线上的多个所述第三子时钟信号线的阻值之和相等。

16.在本技术所述的阵列基板中,在同一条所述时钟信号线上,每个所述第三子时钟信号线的阻值相等。

17.本技术实施例还提供一种显示面板,所述显示面板包括彩膜基板以及如上述所述的阵列基板,所述彩膜基板和所述阵列基板相对设置。

18.在本技术实施例提供的阵列基板以及显示面板中,包括goa电路、多条连接线以及多条时钟信号线,其中,时钟信号线在连接线与时钟信号线的交接处被分为两段,即时钟信号线被分为相互连接的第一子时钟信号线以及第二子时钟信号线。通过使每条第一子时钟信号线的阻值均相等,且使每条第二子时钟信号线的阻值均相等,可以保证每条时钟信号线传输的电流值以及电压值均相等,从而可以避免显示面板出现水平线现象,有利于提高显示面板的显示效果。

附图说明

19.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

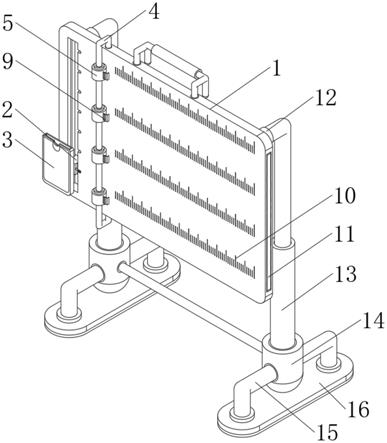

20.图1为本技术实施例提供的阵列基板的第一结构示意图。

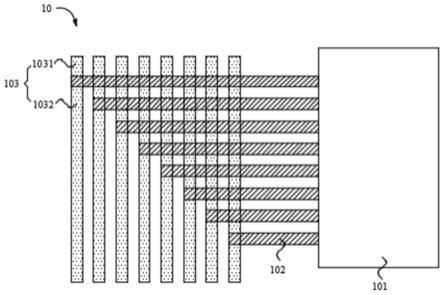

21.图2为本技术实施例提供的时钟信号传输模型图。

22.图3为本技术实施例提供的阵列基板的第二结构示意图。

23.图4为本技术实施例提供的阵列基板的第三结构示意图。

24.图5为本技术实施例提供的阵列基板的第四结构示意图。

25.图6为本技术实施例提供的阵列基板的第五结构示意图。

26.图7为本技术实施例提供的阵列基板的第六结构示意图。

27.图8为本技术实施例提供的阵列基板的第七结构示意图。

28.图9为本技术实施例提供的显示面板的结构示意图。

具体实施方式

29.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完

整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

30.请参阅图1以及图2,图1为本技术实施例提供的阵列基板的第一结构示意图,图2为本技术实施例提供的时钟信号传输模型图。如图1以及图2所示,本技术实施例提供的阵列基板10包括goa电路101、多条连接线102以及多条时钟信号线103。其中,每条时钟信号线103均包括相连的第一子时钟信号线1031以及第二子时钟信号线1032。第一子时钟信号线与第二子时钟信号线的交接处为时钟信号线103与连接线102的连接处。

31.其中,需要说明的是,时钟信号线103用于经连接线102向goa电路提供时钟信号。goa电路用于依据时钟信号向显示面板提供扫描信号,从而控制像素薄膜晶体管的开关态。

32.其中,时钟信号线103与连接线102一一对应连接。时钟信号线103沿着第一方向x排列,连接线沿着与第一方向x垂直的第二方向y排列。需要说明的是,第一方向x与时钟信号线103的延伸方向垂直,且第一方向x与连接线102的延伸方向平行。第二方向y与时钟信号线103的延伸方向平行,且第二方向y与连接线102的延伸方向垂直。具体地,时钟信号线103的延伸方向为时钟信号线103起始端至时钟信号线103末端的方向,连接线102的延伸方向为连接线102起始端至连接线102末端的方向。

33.其中,每条第一子时钟信号线1031的阻值均相等。第二子时钟信号线1032的阻值均相等。

34.需要说明的是,由于时钟信号线103仅包括第一子时钟信号线1031以及第二子时钟信号线10b,因此当每条第一子时钟信号线1031的阻值均相等,且第二子时钟信号线1032的阻值均相等时,那么每条时钟信号线103的阻值也均相等。而由于每条子时钟信号线103接收到的时钟信号的电压是一致的,那么当每条时钟信号线103的阻值均相等时,那么每条时钟信号线103传经连接线102输出至goa电路101的时钟信号的电流值也是相同的。

35.需要说明的是,由于在同一条时钟信号线103上的第一子时钟信号线1031和第二子时钟信号线1032处于串联状态,因此,第一子时钟信号线1031和第二子时钟信号线1032会起到电阻分压的作用,第一子时钟信号线1031和第二子时钟信号线1032分到的具体电压会与他们的阻值有关。而当每条第一子时钟信号线1031的阻值均相等,且第二子时钟信号线1032的阻值均相等时,那么每条第一子时钟信号线1031分到的电压均相等,每条第二子时钟信号线1032分到的电压也均相等。另外,第一子时钟信号线与第二子时钟信号线的交接处为时钟信号线103与连接线102的连接处,因此每条时钟信号线103传经连接线102输出至goa电路101的时钟信号的电压值也是相同的。

36.由上述可知,本技术实施例通过限定每条第一子时钟信号线1031的阻值均相等以及第二子时钟信号线1032的阻值均相等,使每条时钟信号线103传经连接线102输出至goa电路101的时钟信号的电流值也是相同的,且每条时钟信号线103传经连接线102输出至goa电路101的时钟信号的电流值也是相同的,从而避免了显示面板出现水平线现象。因此,采用本技术实施例提供的阵列基板可以避免显示面板出现水平线现象,从而提高显示面板的显示效果。

37.请参阅图3,图3为本技术实施例提供的阵列基板的第二结构示意图。如图3所示,在本技术实施例提供的阵列基板10中,第一子时钟信号线1031的长度l1沿着第一方向x越

来越大,第一子时钟信号线1031的宽度d1沿着第一方向x越来越大。

38.其中,需要说明的是,由于时钟信号线103的排布方向与连接线102的排布方向垂直,因此,为了防止连接线102之间相互交叉,第一子时钟信号线1031的长度l1沿着第一方向x越来越大。

39.而在本技术实施例提供的阵列基板10中,每条第一时钟信号线1031的阻值需要相等。而对于信号线来说,信号线的长度以及宽度均会影响信号线的阻值,其中,信号线的长度与信号线的阻值成正比,信号线的宽度与信号线的阻值成反比。虽然第一子时钟信号线1031的长度l1沿着第一方向x越来越大,但是第一子时钟信号线1031的宽度d1沿着第一方向x越来越大,因此本技术实施例提供的阵列基板10可以使每条第一子时钟信号线1031的阻值相等,从而避免显示面板出现水平线现象,进而提高显示面板的显示效果。

40.请参阅图4,图4为本技术实施例提供的阵列基板的第三结构示意图。如图4所示,在本技术实施例提供的阵列基板10中,第一子时钟信号线1031的长度l1沿着第一方向x越来越大,每条第一子时钟信号线1031上均设置有第一挖空部1031a,且第一子时钟信号线1031上的第一挖空部1031a的个数沿着第一方向x越来越多。

41.其中,需要说明的是,由于时钟信号线103的排布方向与连接线102的排布方向垂直,因此,为了防止连接线102之间相互交叉,第一子时钟信号线1031的长度l1沿着第一方向x越来越大。

42.其中,需要说明的是,对于信号线来说,信号线的长度会影响信号线的阻值,其中,信号线的长度与信号线的阻值成正比。其中,第一子时钟信号线1031的长度l1沿着第一方向x越来越大,从而使第一子时钟信号线1031的阻值沿着第一方向x越来越大。

43.另外,第一子时钟信号线1031上设置有第一挖空部1031a,第一挖空部1031a可以降低第一子时钟信号线1031的阻值,第一挖空部1031a设置的个数越多,能够降低第一子时钟信号线1031的阻值越多。因此本技术实施例通过在每条第一子时钟信号线1031上均设置有第一挖空部1031a,且第一子时钟信号线1031上的第一挖空部1031a的个数沿着第一方向x越来越多,可以避免由于第一子时钟信号线1031的长度l1沿着第一方向x越来越大,而导致第一子时钟信号线1031的阻值沿着第一方向x越来越大,从而能够使每条第一子时钟信号线1031的阻值相等。

44.因此,本技术实施例提供的阵列基板10可以使每条第一时钟信号线1031的阻值相等,从而避免显示面板出现水平线现象,进而提高显示面板的显示效果。

45.请参阅图5,图5为本技术实施例提供的阵列基板的第四结构示意图。如图5所示,在本技术实施例提供的阵列基板10中,第二子时钟信号线1032的长度l2沿着第一方向x越来越小,第二子时钟信号线1032的宽度d2沿着第一方向x越来越小。

46.其中,需要说明的是,对于信号线来说,信号线的长度以及宽度均会影响信号线的阻值,其中,信号线的长度与信号线的阻值成正比,信号线的宽度与信号线的阻值成反比。虽然第二子时钟信号线1032的长度l2沿着第一方向x越来越小,但是第二子时钟信号线1032的宽度d2沿着第一方向x越来越小,因此本技术实施例提供的阵列基板10可以使每条第二子时钟信号线1032的阻值相等,从而避免显示面板出现水平线现象,进而提高显示面板的显示效果。

47.请参阅图6,图6为本技术实施例提供的阵列基板的第五结构示意图。如图6所示,

在本技术实施例提供的阵列基板10中,第二子时钟信号线1032的长度l2沿着第一方向x不变,第二子时钟信号线1032的宽度d2沿着第一方向x不变。

48.其中,需要说明的是,由于时钟信号线103与连接线102的连接处为第一时钟信号线1031与第二时钟信号线1032的交接处,因此第二子时钟信号线1032的长度不会影响到时钟信号线103与连接线102的连接。因此,第二子时钟信号线1032的长度l2可以沿着第一方向x不发生改变。

49.其中。对于信号线来说,信号线的长度以及宽度均会影响信号线的阻值,其中,信号线的长度与信号线的阻值成正比,信号线的宽度与信号线的阻值成反比。由于第二子时钟信号线1032的长度l2沿着第一方向x不发生改变,那么当第二子时钟信号线1032的宽度d2沿着第一方向x也不发生改变时,可以满足每条第二子时钟信号线1032的阻值相等。因此本技术实施例提供的阵列基板10可以使每条第二子时钟信号线1032的阻值相等,从而避免显示面板出现水平线现象,进而提高显示面板的显示效果。

50.请参阅图7,图7为本技术实施例提供的阵列基板的第六结构示意图。如图7所示,在本技术实施例提供的阵列基板10中,第二子时钟信号线1032的长度l2沿着第一方向x越来越大,每条第二子时钟信号线1032上均设置有第二挖空部1032a,且第二子时钟信号线1032上的第二挖空部1032a的个数沿着第一方向x越来越多。

51.其中,需要说明的是,对于信号线来说,信号线的长度会影响信号线的阻值,其中,信号线的长度与信号线的阻值成正比。其中,第二子时钟信号线1032的长度l1沿着第一方向x越来越大,从而使第二子时钟信号线1032的阻值沿着第一方向x越来越大。

52.另外,第二子时钟信号线1032上设置有第二挖空部1032a,第二挖空部1032a可以降低第二子时钟信号线1032的阻值,第二挖空部1032a设置的个数越多,能够降低第二子时钟信号线1032的阻值越多。因此本技术实施例通过在每条第二子时钟信号线1032上均设置有第二挖空部1032a,且第二子时钟信号线1032上的第二挖空部1032a的个数沿着第一方向x越来越多,可以避免由于第二子时钟信号线1032的长度l2沿着第一方向x越来越大,而导致第二子时钟信号线1032的阻值沿着第一方向x越来越大,从而能够使每条第二子时钟信号线1032的阻值相等。

53.因此,本技术实施例提供的阵列基板10可以使每条第二子时钟信号线1032的阻值相等,从而避免显示面板出现水平线现象,进而提高显示面板的显示效果。

54.请参阅图8,图8为本技术实施例提供的阵列基板的第七结构示意图。图8所示的阵列基板10与图1所示的阵列基板10的区别在于:每条时钟信号线103均与多条连接线102连接。每条时钟信号线103均包括多条第三子时钟信号线1033。多条第三子时钟信号线1033依次连接,且第三子时钟信号线1033与第一子时钟信号线1031连接,第三子时钟信号线1033与第二子时钟线1032连接。第三子时钟信号线1033与第一子时钟信号线1031的交接处为时钟信号线103与连接线102的连接处。相邻的两条第三子时钟信号线1033的交接处为时钟信号线103与连接线102的连接处。第三子时钟信号线1033与第二子时钟信号线1032的交接处为时钟信号线103与连接线102的连接处;在同一条时钟信号线103上,每个第三子时钟信号线1033的阻值相等。

55.其中,时钟信号线103上的多个第三子时钟信号线1033的阻值之和相等。需要说明的是,当时钟信号线103上的多个第三子时钟信号线1033的阻值之和相等时,每个时钟信号

线103的阻值相同,且每个第一子时钟信号线1031分到的电压值也是相同的,从而使时钟信号线103经连接线102传输至goa电路101的时钟信号的电流值以及电压值均一致,进而避免显示面板出现水平线现象,有助于提高显示面板的显示效果。

56.其中,在一种实施方式中,在同一条时钟信号线103上,每个第三子时钟信号线1033的阻值相等。需要说明的是,连接线102分为多组,每组连接线102均从离goa电路101距离最长的时钟信号线103至离goa电路101距离最短的时钟信号线沿第二方向y依次连接。因此,为了满足时钟信号线103经每条连接线102传输至goa电路101的电压值相同,需要使每条时钟信号线103上对应的第三子时钟信号线1033阻值相同,因此需要限定每个第三子时钟信号线1033的阻值相同,从而保证时钟信号线103经每条连接线102传输至goa电路101的电压值相同,进而避免显示面板出现水平线现象,有助于提高显示面板的显示效果。

57.在本技术实施例提供的阵列基板中,包括goa电路、多条连接线以及多条时钟信号线,其中,时钟信号线在连接线与时钟信号线的交接处被分为两段,即时钟信号线被分为相互连接的第一子时钟信号线以及第二子时钟信号线。通过使每条第一子时钟信号线的阻值均相等,且使每条第二子时钟信号线的阻值均相等,可以保证每条时钟信号线传输的电流值以及电压值均相等,从而可以避免显示面板出现水平线现象,有利于提高显示面板的显示效果。

58.本技术实施例还提供一种显示面板。请参阅图9,图9为本技术实施例提供的显示面板的结构示意图。如图9所示,本技术实施例提供的显示面板100包括阵列基板10以及彩膜基板20。阵列基板10以及彩膜基板20相对设置。其中,阵列基板10具体可参照以上对该阵列基板的描述,在此不做赘述。

59.在本技术实施例提供的显示面板中,包括goa电路、多条连接线以及多条时钟信号线,其中,时钟信号线在连接线与时钟信号线的交接处被分为两段,即时钟信号线被分为相互连接的第一子时钟信号线以及第二子时钟信号线。通过使每条第一子时钟信号线的阻值均相等,且使每条第二子时钟信号线的阻值均相等,可以保证每条时钟信号线传输的电流值以及电压值均相等,从而可以避免显示面板出现水平线现象,有利于提高显示面板的显示效果。

60.以上对本技术实施例所提供的一种阵列基板及显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。