用于低频驱动和低功率驱动的显示系统和显示控制方法

1.本技术要求于2020年10月12日在韩国知识产权局(kipo)提交的第10-2020-0130886号韩国专利申请以及于2020年12月11日在韩国知识产权局(kipo)提交的第10-2020-0173549号韩国专利申请的优先权,所述韩国专利申请的内容通过引用全部包含于此。

技术领域

2.示例实施例总体涉及半导体集成电路,更具体地,涉及用于低频驱动和低功率驱动的显示系统以及由显示系统执行的显示控制方法。

背景技术:

3.随着信息技术的发展,显示装置对于向用户提供信息变得重要。各种显示装置(诸如,液晶显示器(lcd)、等离子体显示器和电致发光显示器)已经变得流行。其中,使用通过电子和空穴的复合而发光的发光二极管(led)或有机发光二极管(oled)的电致发光显示器具有快的响应速度和降低的功耗。近来,已经研究了能够以低频驱动的显示面板和显示装置,并且已经研究了用于以低频驱动和/或控制显示面板和显示装置的各种方法。

技术实现要素:

4.本公开的至少一个示例实施例提供一种在没有包括在显示驱动器集成电路中的帧缓冲器的情况下能够有效地实现低频驱动和低功率驱动的显示系统。

5.本公开的至少一个示例实施例提供一种由显示系统执行的显示控制方法。

6.根据一些示例实施例,显示系统可包括主机处理器和显示驱动器集成电路。主机处理器可被配置为:生成在高电平与低电平之间周期性摆动的时钟信号,基于时钟信号生成并输出第一同步信号,通过测量显示面板的帧更新周期来生成唤醒中断,通过基于唤醒中断启用图像提供路径来基于第一同步信号生成帧数据,并且针对每个帧更新周期输出帧数据。显示驱动器集成电路可从主机处理器接收第一同步信号和帧数据,并且控制显示面板,使得在不存储帧数据的情况下,基于第一同步信号在显示面板上显示与帧数据对应的帧图像。

7.根据一些示例实施例,显示系统可包括显示驱动器集成电路和主机处理器。显示驱动器集成电路可被配置为:控制显示面板,并且生成并输出第一同步信号。主机处理器可被配置为:从显示驱动器集成电路接收第一同步信号,通过测量显示面板的帧更新周期来生成唤醒中断,通过基于唤醒中断启用图像提供路径来基于第一同步信号生成帧数据,并且针对每个帧更新周期输出帧数据。显示驱动器集成电路可从主机处理器接收帧数据,并且控制显示面板,使得在不存储帧数据的情况下,基于第一同步信号在显示面板上显示与帧数据对应的帧图像。

8.根据一些示例实施例,一种显示系统可包括时钟源、唤醒定时器、控制/状态寄存器、时序生成器、延迟单元、图像处理单元和视频定时器。时钟源可被配置为:生成在高电平

与低电平之间周期性摆动的时钟信号。唤醒定时器可被配置为测量显示面板的帧更新周期。控制/状态寄存器可被配置为基于来自唤醒定时器的测量结果生成唤醒中断。时序生成器可被配置为基于时钟信号生成第一同步信号以将第一同步信号输出到显示驱动器集成电路,或者从显示驱动器集成电路接收第二同步信号,并且基于时钟信号以及第一同步信号和第二同步信号之一生成第一垂直同步信号和第一水平同步信号。延迟单元可被配置为对第一同步信号或第二同步信号进行延迟。图像处理单元可被配置为基于唤醒中断被启用,并且生成帧数据。视频定时器可被配置为基于第一垂直同步信号和第一水平同步信号控制帧数据的时序,并且输出帧数据。第一同步信号和第二同步信号可通过第一通道被输出或接收,并且帧数据可通过与第一通道不同的第二通道被输出。唤醒定时器、控制/状态寄存器和时序生成器可处于始终被启用的第一电源域。图像处理单元和视频定时器可处于与第一电源域不同的第二电源域,并且可被配置为基于唤醒中断选择性地被启用。显示系统可被配置为在第一操作模式下或第二操作模式下选择性地操作,在第一操作模式下,第一同步信号在时序生成器中被生成,在第二操作模式下,第二同步信号从显示驱动器集成电路被接收。

9.根据一些示例实施例,一种显示控制方法可包括:由主机处理器基于在高电平与低电平之间周期性地摆动的时钟信号来生成并输出第一同步信号;由主机处理器通过测量显示面板的帧更新周期来生成唤醒中断;由主机处理器通过基于唤醒中断启用图像提供路径来基于第一同步信号生成帧数据;由主机处理器针对每个帧更新周期输出帧数据;由显示驱动器集成电路从主机处理器接收第一同步信号和帧数据;以及由显示驱动器集成电路控制显示面板,使得在不存储帧数据的情况下,基于第一同步信号在显示面板上显示与帧数据对应的帧图像。

10.根据一些示例实施例,一种显示控制方法可包括:由显示驱动器集成电路生成并输出第一同步信号;由主机处理器从显示驱动器集成电路接收第一同步信号;由主机处理器通过测量显示面板的帧更新周期来生成唤醒中断;由主机处理器通过基于唤醒中断启用图像提供路径来基于第一同步信号生成帧数据;由主机处理器针对每个帧更新周期输出帧数据;由显示驱动器集成电路从主机处理器接收帧数据;以及由显示驱动器集成电路控制显示面板,使得在不存储帧数据的情况下,基于第一同步信号在显示面板上显示与帧数据对应的帧图像。

11.在根据一些示例实施例的显示系统和显示控制方法中,显示驱动器集成电路310a可被实现为不包括帧缓冲器。例如,主机处理器可测量显示面板的帧更新周期,可在需要帧更新或面板更新时启用图像提供路径,并且可基于显示面板的发光时间将新帧发送到显示驱动器集成电路。此外,用于在主机处理器与显示驱动器集成电路之间的同步的信号可从主机处理器和显示驱动器集成电路中的一个被生成,并且可被提供给主机处理器和显示驱动器集成电路中的另一个。因此,可有效地实现低频驱动和低功率驱动。

附图说明

12.从下面结合附图的详细描述,将更清楚地理解说明性的非限制性示例实施例。

13.图1是示出根据示例实施例的显示系统的框图。

14.图2是示出图1的显示系统的示例的框图。

15.图3是用于描述包括在图2的显示系统中的主机处理器的电源域的示图。

16.图4、图5和图6是示出包括在图2的显示系统中的主机处理器中包括的视频模式控制器的示例的框图。

17.图7和图8是示出包括在图2的显示系统中的主机处理器中包括的显示控制器的示例的框图。

18.图9是示出根据示例实施例的包括在显示系统中的显示装置的框图。

19.图10是示出包括在图9的显示装置中的显示面板中包括的像素的示例的电路图。

20.图11a、图11b、图11c、图11d、图12a、图12b、图12c和图12d是用于描述包括在图1的显示系统中的显示装置的操作的示图。

21.图13是示出根据示例实施例的显示系统的框图。

22.图14是示出图13的显示系统的示例的框图。

23.图15是示出包括在图14的显示系统中的主机处理器中包括的视频模式控制器的示例的框图。

24.图16是示出根据示例实施例的显示系统的框图。

25.图17是示出图16的显示系统的示例的框图。

26.图18是示出包括在图17的显示系统中的主机处理器中包括的视频模式控制器的示例的框图。

27.图19是示出根据示例实施例的显示控制方法的流程图。

28.图20是示出图19中的步骤s310和步骤s410的示例的流程图。

29.图21是示出根据示例实施例的显示控制方法的流程图。

30.图22是示出根据示例实施例的包括显示系统的电子系统的框图。

具体实施方式

31.将参照示出一些示例实施例的附图更全面地描述各种示例实施例。然而,本公开可以以许多不同的形式实施,并且不应被解释为限于在此阐述的公开的示例实施例。贯穿本技术,相同的参考标号表示相同的元件。

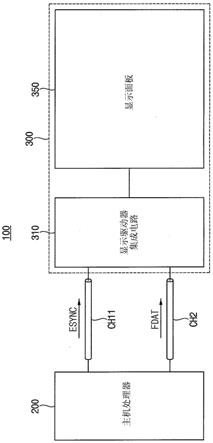

32.图1是示出根据示例实施例的显示系统的框图。

33.参照图1,显示系统100包括主机处理器200和显示装置300。显示装置300包括显示驱动器集成(ddi)电路310和显示面板350。显示系统100还可包括第一通道ch11和第二通道ch2。

34.主机处理器200生成始终被切换的时钟信号,并且基于时钟信号生成并输出第一同步信号esync。主机处理器200通过测量显示面板350的帧更新周期(period,或时段)来生成唤醒中断,通过基于唤醒中断启用图像提供路径来基于第一同步信号esync生成帧数据fdat,并且针对每个(或各个)帧更新周期输出帧数据fdat。

35.在一些示例实施例中,主机处理器200可以以应用处理器(ap)的形式实现。图1的示例可被称为以ap为中心的接口(或者,以主机为中心的接口),其中,主机处理器200生成第一同步信号esync。将参照图2和下面的附图描述主机处理器200的详细配置和操作。

36.显示驱动器集成电路310从主机处理器200接收第一同步信号esync和帧数据fdat,并且控制显示面板350,使得:在不存储帧数据fdat的情况下,与帧数据fdat对应的帧

图像基于第一同步信号esync在显示面板350上被显示。显示驱动器集成电路310可被实现为不包括存储帧数据fdat的帧缓冲器(例如,图形随机存取存储器(gram))。将参照图2和下面的附图描述显示驱动器集成电路310的详细配置和操作。

37.在一些示例实施例中,第一同步信号esync可通过第一通道ch11从主机处理器200发送到显示驱动器集成电路310,并且帧数据fdat可通过与第一通道ch11不同的第二通道ch2从主机处理器200发送到显示驱动器集成电路310。换句话说,用于发送第一同步信号esync的第一通道ch11和用于发送帧数据fdat的第二通道ch2可单独地、独立地和/或分开地形成。

38.在一些示例实施例中,第二通道ch2可基于各种显示接口标准之一(例如,移动工业处理器接口(mipi)、高清晰度多媒体接口(hdmi)、显示端口(dp)、低功率显示端口(lpdp)和高级低功率显示端口(alpdp)之一)来实现。

39.显示面板350可基于显示驱动器集成电路310的控制或在显示驱动器集成电路310的控制下显示帧图像。

40.在一些示例实施例中,显示面板350可具有相对良好(或极好、卓越、突出)的保持特性。例如,显示面板350可以是基于氧化物的有机发光显示面板。例如,显示面板350可利用单次更新将图像保持最多约一秒,因此即使显示驱动器集成电路310不包括帧缓冲器,也可以以相对低的频率驱动显示面板350,从而降低功耗。将参照图9和下面的附图描述显示面板350和包括显示面板350的显示装置300的详细配置和操作。

41.在下文中,将基于这样的示例来详细描述一些示例实施例:在该示例中,第二通道ch2基于mipi标准被实现。然而,示例实施例不限于此,并且可应用或采用于第二通道ch2基于各种其他显示接口标准中之一被实现的各种示例。

42.图2是示出图1的显示系统的示例的框图。

43.参照图2,显示系统100a包括主机处理器200a和显示驱动器集成电路310a。显示系统100a还可包括第一通道ch11和第二通道ch2。为了便于说明,省略了图1中的显示面板350。

44.主机处理器200a可包括视频模式控制器210和显示控制器230。主机处理器200a还可包括第一引脚205、数据处理单元220、时钟源(例如,时钟生成器)240和发送器(tx)250。

45.时钟源240可生成始终被切换(例如,在高电平与低电平之间有规律地或周期性地摆动)的时钟信号clk。例如,在主机处理器200a中,时钟信号clk可用于驱动各种组件并生成各种信号。例如,时钟源240可包括环形振荡器、rc振荡器、晶体振荡器或温度补偿晶体振荡器(tcxo),但是示例实施例不限于此。

46.视频模式控制器210可基于时钟信号clk生成第一同步信号esync,可通过测量显示面板350的帧更新周期来生成唤醒中断wirq,并且可基于时钟信号clk、第一同步信号esync和唤醒中断wirq来生成第一垂直同步信号vsync1和第一水平同步信号hsync1。将参照图4、图5和图6描述视频模式控制器210的详细配置。

47.视频模式控制器210可始终处于启用状态(例如,可始终被启用)。例如,即使主机处理器200a不生成并输出帧数据fdat并且进入空闲模式,视频模式控制器210也可始终保持活动模式而不进入空闲模式。空闲模式可被称为睡眠模式、待机模式、断电模式、省电模式等。

48.第一同步信号esync可以是用于主机处理器200a与显示驱动器集成电路310a之间的同步的信号。例如,第一同步信号esync可对应于在显示装置300中使用的水平同步信号。例如,为了最小化或防止由于水平同步信号的轻微偏斜(或差异)而引起的闪烁,并且为了最小化或防止水平同步信号由于时钟变化而偏离(diverge),主机处理器200a可生成由主机处理器200a和显示驱动器集成电路310a共同使用的第一同步信号esync,并且可与显示驱动器集成电路310a共享第一同步信号esync。例如,不管帧数据fdat的发送如何(例如,即使在不发送帧数据fdat时),第一同步信号esync可始终和/或连续地生成并提供给显示驱动器集成电路310a。

49.第一垂直同步信号vsync1和第一水平同步信号hsync1可以是主机处理器200a内部的用于控制和/或调整帧数据fdat的时序的信号。

50.数据处理单元220可控制主机处理器200a的整体操作,并且可提供用于生成帧数据fdat的原始数据rdat。例如,数据处理单元220可包括中央处理器(cpu)等。

51.显示控制器230可控制显示装置300和显示驱动器集成电路310a的操作,并且可基于第一垂直同步信号vsync1、第一水平同步信号hsync1、第一同步信号esync和原始数据rdat生成并输出帧数据fdat。例如,可以以包(packet)的形式生成并输出帧数据fdat。显示控制器230可被称为显示处理器(dpu)。将参照图7和图8描述显示控制器230的详细配置。

52.可基于唤醒中断wirq选择性地启用(或激活)数据处理单元220和显示控制器230。例如,当帧数据fdat的生成和输出不被期望时,数据处理单元220和显示控制器230可进入空闲模式。当帧数据fdat的生成和输出被期望时,数据处理单元220和显示控制器230的工作模式可基于唤醒中断wirq而从空闲模式切换(或改变)为活动模式。数据处理单元220提供原始数据rdat的路径和显示控制器230生成并输出帧数据fdat的路径可对应于参照图1描述的图像提供路径,图像提供路径包括在主机处理器200a中并且基于唤醒中断wirq被启用。

53.第一引脚205可连接到将第一同步信号esync发送到显示驱动器集成电路310a的第一通道ch11。例如,引脚可以是接触引脚或接触垫,但是示例实施例不限于此。

54.发送器250可连接到将帧数据fdat发送到显示驱动器集成电路310a的第二通道ch2。例如,发送器250可基于mipi标准来实现。

55.尽管未在图2中示出,但是主机处理器200a还可包括系统总线、存储器装置、存储装置、多个功能模块和电源管理集成电路(pmic)。系统总线可对应于主机处理器200a中的组件之间的信号传输路径。存储器装置和存储装置可存储用于主机处理器200a的操作的指令和数据。多个功能模块可执行主机处理器200a的各种功能。电源管理集成电路可将操作电压提供给主机处理器200a中的组件,并且可控制空闲模式与活动模式之间的上述切换操作。

56.在一些示例实施例中,存储器装置可包括易失性存储器装置(诸如,动态随机存取存储器(dram)、静态随机存取存储器(sram)、移动dram等)。在一些示例实施例中,存储装置可包括非易失性存储器装置(诸如,可擦除可编程只读存储器(eprom)、电可擦除可编程只读存储器(eeprom)、闪存、相变随机存取存储器(pram)、电阻随机存取存储器(rram)、纳米浮栅存储器(nfgm)、聚合物随机存取存储器(poram)、磁性随机存取存储器(mram)、铁电随机存取存储器(fram)等。在一些示例实施例中,存储装置还可包括嵌入式多媒体卡(emmc)、

通用闪存(ufs)、固态驱动器(ssd)、硬盘驱动器(hdd)、cd-rom等。

57.在一些示例实施例中,多个功能模块可包括执行通信功能的通信模块(例如,码分多址(cdma)模块、长期演进(lte)模块、射频(rf)模块、超宽带(uwb)模块、无线局域网(wlan)模块、全球微波接入互操作性(wimax)模块等)、执行相机功能的相机模块、包括执行显示功能的显示模块和执行触摸感测功能的触摸面板模块的输入输出(i/o)模块、以及执行音频信号的i/o的包括麦克风(mic)模块、扬声器模块等的音频模块。在一些示例实施例中,多个功能模块还可包括全球定位系统(gps)模块、陀螺仪模块等。

58.显示驱动器集成电路310a可包括时序控制器330和行/列驱动器340,并且可不包括帧缓冲器(例如,gram)。显示驱动器集成电路310a还可包括第二引脚305和接收器(rx)320。

59.第二引脚305可连接到接收从主机处理器200a提供的第一同步信号esync的第一通道ch11。例如,第二引脚305可与第一引脚205类似地实现。

60.接收器320可连接到接收从主机处理器200a提供的帧数据fdat的第二通道ch2。例如,接收器320可基于mipi标准来实现。

61.在不存储帧数据fdat的情况下,时序控制器330可基于第一同步信号esync和帧数据fdat生成第一控制信号cs1、第二控制信号cs2和数据信号ds。

62.行/列驱动器340可基于第一控制信号cs1、第二控制信号cs2和数据信号ds生成提供给显示面板350的多个数据电压(例如,图10中的数据电压vdat)和多个扫描信号(例如,图10中的扫描信号ssc)。显示面板350可基于多个数据电压和多个扫描信号来显示与帧数据fdat对应的帧图像。

63.如上所述,显示驱动器集成电路310a可不包括帧缓冲器,因此,时序控制器330和行/列驱动器340的上述操作(例如,控制显示面板350显示帧图像的操作)可在不存储帧数据fdat的情况下被执行。将参照图9和图10描述包括显示驱动器集成电路310a的显示装置的详细配置。

64.第一通道ch11可包括将第一引脚205与第二引脚305电连接的单条导线。例如,第一通道ch11可表示可发送第一同步信号esync的单向信号线或双向信号线。

65.第二通道ch2可包括将发送器250与接收器320电连接的多条导线。例如,第二通道ch2可表示可传输数字流(例如,比特序列)的双向数字接口。

66.在一些示例实施例中,可在mipi标准的视频模式期间执行发送第一同步信号esync和帧数据fdat的操作,但是示例实施例不限于此。

67.在根据一些示例实施例的显示系统100a中,显示驱动器集成电路310a可被实现为不包括帧缓冲器。例如,主机处理器200a可测量显示面板350的帧更新周期,可在帧更新或面板更新被期望时启用图像提供路径,并且可基于显示面板350的发光时间将新帧发送到显示驱动器集成电路310a。此外,因为显示驱动器集成电路310a不包括帧缓冲器,所以可仅将一个帧发送到显示驱动器集成电路310a。此外,主机处理器200a可通过第一通道ch11提供用于与显示驱动器集成电路310a同步的第一同步信号esync,第一通道ch11与用于发送帧数据fdat的第二通道ch2分开和/或独立地形成。因此,可有效地实现低频驱动和低功率驱动。

68.图3是用于描述包括在图2的显示系统中的主机处理器的电源域的示图。

69.参照图2和图3,主机处理器200a(例如,应用处理器)可包括彼此不同的多个电源域10和20。例如,多个电源域10和20可包括第一电源域10和第二电源域20。例如,第一电源域10可对应于始终供电域(always-powered domain),在始终供电域中,电力在主机处理器200a的活动模式和空闲模式两者中均被供应,并且第二电源域20可对应于省电域(power-save domain),在省电域中,电力在主机处理器200a的空闲模式下被阻止。

70.根据一些示例实施例,活动模式可表示主机处理器200a被启用并且操作系统(os)运行。空闲模式可表示主机处理器200a的至少一部分被禁用的掉电模式(power down mode)。

71.在一些示例实施例中,如图3中所示,视频模式控制器210可设置在第一电源域10中,并且数据处理单元220和显示控制器230可包括在第二电源域20中。如上所述,视频模式控制器210可生成唤醒中断wirq,并且数据处理单元220和显示控制器230可基于唤醒中断wirq选择性地被启用。

72.例如,数据处理单元220和显示控制器230可分别包括电源选通电路pg1和pg2。电源选通电路pg1和电源选通电路pg2可响应于唤醒中断wirq而选择性地分别向数据处理单元220和显示控制器230供应电力。这样,数据处理单元220和显示控制器230可彼此独立地被电源选通和启用。

73.图4、图5和图6是示出包括在图2的显示系统中的主机处理器中包括的视频模式控制器的示例的框图。

74.参照图4,视频模式控制器210a可包括唤醒定时器213、控制/状态寄存器214和时序生成器216。视频模式控制器210a还可包括延迟单元218。

75.唤醒定时器213可测量显示面板350的帧更新周期,并且可输出测量结果mr。换句话说,唤醒定时器213可测量显示面板350将被刷新的时间(例如,面板放电时间)。

76.在一些示例实施例中,由唤醒定时器213测量的帧更新周期可与显示面板350的保持特性相关联或有关。例如,当显示面板350的最小驱动频率是大约1hz时(例如,当显示面板350可利用单次更新将图像保持最多大约一秒时),唤醒定时器213可测量作为与最小驱动频率对应的时间的大约一秒。

77.控制/状态寄存器214可基于从唤醒定时器213提供的测量结果mr来生成唤醒中断wirq。例如,控制/状态寄存器214可包括特殊功能寄存器(sfr)。控制/状态寄存器214可被称为中断控制器。

78.时序生成器216可基于时钟信号clk生成第一同步信号esync,并且延迟单元218可对第一同步信号esync进行延迟并输出。例如,时序生成器216可生成与第一同步信号esync对应的信号esync',并且延迟单元218可对信号esync'进行延迟,并且可输出延迟的信号作为第一同步信号esync。如上所述,第一同步信号esync可以是用于主机处理器200a与显示驱动器集成电路310a之间的同步的信号,因此,第一同步信号esync可始终被切换并且可始终保持活动状态。例如,延迟单元218可包括用于匹配第一同步信号esync与通过串行接口从显示控制器230输出的同步信号之间的偏斜的延迟元件。

79.时序生成器216可基于测量结果mr、时钟信号clk和第一同步信号esync生成第一垂直同步信号vsync1和第一水平同步信号hsync1。例如,当唤醒中断wirq被生成或发出时,时序生成器216可生成第一垂直同步信号vsync1和第一水平同步信号hsync1并将第一垂直

同步信号vsync1和第一水平同步信号hsync1提供给显示控制器230。如上所述,第一垂直同步信号vsync1和第一水平同步信号hsync1可以是主机处理器200a内部的用于控制和/或调整帧数据fdat的时序的信号,因此,第一垂直同步信号vsync1和第一水平同步信号hsync1可仅在显示控制器230被启用时生成。第一垂直同步信号vsync1和第一水平同步信号hsync1可被称为视频同步信号。

80.换句话说,唤醒定时器213可以是测量显示面板350将被刷新的时间的组件,以便提前识别何时期望面板更新。控制/状态寄存器214可以是在期望时唤醒显示系统100a并且控制将待显示的帧发送到显示面板350的操作的组件。时序生成器216可以是生成用于主机处理器200a与显示驱动器集成电路310a之间的同步的信号的组件。

81.参照图5,视频模式控制器210b可包括唤醒定时器213b、控制/状态寄存器214和时序生成器216。视频模式控制器210b还可包括延迟单元218。将省略结合图4提到的描述。

82.除了主机处理器200a还包括模式选择器260并且唤醒定时器213b的操作被部分地改变之外,视频模式控制器210b可与图4的视频模式控制器210a基本相同。

83.模式选择器260可设置显示面板350的帧更新周期,并且可输出帧设置信息fri。例如,模式选择器260可基于帧图像的类型、应用的类型、用户的设置等,将帧更新周期设置在从显示面板350的最小驱动频率到可设置的最大驱动频率的范围内。例如,帧更新周期可被设置为作为正常驱动频率的大约60hz,可被设置为作为低于正常驱动频率的大约10hz,或者可被设置为作为最小驱动频率的大约1hz。

84.唤醒定时器213b可基于从模式选择器260提供的帧设置信息fri来测量由模式选择器260设置的显示面板350的帧更新周期,并且可输出测量结果mr。

85.参照图6,视频模式控制器210c可包括控制/状态寄存器214c和时序生成器216c。视频模式控制器210c还可包括延迟单元218。将省略结合图4提到的描述。

86.除了主机处理器200a还包括全局定时器270并且唤醒定时器213被省略,控制/状态寄存器214c和时序生成器216c的操作被部分地改变之外,视频模式控制器210c可与图4的视频模式控制器210a基本相同。

87.全局定时器270可生成时间信息tm并且可将时间信息tm提供给整个主机处理器200a。例如,可将时间信息tm提供给控制/状态寄存器214c和时序生成器216c。全局定时器270可被称为系统定时器。

88.控制/状态寄存器214c可基于从全局定时器270提供的时间信息tm来生成唤醒中断wirq。

89.时序生成器216c可基于时间信息tm、时钟信号clk和第一同步信号esync来生成第一垂直同步信号vsync1和第一水平同步信号hsync1。

90.图7和图8是示出包括在图2的显示系统中的主机处理器中包括的显示控制器的示例的框图。

91.参照图7,显示控制器230a可包括图像处理单元232和视频定时器234。

92.图像处理单元232可基于唤醒中断wirq而选择性地被启用,并且可在被启用时基于从数据处理单元220提供的原始数据rdat而生成帧数据fdat。例如,图像处理单元232可生成与帧数据fdat对应的数据fdat'。

93.在一些示例实施例中,尽管未详细示出,但是图像处理单元232可包括混合器

(blender)和显示质量增强器,混合器用于混合多个层,显示质量增强器用于执行至少一个显示质量增强算法(或图像质量改善算法)。

94.混合表示计算在构成一个屏幕的若干层(例如,图像)之中实际显示的像素值的操作。当混合被执行时,可以获得实际显示在每个像素上的像素值。例如,当仅一个层设置、布置或放置在像素上时,可原样获得包括在一个层中的像素值。当两个或更多个层设置在像素上时,可获得包括在两个或更多个层之中的一个层中的像素值,或者可基于包括在两个或更多个层中的像素值获得新的像素值。混合可被称为融合和/或复合。

95.在一些示例实施例中,至少一个显示质量增强算法可包括细节增强(de)、缩放(或缩放器)、适应性色调图控制(atc)、色调饱和度控制(hsc)、伽马和去伽马、安卓开源项目(aosp)、色域控制(cgc)、抖动(或抖动器)、圆角显示(rcd)、子像素渲染(spr)等。de可表示用于锐化图像的轮廓的算法。缩放可表示改变图像的大小的算法。atc可表示用于改善室外能见度的算法。hsc可表示用于改善颜色的色调和饱和度的算法。伽马可表示用于伽马校正或补偿的算法。aosp可表示用于处理由安卓os定义的图像转换矩阵(例如,用于颜色受损的人的模式或夜间模式)的算法。cgc可表示用于匹配显示面板的颜色坐标的算法。抖动可表示用于使用有限颜色来表示高比特的颜色的效果的算法。rcd可表示用于处理显示面板的圆角的算法。spr可表示用于提高分辨率的算法。然而,示例实施例不限于此,并且至少一个显示质量增强算法还可包括各种其他算法。

96.视频定时器234可基于第一垂直同步信号vsync1、第一水平同步信号hsync1和第一同步信号esync来控制帧数据fdat的时序。例如,视频定时器234可通过调整数据fdat'的时序来输出帧数据fdat。

97.换句话说,视频定时器234可以是基于显示面板350的发光时间开始新帧、仅发送一帧并且基于同步信号生成时序信息的组件。例如,视频定时器234可在视频模式下仅发送一帧,并且可通过显示器串行接口(dsi)生成时序信息。

98.参照图8,显示控制器230b可包括图像处理单元232和视频定时器234。显示控制器230b还可包括视频模式控制器210。将省略结合图7提到的描述。

99.除了视频模式控制器210被包括和/或设置在显示控制器230b中之外,显示控制器230b可与图7的显示控制器230a基本相同。视频模式控制器210可如参照图4、图5和图6所描述的那样实现。

100.图9是示出根据示例实施例的包括在显示系统中的显示装置的框图。

101.参照图9,显示装置700包括显示面板710和显示驱动器集成电路。显示驱动器集成电路可包括数据驱动器720、扫描驱动器730、电源740和时序控制器750。

102.显示面板710基于图像数据(例如,基于帧数据)进行操作(例如,显示图像)。显示面板710可通过多条数据线d1、d2、

……

、dm连接到数据驱动器720,并且可通过多条扫描线s1、s2、

……

、sn连接到扫描驱动器730,其中,m和n分别是大于一的自然数。多条数据线d1、d2、

……

、dm可沿第一方向延伸,并且多条扫描线s1、s2、

……

、sn可沿与第一方向交叉(例如,基本垂直)的第二方向延伸。

103.显示面板710可包括以具有多个行和多个列的矩阵形式布置的多个像素px。如将参照图10描述的,多个像素px中的每个可包括发光元件和用于驱动发光元件的至少一个晶体管。多个像素px中的每个可电连接到多条数据线d1、d2、

……

、dm中的相应一条和多条扫

描线s1、s2、

……

、sn中的相应一条。

104.在一些示例实施例中,显示面板710可以是在不使用背光单元的情况下发光的自发光显示面板。例如,显示面板710可以是包括有机发光二极管(oled)作为发光元件的有机发光显示面板。

105.在一些示例实施例中,显示面板710可具有能够执行低频驱动的相对良好(例如,优异)的保持特性。例如,显示面板710可以是基于氧化物的有机发光显示面板,基于氧化物的有机发光显示面板包括有机发光二极管作为发光元件并且包括包含低温多晶氧化物(ltpo)的至少一个晶体管。

106.然而,示例实施例不限于此,并且显示面板710可以是包括背光单元并且能够执行低频驱动的液晶显示器(lcd)面板。

107.在一些示例实施例中,根据显示装置700的驱动方案,显示面板710中包括的多个像素px中的每个可具有各种配置。例如,显示装置700可以以模拟驱动方案或数字驱动方案被驱动。模拟驱动方案使用与输入数据对应的可变电压电平产生灰度,而数字驱动方案使用发光二极管发光的可变持续时间产生灰度。因为当显示器大并且期望高分辨率时,需要制造复杂的驱动集成电路(ic),所以模拟驱动方案难以实现。另一方面,数字驱动方案可通过更简单的ic结构容易地实现期望的高分辨率。将参照图10描述多个像素px中的每个的示例。

108.时序控制器750可控制显示装置700的整体操作。例如,时序控制器750可从主机处理器200接收第一同步信号esync,并且可基于第一同步信号esync将预定控制信号cs1、cs2和cs3提供给数据驱动器720、扫描驱动器730和电源740,以控制显示装置700的操作。例如,控制信号cs1、cs2和cs3可包括在显示装置700内部使用的垂直同步信号和水平同步信号。

109.时序控制器750可从主机处理器200接收帧数据fdat,并且基于帧数据fdat生成用于显示图像的数据信号ds。例如,帧数据fdat可包括红色图像数据、绿色图像数据和蓝色图像数据。此外,帧数据fdat可包括白色图像数据。在一些示例实施例中,帧数据fdat可包括品红色图像数据、黄色图像数据、青色图像数据等。

110.数据驱动器720可基于控制信号cs1和数据信号ds生成多个数据电压,并且可通过多条数据线d1、d2、

……

、dm将多个数据电压施加到显示面板710。例如,数据驱动器720可包括将数字形式的数据信号ds转换为模拟形式的多个数据电压的数模转换器(dac)。

111.扫描驱动器730可基于控制信号cs2生成多个扫描信号,并且可通过多条扫描线s1、s2、

……

、sn将多个扫描信号施加到显示面板710。多条扫描线s1、s2、

……

、sn可基于多个扫描信号被顺序地激活。

112.时序控制器750可对应于图2中的时序控制器330,并且数据驱动器720和扫描驱动器730可对应于图2中的行/列驱动器340。

113.在一些示例实施例中,数据驱动器720、扫描驱动器730和时序控制器750可实施为一个集成电路。在一些其他示例实施例中,数据驱动器720、扫描驱动器730和时序控制器750可实施为两个或更两个集成电路。至少包括时序控制器750和数据驱动器720的驱动模块可被称为时序控制器嵌入式数据驱动器(ted)。

114.电源740可基于控制信号cs3将第一电源电压elvdd和第二电源电压elvss提供给显示面板710。例如,第一电源电压elvdd可以是高电源电压,并且第二电源电压elvss可以

是低电源电压。

115.在一些示例实施例中,包括在显示驱动器集成电路中的元件中的至少一些可设置(例如,直接安装)在显示面板710上,或者可以以带载封装(tcp)类型连接到显示面板710。在一些示例实施例中,包括在显示驱动器集成电路中的元件中的至少一些可集成在显示面板710上。在一些示例实施例中,包括在显示驱动器集成电路中的元件可分别利用单独的电路/模块/芯片来实现。在一些其他示例实施例中,基于功能,包括在显示驱动器集成电路中的元件中的一些可组合成一个电路/模块/芯片,或可进一步分离成多个电路/模块/芯片。

116.图10是示出包括在图9的显示装置中的显示面板中包括的像素的示例的电路图。

117.参照图10,每个像素px可包括开关晶体管ts、存储电容器cst、驱动晶体管td和有机发光二极管el。

118.开关晶体管ts可具有连接到数据线di的第一电极、连接到存储电容器cst的第二电极、以及连接到扫描线sj的栅电极。开关晶体管ts可响应于从扫描驱动器730接收的扫描信号ssc,将从数据驱动器720接收的数据电压vdat传送到存储电容器cst。

119.存储电容器cst可具有连接到第一电源电压elvdd的第一电极和连接到驱动晶体管td的栅电极和开关晶体管ts的第二电极的第二电极。存储电容器cst可存储通过开关晶体管ts传送的数据电压vdat。

120.驱动晶体管td可具有连接到第一电源电压elvdd的第一电极、连接到有机发光二极管el的第二电极、以及连接到存储电容器cst的栅电极。驱动晶体管td可根据存储在存储电容器cst中的数据电压vdat而被导通或截止。

121.有机发光二极管el可具有连接到驱动晶体管td的阳极和连接到第二电源电压elvss的阴极。当驱动晶体管td导通时,有机发光二极管el可基于从第一电源电压elvdd流到第二电源电压elvss的电流而发光。像素px的亮度可随着流过有机发光二极管el的电流增大而增大。

122.在一些示例实施例中,开关晶体管ts和驱动晶体管td可包括ltpo。例如,驱动晶体管td可以是包括低温多晶硅(ltps)的ltps薄膜晶体管(tft),并且开关晶体管ts可以是包括氧化物半导体的氧化物tft。因为相对高的电子迁移率,所以ltps tft可适合于或适用于电流驱动。因为相对低的泄漏电流,所以氧化物tft可适合于或适用于开关。因此,当ltps tft和氧化物tft一起使用时,可获得改善的特性(例如,优异的保持特性)。包括ltps tft和氧化物tft两者的像素可被称为ltpo像素,并且包括ltpo像素的显示面板可被称为混合氧化物面板(hop)。

123.尽管图10示出有机发光二极管像素作为可包括在显示面板710中的每个像素px的示例,但是应当理解,示例实施例不限于有机发光二极管像素,并且可应用各种类型和配置的任何像素。

124.图11a、图11b、图11c、图11d、图12a、图12b、图12c和图12d是用于描述包括在图1的显示系统中的显示装置的操作的示图。

125.参照图11a、图11b、图11c和图11d,包括在显示装置300中的显示驱动器集成电路310可通过将一个帧间隔tf划分为多个子间隔(例如,n个子间隔,其中,n是大于或等于一的自然数)来驱动显示面板350。一个帧间隔tf可表示在显示面板350上显示一个帧图像的时间间隔。例如,n=2m,其中,m为零或者大于或等于一的自然数。

126.例如,图11a示出n=1的示例。换句话说,帧间隔tf可不被划分为子部分。在图11a和下面的附图中,加粗竖直线可指示帧间隔tf的开始点和结束点,并且可指示例如包括在垂直同步信号中的脉冲。

127.图11b示出n=2并且帧间隔tf被划分为两个子部分tsf1a和tsf2a的示例。类似地,图11c示出n=4并且帧间隔tf被划分为四个子部分tsf1b、tsf2b、tsf3b和tsf4b的示例。图11d示出n=32并且帧间隔tf被划分为32个子部分的示例。然而,示例实施例不限于此。在一些示例实施例中,n可被改变为适合于显示系统100的配置的优化值。

128.在一些示例实施例中,行/列驱动器340可在多个子间隔之中的接收到帧数据fdat之后首先出现或到达的第一子间隔中开始显示帧图像的操作。将参照图12d详细描述基于子间隔显示帧图像的操作。

129.参照图12a、图12b和图12c,显示装置300可基于各种驱动频率进行操作。

130.图12a示出显示装置300基于第一驱动频率dfreq1进行操作的示例。例如,第一驱动频率dfreq1可以是作为正常驱动频率的大约60hz。在图12a的示例中,可针对每个帧生成并提供与帧图像f1、f2、f3、f4、f5、f6、f7、f8、f9、f10、f11、f12、f13和f14对应的帧数据fdat,并且显示面板350可在每个帧期间显示帧图像f1至f14中的相应一个。换句话说,在图12a的示例中,所有帧可以是显示实际帧图像的活动帧

131.图12b示出显示装置300基于第二驱动频率dfreq2进行操作的示例。例如,第二驱动频率dfreq2可以是大约10hz。在图12b的示例中,可针对于第(6k 1)帧中的每个帧生成并提供与帧图像f1、f7和f13对应的帧数据fdat,其中,k是零或者大于或等于一的自然数,并且显示面板350可在第(6k 1)帧中的每个帧期间显示帧图像f1、f7和f13中的相应一个。在除了第(6k 1)帧之外的剩余(或余下,遗留)帧期间,可保持在先前帧中显示的帧图像而不生成并且不提供帧数据fdat,显示系统100内部的用于生成并提供帧数据fdat的组件可进入空闲模式。换句话说,在图12b的示例中,仅第(6k 1)帧可以是活动帧并且剩余帧可以是空闲帧

132.图12c示出显示装置300基于第三驱动频率dfreq3进行操作的示例。例如,第三驱动频率dfreq3可以是作为最小驱动频率的大约1hz。在图12c的示例中,可针对第(60k 1)帧中的每个帧生成并提供与帧图像f1对应的帧数据fdat,并且显示面板350可在第(60k 1)帧中的每个帧期间显示帧图像f1。在除了第(60k 1)帧之外的剩余帧期间,可保持在先前帧中显示的帧图像。换句话说,在图12c的示例中,仅第(60k 1)帧可以是活动帧并且剩余帧可以是空闲帧

133.在一些示例实施例中,图12b和图12c中的每个可表示用于显示静止图像(或静态图像、停止图像)的操作模式。

134.参照图12d,当如图12b和图12c所示执行低频驱动时,可使用图11b、图11c和图11d所示的多个子间隔来控制和/或调整新帧的起始点。

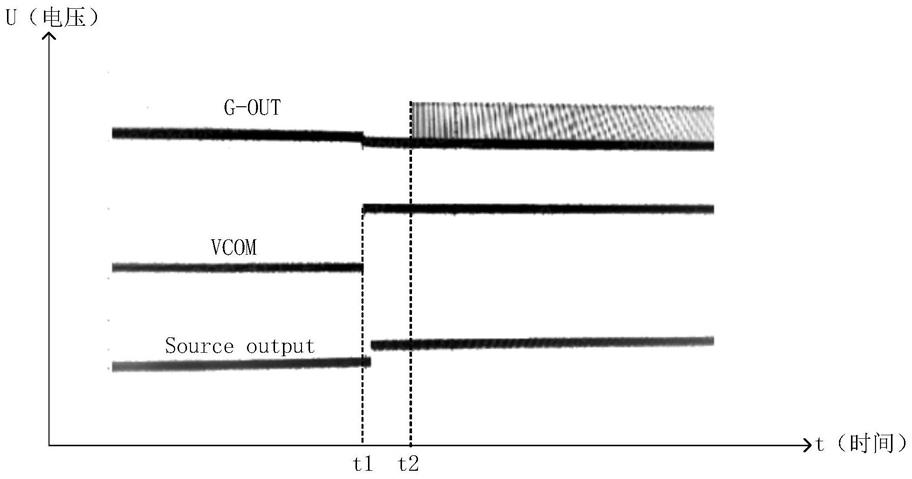

135.与图11d的示例一样,图12d示出n=32并且帧间隔tf被划分为32个子部分的示例。在图12d中,vss、hss和dat可分别表示在显示装置300中使用的垂直同步信号、水平同步信号和数据信号。

136.当控制和/或调整新帧的起始点时,可通过将显示面板350的发光时间划分为n个子间隔来提供在没有显示质量的差异的情况下开始新帧的功能。当操作模式从空闲模式切换到活动模式时(例如,当显示的帧从空闲帧改变为活动帧时),即使在当前帧的开始之后接收到有效数据valid_data,也可以不等到下一帧间隔的开始,并且新帧可在当前帧间隔中的划分的n个子间隔中的最早子间隔出现的时间开始。在图12d的示例中,可在当前帧间隔中接收到有效数据valid_data时的时间t1(例如,在三十二个子间隔之中的第三子间隔的起始点)开始新帧。在图12d中,在有效数据valid_data之前的vbp可表示后沿(back porch)间隔,并且在有效数据valid_data之后的vfp可表示前沿(front porch)间隔。

137.当根据一些示例实施例的显示系统100执行低频驱动时,可仅在活动帧中发送数据,并且即使显示驱动器集成电路310不包括帧缓冲器,显示系统100的大多数组件也可在空闲帧中切换到空闲模式。因此,可降低功耗。

138.图13是示出根据示例实施例的显示系统的框图。将省略结合图1提到的描述。

139.参照图13,显示系统101包括主机处理器201和显示装置301。显示装置301包括显示驱动器集成电路311和显示面板350。显示系统101还可包括第一通道ch12和第二通道ch2。

140.除了用于主机处理器201与显示驱动器集成电路311之间的同步的第一同步信号esync从显示驱动器集成电路311被生成并提供给主机处理器201之外,显示系统101可与图1的显示系统100基本相同。

141.显示驱动器集成电路311控制显示面板350,并且生成并输出第一同步信号esync。第一同步信号esync可与图1中的第一同步信号esync基本相同。图13的示例可被称为以ddi为中心的接口,其中,显示驱动器集成电路311生成第一同步信号esync。

142.主机处理器201从显示驱动器集成电路311接收第一同步信号esync。主机处理器201通过测量显示面板350的帧更新周期来生成唤醒中断,通过基于唤醒中断启用图像提供路径来基于第一同步信号esync生成帧数据fdat,并且针对每个帧更新周期输出帧数据fdat。

143.显示驱动器集成电路311从主机处理器201接收帧数据fdat,并且控制显示面板350,使得在不存储帧数据fdat的情况下,基于第一同步信号esync在显示面板350上显示与帧数据fdat对应的帧图像。显示驱动器集成电路311可被实现为不包括存储帧数据fdat的帧缓冲器。

144.在一些示例实施例中,第一同步信号esync可通过第一通道ch12从显示驱动器集成电路311发送到主机处理器201,并且帧数据fdat可通过与第一通道ch12不同的第二通道ch2从主机处理器201发送到显示驱动器集成电路311。

145.图14是示出图13的显示系统的示例的框图。将省略结合图2提到的描述。

146.参照图14,显示系统101a包括主机处理器201a和显示驱动器集成电路311a。显示系统101a还可包括第一通道ch12和第二通道ch2。

147.主机处理器201a可包括视频模式控制器211和显示控制器230。主机处理器200a还可包括第一引脚207、数据处理单元220、时钟源240和发送器250。

148.除了从显示驱动器集成电路311a接收第一同步信号esync并且视频模式控制器

211和第一引脚207的操作被部分地改变之外,主机处理器201a可与图2中的主机处理器200a基本相同。

149.视频模式控制器211可通过测量显示面板350的帧更新周期来生成唤醒中断wirq,并且可基于时钟信号clk、第一同步信号esync和唤醒中断wirq来生成第一垂直同步信号vsync1和第一水平同步信号hsync1。视频模式控制器211可始终具有启用状态。

150.第一引脚207可连接到接收从显示驱动器集成电路311a提供的第一同步信号esync的第一通道ch12。

151.显示驱动器集成电路311a可包括时序控制器331和行/列驱动器340,并且可不包括帧缓冲器。显示驱动器集成电路311a还可包括第二引脚307和接收器320。

152.除了显示驱动器集成电路311a生成第一同步信号esync并且时序控制器331和第二引脚307的操作被部分地改变之外,显示驱动器集成电路311a可与图2中的显示驱动器集成电路310a基本相同。

153.时序控制器331可生成第一同步信号esync,并且可在不存储帧数据fdat的情况下,基于第一同步信号esync和帧数据fdat生成第一控制信号cs1、第二控制信号cs2和数据信号ds。尽管未在图14中示出,但是显示驱动器集成电路311a还可包括时钟源,时钟源生成用于生成第一同步信号esync的时钟信号。

154.第二引脚307可连接到将第一同步信号esync发送到主机处理器201a的第一通道ch12。

155.在根据一些示例实施例的显示系统101a中,显示驱动器集成电路311a可被实现为不包括帧缓冲器。例如,主机处理器201a可测量显示面板350的帧更新周期,可在帧更新或面板更新被期望时启用图像提供路径,并且可基于显示面板350的发光时间将新帧发送到显示驱动器集成电路311a。此外,显示驱动器集成电路311a可通过第一通道ch12提供用于与主机处理器201a同步的第一同步信号esync,第一通道ch12与用于发送帧数据fdat的第二通道ch2分开和/或独立地形成。因此,可有效地实现低频驱动和低功率驱动。

156.图15是示出包括在图14的显示系统中的主机处理器中包括的视频模式控制器的示例的框图。将省略结合图4提到的描述。

157.参照图15,视频模式控制器211a可包括唤醒定时器213、控制/状态寄存器214和时序生成器215。视频模式控制器211a还可包括延迟单元219。

158.除了从显示驱动器集成电路311a接收第一同步信号esync并且时序生成器215和延迟单元219的操作被部分地改变之外,视频模式控制器211a可与图4的视频模式控制器210a基本相同。唤醒定时器213和控制/状态寄存器214可与参照图4描述的唤醒定时器和控制/状态寄存器基本相同。

159.延迟单元219可对第一同步信号esync进行延迟并将延迟的第一同步信号esync提供给时序生成器215,并且时序生成器215可基于测量结果mr、时钟信号clk和第一同步信号esync来生成第一垂直同步信号vsync1和第一水平同步信号hsync1。例如,延迟单元219可对第一同步信号esync进行延迟以生成信号esync",并且时序生成器215可接收信号esync"作为第一同步信号esync。例如,延迟单元219可包括用于匹配从显示驱动器集成电路311a接收的第一同步信号esync与通过串行接口从显示控制器230输出的同步信号之间的偏斜的延迟元件。

160.图16是示出根据示例实施例的显示系统的框图。将省略结合图1和图13提到的描述。

161.参照图16,显示系统102包括主机处理器202和显示装置302。显示装置302包括显示驱动器集成电路312和显示面板350。显示系统102还可包括第一通道ch11和ch12以及第二通道ch2。

162.除了用于主机处理器202与显示驱动器集成电路312之间的同步的同步信号包括从主机处理器202生成的第一同步信号esync1和从显示驱动器集成电路312生成的第二同步信号esync2之外,显示系统102可与图1的显示系统100基本相同。

163.第一同步信号esync1可与图1中的第一同步信号esync基本相同,并且由主机处理器202生成第一同步信号esync1的操作可与参照图1描述的操作基本相同。第二同步信号esync2可与图13中的第一同步信号esync基本相同,并且由显示驱动器集成电路312生成第二同步信号esync2的操作可与参照图13描述的操作基本相同。

164.在一些示例实施例中,显示系统102可在第一操作模式与第二操作模式中的一种模式下选择性地操作。在第一操作模式期间,显示系统102可生成第一同步信号esync1,并且可基于第一同步信号esync1进行操作。在第二操作模式期间,显示系统102可生成第二同步信号esync2,并且可基于第二同步信号esync2进行操作。如参照图1至图12所描述的,第一操作模式可被称为以ap为中心的模式,并且显示系统102可在第一操作模式下被实现并操作。如参照图13至图15所描述的,第二操作模式可被称为以ddi为中心的模式,并且显示系统102可在第二操作模式下被实现并操作。例如,在第一操作模式下,第一通道ch12和第二同步信号esync2可被禁用或去激活,并且在第二操作模式下,第一通道ch11和第一同步信号esync1可被禁用或去激活。

165.在一些示例实施例中,可省略第一通道ch11和ch12中的一个。例如,可仅使用一个第一通道,第一同步信号esync1可在第一操作模式下通过一个第一通道从主机处理器202发送到显示驱动器集成电路312,并且第二同步信号esync2可在第二操作模式下通过一个第一通道从显示驱动器集成电路312发送到主机处理器202。

166.图17是示出图16的显示系统的示例的框图。将省略结合图2和图14提到的描述。

167.参照图17,显示系统102a包括主机处理器202a和显示驱动器集成电路312a。显示系统102a还可包括第一通道ch11和ch12以及第二通道ch2。

168.主机处理器202a可包括视频模式控制器212和显示控制器230。主机处理器202a还可包括第一引脚205和207、数据处理单元220、时钟源240和发送器250。

169.除了主机处理器202a另外接收第二同步信号esync2之外,主机处理器202a可与图2中的主机处理器200a基本相同。视频模式控制器212可在第一操作模式下与图2中的视频模式控制器210类似地操作,并且可在第二操作模式下与图14中的视频模式控制器211类似地操作。

170.显示驱动器集成电路312a可包括时序控制器332和行/列驱动器340,并且可不包括帧缓冲器。显示驱动器集成电路312a还可包括第二引脚305和307以及接收器320。

171.除了显示驱动器集成电路312a另外生成第二同步信号esync2之外,显示驱动器集成电路312a可与图2中的显示驱动器集成电路310a基本相同。时序控制器332可在第一操作模式下与图2中的时序控制器330类似地操作,并且可在第二操作模式下与图14中的时序控

制器331类似地操作。

172.图18是示出包括在图17的显示系统中的主机处理器包括的视频模式控制器的示例的框图。将省略结合图4和图15提到的描述。

173.参照图18,视频模式控制器212a可包括唤醒定时器213、控制/状态寄存器214和时序生成器217。视频模式控制器212a还可包括延迟单元218和219。

174.除了视频模式控制器212a另外接收第二同步信号esync2之外,视频模式控制器212a可与图4的视频模式控制器210a基本相同。时序生成器217可在第一操作模式下与图4中的时序生成器216类似地操作,并且可在第二操作模式下与图15中的时序生成器215类似地操作。信号esync1'和esync2”可分别与图4中的信号esync'和图15中的信号esync”基本相同。

175.尽管未详细示出,但是图15中的视频模式控制器211a和图18中的视频模式控制器212a可如参照图5和图6所描述的那样被实现,图14和图17中的显示控制器230可如参照图7和图8所描述的那样被实现,并且图13中的显示装置301和图16中的显示装置302可如参照图11a、图11b、图11c、图11d、图12a、图12b、图12c和图12d所描述的那样进行操作。

176.图19是示出根据示例实施例的显示控制方法的流程图。

177.参照图1、图2和图19,在根据示例实施例的显示控制方法中,基于时钟信号clk生成并输出第一同步信号esync(步骤s110)。步骤s110可由主机处理器200执行。图19示出以ap为中心的接口(或以ap为中心的模式)中的操作。

178.通过测量显示面板350的帧更新周期来生成唤醒中断wirq(步骤s210)。步骤s210可由主机处理器200执行。例如,可如参照图4、图5和图6所描述的那样执行步骤s210。

179.通过基于唤醒中断wirq启用图像提供路径,基于第一同步信号esync生成帧数据fdat(步骤s310),并且针对每个帧更新周期输出帧数据fdat(步骤s410)。步骤s310和s410可由主机处理器200执行。将参照图20详细描述步骤s310和s410。

180.接收第一同步信号esync和帧数据fdat(步骤s510),并且控制显示面板350,使得在不存储帧数据fdat的情况下,基于第一同步信号esync在显示面板350上显示与帧数据fdat对应的帧图像(步骤s610)。步骤s510和s610可由显示驱动器集成电路310执行。例如,可如参照图11a、图11b、图11c、图11d、图12a、图12b、图12c和图12d所描述的那样执行步骤s610。

181.图20是示出图19中的步骤s310和步骤s410的示例的流程图。

182.参照图2、图19和图20,在步骤s310中,可基于唤醒中断wirq启用显示控制器230(步骤s312),可生成帧数据fdat(步骤s314),并且可生成第一垂直同步信号vsync1和第一水平同步信号hsync1(步骤s316)。在步骤s410中,可基于第一垂直同步信号vsync1和第一水平同步信号hsync1来控制帧数据fdat的时序(步骤s412)。步骤s312和s316可由视频模式控制器210执行,并且步骤s314和s412可由显示控制器230执行。例如,可如参照图4至图8所描述的那样执行步骤s312、s314、s316和s412。

183.图21是示出根据示例实施例的显示控制方法的流程图。将省略结合图19提到的描述。

184.参照图13和图21,在根据示例实施例的显示控制方法中,生成并输出第一同步信号esync(步骤s120),并且接收第一同步信号esync(步骤s130)。步骤s120可由显示驱动器

集成电路311执行,并且步骤s130可由主机处理器201执行。图21示出以ddi为中心的接口(或以ddi为中心的模式)中的操作。

185.之后,步骤s210、步骤s310和步骤s410可与参照图19描述的基本相同。之后,接收帧数据fdat(步骤s520)。步骤s520可由显示驱动器集成电路311执行。之后,步骤s610可与参照图19描述的基本相同。

186.图22是示出根据示例实施例的包括显示系统的电子系统的框图。

187.参照图22,电子系统1000可被实现为使用或支持移动工业处理器接口(mipi)的数据处理装置。电子系统1000可包括应用处理器1110、图像传感器1140、显示装置1150等。电子系统1000还可包括射频(rf)芯片1160、全球定位系统(gps)1120、存储装置1170、麦克风(mic)1180、动态随机存取存储器(dram)1185和扬声器1190。此外,电子系统1000可使用超宽带(uwb)1210、无线局域网(wlan)1220、全球微波接入互操作性(wimax)1230等来执行通信。

188.应用处理器1110可以是控制图像传感器1140和显示装置1150的操作的控制器或处理器。

189.应用处理器1110可包括与显示装置1150的显示器串行接口(dsi)装置1151执行串行通信的dsi主机1111、与图像传感器1140的相机串行接口(csi)装置1141执行串行通信的csi主机1112、基于mipi digrf(数字射频)与rf芯片1160的phy 1161执行数据通信的物理层(phy)1113、以及控制物理层1161的数据通信的digrf主设备1114。可通过digrf主设备1114来控制rf芯片1160的digrf从设备1162。

190.在一些示例实施例中,dsi主机1111可包括串行器(ser),并且dsi装置1151可包括解串器(des)。在一些示例实施例中,csi主机1112可包括解串器(des),并且csi装置1141可包括串行器(ser)。

191.根据一些示例实施例,应用处理器1110可以是主机处理器或应用处理器,dsi装置1151可以是根据一些示例实施例的显示驱动器集成电路,并且应用处理器1110和dsi装置1151可形成根据一些示例实施例的显示系统,并且可执行根据一些示例实施例的显示控制方法。

192.发明构思可应用于包括显示装置和显示系统的各种电子装置和系统。例如,发明构思可应用于系统(诸如,个人计算机(pc)、服务器计算机、数据中心、工作站、移动电话、智能电话、平板计算机、膝上型计算机、个人数字助理(pda)、便携式多媒体播放器(pmp)、数码相机、便携式游戏机、音乐播放器、摄像机、视频播放器、导航装置、可穿戴装置、物联网(iot)装置、万物联网(ioe)装置、电子书阅读器、虚拟现实(vr)装置、增强现实(ar)装置、机器人装置、无人机等)。

193.公开为黑箱的各种元件(例如,视频模式控制器、数据处理单元、显示控制器、时钟源、发送器、接收器、唤醒定时器、控制/状态寄存器、时序生成器、延迟单元、图像处理单元、视频定时器、模式选择器、全局定时器、行/列驱动器、时序控制器、扫描驱动器和数据驱动器)可以是主机处理器220a的功能单元,并且可被实现为处理电路(诸如,包括逻辑电路的硬件、或者硬件和软件的组合(诸如,执行软件的处理器))。例如,处理电路可包括但不限于中央处理器(cpu)、算术逻辑单元(alu)、数字信号处理器、微型计算机、现场可编程门阵列(fpga)、片上系统(soc)、可编程逻辑单元、微处理器、专用集成电路(asic)等。

194.前述内容是一些示例实施例的说明,并且不应被解释为其限制。尽管已经描述了一些示例实施例,但是本领域技术人员将容易理解,在实质上不脱离示例实施例的新颖性教导和优点的情况下,在示例实施例中进行许多修改是可行的。因此,所有这样的修改意在包括在如权利要求中限定的示例实施例的范围内。因此,应当理解,前述内容是各种示例性实施例的说明,并且不应被解释为限于公开的特定示例实施例,并且对公开的示例实施例的修改以及其他示例实施例意在包括在所附权利要求的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。