1.本揭露涉及一种驱动电路,尤其涉及一种用于驱动光发射单元的驱动电路以及电子装置。

背景技术:

2.对于目前的显示面板,例如发光二极管(light-emitting diode,led)显示面板、有机发光二极管(organic light-emitting diode,oled)显示面板、次毫米发光二极管(mini led)显示面板或微发光二极管(micro led)显示面板,其的驱动电路大多是采用如低温多晶硅(lowtemperature poly-silicon,ltps)、非晶硅(a-si)或氧化物薄膜晶体管(oxide tft)的制程技术来制造,因此导致驱动电路的电路组件本身特性皆会因前述制程而产生变异,而造成输出电压的误差。举例而言,当薄膜晶体管的临界电压变异时,薄膜晶体管的输出电压将出现误差。并且,当驱动电路中包含的薄膜晶体管越多时,这些薄膜晶体管的开关动作将因为寄生电容耦合效应,而对薄膜晶体管的栅极的电压电平产生非理想偏压影响。

技术实现要素:

3.本揭露是针对一种用于驱动光发射单元的驱动电路以及电子装置提出特别的电路设计架构,而可有效地补偿驱动电路当中的驱动晶体管。

4.根据本揭露的实施例,本揭露的用于驱动光发射单元的驱动电路包含驱动晶体管、切换晶体管、点亮晶体管、第一电容器以及第一补偿晶体管。所述切换晶体管耦接所述驱动晶体管。所述点亮晶体管耦接在所述光发射单元以及所述驱动晶体管之间。所述第一电容器耦接所述驱动晶体管。所述第一补偿晶体管耦接所述第一电容器。所述第一补偿晶体管的第一端与所述点亮晶体管的第一端接收相同信号。

5.根据本揭露的实施例,本揭露的电子装置包含基板、光发射单元以及驱动电路。所述光发射单元设置在所述基板上。所述驱动电路设置在所述基板上。所述驱动电路驱动所述光发射单元,且所述驱动电路包含驱动晶体管、切换晶体管、点亮晶体管、第一电容器以及第一补偿晶体管。所述切换晶体管耦接所述驱动晶体管。所述点亮晶体管耦接在所述光发射单元以及所述驱动晶体管之间。所述第一电容器耦接所述驱动晶体管。所述第一补偿晶体管耦接所述第一电容器。所述第一补偿晶体管的第一端与所述点亮晶体管的第一端接收相同信号。

6.基于上述,本揭露的用于驱动光发射单元的驱动电路以及电子装置可通过在驱动电路当中设计有补偿晶体管来有效地补偿驱动电路当中的驱动晶体管的电压。

7.为让本揭露的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

8.图1是本揭露的一实施例的电子装置的示意图;

9.图2是本揭露的第一实施例的驱动电路的示意图;

10.图3是本揭露的一实施例的信号时序图;

11.图4是本揭露的第二实施例的驱动电路的示意图;

12.图5是本揭露的第三实施例的驱动电路的示意图;

13.图6是本揭露的第四实施例的驱动电路的示意图;

14.图7是本揭露的一实施例的电流电压曲线示意图;

15.图8是本揭露的另一实施例的电流电压曲线示意图。

16.附图标记说明

17.100、200、400、500、600:电子装置;

18.110、210、410、510、610:基板;

19.120、220、420、520、620:驱动电路;

20.121:驱动晶体管;

21.122:点亮晶体管;

22.123:数据写入电路;

23.124:存储电路;

24.125、225-1、225-2、425、525、625:补偿电路;

25.130、230、430、530、630:光发射单元;

26.701、801、802:电流电压曲线;

27.vdd:工作电压;

28.vss:接地电压;

29.t1~t12:晶体管;

30.c1~c3、cst:电容;

31.em:发射信号;

32.da:数据信号;

33.sn:写入信号;

34.rst:重置信号;

35.vrst:重置电压;

36.vref:参考电压;

37.an:阳极;

38.t0~t4:时间。

具体实施方式

39.现将详细地参考本揭露的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在附图和描述中用来表示相同或相似部分。

40.在本揭露一些实施例中,用语“耦接”可包含任何直接及间接的电性连接手段,其中间接的电性连接手段是指耦接的两者之间还可存在有其他组件的情况,并且所述其他组件可包含电容、电阻或电感等诸如此类的电路组件、一般组件或前述各组件的组合。在本揭

露一些实施例中,用语“耦接在

…

之间”是指各别对于两个耦接对象之间可包含任何直接及间接的电性连接手段,其中间接的电性连接手段是指各别对于两个耦接对象之间还可存在有其他组件的情况,并且所述其他组件可包含电容、电阻或电感等诸如此类的电路组件、一般组件或前述各组件的组合。另外,在本揭露一些实施例中,用语“耦接某电压”可是指直接或间接耦接某电压线、某电压端或某电压源,或是接收某电压。

41.在本揭露一些实施例中,用语“设置”可包含任何直接及间接的设置、配置或形成手段,其中间接的设置、配置或形成手段是指设置的两者之间还可设置、配置或形成有其他组件、对象或其他材料层等的情况。

42.须知悉的是,以下所举实施例可以在不脱离本揭露的精神下,可将数个不同实施例中的特征进行组合、修饰、置换或转用以完成其他实施例。各实施例间特征只要不违背发明精神或相冲突,均可任意混合搭配使用。

43.说明书与权利要求中所使用的序数例如“第一”、“第二”、“第三”等的用词用以修饰组件,其本身并不意含及代表该,或该些,组件有任何之前的序数,也不代表某一组件与另一组件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的组件得以和另一具有相同命名的组件能作出清楚区分。权利要求与说明书中可不使用相同用词,据此,说明书中的第一构件在权利要求中可能为第二构件。

44.本揭露的电子装置,例如可包含显示设备、天线装置、感测装置、触控电子装置(touch display)、曲面电子装置(curved display)或非矩形电子装置(free shape display),也可以是可弯折或可挠式拼接电子装置,但不以此为限。电子装置的光发射单元可例如包含发光二极管(light-emitting diode,led)、液晶(liquid crystal)、荧光(fluorescence)、磷光(phosphor)、量子点(quantum dot,qd)、其它合适的显示介质、或前述的组合,但不以此为限。发光二极管可例如包含有机发光二极管(organic light-emitting diode,oled)、无机发光二极管(inorganic light-emitting diode)、次毫米发光二极管(mini led)、微发光二极管(micro led)或量子点发光二极管(quantum dot light-emitting diode,可例如为qled、qdled)、或其他适合的材料或上述的任意排列组合,但不以此为限。天线装置可例如是液晶天线,但不以此为限。需注意的是,本揭露的电子装置可为前述的任意排列组合,但不以此为限。此外,电子装置的外型可为矩形、圆形、多边形、具有弯曲边缘的形状或其他适合的形状。电子装置可以具有驱动系统、控制系统、光源系统、层架系统等,诸如此类的外围系统以支持显示设备或天线装置。

45.本揭露通篇说明书与所附的权利要求中会使用某些词汇来指称特定组件。本领域技术人员应理解,电子装置制造商可能会以不同的名称来指称相同的组件。本文并不意在区分那些功能相同但名称不同的组件。在下文说明书与权利要求中,“含有”与“包含”等词为开放式词语,因此其应被解释为“含有但不限定为

…”

之意。

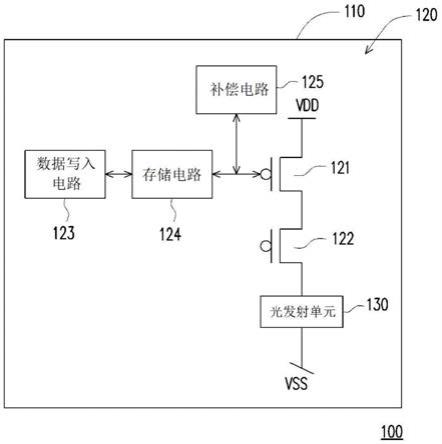

46.图1是本揭露的一实施例的电子装置的示意图。参考图1,电子装置100包含基板110、驱动电路120以及光发射单元(light-emitting unit)130。驱动电路120以及光发射单元130设置在基板110上。驱动电路120包含驱动晶体管(driving transistor)121、点亮晶体管(emitting transistor)122、数据写入电路123、存储电路124以及补偿电路125。在本实施例中,驱动晶体管121的第一端耦接存储电路124以及补偿电路125。驱动晶体管121的第二端耦接工作电压vdd。驱动晶体管121的第三端耦接点亮晶体管122的第二端。点亮晶体

管122的第三端耦接光发射单元130的一端,并且点亮晶体管122的第一端可接收信号(图未示),以决定是否点亮光发射单元130。光发射单元130的另一端耦接接地电压vss。存储电路124还耦接数据写入电路123。在本实施例中,工作电压vdd、驱动晶体管121、点亮晶体管122、光发射单元130以及接地电压vss形成像素驱动电流路径。本揭露的晶体管(例如上述驱动晶体管121或点亮晶体管122等)中可包含半导体材料,半导体材料例如包含非晶硅(amorphous silicon)、低温多晶硅(low temperature poly-silicon,ltps)或金属氧化物(metal oxide)。晶体管可以是包含顶栅极(top gate)、底栅极(bottom gate)或双栅极(dual gate or double gate)薄膜晶体管,或上述材料的组合,本揭露不限于此。在一些实施例中,薄膜晶体管可具有上述不同的半导体材料。本揭露的晶体管(例如驱动晶体管121或点亮晶体管122等)的第一端、第二端以及第三端可分别为栅极(gate)、源极(source)及漏极(drain),但本揭露并不限于此。此外,晶体管的栅极可视为晶体管的控制端。另外,本揭露的晶体管栅极可包含多晶硅、金属或其他导电材料,且不限于此。上述金属包含铜(cu)、铝(al)、钼(mo)、钨(w)、金(au)、铬(cr)、镍(ni)、铂(pt)或钛(ti),且不限于此。本揭露的晶体管的源极及漏极的材料可包含金属,例如铜(cu)、铝(al)、钼(mo)、钨(w)、金(au)、铬(cr)、镍(ni)、铂(pt)或钛(ti),且不限于此。

47.本揭露的基板110可以为硬质基板或可挠性基板,基板110的材料例如包含玻璃、石英、陶瓷、蓝宝石或塑料等,但本揭露并不以此为限。在另一实施例中,基板110的材料可包含合适的不透明材料。在一些实施例中,当基板110为可挠基板时可包含合适的可挠材料,例如聚碳酸酯(polycarbonate,pc)、聚酰亚胺(polyimide,pi)、聚丙烯(polypropylene,pp)或聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、其他合适的材料或前述材料的组合,但并不以此为限。此外,基板110的透光率不加以限制,也就是说,基板110可为透光基板、半透光基板或不透光基板。

48.在本实施例中,数据写入电路123以及补偿电路125可各别包含由一个或多个晶体管组成的电路,并且存储电路124可包含电容器。数据写入电路123可用于提供数据信号(data signal)至存储电路124,并且存储电路124可存储所述数据信号。存储电路124可提供所述数据信号至驱动晶体管121,以使驱动晶体管121可依据所述数据信号的电压大小来从工作电压vdd提供相应的驱动电流至点亮晶体管122。当点亮晶体管122开启(或称导通)时,点亮晶体管122可将所述驱动电流提供至光发射单元130。值得注意的是,补偿电路125还耦接所述像素驱动电流路径上的任意节点,以依据所述节点的电压来提供补偿偏压至驱动晶体管121的第一端。本实施例的驱动电路120可以是由多个晶体管所组成的电路架构,例如可以是由两个晶体管与一个电容器(2t1c)所组成的电路架构,或者可以是由七个晶体管与两个电容器(7t2c)所组成的电路架构,或者可以是由八个晶体管与两个电容器(8t2c)所组成的电路架构,本揭露不限于此,而以下的各个实施例将以由八个晶体管所组成的电路架构来举例说明,但本揭露并不限与此。

49.图2是本揭露的第一实施例的驱动电路的示意图。参考图2,电子装置200包括基板210、驱动电路220以及光发射单元230。基板210的材料举例可参考前述基板110的材料举例,不再赘述。驱动电路220设置于基板210上,且驱动电路220包括晶体管t1~t12、电容c1~c3以及存储电容cst。晶体管t1~t12可为p型晶体管,但本揭露并不限于此。在一实施例中,晶体管t1~t12可也设计为n型晶体管。或是,晶体管t1~t12的一部分为p型晶体管,而

晶体管t1~t12的另一部分为n型晶体管。另外,应理解的是,为了更佳地理解,一些组件将在图2中被省略和/或简化。

50.在本实施例中,晶体管t1可为驱动晶体管,并且可对应如图1的驱动晶体管121,且晶体管t11可为补偿晶体管,晶体管t1的第一端(例如为栅极g)耦接存储电容cst的一端,并且存储电容cst的另一端通过节点n耦接晶体管t2的第三端以及晶体管t4的第三端。晶体管t2可为切换晶体管(switch transistor),并且可对应如图1的数据写入电路123。晶体管t2的第一端接收写入信号sn,并且晶体管t2的第二端接收数据信号da。晶体管t4的第一端可接收发射信号em。晶体管t4的第二端耦接参考电压vref。晶体管t1的第二端耦接工作电压vdd,并且电容c1耦接在晶体管t1的第一端以及第二端(例如为源极s)之间。晶体管t1的第三端(例如为漏极d)耦接晶体管t5的第二端。晶体管t5可为点亮晶体管,并且可对应如图1的点亮晶体管122。晶体管t5的第一端可接收点亮信号(emitting signal)em。晶体管t5的第三端耦接光发射单元230的阳极(anode)an。光发射单元230的阴极(cathode)耦接接地电压vss。光发射单元230可对应如图1的光发射单元130。此外,须先说明的是,本实施例的晶体管t5、t10、t11可例如接收相同信号,例如发射信号em,但本揭露并不限于此。更详细来说,晶体管t11的第一端与晶体管t5的第一端可接收相同的发射信号em。类似地,晶体管t10的第一端与晶体管t5的第一端可接收相同的发射信号em。

51.在本实施例中,工作电压vdd、晶体管t1、晶体管t5、光发射单元230以及接地电压vss形成像素驱动电流路径。当晶体管t2开启时,数据信号da可从晶体管t2写入至存储电容cst,并且电容cst可提供相应的电压至晶体管t1,以使晶体管t1操作在饱和区(saturation region),并且从工作电压vdd提供相应的驱动电流至晶体管t5。当晶体管t5开启时,光发射单元230可被晶体管t5提供的所述驱动电流所驱动。

52.在本实施例中,晶体管t3可为补偿晶体管(compensative transistor)。晶体管t3的第一端接收写入信号sn,并且晶体管t3的第二端以及第三端耦接在晶体管t1的第一端以及晶体管t1的第三端。晶体管t3可补偿晶体管t1的第一端的电压。

53.在本实施例中,晶体管t6可为重置晶体管(reset transistor)。晶体管t6的第一端可接收重置信号rst。晶体管t6的第二端耦接重置电压vrst。晶体管t6的第三端耦接电容c1以及晶体管t1的第一端。在本实施例中,晶体管t6可用于重置晶体管t1的第一端的电位。

54.在本实施例中,晶体管t7可为重置晶体管。晶体管t7的第一端可接收重置信号rst。晶体管t7的第二端耦接参考电压vref。晶体管t7的第三端耦接节点n。晶体管t7可用于重置节点n的电位(即存储电容cst的一端的电位)。在一实施例中,参考电压vref的电压可小于接地电压vss的电压,但本揭露并不限于此。另外,参考电压vref以及重置电压vrst分别为独立电压。也就是说,参考电压vref与重置电压vrst可依设计需求个别给与不同的电压值,且彼此的电压值不受干扰。在一实施例中,参考电压vref的电压可等于重置电压vrst电压,但本揭露并不限于此。在另一实施例中,参考电压vref以及重置电压vrst可以是相依电压,也就是说,参考电压vref与重置电压vrst彼此的电压值会互相影响,本揭露不限于此。

55.在本实施例中,晶体管t8可为重置晶体管。晶体管t8的第一端可接收重置信号rst或写入信号sn。晶体管t8的第二端耦接光发射单元230的阳极an。晶体管t8的第三端耦接重置电压vrst。在本实施例中,晶体管t8可用于重置光发射单元230的阳极an的电位。

56.在本实施例中,晶体管t9、t10以及电容c2组成补偿电路225-1。晶体管t9可以是补偿晶体管。晶体管t10可以是重置晶体管。电容c2的一端耦接晶体管t1的第一端,并且电容c2的另一端耦接晶体管t9的第二端以及晶体管t10的第二端。晶体管t9的第一端可接收写入信号sn。晶体管t9的第三端耦接光发射单元230的阳极an或接地电压vss。晶体管t10的第一端可接收发射信号em。晶体管t10的第三端耦接重置电压vrst。在本实施例中,补偿电路225-1可依据光发射单元230的阳极an的电压或接地电压vss来补偿晶体管t1。

57.在本实施例中,晶体管t11、t12以及电容c3组成补偿电路225-2。根据一些实施例,晶体管t12可为重至晶体管。电容c3的一端耦接晶体管t1的第一端,并且电容c3的另一端耦接晶体管t11的第三端以及晶体管t12的第三端。晶体管t11的第一端可接收发射信号em。晶体管t11的第二端耦接工作电压vdd。晶体管t12的第一端可接收写入信号sn。晶体管t12的第三端耦接重置电压vrst。在本实施例中,补偿电路225-2可依据工作电压vdd的电压来补偿晶体管t1。

58.图3是本揭露的一实施例的信号时序图。参考图2以及图3,图3的信号时序可适用于图2的驱动电路220。请搭配参考以下表1。在本实施例中,在时间t0之前,重置信号rst以及写入信号sn(例如以p型晶体管为例)为高电压电位。在时间t0至时间t1的重置期间,重置信号rst切换为低电压电位,并且写入信号sn以及发射信号em维持为高电压电位。因此,当晶体管t8的第一端接收重置信号rst时,晶体管t1、t6、t7、t8为开启,并且晶体管t2~t5、t9~t12为关闭(或称未导通)。当晶体管t8的第一端接收写入信号sn时,晶体管t1、t6、t7为开启,并且晶体管t2~t5、t8~t12为关闭。在重置期间,节点n的电压依据参考电压vref而重置,并且参考电压vref依据重置电压vrst而重置。对此,在重置期间,节点n的电压为参考电压vef。晶体管t1的第一端的电压近似于重置电压vrst。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为工作电压vdd。值得注意的是,图3以p型晶体管为例,但本揭露不限于此。

59.在时间t1至时间t2,重置信号rst回复为高电压电位,并且写入信号sn以及发射信号em为高电压电位。在时间t2至时间t3的补偿期间,写入信号sn切换为低电压电位,并且重置信号rst以及发射信号em维持为高电压电位。因此,当晶体管t8的第一端接收重置信号rst时,晶体管t1~t3、t9、t12为开启,并且晶体管t4~t8、t10、t11为关闭。当晶体管t8的第一端接收写入信号sn时,晶体管t1~t3、t8、t9、t12为开启,并且晶体管t4~t7、t10、t11为关闭。在补偿期间,数据信号da写入存储电容cst,并且晶体管t3依据工作电压vdd补偿晶体管t1的第一端。对此,在补偿期间,节点n的电压为“vda”,其中“vda”为数据信号da的电压。晶体管t1的第一端的电压为“vdd-|vth|”,其中“|vth|”为晶体管t1的阈值电压。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为“vdd-vx”,其中“vx”为常数电压值且可用于抵销一种或多种晶体管效应所产生的电压影响,例如包括纽结效应(kink effect)产生的电压影响。

60.在时间t3至时间t4,写入信号sn回复为高电压电位,并且重置信号rst以及发射信号em为高电压电位。在时间t4之后的发射期间,发射信号em切换为低电压电位,并且写入信号sn以及重置信号rst维持为高电压电位。因此,晶体管t1、t4、t5、t10、t11为开启,并且晶体管t2、t3、t6~t9、t12为关闭。在发射期间,存储电容cst以及电容c1提供对应的电压至晶体管t1的第一端,以使晶体管t1利用工作电压vdd所提供的相对应的驱动电流来驱动光发

射单元230。对此,在发射期间,节点n的电压为参考电压vref。晶体管t1的第一端的电压为“(vrst-van) (vdd-vrst) vdd-|vth| (vref-vda)”,其中“van”为光发射单元230的阴极的电压。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为“van-vdd vx”。最后,晶体管t1的第二端与第一端之间的电压差加上晶体管t1的阈值电压的补偿结果vsg vth的电压可为“vx (vda-vref)”。据此,所述补偿结果vsg vth的电压可降低非理想偏压、或可减缓纽结效应的影响,或降低工作电压vdd以及接地电压vss电压偏移的影响。

[0061][0062]

表1

[0063]

图4是本揭露的第二实施例的驱动电路的示意图。参考图4,电子装置400包括基板410、驱动电路420以及光发射单元430。基板410的材料举例可参考前述基板110的材料举例,不再赘述。驱动电路420设置在基板410上,且驱动电路420包括晶体管t1~t10、电容c1~c2以及存储电容cst。在本实施例中,晶体管t1~t8以及存储电容cst的电路耦接关系如图2实施例所述,因此可参照上述图2实施例的说明而不再赘述。此外,须先说明的是,本实施例的晶体管t5、t10可例如接收相同信号,例如发射信号em,更详细来说,晶体管t10的第一端与晶体管t5的第一端可接收相同的发射信号em,但本揭露并不限于此。另外,根据一些实施例,晶体管t10可为补偿晶体管。应理解的是,为了更佳地理解,一些组件将在图4中被省略和/或简化。

[0064]

在本实施例中,晶体管t9、t10以及电容c2组成补偿电路425。电容c2的一端耦接晶体管t1的第一端,并且电容c2的另一端耦接晶体管t9的第二端以及晶体管t10的第二端。晶体管t9的第一端可接收写入信号sn。晶体管t9的第三端耦接光发射单元430的阳极an或接收接地电压vss。晶体管t10的第一端可接收发射信号em。晶体管t10的第三端可接收工作电压vdd。在本实施例中,补偿电路425可依据工作电压vdd以及光发射单元430的阳极an的电压或接地电压vss来补偿晶体管t1。

[0065]

参考图4以及图3,图3的信号时序也可适用于图4的驱动电路420。请搭配参考以下表2。在本实施例中,在时间t0之前,重置信号rst、写入信号sn(例如p型晶体管为例)为高电压电位。在时间t0至时间t1的重置期间,重置信号rst切换为低电压电位,并且写入信号sn以及发射信号em维持为高电压电位。因此,当晶体管t8的第一端接收重置信号rst时,晶体管t1、t6、t7、t8为开启,并且晶体管t2~t5、t9、t10为关闭(或称未导通)。当晶体管t8的第一端接收写入信号sn时,晶体管t1、t6、t7为开启,并且晶体管t2~t5、t8~t12为关闭。在重置期间,节点n的电压依据参考电压vref而重置,并且参考电压vref依据重置电压vrst而重置。对此,在重置期间,节点n的电压为参考电压vref。晶体管t1的第一端的电压为重置电压vrst。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为工作电压vdd。

[0066]

在时间t1至时间t2,重置信号rst回复为高电压电位,并且写入信号sn以及发射信号em为高电压电位。在时间t2至时间t3的补偿期间,写入信号sn切换为低电压电位,并且重置信号rst以及发射信号em维持为高电压电位。因此,在晶体管t8的第一端接收重置信号rst的情况,晶体管t1~t3、t9为开启,并且晶体管t4~t8、t10为关闭。在晶体管t8的第一端接收写入信号sn的情况,晶体管t1~t3、t8~t9为开启,并且晶体管t4~t7、t10为关闭。在补偿期间,数据信号da写入存储电容cst,并且晶体管t3依据工作电压vdd补偿晶体管t1的第一端。对此,在补偿期间,节点n的电压例如为“vda”。晶体管t1的第一端的电压为“vdd-|vth|”。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为“vdd-vx”。

[0067]

在时间t3至时间t4,写入信号sn回复为高电压电位,并且重置信号rst以及发射信号em为高电压电位。在时间t4之后的发射期间,发射信号em切换为低电压电位,并且写入信号sn以及重置信号rst维持为高电压电位。因此,晶体管t1、t4、t5、t10为开启,并且晶体管t2、t3、t6~t9为关闭。在发射期间,存储电容cst以及电容c1提供对应的电压至晶体管t1的第一端,以使晶体管t1利用工作电压vdd所提供的相对应的驱动电流来驱动光发射单元430。对此,在发射期间,节点n的电压为参考电压vref。晶体管t1的第一端的电压为“(vdd-van) vdd-|vth| (vref-vda)”。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为“van-vdd vx”。最后,晶体管t1的第二端与第一端之间的电压差加上晶体管t1的阈值电压的补偿结果vsg vth的电压可为“vx (vda-vref)”。据此,所述补偿结果vsg vth的电压可降低非理想偏压、或减缓纽结效应的影响,或降低工作电压vdd以及接地电压vss电压偏移的影响。

[0068][0069]

表2

[0070]

图5是本揭露的第三实施例的驱动电路的示意图。参考图5,电子装置500包括基板510、驱动电路520以及光发射单元530。基板510的材料举例可参考前述基板110的材料举例,不再赘述。驱动电路520设置于基板510上,且驱动电路520包括晶体管t1~t10、电容c1~c2以及存储电容cst。在本实施例中,晶体管t1~t8、电容c1以及存储电容cst的电路耦接关系如图2实施例所述,因此可参照上述图2实施例的说明而不再赘述。此外,须先说明的是,本实施例的晶体管t4、t5、t10可例如接收相同信号,例如发射信号em,更详细来说,晶体管t10的第一端与晶体管t5的第一端以及晶体管t4的第一端可接收相同的发射信号em,但本揭露并不限于此。另外,根据一些实施例,晶体管t10可为补偿晶体管。应理解的是,为了更佳地理解,一些组件将在图5中被省略和/或简化。

[0071]

在本实施例中,晶体管t9、t10以及电容c2组成补偿电路525。电容c2的一端耦接晶体管t1的第一端,并且电容c2的另一端耦接晶体管t9的第二端以及晶体管t10的第二端。晶体管t9的第一端可接收写入信号sn。晶体管t9的第三端耦接光发射单元530的阳极an或接

地电压vss。晶体管t10的第一端可接收发射信号em。晶体管t10的第三端耦接重置电压vrst。在本实施例中,补偿电路525可依据光发射单元530的阳极an的电压或接地电压vss来补偿晶体管t1。

[0072]

参考图5以及图3,图3的信号时序也可适用于图5的驱动电路520。请搭配参考以下表3。在本实施例中,在时间t0之前,重置信号rst以及写入信号sn(例如以p型晶体管为例)为高电压电位。在时间t0至时间t1的重置期间,重置信号rst切换为低电压电位,并且写入信号sn以及发射信号em维持为高电压电位。因此,在晶体管t8的第一端接收重置信号rst的情况,晶体管t1、t6、t7、t8为开启,并且晶体管t2~t5、t9、t10为关闭(或称未导通)。在晶体管t8的第一端接收写入信号sn的情况,晶体管t1、t6、t7为开启,并且晶体管t2~t5、t8、t9、t10为关闭。在重置期间,节点n的电压依据参考电压vref而重置,并且参考电压vref依据重置电压vrst而重置。对此,在重置期间,节点n的电压为参考电压vref。晶体管t1的第一端的电压为重置电压vrst。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为工作电压vdd。

[0073]

在时间t1至时间t2,重置信号rst回复为高电压电位,并且写入信号sn以及发射信号em为高电压电位。在时间t2至时间t3的补偿期间,写入信号sn切换为低电压电位,并且重置信号rst以及发射信号em维持为高电压电位。因此,在晶体管t8的第一端接收重置信号rst的情况,晶体管t1~t3、t9为开启,并且晶体管t4~t8、t10为关闭。在晶体管t8的第一端接收写入信号sn的情况,晶体管t1~t3、t8、t9为开启,并且晶体管t4~t7、t10为关闭。在补偿期间,数据信号da写入存储电容cst,并且晶体管t3依据工作电压vdd补偿晶体管t1的第一端。对此,在补偿期间,节点n的电压例如为“vda”。晶体管t1的第一端的电压为“vdd-|vth|”。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为“vdd-vx”。

[0074]

在时间t3至时间t4,写入信号sn回复为高电压电位,并且重置信号rst以及发射信号em为高电压电位。在时间t4之后的发射期间,发射信号em切换为低电压电位,并且写入信号sn以及重置信号rst维持为高电压电位。因此,晶体管t1、t4、t5、t10为开启,并且晶体管t2、t3、t6~t9为关闭。在发射期间,存储电容cst以及电容c1提供对应的电压至晶体管t1的第一端,以使晶体管t1利用工作电压vdd所提供的相对应的驱动电流来驱动光发射单元530。对此,在发射期间,节点n的电压为参考电压vref。晶体管t1的第一端的电压为“(vrst-van) vdd-|vth| (vref-vda)”。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为“van-vdd vx”。最后,晶体管t1的第二端与第一端之间的电压差加上晶体管t1的阈值电压的补偿结果vsg vth的电压可为“vdd-vrst (vda-vref) vx”。据此,所述补偿结果vsg vth的电压可降低非理想偏压、或减缓纽结效应的影响,或降低工作电压vdd以及接地电压vss电压偏移的影响。

[0075]

vrst) vdd-|vth| (vref-vda)”。晶体管t1的第二端的电压为工作电压vdd。晶体管t1的第三端的电压为“van-vdd vx”。最后,晶体管t1的第二端与第一端之间的电位差加上晶体管t1的阈值电压的补偿结果vsg vth的电压可为“vrst (vda-vref) van vx”。据此,所述补偿结果vsg vth的电压可降低非理想偏压、或减缓纽结效应的影响,或降低工作电压vdd以及接地电压vss电压偏移的影响。

[0082][0083]

表4

[0084]

图7是本揭露的一实施例的电流电压曲线示意图。参考图7,图7的电流电压曲线701可对应于图2的驱动电路220通过补偿电路225-1来依据工作电压vdd补偿晶体管t1的结果,或可对应于图4的驱动电路420通过补偿电路425来依据工作电压vdd补偿晶体管t1的结果,或可对应于图6的驱动电路620通过补偿电路625来依据工作电压vdd补偿晶体管t1的结果。如图7所示,当晶体管t1进入饱和区时,晶体管t1的电流电压曲线701在工作电压vdd发生漂移的情况(例如7v~9v之间)下,仍可维持稳定的电流值。

[0085]

图8是本揭露的另一实施例的电流电压曲线示意图。参考图8,图8的电流电压曲线801可对应于图2的驱动电路220通过补偿电路225-2来依据光发射单元230的阳极an的电压补偿晶体管t1的结果,或可对应于图4的驱动电路420通过补偿电路425来依据光发射单元430的阳极an的电压补偿晶体管t1的结果,或可对应于图5的驱动电路520通过补偿电路525来依据光发射单元530的阳极an的电压补偿晶体管t1的结果。如图8的电流电压曲线801所示,当晶体管t1进入饱和区时,晶体管t1的电流电压曲线801在接地电压vss发生漂移的情况(例如-2v~0v之间)下,仍可维持稳定的电流值。

[0086]

图8的电流电压曲线802可对应于图2的驱动电路220通过补偿电路225-2来依据接地电压vss补偿晶体管t1的结果,或可对应于图4的驱动电路420通过补偿电路425来依据接地电压vss补偿晶体管t1的结果,或可对应于图5的驱动电路520通过补偿电路525来依据接地电压vss补偿晶体管t1的结果。如图8的电流电压曲线802所示,当晶体管t1进入饱和区时,晶体管t1的电流电压曲线801在接地电压vss发生漂移的情况(例如-2v~0v之间)下,仍可维持稳定的电流值。

[0087]

另外,在对于电子产品进行分析或举证时,若电子产品的驱动电路中如设置有包括有如上述各实施例的补偿电路的晶体管,或者是具有如图7、图8的电流电压曲线特性,则可视为此电子产品为实施本揭露所主张的电路设计架构。

[0088]

综上所述,本揭露的用于驱动光发射单元的驱动电路以及电子装置可通过设计补偿电路来耦接驱动电流路径上的任意节点与驱动晶体管的第一端,例如闸极,以及搭配具有补偿期间的晶体管切换时序,来有效地补偿驱动晶体管,而使其补偿结果可降低非理想

偏压、或可减缓纽结效应的影响,或降低工作电压以及接地电压偏移的影响。

[0089]

最后应说明的是:以上各实施例仅用以说明本揭露的技术方案,而非对其限制;尽管参照前述各实施例对本揭露进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本揭露各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。