半导体装置及其制造方法

1.[相关申请]

[0002]

本技术享受以日本专利申请2020-164568号(申请日:2020年9月30日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

[0003]

本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

[0004]

近年来,一般的半导体装置是以利用树脂加以塑模的封装状态使用的。作为近年的半导体装置,球栅阵列(bga:ball grid array)型固态驱动器(ssd:solid state drives)的性能尤其得到了提高。bga型ssd随着性能的提高,遭遇了电磁波辐射及发热量增加的问题。

技术实现要素:

[0005]

本发明的实施方式要解决的问题是,提供一种能实现电磁波的屏蔽与散热性的提高的半导体装置及其制造方法。

[0006]

实施方式的半导体装置包含衬底、半导体存储器、控制器、第1导热板、石墨片、封装部及外部电极。衬底具有第1面、及位于第1面的相反侧的第2面。半导体存储器设置在第1面。控制器设置在第1面,能控制半导体存储器。第1导热板配置在控制器之上。石墨片配置在第1导热板之上。封装部将半导体存储器、控制器、第1导热板及石墨片封装。外部电极有多个,设置在衬底的第2面。

附图说明

[0007]

图1是表示搭载有第1实施方式的半导体装置的电子机器的一例的概略构成图。

[0008]

图2是示意性表示第1实施方式的电路衬底的构成的一部分的框图。

[0009]

图3是表示第1实施方式的半导体装置的构成的一例的框图。

[0010]

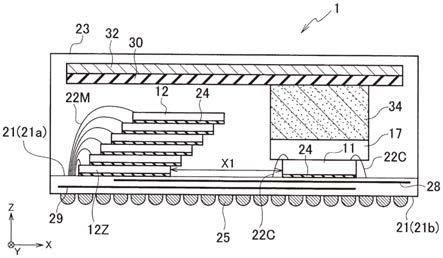

图4是第1实施方式的半导体装置的剖视图。

[0011]

图5是第1实施方式的半导体装置的俯视图。

[0012]

图6是将第1实施方式的半导体装置的一部分构成除外而显示的图。

[0013]

图7是可应用于第1实施方式的半导体装置的石墨片的构成图。

[0014]

图8是例示可应用于第1实施方式的半导体装置的第1石墨片gf(xy)的图。

[0015]

图9是例示可应用于第1实施方式的半导体装置的第2石墨片gf(xz)的图。

[0016]

图10是第1实施方式的变化例的半导体装置的剖视图。

[0017]

图11是第1实施方式的变化例的半导体装置的俯视图。

[0018]

图12是将第1实施方式的变化例的半导体装置的一部分构成除外而显示的图。

[0019]

图13是第2实施方式的半导体装置的剖视图。

[0020]

图14是第2实施方式的半导体装置的俯视图。

[0021]

图15是将第2实施方式的半导体装置的一部分构成除外而显示的俯视图。

[0022]

图16a是第2实施方式的半导体装置的第1剖视图

[0023]

图16b是第2实施方式的半导体装置的第2剖视图。

[0024]

图16c是第2实施方式的半导体装置的第3剖视图。

[0025]

图16d是第2实施方式的半导体装置的第4剖视图。

[0026]

图17是第2实施方式的变化例的半导体装置的剖视图。

[0027]

图18是第3实施方式的半导体装置的剖视图。

[0028]

图19是第3实施方式的半导体装置的俯视图。

[0029]

图20是第4实施方式的半导体装置的剖视图。

具体实施方式

[0030]

下面,参照附图对实施方式进行说明。以下说明的附图的记载中,相同或类似的部分被标注相同或类似的符号。附图是示意性的。另外,以下所示的实施方式例示的是用来将技术思想具体化的装置及方法,并不对零件的材质、形状、结构、配置等进行特定。实施方式可加以各种变更。

[0031]

(第1实施方式)

[0032]

图1是表示搭载有本实施方式的半导体装置1的电子机器2的一例的概略构成图。电子机器2包含壳体3。壳体3收容电路衬底(主板)4。电路衬底4包含半导体装置1及主机控制器5(例如cpu(central processing unit,中央处理器))。半导体装置1例如作为bga型ssd而构成。半导体装置1作为电子机器2的存储装置发挥功能。主机控制器5控制包含半导体装置1的电子机器2整体的动作。主机控制器5例如包含南桥。

[0033]

图2是示意性表示电路衬底4的构成的一部分的框图。在电路衬底4设置有电源电路7。电源电路7经由电源线8(8a、8b)连接于半导体装置1及主机控制器5。电源电路7经由电源线8(8a)将电源电压供给至主机控制器5。另外,电源电路7经由电源线8(8b)将电源电压供给至半导体装置1。

[0034]

半导体装置1与主机控制器5之间设置有多根信号线6。半导体装置1经由信号线6与主机控制器5之间进行信号收发。半导体装置1及主机控制器5例如具有符合高速外设组件互连(pci-express:peripheral component interconnect express,以下称为pcie)标准的接口。半导体装置1及主机控制器5所具有的接口也可未必是符合pcie标准的接口。主机控制器5及半导体装置1所具有的接口例如也可为符合sas(serial attached small computer system interface,串行连接的小型计算机系统接口)或sata(serial advanced technology attachment,串行高级技术附件)标准的接口。另外,主机控制器5及半导体装置1所具有的接口也可为符合nvme(non volatile memory express,高速非易失性存储器)、usb(universal serial bus,通用串行总线)等其他标准的接口。

[0035]

(半导体装置的构成)

[0036]

下面,对半导体装置1的构成进行说明。

[0037]

图3是表示半导体装置1的构成的一例的框图。图4是第1实施方式的半导体装置1的剖视图。图5是第1实施方式的半导体装置1的俯视图。半导体装置1具备控制器11、半导体

存储器12、ram(random access memory,随机访问存储器)13、振荡器(osc)14、eeprom(electrically erasable and programmable read only memory,电可擦除可编程只读存储器)15、温度传感器16、衬底21(封装衬底)、键合线22m及22c、绝缘膜17、第1导热板34、绝缘片30、石墨片32、封装部(塑模材料)23、安装膜24以及焊球(外部电极)25。

[0038]

控制器11是控制半导体存储器12的动作的集成电路。控制器11在集成电路的1个芯片上集成有处理器内核、微控制器等。处理器内核、微控制器等协同工作,而作为soc(system on chip,片上系统)发挥功能。

[0039]

半导体存储器12例如为nand(not and,与非)闪速存储器。半导体存储器12除了nand闪速存储器以外,例如也可应用nor(not or,或非)型闪速存储器、阻变存储器(reram:resistive random access memory)、相变存储器(pcm:phase-change memory)、铁电存储器(feram:ferroelectric random access memory)、磁隧道结(mtj:magneto tunnel junction)阻变元件。

[0040]

ram13是易失性存储器。ram13例如为dram(dynamic random access memory,动态随机访问存储器)。ram13存储半导体存储器12的管理信息。ram13例如用于数据的高速缓冲等。

[0041]

振荡器(osc)14将指定频率的动作信号供给至控制器11。

[0042]

eeprom15是非易失性存储器。eeprom15存储控制程序等作为固定信息。

[0043]

温度传感器16计测半导体装置1内的温度。温度传感器16将所计测到的温度作为温度信息发送至控制器11。

[0044]

衬底21是多层配线衬底。衬底21具有第1面21a、及位于第1面21a的相反侧的第2面21b。衬底21具有电源层28及接地层29。

[0045]

键合线22m及22c例如为铜线、银线、金线。键合线22m及22c的粗细例如为直径20μm~50μm左右。

[0046]

绝缘膜17是具有柔软性的绝缘膜。对绝缘膜17应用线上膜(film on wire,fow)技术。因此,能使键合线22c的一部分内置于绝缘膜17中。绝缘膜17的厚度例如为约50μm左右。绝缘膜17的厚度是足以将键合线22c的一部分埋入的厚度。

[0047]

第1导热板34例如为硅衬底。第1导热板34也可为硅衬底以外的高导热性衬底。第1导热板34隔着绝缘膜17配置在控制器11上。另外,第1导热板34配置在绝缘膜17与绝缘片30之间。通过第1导热板34,能将产自控制器11的热高效地传递至石墨片32。

[0048]

绝缘片30例如为氧化铝片。绝缘片30保护石墨片32。绝缘片30防止石墨片32带电。

[0049]

石墨片32作为散热片使用。半导体存储器12的热经由封装部(塑模材料)23传递至石墨片32。另外,控制器11的热经由第1导热板34传递至石墨片32。石墨片32的导热具有各向异性。石墨片32例如具有在与衬底21平行的方向上热导率较高的配向。另外,石墨片32也可具有在与衬底21平行的方向、及与衬底21垂直的方向上热导率较高的配向。石墨片32的导电性较高。石墨片32例如为电浮动状态。另外,石墨片32也可为接地电位。石墨片32配置在第1导热板34上。石墨片32是以俯视下覆盖第1导热板34及控制器11的方式配置。另外,石墨片32是以俯视下隔着封装部(塑模材料)23覆盖半导体存储器12的方式配置。石墨片32小于封装部23。石墨片32小于衬底21。石墨片32与绝缘片30的面积大致相等。

[0050]

封装部23例如为环氧系树脂等塑模材料。封装部23设置在衬底21的第1面21a。封

装部23将半导体存储器12、控制器11、第1导热板34、绝缘膜17、石墨片32、绝缘片30、键合线22m及键合线22c封装。

[0051]

安装膜24是粘接膜。安装膜24用来将半导体存储器12及控制器11固定于衬底21。

[0052]

焊球25是连接部件。焊球25例如为焊料。焊球25例如为球状。焊球25作为将半导体装置1与外部连接的外部电极使用。焊球25设置在衬底21的第2面21b。

[0053]

(半导体装置的结构)

[0054]

下面,对半导体装置1的结构进行说明。

[0055]

如图4所示,半导体存储器12载置在衬底21的第1面21a。半导体存储器12通过安装膜24固定于第1面21a。多个半导体存储器12经由衬底21电连接于控制器11。另外,在第1面21a上,将半导体存储器12与控制器11排列的方向设为x方向,将与x方向正交的方向设为y方向。另外,将与第1面21a垂直的方向设为z方向。

[0056]

此外,多个半导体存储器12也可积层。多个半导体存储器12在x方向上错开而沿z方向积层。另外,多个半导体存储器12通过安装膜24而固定。另外,多个半导体存储器12通过键合线22m电连接于衬底21。也可对安装膜24应用fow技术,使其中内置键合线22m。以后,将多个半导体存储器12中最下层的半导体存储器特设为半导体存储器12z。半导体存储器12z在衬底21的第1面21a上,与控制器11隔开距离x1而配置。距离x1的值例如为数mm。

[0057]

图6是将第1实施方式的半导体装置1的一部分构成除外而显示的图。在第1实施方式中,控制器11、ram13及温度传感器16安装在与半导体存储器12相邻的区域a。

[0058]

控制器11载置在衬底21的第1面21a。控制器11例如通过安装膜24固定于衬底21的第1面21a。另外,控制器11通过键合线22c电连接于衬底21。

[0059]

ram13载置在衬底21的第1面21a。此外,ram13通过未予图示的安装膜24固定于第1面21a。ram13经由键合线电连接于衬底21。ram13经由衬底21电连接于控制器11。

[0060]

温度传感器16载置在衬底21的第1面21a。温度传感器16例如位于控制器11附近。更具体来说,半导体存储器12z、控制器11及ram13中,控制器11与温度传感器16的距离最短。

[0061]

(石墨片)

[0062]

图7是第1实施方式的石墨片的构成图。石墨片32包含石墨烯gf1、gf2、gf3、

…

、gfn。石墨烯gf1、gf2、gf3、

…

、gfn构成石墨片32的积层结构。石墨烯gf1、gf2、gf3、

…

、gfn在1个晶体结构中具有多个六方晶系的共价键。相邻的石墨烯gf1、gf2、gf3、

…

、gfn彼此通过凡得瓦力而键结。石墨烯gf1、gf2、gf3、

…

、gfn具有在晶面方向上(xy面上)比在z轴的厚度方向上大的导热度(高热导率)。

[0063]

作为石墨片32,可使用第1石墨片gf(xy)与第2石墨片gf(xz)2种石墨片。2种石墨片的配向不同。

[0064]

图8是例示第1实施方式的第1石墨片gf(xy)的图。第1石墨片gf(xy)具有xy配向(第1配向)。第1石墨片gf(xy)的面方向上的热导率高于厚度方向上的热导率。第1石墨片gf(xy)例如具有x=1500(w/mk)左右、y=1500(w/mk)左右、z=5(w/mk)左右的热导率。

[0065]

图9是例示第1实施方式的第2石墨片gf(xz)的图。第2石墨片gf(xz)具有xz配向(第2配向)。第2石墨片gf(xz)的厚度方向上的热导率高于面方向上的热导率。第2石墨片gf(xz)例如具有x=1500(w/mk)左右、y=5(w/mk)左右、z=1500(w/mk)左右的热导率。

[0066]

第1实施方式的半导体装置1能使控制器11的热有效率地向封装外部逸散。根据第1实施方式,能缓和半导体存储器12的温度上升。另外,根据第1实施方式,由于温度传感器16设置在控制器11附近,因此能提高半导体装置1的温度检测精度。另外,第1实施方式的半导体装置1通过内置石墨片32,能对半导体装置的内部进行电磁屏蔽。另外,第1实施方式的半导体装置1通过内置石墨片32,能提高散热性。

[0067]

(第1实施方式的变化例)

[0068]

图10是第1实施方式的变化例的半导体装置1的剖视图。图11是第1实施方式的变化例的半导体装置1的俯视图。图10及图11中省略了半导体装置1所具备的振荡器14及eeprom15。另外,图11中省略了半导体装置1的构成中的封装部(塑模材料)23。

[0069]

第1实施方式的变化例的半导体装置1具备衬底21(封装衬底)、控制器11、半导体存储器12、键合线22m及22c、第1导热板34、绝缘膜17、石墨片32、绝缘片30、封装部(塑模材料)23、安装膜24以及焊球25。

[0070]

图12是将第1实施方式的变化例的半导体装置的一部分构成除外而显示的图。在第1实施方式的变化例中,控制器11、ram13及温度传感器16安装在与半导体存储器12相邻的区域b。多根键合线22m将最下层的半导体存储器12z的端部与衬底21电连接。多根键合线22c将控制器11周围的端部与衬底21电连接。

[0071]

第1实施方式的变化例的半导体装置1能使控制器11的热有效率地向封装外部逸散。根据第1实施方式的变化例,能缓和半导体存储器12的温度上升。另外,第1实施方式的变化例的半导体装置1通过内置石墨片32,能对半导体装置1的内部进行电磁屏蔽。另外,第1实施方式的变化例的半导体装置1通过内置石墨片32,能提高散热性。

[0072]

(第2实施方式)

[0073]

图13是第2实施方式的半导体装置1的剖视图。图13中省略了半导体装置1所具备的振荡器14、eeprom15、ram13及温度传感器16。

[0074]

在第2实施方式的半导体装置1中,键合线22m将半导体存储器12与衬底21电连接。

[0075]

第2实施方式的半导体装置1具备衬底21(封装衬底)、控制器11、半导体存储器12、键合线22m及22c、第1导热板34、第2导热板36、绝缘膜17、石墨片32、绝缘片30、封装部(塑模材料)231及232、安装膜24以及焊球25。

[0076]

第2导热板36是用来使传导至石墨片32的热向半导体装置1的外部释散的导热板。第2导热板36例如为硅衬底。此外,第2导热板36也可为硅衬底以外的高导热性衬底。第2导热板36配置在石墨片32的上表面。

[0077]

封装部231例如为环氧系树脂等塑模材料。封装部231将半导体存储器12、控制器11、第1导热板34、绝缘膜17、石墨片32、绝缘片30、键合线22m及键合线22c封装。

[0078]

封装部232例如为环氧系树脂等塑模材料。封装部232将石墨片32与第2导热板36封装。

[0079]

图14是第2实施方式的半导体装置1的俯视图。图14中省略了除第1导热板34、第2导热板36、绝缘膜17、石墨片32、绝缘片30、封装部(塑模材料)231及232以外的构成。图15是将第2实施方式的半导体装置1的一部分构成除外而显示的俯视图。图15中省略了封装部(塑模材料)231及232。

[0080]

第1导热板34配置在控制器11之上。在控制器11配置有绝缘膜17。第1导热板34也

可还配置在ram或温度传感器的上方。

[0081]

第2导热板36大于第1导热板34。第2导热板36的上表面露出于封装部232的外部。因此,能经由第2导热板36将热高效地向半导体装置1的外部释散。

[0082]

根据第2实施方式,半导体装置1内置石墨片32。石墨片32之上配置有第2导热板36。能使半导体存储器12及控制器11的热经由石墨片32逸散至第2导热板36。另外,根据第2实施方式,半导体装置1具有第1导热板34与第2导热板36之间夹着石墨片32的结构。根据第2实施方式,能提高半导体存储器12及控制器11的散热速度。另外,根据第2实施方式,能使控制器的热有效率地向封装外部逸散。根据第2实施方式,能缓和半导体存储器的温度上升。另外,根据第2实施方式,通过内置石墨片,能对半导体装置的内部进行电磁屏蔽。另外,根据第2实施方式,通过内置石墨片,能提高散热性。

[0083]

(制造方法)

[0084]

图16a是第2实施方式的半导体装置1的第1剖视图。

[0085]

(a1)首先,如图16a所示,形成衬底21,该衬底21具有第1面21a、及位于第1面21a的相反侧的第2面21b。衬底21是多层配线衬底,具有电源层28及接地层29。

[0086]

(a2)接着,如图16a所示,在第1面21a侧形成半导体存储器12。半导体存储器12是多层化的。与最下层的半导体存储器12z沿x方向隔开距离x1,而形成能控制半导体存储器12及12z的控制器11。

[0087]

(a3)继而,如图16a所示,在控制器11的上表面形成键合线22c。另外,在半导体存储器12及12z的上表面形成键合线22m。

[0088]

图16b是第2实施方式的半导体装置1的第2剖视图。

[0089]

(b1)接着,如图16b所示,在第1导热板34上预先形成绝缘膜17。

[0090]

(b2)继而,如图16b所示,在控制器11的上表面配置绝缘膜17与第1导热板34的积层结构。第1导热板34以绝缘膜17接合于控制器11的上表面。此外,第1导热板34也可隔着绝缘膜17倒装配置在控制器11的上表面。

[0091]

图16c是第2实施方式的半导体装置1的第3剖视图。

[0092]

(c1)接着,如图16c所示,在控制器11的上表面隔着绝缘膜17形成第1导热板34。控制器11的上表面的键合线22c通过fow技术,一部分内置于绝缘膜17中。

[0093]

(c2)继而,如图16c所示,在石墨片32的背面一体形成绝缘片30。

[0094]

(c3)接着,如图16c所示,在第1导热板34之上隔着绝缘片30形成石墨片32。

[0095]

(c4)继而,如图16c所示,形成将半导体存储器12及12z、控制器11、键合线22m及22c、绝缘膜17、第1导热板34、绝缘片30以及石墨片32封装的封装部231。要使石墨片32的上表面从第1封装部231露出。

[0096]

图16d是第2实施方式的半导体装置1的第4剖视图。

[0097]

(d)接着,如图16d所示,在石墨片32上的与绝缘片30对向的面形成第2导热板36。

[0098]

(e1)继而,如图13所示,形成将封装部231、石墨片32及第2导热板36封装的第2封装部232。要使第2导热板36的上表面从第2封装部232露出。

[0099]

(e2)接着,如图13所示,在第2面21b侧形成多个焊球25。

[0100]

(第2实施方式的变化例)

[0101]

图17是第2实施方式的变化例的半导体装置的剖视图。第2实施方式的变化例的半

导体装置中,与半导体存储器12连接的键合线22m的连接结构不同。其他构成与第2实施方式的半导体装置相同。图17中省略了半导体装置1所具备的振荡器14、eeprom15、ram13及温度传感器16。以下,对与第2实施方式不同的构成进行说明。

[0102]

在第2实施方式的变化例的半导体装置中,键合线22m将多个半导体存储器12连接。另外,键合线22m将最下层的半导体存储器12z与衬底21电连接。

[0103]

第2实施方式的半导体装置1具备衬底21(封装衬底)、控制器11、半导体存储器12、键合线22m及22c、第1导热板34、第2导热板36、绝缘膜17、石墨片32、绝缘片30、封装部(塑模材料)231及232、安装膜24以及焊球25。

[0104]

根据第2实施方式的变化例,半导体装置1内置石墨片32。石墨片32之上配置有第2导热板36。能使半导体存储器12及控制器11的热经由石墨片32逸散至第2导热板36。另外,根据第2实施方式的变化例,半导体装置1具有第1导热板34与第2导热板36之间夹着石墨片32的结构。根据第2实施方式的变化例,能提高半导体存储器12及控制器11的散热速度。另外,根据第2实施方式的变化例的半导体装置,能使控制器的热有效率地向封装外部逸散。根据第2实施方式的变化例,能缓和半导体存储器的温度上升。另外,根据第2实施方式的变化例的半导体装置,通过内置石墨片,能对半导体装置1的内部进行屏蔽。另外,根据第2实施方式的半导体装置,通过内置石墨片,能提高散热性。

[0105]

(第3实施方式)

[0106]

图18是第3实施方式的半导体装置1的剖视图。另外,图19是第3实施方式的半导体装置1的俯视图。

[0107]

根据第3实施方式的半导体装置1,能使第1导热板34的热向半导体装置1的外部逸散。第3实施方式的半导体装置1中,在控制器11的上部隔着绝缘膜17配置有第1导热板34。第1导热板34的上表面从封装部231露出。

[0108]

根据第3实施方式的半导体装置1,能防止半导体装置1的内部积热。控制器11之上配置有第1导热板34以吸热。第1导热板34的上表面从封装部231露出。也就是说,设置有能使控制器11的热向半导体装置1的外部逸散的路径。

[0109]

(第4实施方式)

[0110]

图20是第4实施方式的半导体装置的剖视图。

[0111]

第4实施方式的半导体装置中,在控制器11的上部隔着绝缘膜17配置有第1导热板34。进而,第1导热板34的上表面与衬底21之间连接有键合线22t。键合线22t通过封装部23而封装。

[0112]

键合线22t是用来导热的引线。键合线22t例如为铜线、银线或金线。键合线22t的粗细例如为直径20μm~50μm左右。通过键合线22t,能使产自控制器11的热向衬底21及焊球25侧逸散。为了提高热导率,也可增加键合线22t的根数。

[0113]

根据第4实施方式的半导体装置,能使控制器的热有效率地向封装外部逸散。根据第4实施方式的半导体装置,能缓和半导体存储器的温度上升。

[0114]

(比较例)

[0115]

ssd在1个封装内搭载有soc(system-on-a-chip)与nand。因此,nand易受soc发热的影响。关于将nand与soc的热阻断的技术,已知有pop(package on package,叠层封装)及导热孔(tmv:thermal via)。pop是一种使ic(integrated circuit,集成电路)或零件积层

安装在ic封装之上的技术。tmv是一种使利用衬底的表面安装零件的散热效果提高的技术。tmv从结构上来说,是一种在衬底设置贯通孔,将衬底表面与背面的铜箔相连,增加用于散热的面积与体积,也就是降低热阻的方法。

[0116]

实施方式是例示,发明的范围并不限定于此。例如,在所述各实施例中,控制器与衬底之间是以键合线的方式接合的,但也可取而代之,以倒装芯片的方式接合。倒装芯片是不经引线,而将设置在芯片表面的凸块与基底衬底直接接合的。通过该倒装芯片接合,能缩小控制器的厚度,相应地,能将导热板厚膜化而使其散热性进一步提高。

[0117]

[符号的说明]

[0118]

1:半导体装置

[0119]

2:电子机器

[0120]

3:壳体

[0121]

4:电路衬底(主板)

[0122]

5:主机控制器(cpu)

[0123]

6:信号线

[0124]

7:电源电路

[0125]

8,8a,8b:电源线

[0126]

11:控制器

[0127]

12,12z:半导体存储器(nand)

[0128]

13:ram

[0129]

14:振荡器(osc)

[0130]

15:eeprom

[0131]

16:温度传感器

[0132]

17:绝缘膜(fow)

[0133]

21:衬底

[0134]

21a:第1面

[0135]

21b:第2面

[0136]

22m,22c,22t:键合线

[0137]

23,231,232:封装部(塑模材料)

[0138]

24:安装膜

[0139]

25:焊球

[0140]

28:电源层

[0141]

29:接地层

[0142]

30:绝缘片

[0143]

32:石墨片

[0144]

34:第1导热板

[0145]

36:第2导热板

[0146]

gf(xy):第1石墨片

[0147]

gf(xz):第2石墨片

[0148]

gf1,gf2,gf3,

…

,gfn:石墨烯

[0149]

x1:x方向的距离。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。