1.本发明涉及一种静电保护元件以及包含静电保护元件的半导体装置。

背景技术:

2.在作为半导体装置的半导体ic芯片中设置有防止与在芯片外部产生的静电放电(以下,称作esd)相伴的大电流经由电源端子流入到内部电路的esd保护电路。

3.在该esd保护电路中包含在电源线的电压值成为规定的电压值以上的高电压的情况下将电源线和接地线连接的esd保护用的晶体管。在esd保护电路中,当与esd相伴的高电压经由外部端子被施加于电源线时,esd保护用的晶体管进行动作,与该高电压相伴的电流流经该esd保护用的晶体管,施加于该晶体管的电压降低,利用被维持为某个电压(称为保持电压)这样的骤回进行内部电路的保护(例如,参照专利文献1)。

4.现有技术文献专利文献专利文献1:日本特开2016-162844号公报。

技术实现要素:

5.发明要解决的课题然而,当流入到esd保护用的晶体管的电流过大时,有时产生柯克效应。当产生柯克效应时,形成耗尽层,电流路径的电流密度变高。当在该状态下持续施加高电压时,与不产生该柯克效应的情况相比,在集电极发射极间流入大的电流,上述的保持电压变低。此时,当比该保持电压高的电源电压被施加于电源线时,在esd终止后,esd保护用的晶体管的动作仍继续。因此,基于该电源电压的电流继续流入到esd保护用的晶体管,存在向内部电路的电力供给不足或该esd保护用的晶体管本身被破坏的可能性。

6.因此,为了消除这样的不良情况,在专利文献1记载的静电保护电路中,采用在电源线和接地线间将两个esd保护用的晶体管进行级联连接的结构。在该静电保护电路中,将被级联连接的两个esd保护用的晶体管各自产生的保持电压相加后的电压成为电路上的保持电压。因此,与电源电压相比,能够使该电路上的保持电压为高电压,因此,在esd终止后,即使施加电源电压,也能够抑制流到esd保护用的晶体管的电流。

7.但是,在专利文献1所公开的结构中,为了与内部电路一起防止本身的破坏,需要两个esd保护用的晶体管,因此,存在半导体装置内的占有面积变大这样的问题。

8.因此,本发明的目的在于提供一种能够在不导致占有面积的增大以及针对内部电路的电力供给不足的情况下与内部电路一起防止本身的静电破坏的静电保护元件以及半导体装置。

9.用于解决课题的方案本发明提供一种静电保护元件,其特征在于,具有:第一导电型的半导体基板;第二导电型的高浓度源极区域,沿着所述半导体基板的表面形成,连接有传送电源电压的电

源线以及接地线中的一方;第二导电型的低浓度源极区域,具有从所述半导体基板的表面露出的露出面,与所述高浓度源极区域相接,且杂质浓度比所述高浓度源极区域低;第二导电型的高浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地沿着所述半导体基板的表面形成,连接有所述电源线以及接地线中的另一方;第二导电型的低浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地形成,具有从所述半导体基板的表面露出的露出面,与所述高浓度漏极区域相接,杂质浓度比所述高浓度漏极区域低,延伸至距所述半导体基板的表面的深度比所述低浓度源极区域深的区域;栅极绝缘膜,形成于所述低浓度源极区域以及所述低浓度漏极区域各自的所述露出面上、以及所述半导体基板的表面上的所述露出面各自之间的区域上;以及栅极电极,形成于所述栅极绝缘膜上,连接有所述电源线以及接地线中的所述一方。

10.另外,本发明提供一种静电保护元件,其特征在于,具有:第一导电型的半导体基板;第二导电型的高浓度源极区域,沿着所述半导体基板的表面形成,连接有传送电源电压的电源线以及接地线中的一方;第二导电型的低浓度源极区域,具有从所述半导体基板的表面露出的露出面,与所述高浓度源极区域相接,且杂质浓度比所述高浓度源极区域低;第二导电型的高浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地沿着所述半导体基板的表面形成,连接有所述电源线以及接地线中的另一方;第二导电型的低浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地形成,具有从所述半导体基板的表面露出的露出面,与所述高浓度漏极区域相接,且杂质浓度比所述高浓度漏极区域低;栅极绝缘膜,形成于所述低浓度源极区域以及所述低浓度漏极区域各自的所述露出面上、以及所述半导体基板的表面上的所述露出面各自之间的区域上;栅极电极,形成于所述栅极绝缘膜上,连接有所述电源线以及接地线中的所述一方;以及第二导电型的阱区域,形成于所述低浓度漏极区域的底面,且杂质浓度比所述高浓度漏极区域低。

11.本发明提供一种半导体装置,其特征在于,包含:传送电源电压的电源线以及接地线;第一导电型的半导体基板;内部电路,形成于所述半导体基板,利用经由所述电源线以及所述接地线传送的所述电源电压进行动作;以及静电保护元件,形成于所述半导体基板,所述静电保护元件具有:第二导电型的高浓度源极区域,沿着所述半导体基板的表面形成,连接有传送电源电压的电源线以及接地线中的一方;第二导电型的低浓度源极区域,具有从所述半导体基板的表面露出的露出面,与所述高浓度源极区域相接,且杂质浓度比所述高浓度源极区域低;第二导电型的高浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地沿着所述半导体基板的表面形成,连接有所述电源线以及接地线中的另一方;第二导电型的低浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地形成,具有从所述半导体基板的表面露出的露出面,与所述高浓度漏极区域相接,杂质浓度比所述高浓度漏极区域低,延伸至距所述半导体基板的表面的深度比所述低浓度源极区域深的区域;栅极绝缘膜,形成于所述低浓度源极区域以及所述低浓度漏极区域各自的所述露出面上、以及所述半导体基板的表面上的所述露出面各自之间的区域上;以及栅极电极,形成于所述栅极绝缘膜上,连接有所述电源线以及接地线中的所述一方。

12.另外,本发明提供一种半导体装置,其特征在于,包含:传送电源电压的电源线以及接地线;第一导电型的半导体基板;内部电路,形成于所述半导体基板,利用经由所述电源线以及所述接地线传送的所述电源电压进行动作;以及静电保护元件,形成于所述半导

体基板,所述静电保护元件具有:第二导电型的高浓度源极区域,沿着所述半导体基板的表面形成,连接有传送电源电压的电源线以及接地线中的一方;第二导电型的低浓度源极区域,具有从所述半导体基板的表面露出的露出面,与所述高浓度源极区域相接,且杂质浓度比所述高浓度源极区域低;第二导电型的高浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地沿着所述半导体基板的表面形成,连接有所述电源线以及接地线中的另一方;第二导电型的低浓度漏极区域,与所述高浓度源极区域以及所述低浓度源极区域分离地形成,具有从所述半导体基板的表面露出的露出面,与所述高浓度漏极区域相接,且杂质浓度比所述高浓度漏极区域低;栅极绝缘膜,形成于所述低浓度源极区域以及所述低浓度漏极区域各自的所述露出面上、以及所述半导体基板的表面上的所述露出面各自之间的区域上;栅极电极,形成于所述栅极绝缘膜上,连接有所述电源线以及接地线中的所述一方;以及第二导电型的阱区域,形成于所述低浓度漏极区域的底面,且杂质浓度比所述高浓度漏极区域低。

13.发明效果在本发明中,当施加esd造成的高电压时,在作为静电保护元件的mos晶体管的源极区域和漏极区域间寄生的双极型的寄生晶体管击穿。由此,与esd相伴的电流流入该寄生晶体管而不是流入内部电路,由此,防止内部电路的静电破坏。

14.进而,在本发明中,将与esd相伴的电流流动的寄生晶体管实现的电流路径在半导体基板的深度方向上扩展。由此,在mos晶体管的栅极氧化膜的正下的区域形成的寄生晶体管实现的电流路径的电流密度变低,在上述的寄生晶体管的击穿时引起柯克效应的电流的阈值相应变高。即,难以产生柯克效应,其结果是,与该柯克效应相伴的寄生晶体管的集电极发射极间的保持电压的降低被抑制,因此,在esd终止后,即使施加电源电压,大电流也不会流入寄生晶体管。

15.因此,根据本发明,利用作为静电保护元件的单一的mos晶体管,能够在不导致占有面积的增大以及向内部电路的电力供给不足的情况下,不仅能够防止eds带来的内部电路的破坏,而且能够防止esd终止后的本身的破坏。

附图说明

16.图1是概略地示出形成于作为本发明的半导体装置的半导体ic芯片100的电路的电路图。

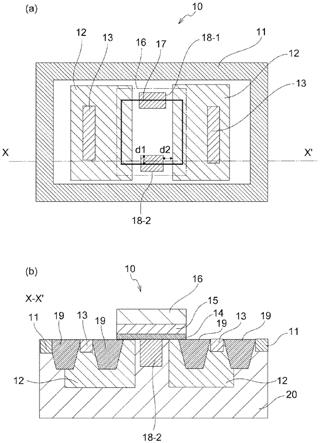

17.图2a是从半导体ic芯片100的上方观察晶体管10的俯视图。

18.图2b是表示图2a中的w-w线的晶体管10的截面的截面图。

19.图3是将在晶体管10中寄生的寄生晶体管符号化并表示在晶体管10的截面图中的图。

20.图4是表示图2a中的w-w线的晶体管10的其它截面的截面图。

具体实施方式

21.以下,参照附图详细地对本发明的实施例进行说明。

22.图1是概略地示出形成于作为本发明的半导体装置的半导体ic芯片100的电路的电路图。

23.在半导体ic芯片100形成有担当主要功能的内部电路uc和作为本发明的静电保护元件的n沟道mos(metal-oxide-semiconductor:金属氧化物半导体)型的晶体管10。进而,在该半导体ic芯片100形成有接受来自外部的电源电压的焊盘pd1以及pd2和传送由焊盘pd1以及pd2接受的电源电压的电源线vl以及接地线gl。内部电路uc利用经由电源线vl以及接地线gl传送的电源电压进行动作。

24.此外,如图1所示,晶体管10的漏极与电源线vl连接,栅极以及源极均与接地线gl连接。

25.以下,对晶体管10的结构进行说明。

26.图2a是从半导体ic芯片100的上方观察晶体管10的俯视图,图2b是沿着图2a中的w-w线的截面图。

27.如图2b所示,晶体管10形成于由p型的si(硅)构成的半导体基板11。

28.在半导体基板11的表面附近形成有担当晶体管10的源极区域的n型的高浓度源极区域12s和杂质浓度比该高浓度源极区域12s低的n型的低浓度源极区域13s。

29.高浓度源极区域12s的上表面从半导体基板11的表面露出,在设置于其上表面的触点ct连接有接地线gl。

30.低浓度源极区域13s具有从半导体基板11的表面露出的露出面,以在半导体基板11的区域内覆盖高浓度源极区域12s的侧面以及底面的方式与该高浓度源极区域12s相接。

31.另外,在半导体基板11的表面附近形成有担当晶体管10的漏极区域的n型的高浓度漏极区域12d和杂质浓度比该高浓度漏极区域12d低的n型的低浓度漏极区域13d。

32.高浓度漏极区域12d的上表面从半导体基板11的表面露出,在设置于其上表面的触点ct连接有电源线vl。

33.低浓度漏极区域13d具有从半导体基板11的表面露出的露出面,以在半导体基板11的区域内覆盖高浓度漏极区域12d的侧面以及底面的方式与该高浓度漏极区域12d相接。

34.另外,如图2b所示,在低浓度源极区域13s以及低浓度漏极区域13d各自的露出面上以及半导体基板11的表面上的上述的露出面各自之间的区域上形成有栅极绝缘膜14。在栅极氧化膜14上形成有栅极电极15。接地线gl连接于栅极电极15。

35.另外,以将形成有上述的高浓度源极区域12s、高浓度漏极区域12d、低浓度源极区域13s以及低浓度漏极区域13d的区域整体呈环状包围的方式形成有sti(shallow trench isolation:浅槽隔离)结构的元件分离绝缘膜20。

36.另外,在半导体基板11的表面附近的环状的元件分离绝缘膜20的外周的一部分区域形成有p型的高浓度扩散层21。接地线gl连接于高浓度扩散层21,经由该接地线gl以及高浓度扩散层21对晶体管10的背栅施加接地电位。

37.进而,如图2b所示,在半导体基板11的区域内的担当漏极区域的低浓度漏极区域13d的底面形成有杂质浓度比高浓度漏极区域12d低的n型的n阱30。

38.在此,n阱30如图2b所示那样,本身的侧面s1相比于高浓度漏极区域12d的与高浓度源极区域12s对置的侧面s2向源极区域(12s、13s)侧伸出。

39.以下,使用图3对由图1、图2a以及图2b所示的晶体管10进行的静电破坏保护动作进行说明。

40.图3是将在晶体管10的漏极源极间寄生的双极型的寄生晶体管符号化并表示在晶

体管10的截面图中的图。

41.首先,如图1所示,当利用在半导体ic芯片100的附近产生的esd向焊盘pd1和pd2间施加高电压时,在mos型的晶体管10的漏极源极间寄生的双极型的寄生晶体管被击穿。

42.接着,如图3所示,在晶体管10中,在低浓度源极区域13s和低浓度漏极区域13d间形成双极型的寄生晶体管,并且,经由n阱30在低浓度源极区域13s和低浓度漏极区域13d间也形成双极型的寄生晶体管。

43.当上述的寄生晶体管击穿时,与esd相伴的放电电流例如从电源线vl经由由高浓度漏极区域12d、低浓度漏极区域13d、半导体基板11的表面附近的区域、低浓度源极区域13s以及高浓度源极区域12s构成的电流路径流入到接地线gl。进而,该放电电流经由由高浓度漏极区域12d、低浓度漏极区域13d、n阱30、半导体基板11的从表面离开的区域、低浓度源极区域13s以及高浓度源极区域12s构成的电流路径流入到接地线gl。

44.因此,与esd相伴的电流不是流入到内部电路uc,而是流入图3所示的双极型的寄生晶体管实现的电流路径,由此,防止内部电路uc的静电破坏。

45.在此,在晶体管10中,利用形成于低浓度漏极区域13d的底面的n阱30,寄生晶体管击穿时的电流路径向半导体基板11的深度方向扩展。由此,在栅极氧化膜14的正下方的区域形成的寄生晶体管所实现的电流路径的电流密度变低。其结果是,相对于经由该寄生晶体管在高浓度漏极区域12d和高浓度源极区域12s间流动的电流,引起柯克效应的电流的阈值变高。因此,与没有在低浓度漏极区域13d的底面形成n阱30的情况相比,难以产生柯克效应,其结果是,与该柯克效应相伴的寄生晶体管的集电极发射极间的保持电压的降低被抑制。

46.因此,在esd终止后,即使通常的电源电压经由电源线vl以及接地线gl被施加于晶体管10,向寄生晶体管的大电流的流入也被阻止。由此,在esd终止后,基于电源电压的电流不流入到寄生晶体管而被供给到内部电路uc,因此,该内部电路uc的电力供给不足被解决,并且,作为静电保护元件的晶体管10的破坏被阻止。

47.这样,利用作为静电保护元件的单一的晶体管10,能够在不导致占有面积的增大以及向内部电路的电力供给不足的情况下防止esd造成的内部电路uc的破坏、以及esd终止后的静电保护元件(晶体管10)本身的破坏。

48.进而,在晶体管10中,如图2b所示,在沿着半导体基板11的表面的方向,使从半导体基板11的区域和低浓度漏极区域13d的边界至高浓度漏极区域12d的最短的距离l1比从该半导体基板11的区域和低浓度源极区域13s的边界至高浓度源极区域12s的最短的距离l2大。

49.此时,距离l1越大,图3所示的寄生晶体管实现的电流路径中的电阻越增加,与此相伴,引起柯克效应的电压的阈值越高,因此,与该柯克效应相伴的寄生晶体管的集电极发射极间的保持电压的降低被抑制。因此,能够更可靠地防止esd终止后的向内部电路uc的电力供给不足、以及静电保护元件(10)的破坏。

50.此外,在图2b所示的一例中,为了使击穿时的电流路径向半导体基板11的深度方向扩展而设置n阱30,但也可以不单独形成n阱30,而将低浓度漏极区域本身向半导体基板11的深度方向扩展。

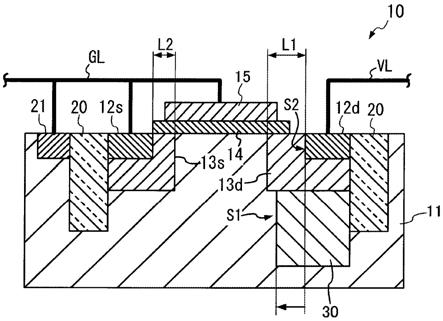

51.图4是示出鉴于该点而作出的沿着图2a中的w-w线的晶体管10的结构的截面图。

52.此外,在图4所示的结构中,除了采用低浓度漏极区域23d来代替低浓度漏极区域13d以及n阱30这一点以外的其它结构与图2b所示的结构相同。因此,以下,对图4所示的低浓度漏极区域23d的结构进行说明。

53.低浓度漏极区域23d与低浓度漏极区域13d同样地,具有从半导体基板11的表面露出的露出面,以在半导体基板11的区域内覆盖高浓度漏极区域12d的侧面以及底面的方式与该高浓度漏极区域12d相接。

54.但是,如图4所示,低浓度漏极区域23d的从半导体基板11的表面至底面的深度h1比低浓度源极区域13s的从半导体基板11的表面至底面的深度h2深。即,低浓度漏极区域23d在半导体基板11的区域内延伸至距半导体基板11的表面的深度比低浓度源极区域13s深的区域。

55.由此,与使低浓度漏极区域的深度与低浓度源极区域13s的深度h2相等的情况相比,在mos型的晶体管10中寄生的双极型的寄生晶体管击穿时的电流路径向半导体基板11的深度方向扩展。由此,在栅极氧化膜14的附近形成的寄生晶体管实现的电流路径的电流密度变低,引起柯克效应的电流的阈值相应变高。

56.因此,与低浓度漏极区域的深度与低浓度源极区域13s的深度相等的情况相比,难以产生柯克效应,其结果是,与该柯克效应相伴的寄生晶体管的集电极发射极间的保持电压的降低被抑制。

57.因此,在esd终止后,即使通常的电源电压经由电源线vl以及接地线gl被施加于晶体管10,向寄生晶体管的大电流的流入也被阻止。

58.因此,在采用了图4所示的结构的情况下,也与采用了图2b所示的结构的情况同样地,利用作为静电保护元件的单一的晶体管10,不仅能够在不导致占有面积的增大以及向内部电路的电力供给不足的情况下防止与静电放电相伴的内部电路uc的破坏,而且能够防止esd终止后的本身的破坏。

59.此外,在上述实施例中,示出了将mos型的晶体管10形成于p型导电型的半导体基板11的情况的结构,但也能够同样地形成于n型导电型的半导体基板。另外,也可以将晶体管10形成于在p型的半导体基板形成的n型的阱区域或者在n型的半导体基板形成的p型的阱区域。

60.总之,作为担当静电保护元件的晶体管10,只要采用具有以下的第一导电型的半导体基板、第二导电型的高浓度源极区域以及低浓度源极区域、第二导电型的高浓度漏极区域以及低浓度漏极区域、栅极绝缘膜以及栅极电极的晶体管即可。

61.即,高浓度源极区域(12s)沿着半导体基板(11)的表面形成,连接有传送电源电压的电源线(vl)以及接地线(gl)中的一方。低浓度源极区域(13s)是杂质浓度比高浓度源极区域低的区域,具有从半导体基板的表面露出的露出面,与上述的高浓度源极区域相接。高浓度漏极区域(12d)与这些高浓度源极区域以及低浓度源极区域分离地沿着半导体基板的表面形成,连接有传送电源电压的电源线以及接地线中的另一方。低浓度漏极区域(23d)是如下的区域:与高浓度源极区域以及低浓度源极区域分离地形成,具有从半导体基板的表面露出的露出面,与上述的高浓度漏极区域相接并且杂质浓度比高浓度漏极区域低。栅极绝缘膜(14)形成于半导体基板的表面上、低浓度源极区域以及低浓度漏极区域各自的露出面上。栅极电极(15)形成于栅极绝缘膜上,连接有电源线以及接地线中的一方。此外,低浓

度漏极区域(23d)的距半导体基板的表面的深度(h1)比低浓度源极区域(13s)的距半导体基板的表面的深度(h2)深。即,低浓度漏极区域在半导体基板的区域内延伸至距半导体基板的表面的深度比低浓度源极区域深的区域。

62.另外,作为担当静电保护元件的晶体管10,也可以采用具有以下的第一导电型的半导体基板、第二导电型的高浓度源极区域以及低浓度源极区域、第二导电型的高浓度漏极区域以及低浓度漏极区域、第二导电型的阱区域、栅极绝缘膜以及栅极电极的晶体管。

63.即,高浓度源极区域(12s)沿着半导体基板(11)的表面形成,连接有传送电源电压的电源线(vl)以及接地线(gl)中的一方。低浓度源极区域(13s)是杂质浓度比高浓度源极区域低的区域,具有从半导体基板的表面露出的露出面,与上述的高浓度源极区域相接。高浓度漏极区域(12d)与这些高浓度源极区域以及低浓度源极区域分离地沿着半导体基板的表面形成,连接有传送电源电压的电源线以及接地线中的另一方。低浓度漏极区域(23d)是如下的区域:与高浓度源极区域以及低浓度源极区域分离地形成,具有从半导体基板的表面露出的露出面,与上述的高浓度漏极区域相接并且杂质浓度比高浓度漏极区域低。阱区域(30)形成于低浓度漏极区域(13d)的底面,且杂质浓度比高浓度漏极区域低。

64.符号说明10

ꢀꢀ

晶体管12d

ꢀꢀ

高浓度漏极区域12s

ꢀꢀ

高浓度源极区域13d

ꢀꢀ

低浓度漏极区域13s

ꢀꢀ

低浓度源极区域30

ꢀꢀꢀ

n阱。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。