1.本发明的实施例是有关于一种用于超高电压的半导体器件及其制造方法。

背景技术:

2.半导体材料及设计的技术进步已产生几代半导体器件,其中每一代具有比前一代更小且更复杂的组件。然而,这些进步已增加了处理及制造半导体器件的复杂性。因此每半导体器件面积的内连组件的数量已增大,同时可使用制作工艺形成的最小组件的几何大小已减小。

技术实现要素:

3.本发明实施例提供一种制造半导体器件的方法,所述方法包括提供超高电压(uhv)组件,超高电压组件包括源极区及漏极区;在超高电压组件的顶表面上形成氧化物层;将低电压端子连接到超高电压组件的源极区;将高电压端子连接到超高电压组件的漏极区;在设置在超高电压组件的漏极区上方的氧化物层的表面上形成屏蔽结构;形成连接到屏蔽结构且连接到高电压端子的高电压内连线;以及形成连接屏蔽结构与低电压端子的金属布线。

4.本发明实施例提供一种半导体器件,包括衬底、氧化物层、低电压端子、高电压端子、屏蔽结构、高电压内连线以及金属布线。衬底包括源极区及漏极区。氧化物层形成在衬底的顶表面上。低电压端子耦合到衬底的源极区。高电压端子耦合到衬底的漏极区。屏蔽结构形成在设置在衬底的漏极区上方的氧化物层的表面上,其中屏蔽结构包括绕组多晶硅线。高电压内连线耦合到屏蔽结构且耦合到高电压端子。金属布线将屏蔽结构与低电压端子耦合。

5.本发明实施例提供一种制造半导体器件的方法,所述方法包括提供包括源极区及漏极区的衬底;在衬底的顶表面上形成氧化物层;将低电压端子连接到衬底的源极区;将高电压端子连接到衬底的漏极区,其中高电压端子被配置成接收比低电压端子被配置成接收的电压大小来得大的电压大小;在设置在衬底的漏极区上方的氧化物层的表面上形成屏蔽结构,其中屏蔽结构包括一条或多条绕组多晶硅线;形成连接到屏蔽结构且连接到高电压端子的高电压内连线;以及形成连接屏蔽结构与低电压端子的金属布线。

附图说明

6.结合附图阅读以下详细说明,会最好地理解本公开的各个方面。应注意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为使论述清晰起见,可任意增大或减小各种特征的尺寸。

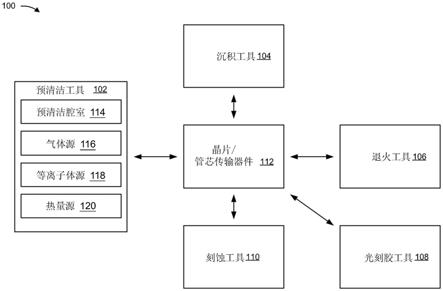

7.图1是其中可实施本文中阐述的系统和/或方法的示例性环境的图;

8.图2a到图2j是在制造本文中阐述的示例性半导体器件中涉及的一个或多个示例性操作的图;

9.图3是图1所示一个或多个工具和/或器件的示例性组件的图;

10.图4是提供用于超高电压(ultra-high voltage,uhv)半导体器件的屏蔽结构的示例性工艺的流程图;

11.图5是本文中所阐述的包括图2a到图2j所示示例性半导体器件的示例性电路的图。

具体实施方式

12.以下公开提供用于实施所提供主题的不同特征的许多不同实施例或实例。以下阐述组件及排列的具体实例以简化本公开。当然,这些仅为实例且不旨在进行限制。举例来说,以下说明中将第一特征形成在第二特征“之上”或第二特征“上”可包括其中第一特征与第二特征被形成为直接接触的实施例,且也可包括其中第一特征与第二特征之间可形成有附加特征从而使得所述第一特征与所述第二特征可不直接接触的实施例。另外,本公开可能在各种实例中重复使用参考编号和/或字母。这种重复使用是出于简洁及清晰的目的,而不是自身指示所论述的各种实施例和/或配置之间的关系。

13.此外,为易于说明,本文中可能使用例如“在

…

之下(beneath)”、“在

…

下方(below)”、“下部的(lower)”、“在

…

上方(above)”、“上部的(upper)”等空间相对性用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对性用语旨在除图中所绘示的取向外还囊括器件在使用或操作中的不同取向。装置可具有其他取向(旋转90度或处于其他取向),且本文中所使用的空间相对性描述语可同样相应地进行解释。

14.可在半导体晶片上制作各种类型的无源组件(例如,电阻器组件)。一些应用要求电阻器组件承受高电压(例如几百伏特)。然而,在获得足够高的电压之前,传统的高电压电阻器可能会经受器件击穿问题(device breakdown issue)。举例来说,传统的高电压电阻器可能依赖于使用p型/n型(p-type/n-type,p/n)结来承担击穿电压。结击穿受掺杂浓度限制,而在传统的高电压电阻器中掺杂浓度尚未得到优化。

15.场板(field plate)及p/n结可降低电阻器组件附近的电场强度。传统的高电压结终端(high-voltage junction termination,hvjt)组件包括减小的表面场(reduced surface field,resurf)结结构(junction structure)及可处理从近似0伏特(volt,v)到近似1000v的高电压内连线(high voltage interconnection,hvi)。hvi在外部hvjt区域(例如,处理从近似0v到近似100v的低侧区域)与内部hvjt区域(例如,处理从近似0v到近似1,000v的高侧区域)之间传递信号。高侧区域器件(high side area devices)(例如,金属氧化物半导体(metal-oxide semiconductor,mos)、二极管和/或类似器件)可被放置在高侧区域终端的内部(例如,内部hvjt区域)以用于高侧电路应用。在击穿电压(breakdown voltage,bv)测试期间,传统的hvjt组件会经历bv劣化问题(例如,80v bv从第一bv下降到第二bv,且稳定bv从第二bv下降到第三bv)。为解决此问题并改善hvjt组件可靠性,增加hvjt组件的电压规则(例如,s-规则(s-rule)),以增大hvjt组件的bv。然而,增加电压规则需要将hvjt组件的面积增大到近似773.4微米(例如,长度)乘以573.4微米(例如,高度),此会对较小器件的趋势起反作用。

16.根据本文中阐述的一些实施方案,一种方法可包括提供用于包括hvjt组件的超高

电压(uhv)半导体器件的屏蔽结构。举例来说,所述方法可包括:提供uhv组件,所述uhv组件包括源极区及漏极区;以及在uhv组件的顶表面上形成氧化物层。所述方法可包括:将低电压端子连接到uhv组件的源极区;以及将高电压端子连接到uhv组件的漏极区。所述方法可包括:在设置在uhv组件的漏极区上方的氧化物层的表面上形成屏蔽结构;以及形成连接到屏蔽结构且连接到高电压端子的高电压内连线。所述方法可包括:形成连接屏蔽结构与低电压端子的金属布线。

17.以此种方式,可提供用于包括hvjt组件的uhv半导体器件的屏蔽结构。可通过将植入多晶硅(polysilicon,poly)线连接到hvjt组件来形成所述屏蔽结构,此使得hvjt组件的bv更鲁棒(robust)且与传统的hvjt组件的面积相比显著减小hvjt组件的面积(例如,减小近似13%)。所述屏蔽结构有效且成功地屏蔽高电压内连线(hvi)产生的高电压电场对hvjt组件的影响。所述屏蔽结构可应用于uhv半导体器件、横向扩散金属氧化物半导体(laterally-diffused metal-oxide semiconductor,ldmos)器件和/或类似器件。

18.图1是其中可实施本文中阐述的系统和/或方法的示例性环境100的图。如图1中所示,环境100可包括预清洁工具102、沉积工具104、退火工具106、光刻胶工具108、刻蚀工具110及晶片/管芯传输器件112。示例性环境100中所包括的工具和/或器件可包括在半导体清洁室、半导体铸造厂(semiconductor foundry)、半导体处理和/或制造设施和/或类似器件中。

19.预清洁工具102包括预清洁腔室114及能够对半导体器件实行预清洁工艺以从半导体器件移除副产物层的一个或多个器件。所述一个或多个器件可包括气体源116、等离子体源118、热量源120和/或类似源。气体源116可向预清洁腔室114供应各种气体,例如氨气体、三氟化氮气体和/或类似气体。等离子体源118可产生等离子体,所述等离子体会引起被供应到预清洁腔室114的气体之间的反应。举例来说,等离子体源118可包括电感耦合等离子体(inductively coupled plasma,icp)源、变压器耦合等离子体(transformer coupled plasma,tcp)源或能够引起氨气体与三氟化氮气体之间的反应以使得形成氟化铵气体的另一类型的等离子体源。热量源120可能够对预清洁腔室114中的半导体器件进行加热,以使半导体器件上的一个或多个层分解,如本文中所阐述。举例来说,热量源120可包括热量灯(heat lamp)、加热线圈(heating coil)或对半导体器件进行加热以使半导体器件上的氟化铵层分解成氨气体及氟化氢气体的另一类型的加热器件,如本文中所阐述。

20.沉积工具104是包括半导体处理腔室以及能够将各种类型的材料沉积到半导体器件上的一个或多个器件的半导体处理工具。举例来说,沉积工具104可包括化学气相沉积器件(例如,静电喷涂器件(electrostatic spray device)、外延器件和/或另一类型的化学气相沉积器件)、物理气相沉积器件(例如,溅镀器件和/或另一类型的物理气相沉积器件)、离子植入器件和/或类似器件。在一些实施方案中,沉积工具104可将金属层沉积到半导体器件的源极区或漏极区上,可沉积接触材料以形成半导体器件的接触件和/或进行如本文中阐述的类似操作。

21.退火工具106是包括半导体处理腔室及能够对半导体器件进行加热的一个或多个器件的半导体处理工具。举例来说,退火工具106可包括快速热退火(rapid thermal annealing,rta)工具或能够对半导体器件进行加热以引起两种或更多种材料或气体之间的反应从而使材料分解的另一类型的退火工具和/或类似工具。举例来说,退火工具106可

对半导体器件进行加热以引起外延区(例如,源极区或漏极区)上的金属层发生反应且形成金属硅化物层,如本文中所阐述。

22.光刻胶工具108是基于被施加到半导体器件的光刻胶层(例如,光刻胶掩模)而从半导体器件移除材料或向半导体器件提供材料的半导体处理工具。光刻胶是在若干工艺(例如,光刻(photolithography)、光雕刻(photoengraving)和/或类似工艺)中使用以在半导体器件的表面上形成图案化涂层的光敏材料(light-sensitive material)。光刻胶工具108可使用感光性有机材料(photo-sensitive organic material)涂覆半导体器件且可将图案化掩模应用到半导体器件以阻挡光,使得感光性有机材料的仅未被掩蔽的区将被暴露到光。光刻胶工具108或另一工具(例如,刻蚀工具110)可将被称为显影剂的溶剂施加到半导体器件。在正性光刻胶的情形中,感光性有机材料被光降解且显影剂将被暴露到光的区溶解掉,从而留下放置掩模的涂层。在负性光刻胶的情形中,感光性有机材料通过光而得到增强(例如,聚合或交联),且显影剂仅将未被暴露到光的区溶解掉,从而在未放置掩模的区域中留下涂层。

23.刻蚀工具110是从半导体器件的表面移除材料的半导体处理工具。在一些实施方案中,通过抗刻蚀的掩蔽材料保护半导体器件的一部分免受刻蚀剂的影响。举例来说,掩蔽材料可包括使用光刻进行图案化的光刻胶。刻蚀工具110可对半导体器件实行湿式刻蚀工艺或干式(例如,等离子体)刻蚀工艺。在湿式刻蚀工艺中,可将半导体器件浸入一批液相(例如,湿式)刻蚀剂中,可搅动所述一批液相(例如,湿式)刻蚀剂以实现工艺控制。举例来说,可使用缓冲氢氟酸(buffered hydrofluoric acid,bhf)在硅衬底之上刻蚀二氧化硅。等离子体刻蚀工艺可基于调整等离子体的参数而以若干模式操作。举例来说,等离子体刻蚀工艺可在处于从近似0.01托到近似5托的范围内的压力下操作。等离子体产生高能自由基,高能自由基带中性电且在半导体器件的表面处发生反应。等离子体刻蚀可为各向同性的(例如,在图案化表面上呈现出与向下刻蚀速率近似相同的横向底切速率)或各向异性的(例如,呈现出比向下刻蚀速率小的横向底切速率)。等离子体的源气体可包含富含氯或氟的小分子。举例来说,四氟化碳(carbon tetra fluorine)可用于对硅进行刻蚀且氯可用于对铝进行刻蚀,三氟甲烷(trifluoro methane)可用于对二氧化硅及氮化硅和/或类似材料进行刻蚀。等离子体还可包括用于使光刻胶氧化且促进光刻胶的移除的氧气。

24.晶片/管芯传输器件112包括移动机器人、机械臂、有轨电车(tram)或轨道车(rail car)和/或以下另一类型的器件:所述另一类型的器件用于在半导体处理工具102到110之间传输晶片和/或管芯、和/或将晶片和/或管芯传输到其他位置(例如晶片架(wafer rack)、储藏室和/或类似位置)以及从所述其他位置传输晶片和/或管芯。在一些实施方案中,晶片/管芯传输器件112可为行进特定路径的编程器件和/或可半自主操作或自主操作。

25.提供图1中所示的器件的数目及排列作为一个或多个实例。实际上,与图1中所示的器件相比,可存在附加的器件、更少的器件、不同的器件或不同排列的器件。此外,图1中所示的两个或更多个器件可在单个器件内实施,或者图1中所示的单个器件可被实施成多个分布式器件。另外地或作为另外一种选择,环境100的一组器件(例如,一个或多个器件)可实行被阐述为由环境100的另一组器件实行的一种或多种功能。

26.图2a到图2j是在制造本文中阐述的示例性半导体器件(例如,uhv半导体器件、ldmos器件和/或类似器件)中涉及的一个或多个示例性操作200的图。如图2a中且由参考编

号202所示,半导体器件可提供uhv组件(例如,hvjt组件),所述uhv组件包括具有第一类型的阱的源极区204及具有第二类型的阱的漏极区206。如进一步所示,源极区204可包括第一类型的阱(例如,p型阱208)。

27.p型阱208可包含掺杂有掺杂剂材料(例如,硼、铝、镓、铟和/或类似材料)的材料(例如,硅、锗、碳化硅、硅锗和/或类似材料)。掺杂是出于调制半导体材料的电性质、光学性质和/或结构性质的目的而有意将杂质引入到本征半导体材料。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行形成用于p型阱208的半导体材料的沉积操作。也可利用沉积工具104(例如,离子植入工具)在半导体材料中植入掺杂剂材料且形成p型阱208。

28.如图2a中进一步所示,漏极区206可包括第二类型的阱(例如,n型阱210)、形成在n型阱210中的第一类型的阱(例如,p型阱212)。n型阱210可包含掺杂有掺杂剂材料(例如,锑、砷、磷、铋、锂和/或类似材料)的材料(例如,硅、锗、碳化硅、硅锗和/或类似材料)。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行形成用于n型阱210的半导体材料的沉积操作。也可利用沉积工具104(例如,离子植入工具)在半导体材料中植入掺杂剂材料且形成n型阱210。

29.p型阱212可包含掺杂有掺杂剂材料(例如,硼、铝、镓、铟和/或类似材料)的材料(例如,硅、锗、碳化硅、硅锗和/或类似材料)。在一些实施方案中,可利用环境100的沉积工具104在半导体材料中植入掺杂剂材料且在n型阱210内形成p型阱212。

30.如图2a中进一步所示,半导体器件可包括具有第二类型的阱(例如,n型阱216)、形成在n型阱216上的第一类型的阱(例如,p型阱218)的中央区。n型阱216可包含掺杂有掺杂剂材料(例如,锑、砷、磷、铋、锂和/或类似材料)的材料(例如,硅、锗、碳化硅、硅锗和/或类似材料)。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行形成用于n型阱216的半导体材料的沉积操作。也可利用沉积工具104(例如,离子植入工具)在半导体材料中植入掺杂剂材料且形成n型阱216。

31.p型阱218可包含掺杂有掺杂剂材料(例如,硼、铝、镓、铟和/或类似材料)的材料(例如,硅、锗、碳化硅、硅锗和/或类似材料)。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行在n型阱216上形成p型阱218的沉积操作。也可利用沉积工具104(例如,离子植入工具)在半导体材料中植入掺杂剂材料且形成p型阱218。

32.如图2b中且由参考编号220所示,可在uhv组件的顶表面上形成氧化物层222。举例来说,可在p型阱208的顶表面、n型阱210的顶表面及p型阱218的顶表面上形成氧化物层222。氧化物层222可包含介电材料,例如氧化硅、二氧化硅、氟化硅石玻璃、硅、氮化硅和/或类似材料。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)在p型阱208的顶表面、n型阱210的顶表面及p型阱218的顶表面上形成氧化物层222。在一些实施方案中,可利用环境100的刻蚀工具110(以上结合图1阐述)在p型阱208的顶表面、n型阱210的顶表面及p型阱218的顶表面上形成氧化物层222的形状。举例来说,刻蚀工具110可在沉积氧化物层222的材料之前对p型阱208的一些部分、n型阱210的一些部分及p型阱218的一些部分进行刻蚀。

33.如图2c中且由参考编号224所示,可在氧化物层222上形成栅极多晶硅结构226。栅极多晶硅结构226可设置在源极区204及漏极区206上方且可用作栅极结构。栅极多晶硅结

构226可由多晶硅形成。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)在氧化物层222上形成栅极多晶硅结构226。

34.如图2d中且由参考编号228所示,可在设置在uhv组件的漏极区206上方的氧化物层222的表面上形成屏蔽结构230。在一些实施方案中,屏蔽结构230包含绕组型植入多晶硅材料。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)在设置在uhv组件的漏极区206上方的氧化物层222的表面上形成屏蔽结构230。以下结合图2h到图2j提供屏蔽结构230的进一步细节。

35.如图2e中且由参考编号232所示,可对氧化物层222的多个部分进行掺杂以形成在p型阱208上形成的源极接触件234、在n型阱210上形成的漏极接触件236及在p型阱218上形成的中央接触件238。源极接触件234、漏极接触件236及中央接触件238可形成在氧化物层222的表面的下方,使得氧化物层222将源极接触件234、漏极接触件236及中央接触件238与半导体器件的其他组件电绝缘。

36.源极接触件234可包含导电金属,例如钛、钴、钨、铝、铜、钌、铱和/或类似材料。在一些实施方案中,源极接触件234可形成在p型阱208的顶表面上。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行在p型阱208的顶表面上形成源极接触件234的沉积操作。在一些实施方案中,可利用环境100的刻蚀工具110(以上结合图1阐述)在p型阱208的顶表面上形成源极接触件234的形状。源极接触件234或源极接触件234的一部分可掺杂有掺杂剂材料(例如,硼、铝、镓、铟和/或类似材料),以形成p型源极接触件234。也可利用沉积工具104(例如,离子植入工具)在源极接触件234中植入掺杂剂材料且形成p型源极接触件234。

37.漏极接触件236可包含导电金属,例如钛、钴、钨、铝、铜、钌、铱和/或类似材料。在一些实施方案中,漏极接触件236可形成在n型阱210的顶表面上。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行在n型阱210的顶表面上形成漏极接触件236的沉积操作。在一些实施方案中,可利用环境100的刻蚀工具110(以上结合图1阐述)在n型阱210的顶表面上形成漏极接触件236的形状。漏极接触件236可掺杂有掺杂剂材料(例如,锑、砷、磷、铋、锂和/或类似材料),以形成n型漏极接触件236。可利用沉积工具104(例如,离子植入工具)在漏极接触件236中植入掺杂剂材料且形成n型漏极接触件236。

38.中央接触件238可包含导电金属,例如钛、钴、钨、铝、铜、钌、铱和/或类似材料。在一些实施方案中,可在p型阱218的顶表面上形成一个或多个中央接触件238。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行在p型阱218的顶表面上形成中央接触件238的沉积操作。在一些实施方案中,可利用环境100的刻蚀工具110(以上结合图1阐述)在p型阱218的顶表面上形成中央接触件238的形状。中央接触件238可掺杂有掺杂材料(例如,硼、铝、镓、铟和/或类似材料),以形成p型中央接触件238。可利用沉积工具104(例如,离子植入工具)在中央接触件238中植入掺杂剂材料且形成p型中央接触件238。

39.如图2f中且由参考编号240所示,可将低电压端子242连接到uhv组件的源极区204,且可将两个高电压端子244及246分别连接到uhv组件的漏极区206及中央区。

40.低电压端子242可包含导电金属,例如钛、钴、钨、铝、铜、钌、铱和/或类似材料。在一些实施方案中,低电压端子242可被形成为与源极接触件234连接。低电压端子242可提供处理从近似0v到近似20v的(例如,uhv组件的)低侧区域。在一些实施方案中,可利用环境

100的沉积工具104(以上结合图1阐述)实行形成低电压端子242以与源极接触件234连接的沉积操作。

41.高电压端子244及246可包含导电金属,例如钛、钴、钨、铝、铜、钌、铱和/或类似材料。在一些实施方案中,高电压端子244及246可被形成为分别与漏极接触件236及中央接触件238连接。第一高电压端子244可提供处理从近似20v到近似1,000v的(例如,uhv组件的)高侧区域。第二高电压端子246可提供处理从近似0v到近似980v的(例如,uhv组件的)高侧区域。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1所述)实行形成高电压端子244及246以分别与漏极接触件236及中央接触件238连接的沉积操作。

42.如图2g中且由参考编号248所示,可形成高电压内连线(hvi)250,且高电压内连线(hvi)250连接到屏蔽结构230且连接到高电压端子244及246中的一者。如参考编号248进一步所示,可形成金属布线252且金属布线252连接到屏蔽结构230及低电压端子242。可包括金属布线252以用于器件端子的内部连接。

43.hvi 250可包含导电金属,例如钛、钴、钨、铝、铜、钌、铱和/或类似材料。在一些实施方案中,hvi 250可处理从近似0v到近似1,000v。hvi 250可在uhv组件的外部区域(例如,处理从近似0v到近似20v的低电压端子242)与uhv组件的内部区域(例如,处理从近似20v到近似1,000v的高电压端子244或处理从近似0v到近似980v的高电压端子246)之间传递信号。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行形成hvi 250以与屏蔽结构230连接且与高电压端子244及246中的一者连接的沉积操作。在一些实施方案中,屏蔽结构230被配置成对由hvi 250产生的高电压电场进行屏蔽,以维持uhv组件的击穿电压稳定性。

44.金属布线252可包含导电金属,例如钛、钴、钨、铝、铜、钌、铱和/或类似材料。在一些实施方案中,金属布线252可处理从近似0v到近似20v,此可来自uhv组件的外部区域(例如,处理从近似0v到近似20v的低电压端子242)。在一些实施方案中,可利用环境100的沉积工具104(以上结合图1阐述)实行形成金属布线252以与屏蔽结构230连接且与低电压端子242连接的沉积操作。

45.图2h提供图2a到图2g中所示的半导体器件(例如,uhv组件)的俯视平面图。如图所示,半导体器件可包括处理从近似0v到近似20v的低侧电路(例如,由低电压端子242提供)。半导体器件还可包括处理从近似0v到近似1,000v的高侧电路(例如,由高电压端子244及246提供)。如图2h中进一步所示,hvi 250可连接到高电压端子244,但也可或者作为另外一种选择连接到高电压端子246。图2h中所绘示的屏蔽结构230可包括一端连接到源极区204且另一端连接到漏极区206的单条绕组多晶硅线。在一些实施方案中,可以允许uhv组件的面积相对于不具有屏蔽结构230的uhv组件减小近似13%的方式对屏蔽结构230进行设计。

46.图2i提供屏蔽结构230的不同实施方案的俯视平面图。如图所示,屏蔽结构230可包括单条绕组多晶硅线254(例如,所述线中不具有u形匝(u-turn))、单条绕组多晶硅线256(例如,所述线中具有u形匝)、两条绕组多晶硅线258、四条绕组多晶硅线260和/或类似绕组多晶硅线。如图2i中进一步所示,绕组多晶硅线254或绕组多晶硅线256的一个端(例如,端“a”)可连接到漏极区206(例如,高电压端子244或246)且绕组多晶硅线254或绕组多晶硅线256的另一端(例如,端“b”)可连接到源极区204(例如,低电压端子242)。两条绕组多晶硅线258的两个端(例如,端“a”)可连接到漏极区206(例如,高电压端子244或246)且两条绕组多

diode,led))。

53.通信组件370包括类似收发器的组件(例如,收发器和/或单独的接收器与发射器),所述类似收发器的组件使得器件300能够例如经由有线连接、无线连接或有线连接与无线连接的组合而与其他器件进行通信。通信组件370可允许器件300从另一器件接收信息和/或向另一器件提供信息。举例来说,通信组件370可包括以太网(ethernet)界面、光学界面、同轴界面(coaxial interface)、红外界面、射频(radio frequency,rf)界面、通用串行总线(universal serial bus,usb)界面、无线局域网界面、蜂窝式网络界面和/或类似界面。

54.器件300可实行本文中阐述的一个或多个工艺。器件300可基于处理器320执行由非暂时性计算机可读介质(例如存储器330和/或存储组件340)存储的软件指令来实行这些工艺。计算机可读介质在本文中被定义为非暂时性存储器器件。存储器器件包括单个实体存储器件内的存储器空间或跨越多个实体存储器件分布的存储器空间。

55.可经由通信组件370将软件指令从另一计算机可读介质或从另一器件读取到存储器330和/或存储组件340中。在被执行时,存储在存储器330和/或存储组件340中的软件指令可使处理器320实行本文中阐述的一个或多个工艺。另外地或作为另外一种选择,可使用硬布线电路系统(hardwired circuitry)来代替软件指令或者与软件指令结合来实行本文中阐述的一个或多个工艺。因此,本文中阐述的实施方案并不限于硬件电路系统与软件的任何特定组合。

56.提供图3中所示的组件的数目及排列作为实例。实际上,与图3中所示的组件相比,器件300可包括附加的组件、更少的组件、不同的组件或不同排列的组件。另外地或作为另外一种选择,器件300的一组组件(例如,一个或多个组件)可实行被阐述为由器件300的另一组组件实行的一个或多个功能。

57.图4是提供用于uhv半导体器件的屏蔽结构的示例性工艺400的流程图。在一些实施方案中,图4所示一个或多个工艺区块可由器件(例如,图1中所绘示的工具中的一者或多者)实行。在一些实施方案中,图4所示一个或多个工艺区块可由与图1中所绘示的所述一个或多个工具分离或包括所述一个或多个工具的另一器件或器件群组来实行。另外地或作为另外一种选择,图4所示一个或多个工艺区块可由器件300的一个或多个组件(例如处理器320、存储器330、存储组件340、输入组件350、输出组件360、通信组件370和/或类似组件)来实行。

58.如图4中所示,工艺400可包括提供包括源极区及漏极区的uhv组件(区块410)。举例来说,所述器件可提供包括源极区204及漏极区206的uhv组件,如上所述。

59.如图4中进一步所示,工艺400可包括在uhv组件的顶表面上形成氧化物层(区块420)。举例来说,所述器件可在uhv组件的顶表面上形成氧化物层222,如上所述。

60.如图4中进一步所示,工艺400可包括在设置在uhv组件的漏极区上方的氧化物层的表面上形成栅极多晶硅结构及屏蔽结构(区块430)。举例来说,所述器件可在设置在uhv组件的漏极区204上方的氧化物层222的表面上形成栅极多晶硅结构226及屏蔽结构230,如上所述。

61.如图4中进一步所示,工艺400可包括对氧化物层进行掺杂以形成源极接触件、漏极接触件及中央接触件(区块440)。举例来说,所述器件可对氧化物层222进行掺杂以形成

源极接触件234、漏极接触件236及中央接触件238,如上所述。

62.如图4中进一步所示,工艺400可包括将低电压端子连接到uhv组件的源极区中的源极接触件(区块450)。举例来说,所述器件可将低电压端子242连接到uhv组件的源极区204中的源极接触件234,如上所述。

63.如图4中进一步所示,工艺400可包括将高电压端子连接到uhv组件的漏极区中的漏极接触件(区块460)。举例来说,所述器件可将高电压端子244连接到uhv组件的漏极区206中的漏极接触件236,如上所述。

64.如图4中进一步所示,工艺400可包括形成连接到屏蔽结构且连接到高电压端子的高电压内连线(区块470)。举例来说,所述器件可形成连接到屏蔽结构230且连接到高电压端子244的高电压内连线250,如上所述。

65.如图4中进一步所示,工艺400可包括形成连接屏蔽结构与低电压端子的金属布线(区块480)。举例来说,所述器件可形成连接屏蔽结构230与低电压端子242的金属布线252,如上所述。

66.工艺400可包括附加的实施方案,例如以下阐述的和/或结合本文中别处阐述的一个或多个其他工艺的任何单个实施方案或实施方案的任意组合。

67.在第一实施方案中,源极区204包括第一类型的阱208且漏极区206包括第二类型的阱210,其中第一类型的阱与第二类型的阱不同。在第二实施方案(单独的实施方案或与第一实施方案结合的实施方案)中,屏蔽结构230包含绕组型植入多晶硅材料。在第三实施方案(单独的实施方案或与第一实施方案及第二实施方案中的一者或多者结合的实施方案)中,屏蔽结构230包括单条绕组多晶硅线254、256、两条绕组多晶硅线258或四条绕组多晶硅线260中的一者。

68.在第四实施方案(单独的实施方案或与第一实施方案到第三实施方案中的一者或多者结合的实施方案)中,屏蔽结构230被配置成对由高电压内连线250产生的高电压电场进行屏蔽,以维持器件的击穿电压稳定性。在第五实施方案(单独的实施方案或与第一实施方案到第四实施方案中的一者或多者结合的实施方案)中,uhv组件包括高电压结终端244、246。

69.在第六实施方案(单独的实施方案或与第一实施方案到第五实施方案中的一者或多者结合的实施方案)中,屏蔽结构230被配置成将uhv组件的面积相对于不具有屏蔽结构的uhv组件减小近似13%。在第七实施方案(单独的实施方案或与第一实施方案到第六实施方案中的一者或多者结合的实施方案)中,绕组多晶硅线包括处于从近似0.05微米到近似7.5微米的范围内的宽度。在第八实施方案(单独的实施方案或与第一实施方案到第七实施方案中的一者或多者结合的实施方案)中,绕组多晶硅线包括大于或等于近似0.05微米的长度。

70.在第九实施方案(单独的实施方案或与第一实施方案到第八实施方案中的一者或多者结合的实施方案)中,绕组多晶硅线包括处于从近似0.03微米到近似4.5微米的范围内的至少一个间隔。在第十实施方案(单独的实施方案或与第一实施方案到第九实施方案中的一者或多者结合的实施方案)中,绕组多晶硅线包括处于从近似一度到近似三十度的范围内的至少一个弯曲角度。在第十一实施方案(单独的实施方案或与第一实施方案到第十实施方案中的一者或多者结合的实施方案)中,屏蔽结构230包括多条绕组多晶硅线。

71.在第十二实施方案(单独的实施方案或与第一实施方案到第十一实施方案中的一者或多者结合的实施方案)中,绕组多晶硅线包括零个或多个u形匝。在第十三实施方案(单独的实施方案或与第一实施方案到第十二实施方案中的一者或多者结合的实施方案)中,所述器件可包括超高电压半导体器件或横向扩散金属氧化物半导体器件中的一者。在第十四实施方案(单独的实施方案或与第一实施方案到第十三实施方案中的一者或多者结合的实施方案)中,所述一条或多条绕组多晶硅线包括多条绕组多晶硅线,所述多条绕组多晶硅线分别在各自的第一端连接到高电压端子244且在各自的第二端连接到低电压端子242。在第十五实施方案(单独的实施方案或与第一实施方案到第十四实施方案中的一者或多者结合的实施方案)中,uhv组件包括高电压结终端244、246。

72.尽管图4示出工艺400的示例性区块,然而在一些实施方案中,与图4中所绘示的区块相比,工艺400可包括附加的区块、更少的区块、不同的区块或不同排列的区块。另外地或作为另外一种选择,可并行实行工艺400的区块中的两者或更多者。

73.图5是本文中所阐述的包括图2a到图2j所示示例性半导体器件(例如,包括屏蔽结构230的hvjt器件)的示例性电路500的图。电路500可为或可包括例如高侧栅极驱动器电路(high-side gate driver circuit)。如图5中所示,电平移位器(level shifter)可包括第一高电压金属氧化物半导体(high voltage metal-oxide semiconductor,hvmos)器件502a及第二hvmos器件502b。电平移位器还可包括第一电阻器504a及第二电阻器504b。在一些实施方案中,第一hvmos器件502a及第二hvmos器件502b是n沟道横向扩散金属氧化物半导体(ldmos)晶体管。第一hvmos器件502a及第一电阻器504a从高侧供应节点506(例如,hs_vdd)串联电耦合到低电压返回节点508(例如,lv_vss),使得第一hvmos器件502a通过第一电阻器504a而与高侧供应节点506隔开。相似地,第二hvmos器件502b及第二电阻器504b从高侧供应节点506串联电耦合到低电压返回节点508,使得第二hvmos器件502b通过第二电阻器504b而与高侧供应节点506隔开。在一些实施方案中,低电压返回节点508电耦合到地510。

74.边沿脉冲发生器(edge pulse generator)512由低电压电源514供电且基于高侧输入信号516控制第一hvmos器件502a的栅极及第二hvmos器件502b的栅极。高侧输入信号516是在0伏特与低电压电源514的电压之间变化的二进制信号。低电压电源514具有电耦合到低电压供应节点518(例如,lv_vdd)的阳极及电耦合到低电压返回节点508的阴极。低电压电源514可为例如直流(direct current,dc)电源和/或可例如供应介于约1伏特到20伏特之间、介于约1伏特到10伏特之间、介于约10伏特到20伏特之间或小于约20伏特的低电压。边沿脉冲发生器512检测高侧输入信号516的上升沿且进一步检测高侧输入信号516的下降沿。此外,边沿脉冲发生器512产生上升沿信号520a及下降沿信号520b。上升沿信号520a在所检测的上升沿中的每一者处具有脉冲且选通(gates)第一hvmos器件502a的栅极。下降沿信号520b在所检测的下降沿中的每一者处具有脉冲且选通第二hvmos器件502b的栅极。

75.置位-复位(set-reset,s-r)锁存器522由第一hvmos器件502a与第一电阻器504a的共享节点处的置位信号524a进行置位,且进一步由第二hvmos器件502b与第二电阻器504b的共享节点处的复位信号524b进行复位。在一些实施方案中,置位信号524a及复位信号524b在传送到s-r锁存器522之前通过噪声滤波器(未示出)进行传送。s-r锁存器522的反

相输出(例如,q)对栅极驱动器526进行控制以使栅极驱动器526在接通状态(on state)与关断状态(off state)之间选择性地切换。举例来说,当s-r锁存器522的反相输出指示二进制“0”时,栅极驱动器526可处于接通状态,且当s-r锁存器522的反相输出指示二进制“1”时,栅极驱动器526可处于关断状态。在一些实施方案中,栅极驱动器526是或包括互补金属氧化物半导体(complementary metal-oxide semiconductor,cmos)反相器。在一些实施方案中,栅极驱动器526包括从高侧供应节点506到高侧返回(例如,hs_vss)节点530串联连接的p沟道金属氧化物半导体场效晶体管(metal-oxide semiconductor field-effect transistor,mosfet)528p及n沟道mosfet 528n,使得p沟道mosfet 528p将n沟道mosfet 528n与高侧供应节点506隔开。

76.在一些实施方案中,复合结构是正方形环形、矩形环形、三角形环形、圆形环形或一些其他闭合路径形状。此外,复合结构被集成电路(ic)管芯532的低电压区域环绕。高侧区域容置s-r锁存器522、栅极驱动器526、第一电阻器504a及第二电阻器504b,而低电压区域容置边沿脉冲发生器512。包括屏蔽结构的hvjt器件是或包括二极管546且将低电压区域与高侧区域电隔开。在一些实施方案中,二极管546的阴极电耦合到高侧供应节点506和/或二极管546的阳极电耦合到低电压返回节点508。

77.自举电容器(bootstrap capacitor)534从高侧供应节点506电耦合到高侧返回节点530。在栅极驱动器526处于关断状态时,自举电容器534由低电压电源514通过自举二极管536进行充电。此外,自举电容器534在高侧区域处为器件(例如,s-r锁存器522)供电以使栅极驱动器526改变为接通状态。高侧电源538电耦合到低电压返回节点508且通过第一功率mosfet 540选择性地电耦合到高侧返回节点530。在一些实施方案中,作为另外一种选择,可使用绝缘栅极双极晶体管(insulated-gate bipolar transistor,igbt)或一些其他切换器件代替第一功率mosfet 540。高侧电源538可为例如dc电源和/或可例如供应介于约300伏特到1200伏特之间、介于约300伏特到750伏特之间、介于约750伏特到1200伏特之间、介于约550伏特到650伏特之间或超过300伏特的高电压。第一功率mosfet 540由栅极驱动器526的输出进行闸控且可为例如n沟道功率mosfet。在一些实施例中,栅极驱动器526的输出位于由p沟道mosfet528p与n沟道mosfet 528n共享的节点处。

78.自举二极管(bootstrap diode)536对低电压供应节点514与高侧供应节点506之间的电流流动进行限制。在高侧供应节点506处于比低电压供应节点518低的电压电平时,自举二极管536使得电流能够从低电压供应节点518流动到高侧供应节点506。此可在栅极驱动器526处于关断状态时发生且使得能够对自举电容器534进行充电。此外,在高侧供应节点506处于比低电压供应节点518高的电压电平时,自举二极管536阻止电流在低电压供应节点518与高侧供应节点506之间流动。此可在栅极驱动器526处于接通状态时发生且防止低电压区域处的器件被高侧电源538的高电压损坏。

79.在操作中,为禁用第一功率mosfet 540,高侧输入信号516从二进制“1”改变为二进制“0”,从而对s-r锁存器522进行复位。在对s-r锁存器522进行复位之后,s-r锁存器522在反相输出处输出二进制“1”,此会禁用p沟道mosfet 528p且启用n沟道mosfet 528n。此使第一功率mosfet 540的栅极及第一功率mosfet 540的源极电短路,从而禁用第一功率mosfet 540。另外,高侧返回节点530电耦合到低电压返回节点508。在一些实施例中,此种电耦合由第二功率mosfet 542或一些其他切换器件来实行。第二功率mosfet 542由低侧输

入信号544进行闸控,低侧输入信号544可例如由低侧栅极驱动器电路产生。由于自举电容器534已被大量放电且高侧返回节点530电耦合到低电压返回节点508,因此与低电压供应节点518的电压相比,高侧供应节点506处的电压是低的。因此,自举二极管536在正向偏置状态中操作且使得电流能够在低电压供应节点518与高侧供应节点506之间流动。此转而会从低电压电源514对自举电容器534进行充电。

80.为启用第一功率mosfet 540,高侧返回节点530与低电压返回节点508电隔开,使得高侧返回节点530是浮动的。在一些实施方案中,此种电分隔由第二功率mosfet 542实行。高侧返回节点530向上浮动,由此自举二极管536移动到反向偏置状态。此外,高侧输入信号516从二进制“0”改变为二进制“1”。此种改变会对s-r锁存器522进行置位,使得s-r锁存器522的反相输出位于二进制“0”处。反相输出会启用p沟道mosfet 528p且启用n沟道mosfet 528n,此将自举电容器534从第一功率mosfet 540的栅极电耦合到第一功率mosfet 540的源极。自举电容器534中累积的电荷会启用第一功率mosfet 540,此将高侧电源538电耦合到高侧返回节点530。此将高侧供应节点506处的电压改变为高侧电源538的电压加上自举电容器534两端的电压。

81.如上所述,提供图5仅作为实例。其他实例可不同于针对图5阐述的实例。

82.以此种方式,可提供用于包括hvjt组件的uhv半导体器件的屏蔽结构230。可通过将植入多晶硅(poly)线连接到hvjt组件(例如,高电压端子242)形成屏蔽结构230,此使得hvjt组件的bv更加鲁棒且使hvjt组件的面积与传统的hvjt组件的面积相比显著减小(例如,减小近似13%)。屏蔽结构230有效且成功地屏蔽了hvi 250产生的高电压电场对hvjt组件的影响。屏蔽结构230可应用于uhv半导体器件、ldmos器件和/或类似器件。

83.如以上所更详细阐述,本文中阐述的一些实施方案提供一种制造半导体器件的方法。所述方法可包括:提供超高电压(uhv)组件,所述超高电压组件包括源极区及漏极区;以及在所述uhv组件的顶表面上形成氧化物层。所述方法可包括:将低电压端子连接到所述uhv组件的所述源极区;以及将高电压端子连接到所述uhv组件的所述漏极区。所述方法可包括:在设置在所述uhv组件的所述漏极区上方的所述氧化物层的表面上形成屏蔽结构;以及形成连接到所述屏蔽结构且连接到所述高电压端子的高电压内连线。所述方法可包括:形成连接所述屏蔽结构与所述低电压端子的金属布线。

84.在一些实施例中,所述源极区包括第一类型的阱且所述漏极区包括第二类型的阱,其中所述第一类型的阱与所述第二类型的阱不同。在一些实施例中,所述屏蔽结构包含绕组型植入多晶硅材料。在一些实施例中,所述屏蔽结构包括以下中的一者:单条绕组多晶硅线,两条绕组多晶硅线,或者四条绕组多晶硅线。在一些实施例中,所述屏蔽结构被配置成对由所述高电压内连线产生的高电压电场进行屏蔽,以维持所述半导体器件的击穿电压稳定性。在一些实施例中,所述超高电压组件包括高电压结终端。在一些实施例中,所述屏蔽结构被配置成将所述超高电压组件的面积相对于不具有所述屏蔽结构的超高电压组件减小近似13%。

85.如以上所更详细阐述,本文中阐述的一些实施方案提供一种半导体器件。所述半导体器件可包括:衬底,包括源极区及漏极区;以及氧化物层,形成在所述衬底的顶表面上。所述半导体器件可包括:低电压端子,耦合到所述衬底的所述源极区;以及高电压端子,耦合到所述衬底的所述漏极区。所述半导体器件可包括:屏蔽结构,形成在设置在所述衬底的

所述漏极区上方的所述氧化物层的表面上,其中所述屏蔽结构包括绕组多晶硅线。所述半导体器件可包括:高电压内连线,耦合到所述屏蔽结构且耦合到所述高电压端子;以及金属布线,将所述屏蔽结构与所述低电压端子耦合。

86.在一些实施例中,所述绕组多晶硅线包括处于从近似0.05微米到近似7.5微米的范围内的宽度。在一些实施例中,所述绕组多晶硅线包括大于或等于近似0.05微米的长度。在一些实施例中,所述绕组多晶硅线包括处于从近似0.03微米到近似4.5微米的范围内的至少一个间距。在一些实施例中,所述绕组多晶硅线包括处于从近似一度到近似三十度的范围内的至少一个弯曲角度。在一些实施例中,所述屏蔽结构包括多条绕组多晶硅线。在一些实施例中,所述绕组多晶硅线包括零个或多个u形匝。

87.如以上所更详细阐述,本文中阐述的一些实施方案提供一种制造半导体器件的方法。所述方法可包括:提供包括源极区及漏极区的衬底;以及在所述衬底的顶表面上形成氧化物层。所述方法可包括:将低电压端子连接到所述衬底的所述源极区;以及将高电压端子连接到所述衬底的所述漏极区,其中所述高电压端子被配置成接收比所述低电压端子被配置成接收的电压大小大的电压大小。所述方法可包括:在设置在所述衬底的所述漏极区上方的所述氧化物层的表面上形成屏蔽结构,其中所述屏蔽结构包括一条或多条绕组多晶硅线。所述方法可包括:形成连接到所述屏蔽结构且连接到所述高电压端子的高电压内连线;以及形成连接所述屏蔽结构与所述低电压端子的金属布线。

88.在一些实施例中,所述半导体器件包括超高电压半导体器件或横向扩散金属氧化物半导体器件中的一者。在一些实施例中,所述一条或多条绕组多晶硅线包括多条绕组多晶硅线,所述多条绕组多晶硅线分别在各自的第一端连接到所述高电压端子且在各自的第二端连接到所述低电压端子。在一些实施例中,所述衬底包括高电压结终端。在一些实施例中,所述一条或多条绕组多晶硅线中的每一者包括处于从近似0.05微米到近似7.5微米的范围内的宽度。在一些实施例中,所述一条或多条绕组多晶硅线中的每一者包括:大于或等于近似0.05微米的长度,处于从近似0.03微米到近似4.5微米的范围内的至少一个间距,以及处于从近似一度到近似三十度的范围内的至少一个弯曲角度。

89.以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,他们可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下对本文进行各种改变、代替及变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。