用于长主机路由的替代电路装置

背景技术:

1.用于联网和其他通信基础设施的高速通信正不断改进,以促进云计算、云存储、视频会议、流式传输和其他应用。例如,当今的基础设施的传输速率通常以吉比特每秒(gb/s)来度量。为了满足这些高带宽能力,必须设计物理(phy)层以促进通过路由通路的数据交换。

2.尽管有传输速率中的提高,但用于联网和存储的生态系统仍然是成本敏感的,这限制了高速联网和存储系统的部件的材料和设计选择。特别地,印刷电路板(pcb)被广泛用于联网和存储系统中,以将信号和数据路由到适当的电路。然而,即使在对高速数据传输的要求增加时,市场也将不容忍增加pcb成本和/或复杂性。

附图说明

3.本发明的前述方面和许多的伴随的优点将变得更容易理解,因为在结合附图时通过参考以下详细描述,本发明的前述方面和许多的伴随的优点变得更好理解,其中相同的参考编号贯穿各种视图指代相同的部分,除非另外指定:图1图示了从集成电路(ic)到连接器的10英寸的基线距离(reach)的实施例;图2图示了根据本公开的实施例的承载高速数据通道的球栅阵列(bga)挠性(flex)电路的实施例。

4.图3是图示了与低成本服务器pcb相比的高成本优化的pcb结构的少大约50%的信号衰减的图;图4是图示了使用根据一个实施例的挠性电路技术的10英寸主机距离与低成本非优化pcb上的10英寸主机距离相比的好大约50%的信号衰减的图;图5是展示具有挠性电路装置的一个实施例的满足ieee标准802.3条款110 (25gbase-cr)发射机规范的部分的图;图6是示出了针对具有非优化的层结构的低成本pcb上的10英寸距离的基线装置不满足ieee标准802.3条款110 (25gbase-cr)发射机规范的图;图7图示了具有顶板挠性电路的示例电路组件;图8图示了具有对板挠性电路的封装的示例电路组件;图9图示了具有顶部柔性双轴向附件的示例电路组件;图10图示了具有顶部封装柔性双轴向组件的示例电路组件;以及图11图示了具有底部柔性双轴向附件的示例电路组件。

具体实施方式

5.本文中描述了用于利用柔性(挠性)电路技术和/或轴向电缆来促进高速数据通道的路由的方法和装置的实施例。在以下描述中,阐述了许多具体细节来提供对本发明的实施例的透彻理解。然而,相关领域中的技术人员将认识到,本发明可以在没有具体细节中的一个或多个的情况下被实施,或者与其他方法、部件、材料等一起实施。在其他情况下,众所

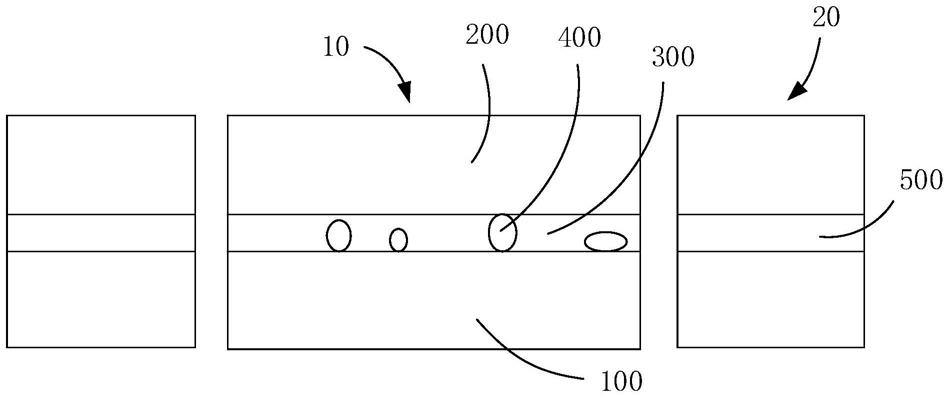

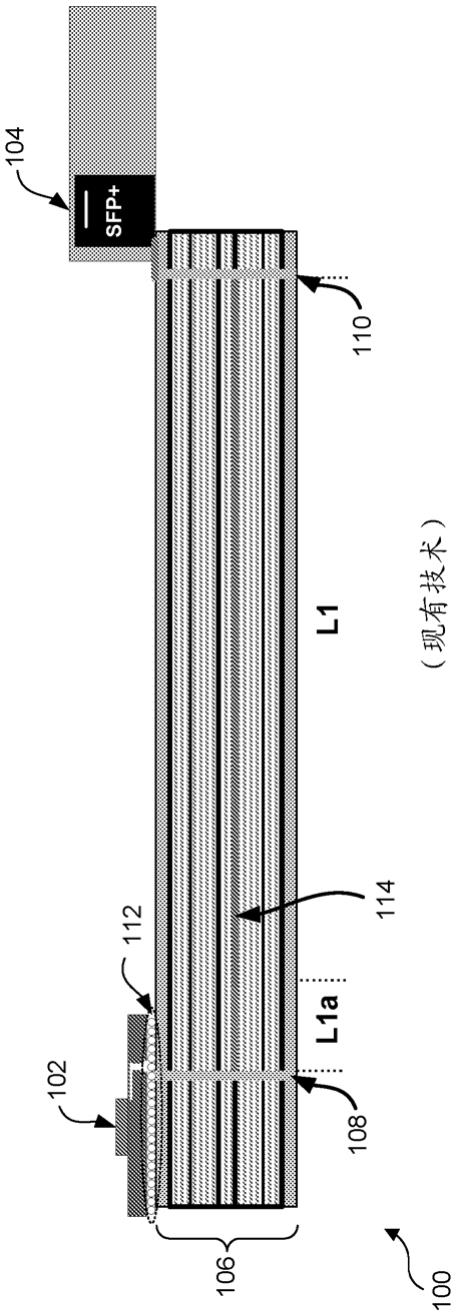

周知的结构、材料或操作未被详细示出或描述,以避免模糊本发明的各方面。

6.贯穿本说明书对“一个实施例”或“实施例”的引用意指将结合实施例描述的特定特征、结构或特性包括在本发明的至少一个实施例中。因此,贯穿本说明书在各种位置中的短语“在一个实施例中”或“在实施例中”的出现不一定全部都指代相同的实施例。此外,可以以任何合适的方式将特定特征、结构或特性组合在一个或多个实施例中。

7.为了清楚起见,本文中的附图中的各个部件也可以通过它们在附图中的标签来指代,而不通过特定的参考编号来指代。另外,可以用后面跟着意指“典型”的“(typ)”的参考编号示出指代特定类型的部件(如与特定部件相对)的参考编号。将理解的是,这些部件的配置将是可能存在但是为了简单和清楚起见而未在附图中示出的典型的类似部件或者未用分开的参考编号加标记的另外的类似部件。相反,“(typ)”不被解释成意指所述部件、元件等被典型地用于其所公开的功能、实现、目的等。

8.如以上讨论的那样,pcb被用于联网和存储部件。pcb受到成本限制,同时还需要满足高速数据要求。高速以太网协议是具有高速数据要求的联网协议的示例。一些集成电路(ic)具有集成以太网,所述集成以太网被设计成符合ieee 802.3标准,以例如在铜以太网上实现每通道10 gb/s、25 gb/s和50 gb/s。还已经定义了多通道以太网标准,包括采用并行操作的四个25 gb/s通道的ieee 802.3bj-2014 100 gb/s以太网。主机pcb (托管ic)可以具有从ic所处的位置到数据连接器(例如以太网连接器)所处的位置的相对长的距离(例如,大于3英寸)。示例ic包括中央处理单元(cpu)、片上系统(soc)芯片(包括具有soc架构的处理器)和平台控制器中枢(pch)。

9.图1图示了电路组件100的一个实施例,其具有从集成电路(ic) 102到连接器104的10英寸的基线距离。在图1中,连接器104是小型可插拔(sfp)连接器。电路组件100包括多层pcb 106,其中形成有多个过孔108和110。高速数据通道从ic 102通过球栅阵列(bga) 112被路由到过孔108。形成为多层pcb中的内层的布线层114将过孔108连接到过孔110,并且高速数据通道从布线层114被路由到过孔110,并且连接到连接器104。因此,高速数据通道(例如,以太网)通过多层pcb 106的层从ic 102被路由到连接器104。如进一步描绘的,该层包括两个部分:和l1a部分和l1部分。除了本文中图示的sfp连接器之外,连接器104还可以被配置成容纳其他类型的电缆,诸如使用除sfp插孔之外的插孔的以太网电缆。

10.如本文中各种附图中描绘的那样,使用一个或多个bga的用途。球栅阵列是封装的类型,在该封装下,在集成电路(通常被称为ic或芯片)的下侧上的栅(栅阵列)中布置的焊盘的阵列被电耦合到具有相同的栅配置的类似的焊盘的阵列,并在pcb上的外层上图案化,其中ic和pcb上的相应的焊盘的对经由焊球被耦合。在制造工艺期间,焊球被熔化(例如,经由回流(reflow)操作),导致相应的焊盘的对被电耦合,使得信号能够从ic传递到连接到在pcb的表面上图案化的焊盘的阵列的一个或多个pcb层上的“布线”。例如,在图1的示例和图2、7-11中图示的实施例中,用于在pcb表面上图案化的栅阵列的所选焊盘被耦合到pcb中形成的过孔,诸如图1中的过孔108。本领域技术人员将理解,在pcb上图案化的焊盘的仅一部分被连接到本文中图示的过孔,或者以其他方式连接到pcb上与图案化的bga焊盘或中间衬底相同的层中形成的布线(诸如图8中所示)。下面参考图12和13讨论bga封装的进一步的细节以及bga焊盘和过孔之间的互连。

11.本领域技术人员还将认识到,术语“布线”、“迹线”和“布线迹线”通常被称为在pcb

中的层上形成的电通路图案。

12.例如,这样的电通路通常通过蚀刻铜层或通过选择性地去除铜层的部分的类似制造工艺在pcb上图案化,留下被用于互连安装到pcb的部件的“布线”或“迹线”的图案。

13.多层pcb中的不同层上的焊盘和/或迹线可以使用过孔来电耦合。通常通过在pcb中钻或冲小孔或者以其他方式使用制造工艺形成类似的孔来形成过孔。在随后的工艺期间,导电材料诸如经由电镀工艺被形成在形成导电管或“桶”的孔的表面上。因此,完全穿过pcb的过孔通常被称为“电镀通孔”、“电镀通孔过孔”或通孔过孔。除了通孔过孔之外,还可以使用盲过孔和掩埋过孔。除了孔仅穿过pcb的一个表面之外,盲过孔类似于通孔过孔。掩埋过孔具有在pcb内部的孔,该孔不穿过pcb的任一表面。为了简单起见,在以下描述中使用术语“过孔”和“过孔”来包含这些各种类型的过孔。

14.图2图示了根据本公开的实施例的具有承载高速数据通道的bga挠性电路202电路组件200。电路组件200包括ic 102、连接器104和多层pcb 204。ic 102经由bga 112被耦合到多层pcb 204的顶层。bga挠性电路202在其相对端处包括一对bga连接器206和208。ic 102和bga 112可以被集成到单个bga封装(诸如陶瓷球栅阵列(cbga))中,如图12中图示并在下面描述的那样。

15.bga 112和bga连接器206和208分别被耦合到在多层pcb 204的外层上图案化的bga焊盘阵列,其包括顶层210和底层212。使用多个过孔214将在顶层210上图案化并用于bga 112的选择性bga焊盘电耦合到在底层212上图案化的用于bga连接器206的bga焊盘。同时,使用多个过孔216将在底层212上图案化的用于bga连接器208的bga焊盘电耦合到在顶层210的表面上形成的布线层l2中的布线。布线层l2中的布线被连接到连接器104上的引脚。

16.在电路组件200下,高速数据通道从ic 102通过bga 112、过孔215、bga 206、挠性电路202、bga 208、过孔216、布线层l2被路由到高速数据连接器104。

17.在一个实施例中,ic 102具有用于发送和接收数据的集成高速数据收发器(例如,以太网)。可以利用本公开的高速数据接口的其他示例包括ultrapath互连(upi)、外围部件互连快速(pcie)、串行at附件(sata)、串行附接scsi (sas)、通用串行总线(usb)、光纤通道、infiniband和存储器。诸如双数据速率(ddr)总线的单端总线可以使用本公开的实施例。

18.通常,高速数据可以是1 gb/s或更高。在一些实施例中,高速数据通道具有25 gb/s的带宽,而在其他实施例中,带宽可以是每通道50 gb/s或更大,并且对于多通道链路,带宽可以是每通道100 gb/s或更大。图2中的高速数据通道从ic 102通过bga 112、过孔214、bga挠性电路202、过孔216并且然后经由布线层l2中的布线被路由到连接器104。

19.图3是针对8英寸的高成本的优化层结构(例如结构交换机路由)和8英寸的低成本的非优化层结构(例如服务器路由)的信号衰减(db)与频率相比的图。如示出的那样,与低成本服务器pcb相比,高成本优化的pcb结构提供了少大约50%的信号衰减。虽然高成本优化的pcb减少了衰减,但它比低成本pcb结构显著昂贵得多。

20.图4是信号衰减(db)与频率图,其图示了使用挠性电路技术的一个实施例的10英寸主机距离与低成本非优化pcb上的10英寸主机距离相比好大约50%的信号衰减。如这展示的那样,挠性电路技术产生与高成本优化的pcb类似的结果。然而,对于类似应用,挠性电

1014、挠性电路1010、轴向端口1006、双轴电缆1004、轴向端口1008、挠性电路1012、bga 1016、pcb 1020的层l2,并且然后被路由到连接器104。

29.图11图示了根据本公开的实施例的具有底部柔性双轴向附件1102的示例电路组件1100。柔性双轴向附件1102包括耦合在一对轴向端口1106和1108之间的双轴电缆1104,轴向端口1106和1108又被安装到挠性电路1110和1112。挠性电路1110通过bga 1114被安装到多层pcb 1118的底层,通过该多层pcb 1118形成过孔1120和1122。如前所述,使用球栅阵列112将ic 102安装到多层pcb 1118的顶层。同时,在柔性双轴向附件1102的相对端处,挠性电路1112通过bga 1124被安装到多层pcb 1118的底层,bga 1124被电连接到过孔1122,过孔1122又被电连接到层l2,连接器104被耦合到所述层l2。

30.在电路组件1100中,高速数据通道从ic 102通过bga 112被路由到过孔1120、bga 1114、挠性电路1110、轴向端口1106、双轴电缆1104、轴向端口1108、挠性电路1112、bga 1118、过孔1122、层l2,并且然后被路由到连接器104。

31.对于图2和图7-11,将理解,元件202、702、802、902、1002和1102可以包括用于单独导体的路由,以促进高速数据通道(例如以太网)的发送和接收两者。另外,元件202、702、802、902、1002和1102可以包括用于多个高速数据通道的路由,或者具有多个通道的高速数据通道。类似地,pcb 204、704、812、914、1018和1118可以被配置为承载高速数据通道的传输和接收信号两者,因此可以在pcb中布线过孔和/或(一个或多个)铜层的多于一个集合,以促进传输和接收高速数据通道的信号或促进多个高速数据通道或多通道数据通道。图2和图7-11示出了其中一个或多个高速数据通道从ic 102通过挠性电路和/或轴向电缆被路由到连接器104而不是完全(或绝大多数)通过pcb将高速数据路由到连接器104的示例。如图3-6中的图展示的那样,使用这些实施例而不是依赖于低成本的pcb布线可以实现更好的信令特性。同时,本文中描述的各种实施例支持满足适用标准的传输质量水平,同时比使用高成本pcb路由所需的优化层结构更便宜。

32.图12描绘了陶瓷球栅阵列(cbga) 1200的横截面视图。在一些实施例中,ic 102和bga 112包括具有与图12中示出的结构类似的结构的cbga封装。在其他实施例中,其他类型的bga可以被用于本文中的附图中图示的和上文描述的各种bga。这些包括但不限于塑料球栅阵列和倒装芯片带球栅阵列。通常,各种类型的bga的“球”结构类似于图12中示出的结构。

33.更详细地,cbga 1200包括管芯1202,该管芯1202包括通过倒装芯片附接件1206被安装到多层陶瓷衬底1204的ic。多个焊球1208以共晶焊料1210的栅图案被耦合在多层陶瓷衬底1204的下侧上。如进一步示出的那样,cbga封装可以进一步包括盖1212、热油脂1214和底部填充物1216。

34.图13示出了bga焊盘和过孔之间的互连的示例。如以上描述的那样,bga焊盘(描绘为bga-pad)以pcb (未示出)上的外层上的图案来布置。过孔1300被布置为与bga图案偏移的类似图案。除了在bga焊盘和过孔之间具有1:1的对应关系之外,如图13的左部中示出的那样,可以与多个bga焊盘共享过孔,如图13的右部中示出的那样,其中sg意指共享接地,sv意指共享通道,sp意指共享电源。在一个实施例中,可以采用去耦电容器(dc)来减少相邻信号之间的耦合。

35.在以下编号条款中阐述了本文中描述的主题的其他方面:

1.电路组件,包括:多层印刷电路板(pcb);集成电路(ic),其耦合到印刷电路板;高速数据连接器,其耦合到印刷电路板,高速数据连接器被布置在距集成电路(ic)大于3英寸的距离处;以及信号通路,其耦合在高速数据连接器和集成电路之间,信号通路提供从集成电路到高速数据连接器的高速数据通道,所述高速数据通道具有至少25吉比特每秒(gb/s)的带宽,其中信号通路的一部分包括具有至少3英寸的长度的柔性(挠性)电路或轴向电缆。

36.2.如条款1所述的电路组件,其中高速数据连接器被布置在距ic至少10英寸处。

37.3.如条款1或2所述的电路组件,其中高速数据通道具有至少50 gb/s的带宽。

38.4.如条款1或2所述的电路组件,其中高速数据通道采用具有至少100吉比特每秒的带宽的多通道链路。

39.5.如前述条款中的任一项所述的电路组件,其中高速数据连接器包括小型可插拔(sfp)连接器。

40.6.如前述条款中的任一项所述的电路组件,其中高速数据通道符合由ieee标准802.3条款110 (25gbase-cr)定义的发射机信号规范。

41.7.如前述条款中的任一项所述的电路组件,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第二侧上的bga焊盘的第二集合;布置在pcb的第二侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及布线层,其具有在多层pcb的第一侧上形成的多个电路路径,其中bga焊盘的第一集合的一部分通过穿过多层pcb的第一多个过孔被电耦合到bga焊盘的第二集合,并且其中bga焊盘的第三集合通过穿过多层pcb的第二多个过孔被耦合到布线层中的电路路径的第一端,并且布线层中的电路路径的第二端被耦合到安装到多层pcb的第一侧的高速数据连接器;其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括bga挠性电路,所述bga挠性电路具有布置在相对端处的第二和第三bga,第二bga经由bga焊盘的第二集合安装到多层pcb的第二侧,第三bga经由bga焊盘的第三集合安装到多层pcb的第二侧。

42.8.如条款1-6中的任一项所述的电路组件,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第一侧上的bga焊盘的第二集合;以及布置在pcb的第一侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及第一布线层,其具有在多层pcb的第二侧上形成的多个电路路径,多层pcb进一步具有从第一侧到第二侧穿过的过孔的第一和第二集合,其中过孔的第一和第二集合之中的过孔经由第二布线层中的电路路径被电连接,其中bga焊盘的第一集合的一部分被电耦合到过孔的第一集合,并且其中bga焊盘的第三集合被耦合到去往安装到多层pcb的第一侧的高速数据连接器的布线层中的电路路径;并且其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括bga挠性电路,所述bga挠性电路具有布置在相对端处的第二

和第三bga,第二bga经由bga焊盘的第二集合安装到多层pcb的第一侧,并且第三bga经由bga焊盘的第三集合安装到多层pcb的第一侧。

43.9.如条款1-6中的任一项所述的电路组件,其中所述多层pcb包括:布置在所述多层pcb的第一侧上的球栅阵列(bga)焊盘的第一和第二集合;以及布线层,其具有在所述多层pcb的第一侧上形成的多个电路路径,所述多个电路路径在第一端处连接到bga焊盘的第二集合中的bga焊盘;其中高速数据连接器被安装在多层pcb的第一侧,并耦合到布线层中的多个电路路径的第二端;并且其中ic被安装到或集成在bga/芯片载体中,所述bga/芯片载体包括安装到芯片载体/插入板的第一bga,所述芯片载体/插入板包括被插入在第一bga和第二bga之间的衬底,所述第二bga经由bga焊盘的第一集合被安装到多层pcb,其中芯片载体/插入板包括bga焊盘的第三集合和bga焊盘的第四集合,第一bga被耦合到所述bga焊盘的第三集合,电路组件进一步包括bga挠性电路,所述bga挠性电路具有布置在相对端处的第三和第四bga,第三bga经由bga焊盘的第四集合安装到芯片载体/插入板,并且第四bga经由bga焊盘的第二集合安装到多层pcb的第一侧。

44.10.如条款1-6中的任一项所述的电路组件,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第一侧上的bga焊盘的第二集合;以及布置在pcb的第一侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及第一布线层,其具有在多层pcb的第二侧上形成的多个电路路径,多层pcb进一步具有从第一侧到第二侧穿过的过孔的第一和第二集合,其中过孔的第一和第二集合之中的过孔经由第二布线层中的电路路径被电连接,其中bga焊盘的第一集合的一部分被电耦合到过孔的第一集合,并且其中bga焊盘的第三集合被耦合到去往安装到多层pcb的第一侧的高速数据连接器的布线层中的电路路径到;并且其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括顶部柔性双轴向附件,所述顶部柔性双轴向附件包括双轴电缆,所述双轴电缆在第一端处耦合到第一轴向端口并且在第二端处耦合到第二轴向端口,第一轴向端口经由bga焊盘的第二集合可操作地耦合到安装到多层pcb的第一侧的第二bga,并且第二轴向端口经由bga焊盘的第三集合可操作地耦合到安装到多层pcb的第一侧的第三bga。

45.11.如条款10所述的电路组件,其中第一轴向端口通过第一挠性电路被可操作地耦合到第二bga,并且其中第二轴向端口通过第二挠性电路被可操作地耦合到第三bga。

46.12.如条款1-6中的任一项所述的电路组件,其中所述多层pcb包括:布置在所述多层pcb的第一侧上的球栅阵列(bga)焊盘的第一和第二集合;以及布线层,其具有在所述多层pcb的第一侧上形成的多个电路路径,所述多个电路路径在第一端处连接到bga焊盘的第二集合中的bga焊盘;其中高速数据连接器被安装到多层pcb的第一侧,并耦合到布线层中的多个电路路径的第二端;并且其中ic经由bga焊盘的第一集合被安装到第一bga,所述第一bga安装到多层pcb,

第一bga包括具有在其顶表面上图案化的bga焊盘的第三集合的衬底,电路组件进一步包括顶部柔性双轴向附件,所述顶部柔性双轴向附件包括双轴电缆,所述双轴电缆在第一端处耦合到第一轴向端口并且在第二端处耦合到第二轴向端口,第一轴向端口经由bga焊盘的第三集合可操作地耦合到安装到bga衬底的第二bga,并且第二轴向端口经由bga焊盘的第二集合可操作地耦合到安装到多层pcb的第一侧的第三bga。

47.13.如条款12所述的电路组件,其中第一轴向端口通过第一挠性电路被可操作地耦合到第二bga,并且其中第二轴向端口通过第二挠性电路被可操作地耦合到第三bga。

48.14.如条款1-6中的任一项所述的电路组件,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第二侧上的bga焊盘的第二集合;布置在pcb的第二侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及布线层,其具有在多层pcb的第一侧上形成的多个电路路径,其中bga焊盘的第一集合的一部分通过穿过多层pcb的第一多个过孔被电耦合到bga焊盘的第二集合,并且其中bga焊盘的第三集合通过穿过多层pcb的第二多个过孔被耦合到布线层中的电路路径的第一端,并且布线层中的电路路径的第二端被耦合到安装到多层pcb的第一侧的高速数据连接器;其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括底部柔性双轴向附件,所述底部柔性双轴向附件包括双轴电缆,所述双轴电缆在第一端处耦合到第一轴向端口并且在第二端处耦合到第二轴向端口,第一轴向端口经由bga焊盘的第二集合可操作地耦合到安装到多层pcb的第二侧的第二bga,并且第二轴向端口经由bga焊盘的第三集合可操作地耦合到安装到多层pcb的第二侧的第三bga。

49.15.如条款15所述的电路组件,其中第一轴向端口通过第一挠性电路被可操作地耦合到第二bga,并且其中第二轴向端口通过第二挠性电路被可操作地耦合到第三bga。

50.16.一种在安装到多层印刷电路板(pcb)的集成电路(ic)和安装到多层pcb的高速数据连接器之间路由高速数据通道的信号的方法,所述方法包括:通过支持至少25吉比特每秒(gb/s)的带宽的信号通路将信号从ic路由到高速数据连接器,其中信号通路的一部分包括具有至少3英寸的长度的柔性(挠性)电路或轴向电缆。

51.17.如条款16所述的方法,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第二侧上的bga焊盘的第二集合;布置在pcb的第二侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及布线层,其具有在多层pcb的第一侧上形成的多个电路路径,其中bga焊盘的第一集合的一部分通过穿过多层pcb的第一多个过孔被电耦合到bga焊盘的第二集合,并且其中bga焊盘的第三集合通过穿过多层pcb的第二多个过孔被耦合到布线层中的电路路径的第一端,并且布线层中的电路路径的第二端被耦合到安装到多层pcb的第一侧的高速数据连接器;其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括bga挠性电路,所述bga挠性电路具有布置在相对端处的第二和第三bga,第二bga经由bga焊盘的第二集合安装到多层pcb的第二侧,第三bga经由bga焊

盘的第三集合安装到多层pcb的第二侧,其中高速数据通道从ic通过第一bga、通过过孔的第一集合中的过孔、通过第二bga、通过挠性电路、通过第三bga、通过过孔的第二集合中的过孔并且通过布线层被路由到高速数据连接器104。

52.18.如条款16所述的方法,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第一侧上的bga焊盘的第二集合;以及布置在pcb的第一侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及第一布线层,其具有在多层pcb的第二侧上形成的多个电路路径,多层pcb进一步具有从第一侧到第二侧穿过的过孔的第一和第二集合,其中过孔的第一和第二集合之中的过孔经由第二布线层中的电路路径被电连接,其中bga焊盘的第一集合的一部分被电耦合到过孔的第一集合,并且其中bga焊盘的第三集合被耦合到去往安装到多层pcb的第一侧的高速数据连接器的布线层中的电路路径;并且其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括bga挠性电路,所述bga挠性电路具有布置在相对端处的第二和第三bga,第二bga经由bga焊盘的第二集合安装到多层pcb的第一侧,并且第三bga经由bga焊盘的第三集合安装到多层pcb的第一侧,其中高速数据通道从ic通过第一bga、通过过孔的第一集合中的过孔、通过第二布线层中的布线、通过过孔的第二集合中的过孔、通过bga挠性电路、通过第一布线层被路由到高速数据连接器。

53.19.如条款16所述的方法,其中所述多层pcb包括:布置在所述多层pcb的第一侧上的球栅阵列(bga)焊盘的第一和第二集合;以及布线层,其具有在所述多层pcb的第一侧上形成的多个电路路径,所述多个电路路径在第一端处连接到bga焊盘的第二集合中的bga焊盘;其中高速数据连接器被安装在多层pcb的第一侧,并耦合到布线层中的多个电路路径的第二端;并且其中ic被安装到或集成在bga/芯片载体中,所述bga/芯片载体包括安装到芯片载体/插入板的第一bga,所述芯片载体/插入板包括被插入在第一bga和第二bga之间的衬底,所述第二bga经由bga焊盘的第一集合被安装到多层pcb,其中芯片载体/插入板包括bga焊盘的第三集合和bga焊盘的第四集合,第一bga被耦合到所述bga焊盘的第三集合,电路组件进一步包括bga挠性电路,所述bga挠性电路具有布置在相对端处的第三和第四bga,第三bga经由bga焊盘的第四集合安装到芯片载体/插入板,并且第四bga经由bga焊盘的第二集合安装到多层pcb的第一侧,其中高速数据通道从ic通过第一bga、芯片载体/插入板、第二bga、通过挠性电路、通过第三bga、通过布线层被路由到高速数据连接器。

54.20.如条款16所述的方法,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第一侧上的bga焊盘的第二集合;以及布置在pcb的第一侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及第一布线层,其具有在多层pcb的第二侧上形成的多个电路路径,多层pcb进一步具有从第一侧到第二侧

穿过的过孔的第一和第二集合,其中过孔的第一和第二集合之中的过孔经由第二布线层中的电路路径被电连接,其中bga焊盘的第一集合的一部分被电耦合到过孔的第一集合,并且其中bga焊盘的第三集合被耦合到去往安装到多层pcb的第一侧的高速数据连接器的布线层中的电路路径;并且其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括顶部柔性双轴向附件,所述顶部柔性双轴向附件包括双轴电缆,所述双轴电缆在第一端处耦合到第一轴向端口并且在第二端处耦合到第二轴向端口,第一轴向端口经由bga焊盘的第二集合可操作地耦合到安装到多层pcb的第一侧的第二bga,并且第二轴向端口经由bga焊盘的第三集合可操作地耦合到安装到多层pcb的第一侧的第三bga,其中高速数据通道从ic通过第一bga、通过过孔的第一集合中的过孔、通过第二布线层、通过过孔的第二集合中的过孔、通过顶部柔性双轴向附件被路由到去往高速数据连接器的布线层。

55.21.如条款16所述的方法,其中所述多层pcb包括:布置在所述多层pcb的第一侧上的球栅阵列(bga)焊盘的第一和第二集合;以及布线层,其具有在所述多层pcb的第一侧上形成的多个电路路径,所述多个电路路径在第一端处连接到bga焊盘的第二集合中的bga焊盘;其中高速数据连接器被安装到多层pcb的第一侧,并耦合到布线层中的多个电路路径的第二端;并且其中ic经由bga焊盘的第一集合被安装到第一bga,所述第一bga安装到多层pcb,第一bga包括具有在其顶表面上图案化的bga焊盘的第三集合的衬底,电路组件进一步包括顶部柔性双轴向附件,所述顶部柔性双轴向附件包括双轴电缆,所述双轴电缆在第一端处耦合到第一轴向端口并且在第二端处耦合到第二轴向端口,第一轴向端口经由bga焊盘的第三集合可操作地耦合到安装到bga衬底的第二bga,并且第二轴向端口经由bga焊盘的第二集合可操作地耦合到安装到多层pcb的第一侧的第三bga,其中高速数据通道从ic通过第一bga、通过顶部柔性双轴向附件、通过布线层被路由到高速数据连接器。

56.22.如条款16所述的方法,其中所述多层pcb包括:布置在pcb的第一侧上的球栅阵列(bga)焊盘的第一集合;布置在pcb的第二侧上的bga焊盘的第二集合;布置在pcb的第二侧上的bga焊盘的第三集合,其距离bga焊盘的第二集合至少3英寸;以及布线层,其具有在多层pcb的第一侧上形成的多个电路路径,其中bga焊盘的第一集合的一部分通过穿过多层pcb的第一多个过孔被电耦合到bga焊盘的第二集合,并且其中bga焊盘的第三集合通过穿过多层pcb的第二多个过孔被耦合到布线层中的电路路径的第一端,并且布线层中的电路路径的第二端被耦合到安装到多层pcb的第一侧的高速数据连接器;其中ic经由第一bga被安装到多层pcb,所述第一bga经由bga焊盘的第一集合将集成电路耦合到多层pcb的第一侧,电路组件进一步包括底部柔性双轴向附件,所述底部柔性双轴向附件包括双轴电缆,所述双轴电缆在第一端处耦合到第一轴向端口并且在第二端处耦合到第二轴向端口,

第一轴向端口经由bga焊盘的第二集合可操作地耦合到安装到多层pcb的第二侧的第二bga,并且第二轴向端口经由bga焊盘的第三集合可操作地耦合到安装到多层pcb的第二侧的第三bga,其中高速数据通道从ic通过第一bga、通过过孔的第一集合中的过孔、通过底部柔性双轴向附件、通过过孔的第二集合中的过孔、通过布线层被路由到高速数据连接器。

57.23.如条款16-22中的任一项所述的方法,其中高速数据连接器被布置在距ic至少10英寸处。

58.24.如条款16-23中的任一项所述的方法,其中高速数据通道具有至少50 gb/s的带宽。

59.25.条款16-23中的任一项所述的方法,其中高速数据通道符合由ieee标准802.3条款110 (25gbase-cr)定义的发射机信号规范。

60.26.如条款1-15中的任一项所述的电路组件,其中多层pcb包括服务器板。

61.27.如条款1-15和26中的任一项所述的电路组件,其中ic包括具有集成高速收发器的处理器。

62.28.如条款1-15和26中的任一项所述的电路组件,其中ic包括具有集成高速收发器的高速通信芯片。

63.29.如条款1-15、27和28中的任一项所述的电路组件,其中集成高速收发器被配置为以下各项中的一个:ultrapath互连(upi)、外围部件互连快速(pcie)、串行at附件(sata)、串行附接scsi (sas)、通用串行总线(usb)、光纤通道和infiniband高速数据接口。

64.30.如条款16-23中的任一项所述的方法,其中多层pcb包括服务器板。

65.31.如条款16-23和30中的任一项所述的方法,其中ic包括具有集成高速收发器的处理器。

66.32.如条款16-23和30中的任一项所述的方法,其中ic包括具有集成高速收发器的高速通信芯片。

67.33.如条款16-23、31和32中的任一项所述的方法,其中集成高速收发器被配置为以下各项中的一个:ultrapath互连(upi)、外围部件互连快速(pcie)、串行at附件(sata)、串行附接scsi(sas)、通用串行总线(usb)、光纤通道和infiniband高速数据接口。

68.虽然已经关于特定实现描述了一些实施例,但是根据一些实施例,其他实现也是可能的。此外,不需要以图示和描述的特定方式来布置附图中图示的和/或本文中所描述的布置和/或元件或其他特征的顺序。根据一些实施例,许多其他布置是可能的。

69.在附图中示出的每个系统中,在一些情况下,元件可以各自具有相同的参考编号或不同的参考编号以暗示所表示的元件可以是不同的和/或类似的。然而,元件可以是足够柔性的以具有不同的实现以及与本文中示出或描述的系统中的一些或全部一起起作用。附图中示出的各种元件可以是相同的或不同的。哪一个被称为第一元件以及哪一个被称为第二元件是任意的。

70.在说明书和权利要求中,可以使用术语“耦合的”和“连接的”连同它们的衍生词。应该理解的是,这些术语不旨在作为彼此的同义词。而是,在特定实施例中,“连接的”可以被用于指示两个或更多个元件与彼此处于直接物理或电接触中。“耦合的”可以意指两个或更多个元件处于直接的物理或电接触中。然而,“耦合的”还可以意指两个或更多个元件彼

此不处于直接接触中,但是还仍彼此合作或相互作用。

71.实施例是本发明的实现或示例。说明书中对“实施例”、“一个实施例”、“一些实施例”或“其他实施例”的引用意指结合实施例所描述的特定特征、结构或特性被包括在本发明的至少一些实施例而不一定所有实施例中。各种出现“实施例”、“一个实施例”或“一些实施例”不一定都指代相同的实施例。

72.不是本文中描述和说明的所有部件、特征、结构、特性等都需要被包括在一个或多个特定实施例中。例如,如果说明书陈述部件、特征、结构或特性“可以”、“可能”、“能够”或“可”被包括,则不需要包括该特定部件、特征、结构或特性。如果说明书或权利要求引用“一”或“一个”元件,这不意指仅存在一个元件。如果说明书或权利要求提及“附加”元件,这不排除存在多于一个的附加元件。

73.本发明的图示的实施例的以上描述(包括摘要中所描述的内容)不旨在是详尽的或者要将本发明限于所公开的精确形式。虽然出于说明的目的在本文中描述了本发明的具体实施例和针对本发明的示例,但是在本发明的范围内,各种等价修改是可能的,如相关领域中的技术人员将意识到的那样。

74.可以根据以上详细描述对本发明作出这些修改。以下权利要求中使用的术语不应当被解释成将本发明限于说明书和附图中所公开的具体实施例。而是,本发明的范围要完全由以下权利要求来确定,所述权利要求要根据权利要求解释的既定原则来解释。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。