1.本发明涉及一种存储元件。

背景技术:

2.电阻式随机存取存储器(resistive random access memory,rram)因其简易的交错式(crossbar)阵列架构以及低温工艺等优势,已广泛地应用在非易失性存储器的技术领域。由于交错式电阻式随机存取存储器是基于电阻切换组件(亦即1r)的概念来设计,因此,相较于1晶体管1电阻器(1-transistor-1-resistor,1t1r)或是1选择器1电阻器(1-selector-1-resistor,1s1r)的架构,交错式电阻式随机存取存储器的架构理论上具有小的单元尺寸(cell size)与较低的操作电压。也就是说,交错式电阻式随机存取存储器可具有高的集成密度并可有效地降低操作电压。

3.然而,交错式电阻式随机存取存储器仍存在部分问题,例如在存储器操作时会产生潜行电流(sneak current)、骤回(snapback)现象等问题。

技术实现要素:

4.本发明提供一种存储元件,其将具有特定电阻值的电阻层配置在位线与电阻切换层之间,以解决骤回现象(通过电阻切换层将位线短接到相交线)的问题,此时电阻切换层从初始的绝缘层转变为较小电阻的切换层。

5.本发明提供一种存储元件包括:电阻切换层、导电柱、阻障层、字线、多个电阻层以及多条位线。电阻切换层呈杯状且具有内表面以定义出开口。导电柱配置在开口中。阻障层配置在电阻切换层与导电柱之间。字线与导电柱电性连接。多个电阻层分别分布在电阻切换层的外表面。多条位线分别与多个电阻层电性连接。

附图说明

6.图1是理论上交错式电阻式随机存取存储元件的形成状态示意图;

7.图2是本发明实施例的一种交错式电阻式随机存取存储元件的形成状态示意图;

8.图3a至图3i是本发明第一实施例的一种存储元件的制造流程的立体示意图;

9.图4a是图3i的存储单元的立体示意图;

10.图4b是图4a的存储单元的剖面示意图;

11.图5是本发明第二实施例的一种存储元件的立体示意图;

12.图6a至图6h是本发明第三实施例的一种存储元件的制造流程的立体示意图;

13.图7a是本发明第四实施例的一种存储元件的立体示意图;

14.图7b是图7a的上视示意图;

15.图8是图7a的存储元件的操作示意图。

具体实施方式

16.请参照图1,当交错式电阻式随机存取存储元件10a的存储单元m1被选定以进行形成操作时,对第一位线bl1施加1单位形成电压(1vf),并对第二位线bl2、第一字线wl1以及第二字线wl2施加0电压(例如接地)。在此情况下,存储单元m1被导通而产生骤回(snapback)现象,其为相交的第一位线bl1与第一字线wl1之间的突然的且明显的电压降(voltage drop)。此现象将第一字线wl1的电压拉至与第一位线bl1的电压相同,这反过来导致存储单元m2因相反极性的电压(1vf)而受到不当干扰或切换。

17.本发明实施例提供一种交错式电阻式随机存取存储元件10包括存储器阵列。所述存储器阵列包括:第一位线bl1、第二位线bl2、第一字线wl1、第二字线wl2、多个存储单元m1、m2、m3、m4以及多个接触电阻rc1、rc2、rc3、rc4。具体来说,存储单元m1、m2、m3、m4分别位于第一位线bl1、第二位线bl2与第一字线wl1、第二字线wl2的交迭处。接触电阻rc1、rc2、rc3、rc4分别位于存储单元m1、m2、m3、m4与第一位线bl1、第二位线bl2之间。当存储单元m1被选定以进行形成操作时,对第一位线bl1施加1单位形成电压(1vf),并对第二位线bl2、第一字线wl1以及第二字线wl2施加0电压(例如接地)。在此情况下,存储单元m1被导通,几乎所有电压会负载到接触电阻rc1上,而不会转移到第一字线wl1,进而解决了因骤回而可能对存储单元m2造成干扰的问题。

18.以下实施例中所述的存储元件可以是交错式电阻式随机存取存储元件,但本发明不以此为限。

19.请参照图3a,首先,提供衬底102。在一实施例中,衬底102包括半导体衬底,例如是硅衬底。接着,在衬底102上形成导体层104。在一实施例中,导体层104的形成方法包括:形成导体材料层,接着图案化所述导体材料层,以形成暴露出衬底102的开口103。如图3a所示,导体层104可以是h字型,但本发明不以此为限。在一实施例中,导体层104的材料包括ta、ti、w、al或其组合。导体层104的厚度104t可介于20nm至50nm之间。

20.请参照图3b,在导体层104上形成介电层106。介电层106填入开口103中,且延伸覆盖介电层106的顶面。在一实施例中,介电层106的形成方法包括:形成介电材料层,接着平坦化所述介电材料层。介电层106的材料可包括氧化硅、氮化硅、氮氧化硅或其组合。导体层104上的介电层106的厚度106t可介于10nm至50nm之间。在替代实施例中,亦可选择性地图案化介电层106,以增加存储元件的设计弹性。

21.请参照图3c,在介电层106上形成导体层108。在一实施例中,导体层108的形成方法包括:形成导体材料层,接着图案化所述导体材料层,以形成暴露出介电层106的开口107。在本实施例中,如图3c所示,导体层108可以是h字型,并对应于导体层104的图案。在一实施例中,导体层108的材料包括ta、ti、w、al或其组合。导体层108的厚度108t可介于20nm至50nm之间。

22.接着,将介电层110填入开口107中,接着进行平坦化工艺(例如cmp工艺),以使介电层110的顶面与导体层108的顶面共平面。在一实施例中,介电层110的材料可包括氧化硅、氮化硅、氮氧化硅或其组合。介电层110的厚度110t可介于10nm至30nm之间。

23.请参照图3c与图3d,在导体层108与介电层110上形成掩膜图案112。接着,以掩膜图案112为掩膜,移除部分介电层110、部分导体层108、部分介电层106以及部分导体层104,进而形成沟槽114。沟槽114暴露出衬底102的顶面。

24.请参照图3d与图3e,在移除掩膜图案112之后,在导体层108上形成另一掩膜图案116。掩膜图案116具有开口118。开口118暴露出沟槽114、介电层110的顶面以及突出在介电层106、110之间的导体层108、104。接着,以掩膜图案116为掩膜,进行蚀刻工艺,以移除突出在介电层106、110之间的导体层108、104,进而形成空隙120。在一实施例中,蚀刻工艺包括湿式蚀刻工艺或是各向同性蚀刻工艺。

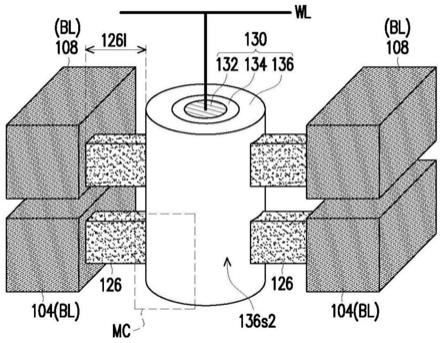

25.请参照图3e与图3f,在移除掩膜图案116之后,在空隙120中形成电阻材料122,以使电阻材料122填满空隙120并延伸覆盖沟槽114的侧壁。在一实施例中,电阻材料122包括高电阻值材料,例如是tan、tin或其组合,电阻材料122的形成方法包括原子层沉积法(ald)、化学气相沉积法(cvd)或其组合。

26.请参照图3f与图3g,在导体层108与介电层110上形成掩膜图案124。接着,以掩膜图案124为掩膜,移除外露于沟槽114的部分电阻材料122。在此情况下,剩余的电阻材料122夹置在介电层106、110之间,以下称为电阻层126。

27.请参照图3g与图3h,在移除掩膜图案124之后,在沟槽114中形成介电层128。在一实施例中,介电层128的材料可包括氧化硅、氮化硅、氮氧化硅或其组合。在本实施例中,介电层128、110、106具有相同介电材料,例如氧化硅。

28.请参照图3h与图3i,在相邻两个电阻层126之间的介电层128中形成存储器结构130,由此完成本发明第一实施例的存储元件100。具体来说,存储器结构130包括导电柱132、阻障层134以及电阻切换层136。在一实施例中,存储器结构130的形成方法包括:在介电层128中形成开口131,其中开口131暴露出衬底102的顶面;在开口131中共形地形成电阻切换层136;在电阻切换层136上共形地形成阻障层134;以及在阻障层134上形成导电柱132。由图4b可知,电阻切换层136呈杯状,且具有内表面136s1以定义出开口135。导电柱132配置在开口135中。阻障层134亦呈杯状且配置在电阻切换层136与导电柱132之间。在一实施例中,导电柱132的材料包括ti、ta或其组合;阻障层134的材料包括al2o3、tio

x

或其组合;而电阻切换层136的材料包括hfo2、zro2、ta2o5、tio2或其组合。

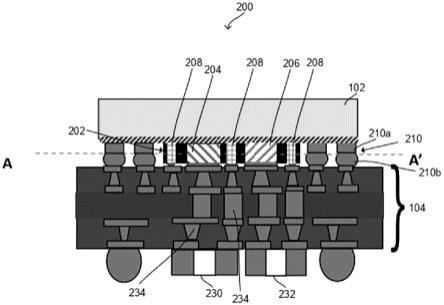

29.请参照图4a与图4b,电阻层126分别分布在电阻切换层136的外表面136s2上。在一实施例中,电阻层126的长度126l为10nm至100nm。导体层104、108呈条状,且分别与电阻层126连接。在本实施例中,条状的导体层104、108可统称为位线bl。另外,导电柱132亦可与字线wl电性连接。于此,与每一个电阻层126连接的部分存储器结构130可视为一个存储单元mc。如图4a所示,此存储器结构130分别与4个电阻层126连接,由此形成4个存储单元mc。

30.在一实施例中,电阻层126的电阻值大于导电柱132的电阻值,大于位线bl的电阻值且大于字线wl的电阻值。在此情况下,电阻层126可用以当作接触电阻(如图2所示),以在存储单元mc导通时保持电压,以避免因骤回所导致的损坏。在一些实施例中,电阻层126的电阻值可以下列式子来表示:

31.rc/rp≧(vf-vr)/vr=vf/vr-1,

32.其中rc为电阻层126的电阻值,rp为周边电路20(如图2所示)的电阻值,vr为复位电压(reset voltage),而vf为形成电压(forming voltage)。这是为了确保电阻层126的电阻值rc(而不是rp)会因骤回而占用大部分的电压。

33.举例来说,电阻层126的电阻值为1千欧姆(kohm)至3kohm;而电阻切换层136的电阻值为5kohm至100kohm。在一些实施例中,电阻切换层136的电阻值与电阻层126的电阻值

的比值约为2至100。

34.请参照图5,本发明第二实施例的存储元件200与本发明第一实施例的存储元件100相似,其主要差异之处在于:存储元件200具有存储器阵列。所述存储器阵列包括4个存储器结构130a、130b、130c、130d。存储器结构130a、130b、130c、130d分别通过电阻层126与条状的导体层104、108(又称为位线bl)电性连接。

35.具体来说,如图6a所示,在衬底102上依序形成导体层204、介电层206以及导体层208。在本实施例中,导体层204、介电层206以及导体层208皆为h字型,其形成方法包括:形成由一导体材料层、介电材料层以及另一导体材料层所构成的堆叠层结构,接着图案化所述堆叠层结构,以形成暴露出衬底102的开口203。

36.请参照图6b,将填充材料210回填至开口203中。在图6c,导体层204、208的凸出部分被各向同性蚀刻所蚀刻以形成狭缝214,而导体层208的线形部分被掩膜图案212所覆盖。在移除掩膜图案212之后,如图6d所示,在导体层108上形成另一掩膜图案216。掩膜图案216具有开口218。开口218暴露出狭缝214、介电层210的顶面以及导体层208、204的突出部分。接着,以掩膜图案216为掩膜,进行蚀刻工艺,以移除导体层208、204的突出部分,进而形成空隙220。在移除掩膜图案216之后,如图6e所示,在空隙220中形成电阻材料222,以使电阻材料222填满空隙220并延伸覆盖狭缝214的侧壁。之后,如图6f所示,在导体层208与介电层210上形成掩膜图案224。接着,以掩膜图案224为掩膜,移除外露于狭缝214的部分电阻材料222。在此情况下,剩余的电阻材料222夹置在介电层206、210之间,以下称为电阻层226。在移除掩膜图案224之后,如图6g所示,在狭缝214中形成介电层228。接着,在相邻两个电阻层226之间的介电层228中形成存储器结构130,由此完成本发明第三实施例的存储元件300,如图6h所示。

37.图7a本发明第四实施例的一种存储元件的立体示意图。图7b是图7a的上视示意图。以下实施例中所述的存储器结构可以是图4a所示的存储器结构130,但本发明不以此为限。

38.请参照图7a,本发明第四实施例的存储元件400包括选择晶体管410、存储器结构130、多个电阻层126以及多条位线bl。具体来说,存储器结构130包括导电柱132、阻障层134以及电阻切换层136。电阻切换层136呈杯状且具有内表面以定义出开口。导电柱132配置在所述开口中。阻障层134配置在电阻切换层136与导电柱132之间。选择晶体管410配置在导电柱132的上方。但本发明不以此为限,在其他实施例中,选择晶体管410亦可配置在导电柱132的下方。在一些实施例中,选择晶体管410可以是金属氧化物半导体场效晶体管(mosfet),其包括栅极、源极以及漏极。选择晶体管410的栅极电性连接至字线wl,而字线wl可沿着y方向延伸。选择晶体管410的源极电性连接至源极线sl,而源极线sl可沿着x方向延伸。选择晶体管410的漏极可电性连接至导电柱132。电阻层126分别分布在电阻切换层136的外表面上。多条位线bl包括第一位线(奇数位线)bl1与第二位线(偶数位线)bl2。如图7a所示,第一位线bl1包括沿着存储器结构130垂直排列的子位线bl1a、bl1b,其在存储器结构130的第一侧s1处与一些电阻层126a1、126a2连接。在一些实施例中,子位线bl1a、bl1b可彼此电性连接。第二位线bl2包括沿着存储器结构130垂直排列的子位线bl2a、bl2b,其在存储器结构130的第二侧s2与另一些电阻层126b1、126b2连接。在一些实施例中,子位线bl2a、bl2b可彼此电性连接。

39.请参照图7b,存储元件400可包括多个存储器结构130、多条位线bl、多个选择晶体管410、多条源极线sl以及多条字线wl。多个存储器结构130排列成阵列。多条位线bl包括多个奇数位线bl1、bl3、bl5以及偶数位线bl2、bl4。奇数位线bl1、bl3、bl5分别配置在存储器结构130的第一侧s1,而偶数位线bl2、bl4则是分别配置在存储器结构130的相对第一侧s1的第二侧s2。在一些实施例中,奇数位线bl1、bl3、bl5彼此电性连接。在替代实施例中,偶数位线bl2、bl4彼此电性连接。多个选择晶体管410分别配置在存储器结构130的上方,且其漏极与对应的导电柱132电性连接。多个选择晶体管410的源极分别电性连接至包括源极线sl0、sl1、sl2、sl3的多条源极线sl。在一些实施例中,源极线sl0、sl1、sl2、sl3沿着x方向延伸,并沿着y方向排列。多个选择晶体管410的栅极分别电性连接至包括字线wl0、wl1、wl2、wl3的多条字线wl。在一些实施例中,字线wl0、wl1、wl2、wl3沿着y方向延伸,并沿着x方向排列。

40.请参照图8,在一实施例中,当存储单元m1被选定以进行复位(reset)操作时,对字线wl施加栅极电压(vg),对源极线sl施加复位电压(vr),对位线bl1a施加0电压,并对其他位线bl1b、bl2a、bl2b施加开路电压(open circuit voltage)。在穿过3个未选定的存储单元(例如是)m2、m3、m4所累积的电阻可最小化潜行电流或非预期的存储单元干扰现象。在本实施例中,此累积电阻为三个接触电阻加上相应的串联的电阻切换层的总和电阻。此总和电阻大约是选定的存储单元m1的接触电阻rc1的5~6倍电阻值。

41.另一方面,当存储单元m1被选定以进行设定(set)操作时,对字线wl施加栅极电压(vg),对源极线sl施加0电压,对位线bl1a施加设定电压(vs),并对其他位线bl1b、bl2a、bl2b施加开路电压。在此情况下,存储单元m1被选定以进行设定操作,而相邻存储单元m2、m3、m4则可降低潜行电流或非预期的存储单元干扰现象。

42.另外,当沿着存储器结构130的存储单元m1、m2、m3、m4皆未被选定以进行操作时,则对字线wl施加0电压,以关闭选择晶体管410。

43.此外,在用于形成的大偏压情况下,晶体管可能会遭受电流的非线性增加。本实施例之接触电阻可减轻这种非线性带来的不利影响。

44.综上所述,本发明将具有适当电阻值的接触电阻配置在位线与存储单元之间,以解决在进行形成操作时所产生的骤回现象而导致周边电路损坏的问题,进而提升存储元件的可靠度。另外,本发明提供一种存储元件的设定操作与复位操作以降低潜行电流,进而避免干扰存储元件的操作或判读。

45.虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定的为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。