1.本公开中讨论的各方面涉及芯片组件。

背景技术:

2.除非在本公开中另有说明,否则本公开中描述的材料不是本技术中权利要求的现有技术,并且不通过包含在本部分中而被承认为现有技术。

3.芯片组件可以包括定位在硅管芯和板之间的封装基板。硅管芯可以机械地耦合到封装基板的第一表面。此外,硅管芯内的引脚或其他装置可以电耦合到封装基板内的引脚或其他装置。此外,板可以机械地耦合到封装基板的第二表面。板内的板焊盘也可以电耦合到封装基板内的引脚或其他装置。

4.本公开中要求保护的主题不限于解决任何缺点或仅在诸如上述那些的环境中操作的各方面。相反,提供该背景技术仅用于说明可以实践本公开中描述的一些方面的一个示例性技术领域。

附图说明

5.将通过使用附图来以附加的特性和细节描述和解释示例性方面,在附图中:

6.图1示出了包括硅管芯、封装基板和板的示例性芯片组件的截面图;

7.图2示出了包括硅管芯、封装基板和板的另一示例性芯片组件的截面图;

8.图3示出了包括桥接装置的示例性芯片组件的截面图;

9.图4示出了包括桥接装置和多芯片装置的示例性芯片组件的截面图;

10.图5示出了球栅阵列的一部分的示例性布置;

11.图6示出了示例性球栅阵列;

12.图7示出了示例性接地层和示例性焊盘阵列;

13.图8示出了封装基板内的信号迹线的插入损耗对比频率的图形表示;

14.图9示出了制造芯片组件的方法的示例性流程图;

15.图10示出了制造芯片组件的方法的另一示例性流程图;

16.图11示出了制造包括再分布层的芯片组件的方法的示例性流程图;

17.图12示出了制造包括再分布层的芯片组件的方法的另一示例性流程图;

18.图13示出了制造芯片组件的方法的示例性流程图;以及

19.图14示出了制造芯片组件的方法的另一示例性流程图;

20.这些附图都是根据本公开中描述的至少一个方面的。

具体实施方式

21.芯片组件可以包括定位在硅管芯和板之间的封装基板。封装基板可以包括多个迹线、过孔或用于将信号从封装基板的第一表面上的引脚路由到封装基板的第二表面上的引脚任何其他合适的装置。如在本公开中使用的,术语“引脚”可以包括部件表面上的用于将

信号路由到部件或路由来自部件的信号的任何合适的装置。例如,引脚可以包括一种结构,该结构包括引脚、端子、凸块、柱、焊盘、迹线、过孔或这些结构中的任一种的一部分、以及这些或其他结构的组合。硅管芯可以包括电耦合到封装基板的第一表面上的引脚的多个引脚。此外,硅管芯可以机械地耦合到封装基板的第一表面。板可以包括多个板焊盘,这些板焊盘电耦合到封装表面的第二表面上的引脚。此外,板可以机械地耦合到封装基板的第二表面。在一些方面中,封装基板可以将一个或多个信号从板路由到硅管芯。在这些和其他方面中,封装基板可以将一个或多个信号从硅管芯路由到板。板可以包括多个迹线、过孔或用于将信号从板焊盘路由到板内的其他位置的任何其他合适的装置。在一些方面中,板可以将信号路由到电耦合到板的多个装置或路由来自电耦合到板的多个装置的信号。

22.在一些芯片组件中,球栅阵列(bga)可以将封装基板内的引脚电耦合到板焊盘。此外,bga可以将封装基板机械地耦合到板。芯片组件可以包括增加数量的焊料球以提供良好的返回路径并提高用于路由信号的耦合性能。例如,芯片组件可以包括插入到对应于输入输出(io)信号(例如,io球)的焊料球之中的对应于系统接地(例如,接地球)的增加数量的焊料球,以提高同时切换噪声(ssn)比率。例如,用于高速双倍数据速率(ddr)io的装置的芯片组件可以包括4比1的io与接地球的比率以提高ssn比率。作为另一示例,用于现场可编程门阵列(fpga)的芯片组件可以包括更多数量的焊料球,以便路由(例如,接合引出(bond out))更多的io信号(例如,接合引出io计数)。此外,芯片组件可以包括更多数量的焊料球以提供用于从板到封装基板的功率输送的低阻抗回路。

23.用于具有更高io密度或功耗的装置的芯片组件可以包括更多数量的焊料球,这可能增加封装基板的占用面积。在一些方面中,增加焊料球的数量(例如,球计数)可以增大封装尺寸(例如,封装基板的占用面积)。在这些和其他方面中,焊料球的尺寸相对于硅凸块的尺寸可以更大。

24.当焊料球的数量增加时,用于芯片组件的接合io计数(例如,与接地球和/或电源球对比的io球的数量)可能受到限制。为使芯片组件增加接合io数量,可以增加焊料球的总数量,这可能进一步增加封装基板的占用面积。此外,随着封装基板的占用面积增加,封装基板内的一个或多个迹线的长度可能相应地增加。增加封装基板内的一个或多个迹线的长度可能增加封装基板内经历的插入损耗。

25.本公开中描述的一些方面可以包括用于将封装基板电耦合到板的无球焊盘阵列。在一些方面中,芯片组件可以包括替代bga的高密度无球焊盘阵列和各向异性层。焊盘阵列和各向异性层可以将封装基板的第二表面的引脚电耦合到板焊盘。此外,各向异性层可以将封装基板机械地耦合到板。

26.在一些方面中,芯片组件可以包括桥接装置(例如,布线分布层(rdl))以根据与封装基板的引脚分配(pinout)不同的引脚分配来提供一个或多个信号。在这些和其他方面中,焊盘阵列和各向异性层可以将桥接装置的引脚电耦合到板焊盘。此外,各向异性层可以将桥接装置机械地耦合到板。此外,附加的焊盘阵列和附加的各向异性层可以将封装基板的第二表面上的引脚电耦合到桥接装置内的引脚。此外,附加的各向异性层可以将封装基板机械地耦合到桥接装置。

27.在一些方面中,芯片组件可以包括桥接装置和多芯片装置。在这些和其他方面中,桥接装置可以包括多芯片装置。此外,在这些和其他方面中,芯片组件可以包括多个封装基

板。附加的焊盘阵列的焊盘中的部分和附加的各向异性层可以将封装基板的第二表面的引脚中的一部分电耦合到桥接装置。此外,附加的焊盘阵列的焊盘的其他部分和附加的各向异性层可以将封装基板的第二表面的引脚的另一部分电耦合到多芯片装置。多芯片装置可以在封装基板之间路由一个或多个信号。在一些方面中,附加的焊盘阵列可以包括不同尺寸的焊盘。例如,包括微尺寸的焊盘可以对应于电耦合到多芯片装置的焊盘,以增加对应于多芯片装置的焊盘密度。此外,芯片组件可以包括一个或多个分立的部件,以提高芯片组件的性能。

28.与实施bga的芯片组件相比,本公开的一个或多个方面可以提供从封装基板到板的紧凑互连。此外,由于焊盘尺寸小于bga中的焊料球的球尺寸,因此本公开的一些方面与bga相比可以减小互连的尺寸。在一些方面中,与实施bga的芯片组件相比,芯片组件可以包括封装基板的减小的占用面积。此外,由于封装基板内的一个或多个迹线的长度减小,本公开的一些方面与包括bga的芯片组件相比可以减少插入损耗。在这些方面中,由于封装基板的占用面积减小,因此一个或多个迹线的长度可以减小。与实施bga的芯片组件相比,本公开的一些方面可以在不增加封装基板的占用面积的情况下增加封装基板的io密度。

29.将参考附图解释本公开的这些和其他方面。应当理解,附图是这些示例性方面的图解和示意性表示,并且既不是限制性的,也不一定按比例绘制。在图中,除非另有描述,否则具有类似附图标记的特征指示类似的结构和功能。

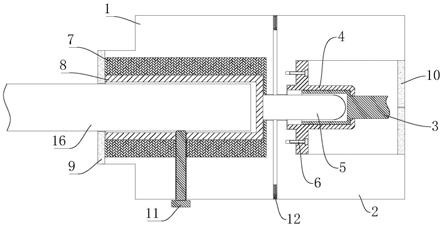

30.图1示出了根据本公开中描述的至少一个方面的包括硅管芯118、封装基板102和板104的示例性芯片组件100的截面图。此外,芯片组件100可以包括多个焊料凸块106和多个焊料球114a-g(在本公开中统称为“焊料球114”)。在图中,为了图示的简单起见,对单个焊料凸块106进行了编号。

31.封装基板102可以包括多个引脚101a-g(在本公开中统称为“引脚101”)和封装阻焊剂层110。引脚101可以形成封装基板102的第二表面105的一部分。此外,封装基板102可以包括形成封装基板102的第一表面103的一部分的多个引脚(未示出)。板104可以包括板焊盘116a-g(在本公开中统称为“板焊盘116”)、过孔119a-g(在本公开中统称为“过孔119”)和阻焊剂层108。

32.焊料球114可以定位在板104的第二表面和封装基板102之间。焊料球114可以将引脚101电耦合到板焊盘116。此外,焊料球114可以将封装基板102机械地耦合到板104(例如,将板焊盘116机械地耦合到封装基板102)。此外,底部填充层112可以定位在封装基板102的一部分与板104的一部分之间。底部填充层112可以将封装基板102机械地耦合到板104。在一些方面中,底部填充层112可以为由焊料球114提供的机械地耦合提供支撑、稳定性或其一些组合。

33.焊料凸块106可以定位在封装基板102和硅管芯118之间。焊料凸块106可以将硅管芯118电耦合到第一表面103的引脚。焊料凸块106还可以将硅管芯118机械地耦合到第一表面103。

34.焊料凸块106、封装基板102(例如,封装基板102内的引脚、过孔、迹线或其他装置)和焊料球114可以使用焊料凸块106、封装基板将一个或多个信号从硅管芯118路由到板104。过孔119、引脚、迹线或任何其他合适的装置可以在板104内路由一个或多个信号。此外,焊料球114、封装基板102和焊料凸块106可以将一个或多个信号从板104路由到硅管芯

118。

35.在一些方面中,焊料球114的间距可以包括在0.5mm和1mm之间。此外,焊料球114的尺寸可以在十密耳至十八密耳之间。

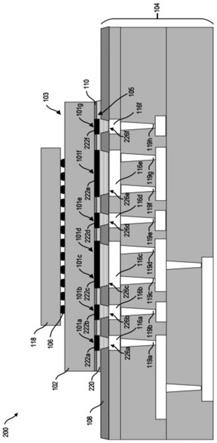

36.图2示出了根据本公开中描述的至少一个方面的包括硅管芯118、封装基板102和板104的另一示例性芯片组件200的截面图。此外,芯片组件200可以包括多个焊盘222a-f(在本公开中统称为“焊盘222”)和各向异性层220。焊盘222可以机械地耦合到第二表面105。此外,焊盘222可以电耦合到引脚101。

37.阻焊剂层108和板接地层(物理上定位为靠近阻焊剂层108和板焊盘116)可以限定多个开口226a-f(在本公开中统称为“开口226”)。在一些方面中,阻焊剂层108和板接地层可以限定开口226使得板焊盘116被暴露。板焊盘116、焊盘222、引脚101、或其一些组合可以被定位成使得当封装基板102附接到板104时,焊盘222相对于板焊盘226定位。此外,板接地层可以屏蔽板焊盘116、焊盘222、或其一些组合。例如,板接地层可以限定开口226,使得第一焊盘222a和第一板焊盘116a与第二焊盘222b和第二板焊盘116b屏蔽。

38.各向异性层220可以定位在板104与焊盘222和封装基板102(例如,封装基板102的一部分)之间。各向异性层220可以将焊盘222机械地耦合到板104。此外,各向异性层220可以将封装基板102机械地耦合到板104。此外,各向异性层220可以将焊盘222电耦合到板焊盘116。在一些方面,各向异性层220可以将焊盘222中的每个焊盘电耦合到板焊盘116中的不同的板焊盘。

39.焊料凸块106、封装基板102(例如,封装基板102内的引脚、过孔、迹线或其他装置)、焊盘222和各向异性层220可以将一个或多个信号从硅管芯118路由到板104。过孔119、引脚、迹线或任何其他适当的装置可以在板104内路由一个或多个信号。此外,各向异性层220、焊盘222、封装基板102和焊料凸块106可以将一个或多个信号从板104路由到硅管芯118。

40.图3示出了根据本公开中描述的至少一个方面的包括桥接装置332的示例性芯片组件300的截面图。芯片组件300还可以包括第一组焊盘321a-f(在本公开中统称为“第一组焊盘321”)、第二组焊盘328a-f(在本公开中统称为“第二组焊盘328”)、和第三组焊盘330a-e(在本公开中统称为“第三组焊盘330”)。在一些方面中,封装基板102可以根据第一引脚分配经由引脚101向第一组焊盘321提供信号。第一组焊盘321可以对应于本公开中其他地方所讨论的焊盘222。

41.第一各向异性层323a可以定位在封装基板102的一部分和桥接装置332的一部分之间。第一各向异性层323a可以对应于本公开中其他地方所讨论的各向异性层220。此外,第一各向异性层323a可以定位在第一组焊盘321和第二组焊盘328之间。第一各向异性层323a可以将封装基板102的一部分机械地耦合到桥接装置332的一部分。此外,第一各向异性层323a可以将第一组焊盘321机械地耦合到第二组焊盘328。此外,第一各向异性层323a可以将第一组焊盘321电耦合到第二组焊盘328。在一些方面中,第一各向异性层323a可以将第一组焊盘321中的每个焊盘电耦合到第二组焊盘328中的不同焊盘。

42.桥接装置332可以包括多个装置过孔334。在图中,为了图示的简单起见,对单个焊料装置过孔334进行了编号。在一些方面中,第二组焊盘328可以电耦合到装置过孔334的第一端。在这些和其他方面中,第二组焊盘328中的每个焊盘可以电耦合到装置过孔334中的

不同的装置过孔的第一端。桥接装置332可以包括装置过孔334、迹线(未示出)、引脚336或用于在桥接装置332内路由信号的其他装置。在图中,为了图示的简单起见,对单个引脚336进行了编号。

43.第三组焊盘330可以电耦合到引脚336。桥接装置332可以根据第二引脚分配向第三组焊盘330(例如,经由装置过孔334的不同的第二端)提供一个或多个信号。在一些方面中,第二引脚分配可以不同于第一引脚分配。例如,桥接装置332可以路由并组合对应于引脚101c和101d的信号以便仅提供在焊盘330c上。

44.第二各向异性层323b可以定位在桥接装置332的一部分和板104之间。第二各向异性层323b可以对应于本公开中其他地方所讨论的各向异性层220。此外,第二各向异性层323b可以定位在第三组焊盘330和板104之间。第二各向异性层323b可以将第三组焊盘330机械地耦合到板104。另外,第二各向异性层323b可以将桥接装置332的一部分机械地耦合到板104。此外,第二各向异性层323b可以经由开口226将第三组焊盘330电耦合到板焊盘116。在一些方面中,第二各向异性层323b可以将第三组焊盘330中的每个焊盘电耦合到板焊盘116中的不同焊盘。

45.焊料凸块106、封装基板102(例如,封装基板102内的引脚、过孔、迹线或其他装置)、第一组焊盘321、第一各向异性层323a、第二组焊盘328、桥接装置323(例如,桥接装置332内的引脚336、装置过孔334、迹线或其他装置)、第三组焊盘330和第二各向异性层323b可以将一个或多个信号从硅管芯118路由到板104。过孔119、引脚、迹线或任何其他合适的装置可以在板104内路由一个或多个信号。此外,第二各向异性层323b、第三组焊盘330、桥接装置332、第二焊盘组328、第一各向异性层323a、第一组焊盘321、封装基板102和焊料凸块106可以将一个或多个信号从板104路由到硅管芯118。

46.图4示出了根据本公开中描述的至少一个方面的包括桥接装置432和多芯片装置438的示例性芯片组件400的截面图。芯片组件400可以包括第一硅管芯118a、第二硅管芯118b、第一封装基板102a、第二封装基板102b、分立部件440、板104和桥接装置432。桥接装置432可以以与关于图3描述的桥接装置332相同或相似的方式操作。

47.芯片组件400可以包括第一组桥接焊盘401a-b(在本公开中统称为“第一组桥接焊盘401”)和第二组桥接焊盘403a-b(在本公开中统称为“第二组桥接焊盘403”)。在一些方面中,第一组桥接焊盘401可以形成第一组焊盘321的一部分。在这些和其他方面中,第二组桥接焊盘403可以形成第二组焊盘328的一部分。在图4中,为了图示的简单起见,省略了引脚101的附图标记。第一封装基板102a和第二封装基板102b可以一起根据第三引脚分配来提供信号。

48.第一各向异性层323a可以定位在第一封装基板102a的一部分与桥接装置432的一部分之间。此外,第一各向异性层323a可以定位在第二封装基板102b的一部分与桥接装置432的另一部分之间。第一各向异性层323a也可以定位在第一组焊盘321和第二组焊盘328之间。此外,第一各向异性层323a可以定位在第一组桥接焊盘401和第二组桥接焊盘403之间。

49.第一各向异性层323a可以将第一封装基板102a的部分机械地耦合到桥接装置432的部分。第一各向异性层323a也可以将第二封装基板102b的部分机械地耦合到桥接装置432的其他部分。此外,第一各向异性层323a可以将第一组焊盘321机械地耦合到第二组焊

盘328。此外,第一各向异性层323a可以将第一组桥接焊盘401电耦合到第二组桥接焊盘403。

50.第一各向异性层323a可以将第一组焊盘321电耦合到第二组焊盘328。第一各向异性层323a可以将第一组桥接焊盘401电耦合到第二组桥接焊盘403。在一些方面中,第一各向异性层323a可以将第一组焊盘321中的焊盘电耦合到第二组焊盘328中的不同数量的焊盘。例如,第一各向异性层323a可以将第一组焊盘321中的焊盘321e和焊盘321f两者电耦合到第二组焊盘328中的焊盘328e。在其他方面中,第一各向异性层323a可以将第一组焊盘321中的每个焊盘电耦合到第二组焊盘328中的不同焊盘。此外,第一各向异性层323a可以将第一组桥接焊盘401中的每个焊盘电耦合到第二组桥接焊盘403中的不同焊盘。

51.在一些方面中,第二组焊盘328可以电耦合到装置过孔334的第一端。在这些和其他方面中,第二组桥接焊盘403可以电耦合到多芯片装置438。桥接装置432可以包括装置过孔334、迹线(未示出)、引脚336或用于在桥接装置432内路由信号的其他装置。多芯片装置438可以包括过孔(未示出)、迹线(未示出)、引脚(未示出)或用于在多芯片装置438内路由信号的其他装置。在图4中,为了图示的简单起见,省略了引脚336的附图标记。

52.第三组焊盘330可以电耦合到引脚336。桥接装置432可以根据第四引脚分配将信号提供给第三组焊盘330(例如,经由装置过孔334的第二端)。此外,桥接装置432可以根据第四引脚分配在第一组桥接焊盘401和第二组桥接焊盘403之间路由信号的一部分。第四引脚分配可以与第三引脚分配不同。

53.第二各向异性层323b可以定位在桥接装置432的一部分和板104之间。另外,第二各向异性层323b可以定位在第三组焊盘330和板104之间。第二各向异性层323b可以将第三组焊盘330机械地耦合到板104。此外,第二各向异性层323b可以将桥接装置432的部分机械地耦合到板104。此外,第二各向异性层323b可以经由开口226将第三组焊盘330电耦合到板焊盘116。在图4中,为了图示的简单起见,省略了板焊盘116的附图标记。在一些方面中,第二各向异性层323b可以将第三组焊盘330中的焊盘电耦合到不同数量的板焊盘116。例如,第二各向异性层323b可以将第三组焊盘330中的焊盘330f电耦合到板焊盘116中的板焊盘116g、板焊盘116h和板焊盘116i。在其他方面中,第二各向异性层323b可以将第三组焊盘330中的每个焊盘电耦合到板焊盘116中的不同焊盘。

54.在一些方面中,分立部件440可以物理上定位在第一封装基板102a和第二封装基板102b之间。在其他方面中,分立部件440可以定位在第一封装基板102a或第二封装基板102b的其他侧上。分立焊盘441可以将分立部件440电耦合到第一各向异性层323a。在一些方面中,第一各向异性层323a可以定位在分立焊盘441和多芯片装置438的一部分之间。在其他方面中,第一各向异性层323a可以定位在分立焊盘441和桥接装置432的一部分之间。第一各向异性层323a可以将分立焊盘441机械地耦合到多芯片装置438、桥432或它们的一些组合。

55.图5示出了根据本公开中描述的至少一个方面的bga 500的一部分的示例性布置。bga 500可以对应于ddr5装置的引脚分配。bga 500可以包括信号球544a-d(在本公开中统称为“信号球544”)和接地球542a-c(在本公开中统称为“接地球542”)。在图5中,为了图示的简单起见,对单个行的信号球544和单个行的接地球542进行了编号。为了为ddr5装置提供良好的信号返回路径和耦合性能,芯片组件可以包括对于每四个信号球544有接地球542

中的一个球的比率。接地球542与信号球544的比率可以提高或恶化封装基板的ssn性能。

56.图6示出了根据本公开中描述的至少一个方面的示例性bga 600a-b。bga 600a可以包括多个接地球646a-f(在本公开中统称为“接地球646”)、多个电源球648a-b(在本公开中统称为“电源球648”)和多个信号球650a-d(在本公开中统称为“信号球650”)。在图6中,为了图示的简单起见,对单个行的信号球650进行了编号。接地球646的数量可以控制信号球650上的高速信号的返回路径和屏蔽。如bga 600a所示,bga 600a可以包括六个接地球646与两个电源球648和十六个信号球650的比率,以实现用于信号球650上的高速信号的返回路径屏蔽。

57.bga 600b可以对应于实施不同对信号的收发器装置。bga 600b可以包括差分信号对组652a-d(在本公开中统称为“差分信号对组652”)。差分信号对组652中的每组可以对应于不同的差分信号对。bga 600b还可以包括定位在差分信号对组652周围以将差分对组652彼此屏蔽的接地球646。在图6中,为了图示的简单起见,对单个接地球646进行编号。

58.图7示出了根据本公开中描述的至少一个方面的示例性接地层754a-b和示例性焊盘阵列700a-b。接地层754a-b可以对应于本公开中描述的板接地层(例如,物理上定位为靠近阻焊剂层108的板接地层)。

59.在焊盘阵列700a中,接地层754a的一部分可以限定多个开口756a-f(在本公开中统称为“开口756”)。在图7中,为了图示的简单起见,仅对由接地层754a限定的开口756的一部分进行编号。开口756可以对应于在本公开中的其他地方所讨论的开口226。开口756可以暴露板焊盘116或者可以对应于其他组焊盘(例如,焊盘222组和第三组焊盘330)。在一些方面中,焊盘的一部分可以包括电源焊盘758a-e(在本公开中统称为“电源焊盘758”),焊盘的另一部分可以包括信号焊盘762a-b(在本公开中统称为“信号焊盘762”)。在一些方面中,电源焊盘758中的两个或更多个可以一起相对于单个开口756定位。例如,电源焊盘758a-d可以一起定位为对应于单个开口756a。另外,组合焊盘760可以电耦合到分组的焊盘中的每个焊盘。组合焊盘760可以对应于焊盘222组、第三组焊盘330或板焊盘116中的焊盘。每个信号焊盘762可以相对于不同的开口756定位。接地层754a可以使每个信号焊盘762彼此屏蔽并且可以使信号焊盘762与电源焊盘758屏蔽。

60.在焊盘阵列700b中,接地层754b的一部分可以限定开口756g-j。在图7中,为了图示的简单起见,仅对接地层754b的开口756的一部分进行编号。在一些方面中,焊盘可以包括差分信号对组764a-d(在本公开中统称为“差分信号对组764”)。在图7中,为了图示的简单起见,仅对差分信号对组764的一部分进行编号。不同差分信号对组764中的每组可以对应于不同的差分信号对。另外,对应于不同差分信号对组764的焊盘可以相对于不同的开口756定位。接地层754b可以将对应于不同差分信号对组764的焊盘彼此屏蔽。

61.图8示出了根据本公开中描述的至少一个方面的封装基板内的信号迹线的插入损耗对比频率的图形表示800。在一些方面中,如果封装基板的尺寸增加,则封装基板内的迹线的长度也可能增加。较长的迹线可能增加信号插入损耗并减小高速信号的带宽。

62.曲线802、804、806和808分别代表分别为5mm、15mm、25mm和30mm的迹线的插入损耗对比频率。如图8所示,随着迹线长度减小,插入损耗提高(例如,插入损耗的值增大)。

63.图9示出了根据本公开中描述的至少一个方面的制造芯片组件的方法900的示例性流程图。方法900可以由关于制造(例如,制作)芯片组件的任何合适的系统、设备或装置

来执行。方法900可以包括一个或多个块902、904、906、908、910或912。虽然以分立的块示出,但与方法900的一个或多个块相关联的步骤和工艺可以被分成附加的块,组合成更少的块,或被消除,这取决于特定的实施方式。

64.在块902,方法900可以包括执行前端工艺。在一些方面中,方法900可以包括执行前端工艺以形成包括多个板管芯的晶片。每个板管芯可以与本技术中其他地方描述的板104相同或相似。在这些和其他方面中,方法900可以包括执行前端工艺以形成包括多个硅管芯的晶片。每个硅管芯可以与本公开中其他地方描述的硅管芯118相同或相似。此外,在一些方面中,方法900可以包括执行前端工艺以形成包括多个封装基板管芯的晶片。每个封装基板管芯可以与本公开中其他地方描述的封装基板102相同或相似。

65.方法900可以包括向晶片添加层以在晶片内的硅管芯、封装基板管芯或板管芯内形成过孔、集成电路、部件或任何其他合适的装置。例如,方法900可以包括光掩模、蚀刻、扩散、金属沉积、钝化或任何其他适当的工艺。在一些方面中,该方法可以包括切割晶片(例如,管芯切割)以分离晶片内的每个板管芯、硅管芯或封装基板管芯。

66.在块904,方法900可以包括附接球。在一些方面中,方法900可以包括将球附接到板管芯。方法900可以包括将球附接到板管芯以形成bga。bga可以如本公开中其他地方所述那样形成。

67.在块906,方法900可以包括在板上印刷焊膏。在一些方面中,方法900可以包括在每个板管芯的表面上印刷焊膏。在一些方面中,方法900可以包括在板管芯的表面上印刷焊膏以向由bga提供的任何机械耦合提供支撑、稳定性或其一些组合。

68.在块908,方法900可以包括将封装放置在板上。在一些方面中,方法900可以包括使用焊料凸块将每个硅管芯附接到不同的封装基板管芯以形成封装。方法900还可以包括将每个封装放置在不同的板管芯上。方法900可以包括将封装相对于bga放置在板管芯上以便将封装基板内的引脚电耦合到bga的球。

69.在块910,方法900可以包括执行回流。方法900可以包括执行回流以使焊膏变为熔融状态以将封装(例如,封装基板)机械地耦合到板管芯。此外,方法900可以包括执行回流以使bga的球变为熔融状态以将封装基板机械地耦合和电耦合到bga。

70.在块912,方法900可以包括施加第二级底部填充或胶。方法900可以包括向芯片组件施加第二级底部填充或胶以填充封装与板管芯、硅管芯和封装基板、或其一些组合之间的开口空间。方法900可以包括制造芯片组件,使得焊料凸块、封装基板和bga将信号从硅管芯路由到板。此外,方法900可以包括制造芯片组件,使得bga、封装基板和焊料凸块将信号从板路由到硅管芯。

71.可以对方法900进行修改、添加或省略,而不脱离本公开的范围。例如,方法900可以以不同的顺序实施。另外或替代地,可以同时执行两个或更多个工艺。此外,所概述的工艺和动作仅作为示例提供,并且一些工艺和动作可以是可选的,可以组合成更少的工艺和动作,或者可以扩展成附加的工艺和动作,而不偏离所描述的方面的本质。

72.图10示出了根据本公开中描述的至少一个方面的制造芯片组件的方法的另一示例性流程图。方法1000可以由关于制造(例如,制作)芯片组件的任何合适的系统、设备或装置来执行。方法1000可以包括一个或多个块1002、1004、1006或1008。虽然以分立的块示出,但是与方法1000的一个或多个块相关联的步骤和工艺可以被划分成附加的块,组合成更少

的块,或被消除,这取决于特定的实施方式。

73.在块1002,方法1000可以包括执行前端工艺。在一些方面中,方法1000可以包括执行前端工艺以形成包括多个板管芯的晶片。每个板管芯可以与本技术中其他地方描述的板104相同或相似。在这些和其他方面中,方法1000可以包括执行前端工艺以形成包括多个硅管芯的晶片。每个硅管芯可以与本公开中其他地方描述的硅管芯118相同或相似。此外,在一些方面中,方法1000可以包括执行前端工艺以形成包括多个封装基板管芯的晶片。每个封装基板管芯可以与本公开中其他地方描述的封装基板102相同或相似。

74.方法1000可以包括向晶片添加层以在晶片内的硅管芯、封装基板管芯或板管芯内形成过孔、集成电路、部件或任何其他合适的装置。例如,方法1000可以包括光掩模、蚀刻、扩散、金属沉积、钝化或任何其他适当的工艺。在一些方面中,方法1000可以包括切割晶片以分离晶片内的每个板管芯、硅管芯或封装基板管芯。此外,方法1000可以包括在包括板管芯的晶片的接地层中形成多个开口。方法1000可以包括形成开口以暴露板管芯内的板焊盘。

75.在块1004,方法1000可以包括在板上分配各向异性聚合物膏。方法1000可以包括相对于板焊盘在板管芯上分配各向异性聚合物膏。各向异性聚合物膏可以对应于本公开中其他地方描述的各向异性层220。

76.在块1006,方法1000可以包括利用热压接合来放置封装。在一些方面中,方法1000可以包括使用焊料凸块将每个硅管芯附接到不同的封装基板管芯以形成封装。方法1000还可以包括将每个封装形成为包括相对于对应封装基板管芯内的引脚定位的多个焊盘。方法1000可以包括相对于不同板管芯的板焊盘将封装放置在各向异性聚合物膏上。方法1000可以包括将封装放置在各向异性聚合物膏上,使得焊盘相对于对应板管芯内的板焊盘定位。

77.方法1000可以包括使用热压缩将封装接合到各向异性聚合物膏。此外,方法1000可以包括使用热压缩将板管芯和封装接合到各向异性聚合物膏。在一些方面中,方法1000可以包括向各向异性聚合物膏施加温度以使各向异性聚合物膏变软并粘附到板管芯和封装(例如,焊盘和封装基板的一部分)。在这些和其他方面中,方法1000可以包括向封装施加压力以在各向异性聚合物膏变软时压缩封装与板管芯之间的各向异性聚合物膏。方法1000可以包括向封装施加压力以使得焊盘在对应板管芯的板焊盘的特定物理接近度内。方法1000可以包括向封装施加压力,使得焊盘与对应板管芯的板焊盘的物理接近度可以使焊盘电耦合到板焊盘。

78.在块1008,方法1000可以包括在烘箱中固化聚合物。在一些方面中,方法1000可以包括固化各向异性聚合物膏以使各向异性聚合物膏硬化并保持焊盘与对应板管芯的板焊盘的物理接近度以及封装与板管芯之间的机械耦合。方法1000可以包括制造芯片组件,使得焊料凸块、封装基板、焊盘和各向异性聚合物膏将信号从硅管芯路由到板管芯。此外,方法1000可以包括制造芯片组件,使得各向异性聚合物膏、焊盘、封装基板和焊料凸块将信号从板管芯路由到硅管芯。

79.可以对方法1000进行修改、添加或省略,而不脱离本公开的范围。例如,方法1000的工艺可以以不同的顺序实施。另外或替代地,可以同时执行两个或更多个工艺。此外,所概述的工艺和动作仅作为示例提供,并且一些工艺和动作可以是可选的,可以组合成更少的工艺和动作,或者可以扩展成附加的工艺和动作,而不偏离所描述的方面的本质。

80.图11示出了根据本公开中描述的至少一个方面的制造包括再分布层的芯片组件的方法1100的示例性流程图。方法1100可以由关于制造(例如,制作)芯片组件的任何合适的系统、设备或装置来执行。方法1100可以包括一个或多个块1102、1104、1106、1108或1110。虽然以分立的块示出,但是与方法1100的一个或多个块相关联的步骤和工艺可以被划分成附加的块,组合成更少的块,或被消除,这取决于特定的实施方式。

81.在块1102,方法1100可以包括执行前端工艺。在一些方面中,方法1100可以包括执行前端工艺以形成包括多个板管芯的晶片。每个板管芯可以与本技术中其他地方描述的板104相同或相似。在这些和其他方面中,方法1100可以包括执行前端工艺以形成包括多个硅管芯的晶片。每个硅管芯可以与本公开中其他地方描述的硅管芯118相同或相似。此外,在一些方面中,方法1100可以包括执行前端工艺以形成包括多个封装基板管芯的晶片。每个封装基板管芯可以与本公开中其他地方描述的封装基板102相同或相似。

82.方法1100可以包括向晶片添加层以在晶片内的硅管芯、封装基板管芯或板管芯内形成过孔、集成电路、部件或任何其他合适的装置。例如,方法1100可以包括光掩模、蚀刻、扩散、金属沉积、钝化或任何其他适当的工艺。在一些方面中,方法1100可以包括切割晶片以分离晶片内的每个板管芯、硅管芯或封装基板管芯。此外,方法1100可以包括在晶片的接地层中形成多个开口以暴露板管芯内的板焊盘。

83.在块1104,方法1100可以包括形成再分布层。在一些方面中,方法1100可以包括将再分布层形成为包括过孔、引脚或任何其他合适的部件。再分布层可以与本公开中其他地方描述的桥接装置332相同或相似。方法1100可以包括形成再分布层,使得再分布层根据与封装基板管芯不同的引脚分配来路由信号并提供信号。此外,方法1100可以包括将再分布层形成为封装管芯的一部分。

84.在块1106,方法1100可以包括在板上分配各向异性聚合物膏。方法1100可以包括相对于板焊盘在板管芯上分配各向异性聚合物膏。各向异性聚合物膏可以对应于本公开中其他地方描述的各向异性层323a、b。

85.在块1108,方法1100可以包括利用热压接合来放置封装。在一些方面中,方法1100可以包括使用焊料凸块将每个硅管芯附接到包括再分布层的不同封装基板管芯以形成封装。方法1100还可以包括将每个封装形成为包括相对于对应的再分布层内的引脚定位的多个焊盘。方法1100可以包括相对于不同板管芯的板焊盘将封装放置在各向异性聚合物膏上。方法1100可以包括将封装放置在各向异性聚合物膏上,使得焊盘相对于对应的板管芯内的板焊盘定位。

86.方法1100可以包括使用热压缩将封装接合到各向异性聚合物膏。此外,方法1100可以包括使用热压缩将板管芯和封装接合到各向异性聚合物膏。在一些方面中,方法1100可以包括向各向异性聚合物膏施加温度以使各向异性聚合物膏变软并粘附到板管芯和封装(例如,封装基板的一部分和焊盘)。在这些和其他方面中,方法1100可以包括向封装施加压力以在各向异性聚合物膏变软时压缩封装与板管芯之间的各向异性聚合物膏。方法1100可以包括向封装施加压力以使焊盘在对应的板管芯的板焊盘的特定物理接近度内。方法1100可以包括向封装施加压力,使得焊盘与对应的板管芯的板焊盘的物理接近度可以使焊盘电耦合到板焊盘。

87.在块1110,方法1100可以包括在烘箱中固化聚合物。在一些方面中,方法1100可以

包括固化各向异性聚合物膏以使各向异性聚合物膏硬化并保持焊盘与对应的板管芯的板焊盘的物理接近度以及封装与板管芯之间的机械耦合。方法1100可以包括制造芯片组件,使得焊料凸块、封装基板、再分布层、焊盘和各向异性聚合物膏将信号从硅管芯路由到板。此外,方法1100可以包括制造芯片组件,使得各向异性聚合物膏、焊盘、再分布层、封装基板和焊料凸块将信号从板路由到硅管芯。此外,方法1100可以形成再分布层,使得再分布层可以根据与封装基板的引脚分配不同的引脚分配向板提供信号。

88.可以对方法1100进行修改、添加或省略,而不脱离本公开的范围。例如,方法1100的工艺可以以不同的顺序实施。另外或替代地,可以同时执行两个或更多个工艺。此外,所概述的工艺和动作仅作为示例提供,并且一些工艺和动作可以是可选的,可以组合成更少的工艺和动作,或者可以扩展成附加的工艺和动作,而不偏离所描述的方面的本质。

89.图12示出了根据本公开中描述的至少一个方面的制造包括再分布层的芯片组件的方法的另一示例性流程图。方法1200可以由关于制造(例如,制作)芯片组件的任何合适的系统、设备或装置来执行。方法1200可以包括一个或多个块1202、1204、1206、1208、1210、1212、1214或1216。虽然以分立的块示出,但是与方法1200的一个或多个块相关联的步骤和工艺可以被划分成附加的块,组合成更少的块,或被消除,这取决于特定的实施方式。

90.在块1202,方法1200可以包括形成再分布层。在一些方面中,方法1200可以包括将再分布层形成为包括过孔、引脚或任何其他合适的部件。在一些方面中,方法1200可以包括将再分布层形成为包括用于将信号从一个封装基板路由到附加的封装基板的多芯片装置。再分布层可以与本公开中其他地方描述的桥接装置332和432相同或相似。方法1200可以包括形成再分布层,使得再分布层路由信号。

91.此外,方法1200可以包括形成具有机械耦合并且电耦合到对应的再分布层的表面的第二组焊盘的再分布层。此外,方法1200可以包括形成具有机械耦合并且电耦合到再分布层的不同表面的第三组焊盘的再分布层。

92.在块1204,方法1200可以包括在再分布层上分配各向异性聚合物膏。方法1200可以包括相对于第二组焊盘在再分布层上分配各向异性聚合物膏。各向异性聚合物膏可以对应于本公开中其他地方描述的各向异性层323a。

93.在块1206,方法1200可以包括执行前端工艺。在一些方面中,方法1200可以包括执行前端工艺以形成包括多个板管芯的晶片。每个板管芯可以与本技术中其他地方描述的板104相同或相似。在这些和其他方面中,方法1200可以包括执行前端工艺以形成包括多个硅管芯的晶片。每个硅管芯可以与本公开中其他地方描述的硅管芯118相同或相似。此外,在一些方面中,方法1200可以包括执行前端工艺以形成包括多个封装基板管芯的晶片。每个封装基板管芯可以与本公开中其他地方描述的封装基板102相同或相似。

94.方法1200可以包括向晶片添加层以在晶片内的硅管芯、封装基板管芯或板管芯内形成过孔、集成电路、部件或任何其他合适的装置。例如,方法1200可以包括光掩模、蚀刻、扩散、金属沉积、钝化或任何其他适当的工艺。在一些方面中,方法1200可以包括切割晶片以分离晶片内的每个板管芯、硅管芯或封装基板管芯。此外,方法1200可以包括在晶片的接地层中形成多个开口以暴露板管芯内的板焊盘。

95.在块1208,方法1200可以包括将封装放置在再分布层上。在一些方面中,方法1200可以包括使用焊料凸块将每个硅管芯附接到不同的封装基板管芯以形成封装。方法1200还

可以包括将每个封装形成为包括相对于对应的封装基板内的引脚定位的多个焊盘。方法1200可以包括相对于第二组焊盘将封装放置在各向异性聚合物膏上。方法1200可以包括将封装放置在各向异性聚合物膏上,使得焊盘相对于第二组焊盘定位。在一些方面中,方法1200可以包括相对于单个再分布层放置多个封装。

96.此外,方法1200可以包括使用热压缩将封装接合到各向异性聚合物膏。此外,方法1200可以包括使用热压缩将再分布层和封装接合到各向异性聚合物膏。在一些方面中,方法1200可以包括向各向异性聚合物膏施加温度以使各向异性聚合物膏变软并粘附到再分布层(例如,再分布层的一部分和第二组焊盘)以及封装(例如,封装基板的一部分和焊盘)。在这些和其他方面中,方法1200可以包括向封装施加压力以在各向异性聚合物膏变软时压缩封装与再分布层之间的各向异性聚合物膏。方法1200可以包括向封装施加压力以使焊盘在对应的再分布层的第二组焊盘的特定物理接近度内。方法1200可以包括向封装施加压力,使得焊盘与对应的再分布层的第二组焊盘的物理接近度可以使焊盘电耦合到第二组焊盘。

97.在块1210,方法1200可以包括在烘箱中固化聚合物。在一些方面中,方法1200可以包括固化各向异性聚合物膏以使各向异性聚合物膏硬化并保持焊盘与第二组焊盘的物理接近度以及封装与再分布层之间的机械耦合。

98.在块1212,方法1200可以包括在板上分配各向异性聚合物膏。方法1200可以包括相对于板焊盘在板管芯上分配各向异性聚合物膏。各向异性聚合物膏可以对应于本公开中其他地方描述的各向异性层323b。

99.在块1214,方法1200可以包括利用热压接合来放置封装。方法1200可以包括相对于不同板管芯的板焊盘在各向异性聚合物膏上放置包括对应再分布层的封装。方法1200可以包括将封装放置在各向异性聚合物膏上,使得焊盘相对于对应板管芯内的板焊盘定位。

100.方法1200可以包括使用热压缩将包括对应再分布层的封装接合到各向异性聚合物膏。此外,方法1200可以包括使用热压缩将板管芯和包括对应再分布层的封装接合到各向异性聚合物膏。在一些方面中,方法1200可以包括向各向异性聚合物膏施加温度以使各向异性聚合物膏变软并粘附到板管芯和封装(例如,封装基板的一部分和焊盘)。在这些和其他方面中,方法1200可以包括向包括对应再分布层的封装施加压力以在各向异性聚合物膏变软时压缩包括对应再分布层的封装与板管芯之间的各向异性聚合物膏。方法1200可以包括向包括对应再分布层的封装施加压力以使第三组焊盘在对应板管芯的板焊盘的特定物理接近度内。方法1200可以包括向包括对应再分布层的封装施加压力,使得第三组焊盘与对应板管芯的板焊盘的物理接近度可以使第三组焊盘电耦合到板焊盘。

101.在块1216,方法1200可以包括在烘箱中固化聚合物。在一些方面中,方法1200可以包括固化各向异性聚合物膏以使各向异性聚合物膏硬化并保持第三组焊盘与对应板管芯的板焊盘的物理接近度以及包括对应再分布层的封装与板管芯之间的机械耦合。方法1200可以包括制造芯片组件,使得芯片组件经由焊料凸块、封装基板、焊盘、各向异性聚合物膏、第二组焊盘、再分布层、第三组焊盘、以及各向异性聚合物膏将信号从硅管芯路由到板。此外,方法1200可以包括制造芯片组件,使得芯片组件经由各向异性聚合物膏、第三组焊盘、再分布层、第二组焊盘、各向异性聚合物膏、焊盘、封装基板和焊料凸块将信号从板路由到硅管芯。此外,方法1200可以形成再分布层,使得再分布层根据与封装基板的引脚分配不同

的引脚分配向板提供信号。此外,方法1200可以形成多芯片装置,使得多芯片装置将来自不同封装基板的信号路由到彼此。例如,方法1200可以包括形成多芯片装置,使得使用作为第二组焊盘的一部分的一个或多个桥接焊盘将一个或多个信号从第一封装基板路由到第二封装基板。

102.可以对方法1200进行修改、添加或省略,而不脱离本公开的范围。例如,方法1200的工艺可以以不同的顺序实施。另外或替代地,可以同时执行两个或更多个工艺。此外,所概述的工艺和动作仅作为示例提供,并且一些工艺和动作可以是可选的,可以组合成更少的工艺和动作,或者可以扩展成附加的工艺和动作,而不偏离所描述的方面的本质。

103.图13示出了根据本公开中描述的至少一个方面的制造芯片组件的方法1300的示例性流程图。方法1300可以包括:形成包括第一表面的板,该第一表面包括一个或多个板焊盘1302;在板的第一表面的至少一部分上放置各向异性材料1304;形成包括第一表面的封装基板,该第一表面包括一个或多个引脚1306;相对于一个或多个引脚将一个或多个焊盘附接到封装基板的第一表面1308;相对于板定位封装基板和一个或多个焊盘,使得各向异性材料在板与一个或多个焊盘之间以及板与封装基板的一部分之间1310;以及固化各向异性材料,使得板机械地耦合到一个或多个焊盘并且机械地耦合到封装基板的一部分,并且使得一个或多个焊盘电耦合到一个或多个板焊盘1312。

104.图14示出了根据本公开中描述的至少一个方面的制造芯片组件的方法1400的示例性流程图。方法1400可以包括:形成包括第一表面的板,该第一表面包括多个板焊盘1402;将第一各向异性材料放置在板的第一表面的至少一部分上1404;形成包括第一表面、第二表面和多个装置过孔的桥接装置1406;形成包括第一表面的封装基板,该第一表面包括多个引脚1408;相对于所述引脚将第一组焊盘附接到封装基板的第一表面1410;相对于装置过孔的第一端将第二组焊盘附接到桥接装置的第一表面1412;相对于装置过孔的第二端将第三组焊盘附接到桥接装置的第二表面1414;相对于板定位桥接装置和第三组焊盘,使得第一各向异性材料在板与第三组焊盘之间以及板与桥接装置的一部分之间1416;将第二各向异性材料放置在桥接装置的第一表面的至少一部分和第二组焊盘上1418;相对于桥接装置定位封装基板和第一组焊盘,使得第二各向异性材料在第一组焊盘与第二组焊盘之间以及桥接装置的一部分与封装基板的一部分之间1420;固化第一各向异性材料,使得板机械地耦合到桥接装置的一部分和第三组焊盘,并且使得第三组焊盘电耦合到板焊盘1422;以及固化第二各向异性材料,使得封装基板的一部分机械地耦合到桥接装置的一部分并且使得第一组焊盘机械耦合并且电耦合到第二组焊盘1424。

105.本公开中描述的一些方面可以包括无球焊盘阵列和各向异性层以将封装基板电耦合到板。芯片组件可以包括包含多个引脚的封装基板。芯片组件还可以包括多个焊盘。焊盘可以电耦合到封装基板的引脚。此外,芯片组件可以包括包含多个板焊盘的板。此外,芯片组件可以包括定位在板和焊盘之间的各向异性层。各向异性层也可以定位在板和封装基板的一部分之间。在一些方面中,各向异性层可以使用各向异性聚合物膏形成。在一些方面中,各向异性层可以将板机械地耦合到焊盘。在这些和其他方面中,各向异性层可以将板机械地耦合到封装基板的一部分。此外,各向异性层可以将焊盘电耦合到板焊盘。

106.在一些方面中,焊盘可以包括高密度无球焊盘阵列以提供从封装基板到板的紧凑互连。在这些和其他方面中,焊盘阵列和各向异性层可以代替芯片组件内的bga。焊盘阵列

可以部署到封装基板和电路板两者上。在一些方面中,各向异性层(例如,各向异性导电材料)可以将焊盘、封装基板和pcb基板(例如,板)接合到一起。在一些方面中,各向异性层可以在不使用焊料球的情况下提供封装基板与板之间的强粘合接合。

107.在一些方面中,各向异性层可以将每个焊盘电耦合到板内的不同板焊盘。在其他方面中,各向异性层可以通过保持焊盘相对于板焊盘的物理接近度来将焊盘电耦合到板焊盘。

108.封装基板可以包括封装接地层。封装接地层可以包括封装阻焊剂层。

109.在一些方面中,板可以包括板接地层。板接地层可以限定暴露板焊盘的多个开口。此外,封装基板中的引脚的一部分可以包括电源引脚。在这些和其他方面中,电耦合到电源引脚的每个焊盘可以相对于由接地层限定的单个开口定位。例如,电源引脚可以分组在一起并作为平面电耦合到电源焊盘以在封装基板与板之间具有更强的连接。

110.在一些方面中,封装基板中的引脚的一部分可以包括信号引脚。信号引脚中的每个可以电耦合到不同的焊盘。此外,电耦合到信号引脚的每个焊盘可以相对于不同的开口定位。电耦合到信号引脚的焊盘可以相对于不同的开口定位。板接地层可以将每个对应的焊盘(例如,每个信号焊盘)彼此屏蔽。

111.在一些方面中,封装基板中的引脚的一部分可以包括电源引脚。焊盘的另一部分(例如,除了电耦合到信号引脚的焊盘之外的一部分)可以电耦合到电源引脚。焊盘中的电耦合到电源引脚的一部分可以相对于由板接地层限定的单个开口定位。在这些和其他方面中,板接地层可以将电耦合到信号引脚的焊盘与电耦合到电源引脚的焊盘屏蔽。

112.在一些方面中,封装基板中的引脚的一部分可以包括差分信号引脚组(例如,第一组差分信号引脚和第二组差分信号引脚)。不同组差分信号引脚中的每个引脚可以电耦合到不同的焊盘(例如,差分信号焊盘)。每组差分信号焊盘可以相对于不同的开口定位。例如,第一组差分信号焊盘可以相对于第一开口定位并且第二组差分信号焊盘可以相对于第二开口定位。差分信号焊盘组可以相对于不同的开口定位以将差分信号焊盘组彼此屏蔽。

113.在一些方面中,芯片组件可以包括尺寸小于焊料球的球尺寸的焊盘。在这些和其他方面中,芯片组件可以包括间距尺寸小于焊料球的球间距的焊盘。此外,封装基板可以包括迹线,并且与包括焊料球的芯片组件相比,焊盘可以使迹线中的一个或多个迹线的长度减小。此外,板可以包括迹线,并且与包括焊料球的芯片组件相比,焊盘可以使迹线中的一个或多个迹线的长度减小。

114.在一些方面中,焊盘的尺寸可以包括小于或等于一毫米。

115.在一些方面中,芯片组件还可以包括硅管芯。芯片组件还可以包括焊料凸块。硅管芯可以经由焊料凸块机械耦合并且电耦合到封装基板。

116.在一些方面中,芯片组件可以包括包含多个引脚的封装基板。封装基板可以被配置为根据第一引脚分配经由引脚提供信号。芯片组件可以包括电耦合到引脚的第一组焊盘。芯片组件还可以包括包含多个装置过孔的桥接装置。此外,芯片组件可以包括电耦合到装置过孔的第一端的第二组焊盘。此外,芯片组件可以包括定位在桥接装置的一部分与封装基板的一部分之间的各向异性层(例如,第一各向异性层)。此外,各向异性层可以定位在第一组焊盘与第二组焊盘之间。各向异性层可以将桥接装置的一部分机械地耦合到封装基板的一部分。各向异性层还可以将第一组焊盘机械地耦合到第二组焊盘。各向异性层可以

将第一组焊盘电耦合到第二组焊盘。桥接装置可以被配置为根据与第一引脚分配不同的第二引脚分配来提供信号。

117.芯片组件可以包括另一各向异性层和第三组焊盘。第三组焊盘可以电耦合到装置过孔的第二端。芯片组件还可以包括包含多个板焊盘的板。另一各向异性层(例如,第二各向异性层)可以定位在板与第三组焊盘之间。此外,另一各向异性层可以定位在第三组焊盘与桥接装置的一部分之间。另一各向异性层可以将板机械地耦合到桥接装置的一部分和第三组焊盘。

118.另一各向异性层还可以将第三组焊盘电耦合到板焊盘。

119.在一些方面中,芯片组件可以包括封装基板和板之间的高密度无球第二级互连(sli)。sli可以提供附加的rdl以用于路由或再分布信号,以适配特定的引脚分配。sli的顶部焊盘可以接合到封装基板,并且sli的底部焊盘可以通过各向异性导电材料(例如,各向异性层)接合到pcb基板(例如,板)以在没有bga球的情况下提供强粘合接合。在一些方面中,电源焊盘、接地焊盘或其一些组合可以基于不同的引脚分配在顶部焊盘和底部焊盘之间以不同方式分组在一起作为平面。

120.第一各向异性层可以将第一组焊盘中的每个焊盘电耦合到第二组焊盘中的不同焊盘。此外,第一各向异性层可以通过保持第一组焊盘相对于第二组焊盘的物理接近度来将第一组焊盘电耦合到第二组焊盘。

121.第二各向异性层可以将第三组焊盘中的每个焊盘电耦合到板焊盘中的不同焊盘。此外,第二各向异性层可以通过保持第三组焊盘相对于板焊盘的物理接近度来将第三组焊盘电耦合到板焊盘。

122.封装基板可以包括封装阻焊剂层。

123.在一些方面中,装置过孔的一部分可以包括电源过孔。板可以包括板接地层,其限定暴露板焊盘的开口。第三组焊盘的至少一部分电耦合到电源过孔。在一些方面中,第三组焊盘的一部分可以相对于由板接地层限定的单个开口定位。在一些方面中,板接地层可以包括阻焊剂层。

124.装置过孔的一部分可以包括信号过孔。此外,每个信号过孔可以电耦合到第三组焊盘中的不同焊盘。电耦合到信号过孔的第三组焊盘中的每个焊盘可以相对于由板接地层限定的不同开口定位,以将第三组焊盘中的电耦合到信号过孔的每个焊盘彼此屏蔽。

125.在一些方面中,装置过孔的另一部分可以包括电源过孔。此外,第三组焊盘的至少另一部分可以电耦合到电源过孔。第三组焊盘的另一部分可以相对于由板接地层限定的单个开口定位。此外,可以将第三组焊盘中的电耦合到信号过孔的每个焊盘与第三组焊盘中的电耦合到电源过孔的部分屏蔽。

126.装置过孔的一部分可以包括第一组差分信号过孔和第二组差分信号过孔。第一组差分信号过孔中的每个过孔和第二组差分信号过孔中的每个过孔可以电耦合到第三组焊盘中的不同焊盘(例如,第一组差分信号焊盘和第二组差分信号焊盘)。第一组差分焊盘可以相对于第一开口定位并且第二组差分焊盘可以相对于第二开口定位,以将不同差分信号的焊盘彼此屏蔽。

127.封装基板可以包括迹线。在一些方面中,第一组焊盘、第二组焊盘和第三组焊盘可以使封装基板的一个或多个迹线的长度相对于实施焊料球的系统减小。板可以包括迹线。

在一些方面中,第一组焊盘、第二组焊盘和第三组焊盘可以使板的一个或多个迹线的长度相对于实施焊料球的系统减小。

128.第一组焊盘、第二组焊盘和第三组焊盘中的每个焊盘的尺寸可以包括小于或等于一毫米。

129.在一些方面中,桥接装置可以包括sli桥接装置。

130.在一些方面中,芯片组件可以包括包含引脚的另一封装基板(例如,第二封装基板)。第二封装基板可以被配置为根据第二引脚分配来提供信号。第一组焊盘的一部分可以电耦合到第二封装基板的引脚。桥接装置还可以包括多芯片装置。此外,封装基板(例如,第一封装基板)的引脚的一部分可以经由第一组焊盘的一部分和第二组焊盘的一部分电耦合到多芯片装置。第二封装基板的引脚的一部分可以经由第一组焊盘的另一部分和第二组焊盘的另一部分电耦合到多芯片装置。多芯片装置可以被配置为在第二封装基板和第一封装基板之间路由信号。此外,第一各向异性层的一部分还可以定位在多芯片装置的一部分、第一封装基板和第二封装基板之间。

131.在一些方面中,芯片组件可以包括物理上定位在第一封装基板和第二封装基板之间的分立部件。此外,芯片组件可以包括电耦合到分立部件的分立焊盘。第一各向异性层还可以定位在多芯片装置的一部分和分立焊盘之间。

132.在一些方面中,无球sli可以通过将多个装置(例如,封装)放置在rdl顶部上而被扩展以实现多芯片模块解决方案,并且rdl可以作为封装之间的互连来操作。在这些和其他方面中,多芯片装置可以包括在sli内的嵌入式多管芯互连桥(emib)。emib可以提供sli co-emib解决方案。无球焊盘阵列和sli可以包括混合焊盘尺寸,混合焊盘尺寸包括在emib实施的微焊盘尺寸。微焊盘尺寸可以允许从封装到emib的高io密度连接。此外,可以将分立部件放置在无球sli上以增强去耦方案。

133.本公开中描述的一些方面可以在不添加大量专用的个体接地焊盘的情况下减少焊盘计数。此外,由于封装尺寸减小,本公开中描述的一些方面可以减小封装基板和/或板内的信号路由迹线长度。减小的迹线长度可以提高封装基板和/或板的信号插入损耗性能,这对于高速信号带宽可能是关键的。

134.本公开中描述的一些方面可以包括等于或大于0.5mm的焊盘阵列间距,其与实施具有1mm球尺寸的bga的芯片组件相比可以将封装基板迹线长度减小百分之五十。在一些方面中,当迹线从30mm减小到15mm时,可能出现大约一分贝的提高。

135.与分离且成本高的接地球方法相比,本公开中描述的一些方面可以通过将电源焊盘和焊盘位置分组来提供相邻的接地返回路径和屏蔽。

136.示例1可以包括一种芯片组件,其包括:包括一个或多个引脚的封装基板;一或多个焊盘,该一或多个焊盘电耦合到一或多个引脚;包括一个或多个板焊盘的板;以及各向异性层,其定位在板和一个或多个焊盘之间以及板和封装基板的一部分之间,该各向异性层将板机械地耦合到一个或多个焊盘和封装基板的一部分,并将一个或多个焊盘电耦合到一个或多个板焊盘。

137.示例2可以包括示例1的芯片组件,其中各向异性层将一个或多个焊盘中的每个焊盘电耦合到一个或多个板焊盘中的不同板焊盘。

138.示例3可以包括示例1的芯片组件,其中各向异性层通过保持一个或多个焊盘相对

于一个或多个板焊盘的物理接近度来将一个或多个焊盘电耦合到一个或多个板焊盘。

139.示例4可以包括示例1-3中任一个的芯片组件,其中封装基板的部分包括封装接地层。

140.示例5可以包括示例4的芯片组件,其中封装接地层包括封装阻焊剂层。

141.示例6可以包括示例1-5中任一个的芯片组件,其中一个或多个引脚的一部分包括一个或多个电源引脚,并且板的一部分包括限定一个或多个开口的板接地层,该一个或多个开口暴露一个或多个板焊盘,并且其中一个或多个焊盘的至少一部分电耦合到一个或多个电源引脚,并且一个或多个焊盘的该部分相对于一个或多个开口中的单个开口定位。

142.示例7可以包括示例6的芯片组件,其中板接地层包括阻焊剂层。

143.示例8可以包括示例1-5中任一个的芯片组件,其中一个或多个引脚的一部分包括一个或多个信号引脚,并且一个或多个信号引脚中的每个信号引脚耦合到一个或多个焊盘中的不同焊盘,并且板的一部分包括限定多个开口的板接地层,该多个开口暴露一个或多个板焊盘,并且其中一个或多个焊盘中的电耦合到一个或多个信号引脚的每个焊盘相对于多个开口中的不同开口定位,以通过板接地层将一个或多个焊盘中的电耦合到一个或多个信号引脚的每个焊盘彼此屏蔽。

144.示例9可以包括示例8的芯片组件,其中一个或多个引脚的另一部分包括一个或多个电源引脚,并且其中一个或多个焊盘的至少另一部分电耦合到一个或多个电源引脚并且相对于多个开口中的单个开口定位,并且其中一个或多个焊盘中的电耦合到一个或多个信号引脚的每个焊盘通过板接地层而与一个或多个焊盘中的电耦合到电源引脚的部分屏蔽。

145.示例10可以包括示例1-5中任一个的芯片组件,其中一个或多个引脚的一部分包括第一组差分信号引脚和第二组差分信号引脚,并且其中第一组差分信号引脚中的每个引脚和第二组差分信号引脚中的每个引脚电耦合到一个或多个焊盘中的不同焊盘,并且板的一部分包括限定多个开口的板接地层,该多个开口暴露一个或多个板焊盘,其中第一组差分引脚相对于多个开口中的第一开口定位,并且第二组差分引脚相对于多个开口中的第二开口定位,以通过板接地层将一个或多个焊盘中的电耦合到第一组差分引脚的焊盘与一个或多个焊盘中的电耦合到第二组差分引脚的焊盘屏蔽。

146.示例11可以包括示例1-10中任一个的芯片组件,其中一个或多个焊盘中的每个焊盘的尺寸相对于焊料球的球尺寸较小。

147.示例12可以包括示例1-11中任一个的芯片组件,其中一个或多个焊盘的间距相对于多个焊料球的球间距较小。

148.示例13可以包括示例1-12中任一个的芯片组件,其中封装基板包括一个或多个迹线并且一个或多个焊盘使所述迹线中的一个或多个的长度相对于实施焊料球的芯片组件减小。

149.示例14可以包括示例1-13中任一个的芯片组件,其中一个或多个焊盘中的每个焊盘的尺寸小于一毫米。

150.示例15可以包括示例1-14中任一个的芯片组件,还包括硅管芯和多个焊料凸块,其中硅管芯经由多个焊料凸块电耦合到封装基板。

151.示例16可以包括一种芯片组件,其包括:包括多个引脚的封装基板,该封装基板被配置为根据第一引脚分配经由多个引脚提供一个或多个信号;电耦合到多个引脚的第一多

个焊盘;桥接装置,其包括多个装置过孔;第二多个焊盘,该第二多个焊盘电耦合到多个装置过孔的第一端;以及各向异性层,其定位在桥接装置的一部分和封装基板的一部分之间以及第一多个焊盘和第二多个焊盘之间,其中:各向异性层将桥接装置的一部分机械地耦合到封装基板的一部分,并且将第一多个焊盘机械地耦合到第二多个焊盘;各向异性层将第一多个焊盘电耦合到第二多个焊盘;并且桥接装置被配置为根据不同于第一引脚分配的第二引脚分配经由多个装置过孔的第二端提供一个或多个信号。

152.示例17可以包括示例16的芯片组件,其中各向异性层包括第一各向异性层,该芯片组件还包括:第三多个焊盘,第三多个焊盘电耦合到多个装置过孔的第二端;板,其包括多个板焊盘;以及第二各向异性层,其定位在板与桥接装置的一部分和第三多个焊盘之间,第二各向异性层将板机械地耦合到桥接装置的一部分和第三多个焊盘,并将第三多个焊盘电耦合到多个板焊盘。

153.示例18可以包括示例16和17中任一个的芯片组件,其中第一各向异性层将第一多个焊盘中的每个焊盘电耦合到第二多个焊盘中的不同焊盘。

154.示例19可以包括示例16-18中任一个的芯片组件,其中第一各向异性层通过保持第一多个焊盘相对于第二多个焊盘的物理接近度来将第一多个焊盘电耦合到第二多个焊盘。

155.示例20可以包括示例17-19中任一个的芯片组件,其中第二各向异性层将第三多个焊盘中的每个焊盘电耦合到多个板焊盘中的不同焊盘。

156.示例21可以包括示例17-20中任一个的芯片组件,其中第二各向异性层通过保持第三多个焊盘相对于多个板焊盘的物理接近度来将第三多个焊盘电耦合到多个板焊盘。

157.示例22可以包括示例16-21中任一个的芯片组件,其中封装基板的部分包括封装阻焊剂层。

158.示例23可以包括示例17-22中任一个的芯片组件,其中多个装置过孔的一部分包括一个或多个电源过孔,并且板的一部分包括限定多个开口的板接地层,该多个开口暴露多个板焊盘,并且其中第三多个焊盘的至少一部分电耦合到一个或多个电源过孔,并且第三多个焊盘的该部分相对于多个开口中的单个开口定位。

159.示例24可以包括示例23的芯片组件,其中板接地层包括阻焊剂层。

160.示例25可以包括示例17-22中任一个的芯片组件,其中多个装置过孔的一部分包括一个或多个信号过孔并且一个或多个信号过孔中的每个信号过孔耦合到第三多个焊盘中的不同焊盘,并且板的一部分包括限定多个开口的板接地层,该多个开口暴露多个板焊盘,并且其中第三多个焊盘中的电耦合到一个或多个信号过孔的每个焊盘相对于多个开口中的不同开口定位,以通过板接地层将第三多个焊盘中的电耦合到一个或多个信号过孔的每个焊盘彼此屏蔽。

161.示例26可以包括示例25的芯片组件,其中多个装置过孔的另一部分包括一个或多个电源过孔,并且其中第三多个焊盘的至少另一部分电耦合到一个或多个电源过孔并且相对于多个开口中的单个开口定位,并且其中第三多个焊盘中的电耦合到一个或多个信号过孔的每个焊盘通过板接地层与第三多个焊盘中的电耦合到电源过孔的部分屏蔽。

162.示例27可以包括示例17-22中任一个的芯片组件,其中多个装置过孔的一部分包括第一组差分信号过孔和第二组差分信号过孔,并且其中第一组差分信号过孔中的每个过

孔和第二组差分信号过孔中的每个过孔电耦合到第三多个焊盘中的不同焊盘,并且板的一部分包括限定多个开口的板接地层,该多个开口暴露多个板焊盘,并且其中第一组差分过孔相对于多个开口中的第一开口定位,并且第二组差分过孔相对于多个开口中的第二开口定位,以通过板接地层将第三多个焊盘中的电耦合到第一组差分过孔的焊盘与第三多个焊盘中的电耦合到第二组差分过孔的焊盘屏蔽。

163.示例28可以包括示例16-27中任一个的芯片组件,其中第一多个焊盘、第二多个焊盘和第三多个焊盘中的每个焊盘的尺寸相对于焊料球的球尺寸较小。

164.示例29可以包括示例16-28中任一个的芯片组件,其中第一多个焊盘、第二多个焊盘和第三多个焊盘中的每一个的间距相对于多个焊料球的球间距较小。

165.示例30可以包括示例16-29中任一个的芯片组件,其中封装基板包括多个迹线并且第一多个焊盘、第二多个焊盘和第三多个焊盘使多个迹线中的一个或多个迹线的长度相对于实施焊料球的系统减小。

166.示例31可以包括示例16-30中任一个的芯片组件,其中第一多个焊盘、第二多个焊盘和第三多个焊盘中的每个焊盘的尺寸小于一毫米。

167.示例32可以包括示例16-31中任一个的芯片组件,还包括硅管芯和多个焊料凸块,其中硅管芯经由多个焊料凸块电耦合到封装基板。

168.示例33可以包括示例16-32中任一个的芯片组件,其中桥接装置包括第二级互连(sli)桥接装置。

169.示例34可以包括示例17的芯片组件,其中封装基板包括第一封装基板,芯片组件还包括包含多个引脚的第二封装基板,第二封装基板被配置为根据第二引脚分配经由多个引脚提供一个或多个信号,其中:第一多个焊盘的一部分电耦合到第二封装基板的多个引脚;桥接装置还包括多芯片装置,其中:第一封装基板的多个引脚的一部分经由第一多个焊盘的一部分和第二多个焊盘的一部分电耦合到多芯片装置;第二封装基板的多个引脚的一部分经由第一多个焊盘的另一部分和第二多个焊盘的另一部分电耦合到多芯片装置;以及多芯片装置,其被配置为将第二封装基板的一个或多个信号路由到第一封装基板,并将第一封装基板的一个或多个信号路由到第二封装基板;并且第一各向异性层进一步定位在多芯片装置的一部分、第一封装基板和第二封装基板之间。

170.示例35可以包括示例34的芯片组件,还包括:物理上定位在第一封装基板和第二封装基板之间的分立部件;以及电耦合到分立部件的分立焊盘,其中第一各向异性层进一步定位在多芯片装置的一部分和分立焊盘之间。

171.示例36可以包括一种方法,其包括:形成包括第一表面的板,该第一表面包括一个或多个板焊盘;将各向异性材料放置在板的第一表面的至少一部分上;形成包括第一表面的封装基板,该第一表面包括一个或多个引脚;相对于一个或多个引脚将一个或多个焊盘附接至封装基板的第一表面;相对于板来定位封装基板和一个或多个焊盘,使得各向异性材料在板和一个或多个焊盘之间以及板和封装基板的一部分之间;以及固化各向异性材料,使得板机械地耦合到一个或多个焊盘并且机械地耦合到封装基板的部分,并且使得一个或多个焊盘电耦合到一个或多个板焊盘。

172.示例37可以包括示例36的方法,其中封装基板和一个或多个焊盘被定位成使得各向异性层将一个或多个焊盘中的每个焊盘电耦合到一个或多个板焊盘中的不同板焊盘。

173.示例38可以包括示例36和37中任一个的方法,还包括向封装基板施加压力,使得各向异性材料在板和一个或多个焊盘之间以及在板和封装基板的部分之间被压缩。

174.示例39可以包括示例36-38中任一个的方法,其中板被形成为包括板接地层,该板接地层包括板的第一表面,该方法还包括在板接地层中形成一个或多个开口以暴露一个或多个板焊盘,并且其中封装基板和一个或多个焊盘附接到板上,使得一个或多个焊盘定位为接近一个或多个开口。

175.示例40可以包括示例36-39中任一个的方法,其中封装基板包括定位为与第一表面相对的第二表面,该方法还包括:在封装基板的第二表面上形成多个焊料凸块;相对于焊料凸块定位硅管芯;以及固化焊料凸块,使得硅管芯机械耦合并且电耦合到封装基板。

176.示例41可以包括示例36-40中任一个的方法,其中各向异性材料包括各向异性聚合物膏。

177.示例42可以包括一种方法,其包括:形成包括第一表面的板,该第一表面包括多个板焊盘;将第一各向异性材料放置在板的第一表面的至少一部分上;形成包括第一表面、第二表面以及多个装置过孔的桥接装置;形成包括第一表面的封装基板,该第一表面包括多个引脚;相对于多个引脚将第一多个焊盘附接到封装基板的第一表面;相对于多个装置过孔的第一端将第二多个焊盘附接到桥接装置的第一表面;相对于多个装置过孔的第二端将第三多个焊盘附接到桥接装置的第二表面;相对于板定位桥接装置和第三多个焊盘,使得第一各向异性材料在板和第三多个焊盘之间以及板和桥接装置的一部分之间;将第二各向异性材料放置在桥接装置的第一表面的至少一部分和第二多个焊盘上;相对于桥接装置定位封装基板和第一多个焊盘,使得第二各向异性材料在第一多个焊盘和第二多个焊盘之间以及桥接装置的一部分和封装基板的一部分之间;固化第一各向异性材料,使得板机械地耦合到第三多个焊盘和桥接装置的部分,并且使得第三多个焊盘电耦合到多个板焊盘;以及固化第二各向异性材料,使得封装基板的部分机械地耦合到桥接装置的部分并且使得第一多个焊盘机械耦合并且电耦合到第二多个焊盘。

178.示例43可以包括示例42的方法,其中封装基板包括第一封装基板,该方法还包括:形成包括第一表面的第二封装基板,该第一表面包括多个引脚;相对于第二封装基板的多个引脚将第一多个焊盘的一部分附接到第二封装基板的第一表面;在桥接装置的一部分内形成多芯片装置,其中:相对于多芯片装置将第一多个焊盘的一部分附接到第一封装基板;相对于多芯片装置将第一多个焊盘的一部分附接到第二封装基板;并且相对于桥接装置和多芯片装置来定位第二封装基板和第一多个焊盘的附接到第二封装基板的部分,使得第二各向异性材料在第二封装基板的一部分和桥接装置的一部分之间,并且使得第一多个焊盘的附接到第二封装基板的部分机械耦合并且电耦合到多芯片装置和第二多个焊盘。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。