1.本公开总体上涉及半导体存储器装置和该半导体存储器装置的制造方法,更具体地,涉及一种三维半导体存储器装置和该三维半导体存储器装置的制造方法。

背景技术:

2.半导体存储器装置包括能够存储数据的存储器单元。三维半导体存储器装置包括三维布置的存储器单元,以使得基板的每单位面积存储器单元所占据的面积可减小。

技术实现要素:

3.根据本公开的实施方式的半导体存储器装置可包括:多个源极沟道,所述多个源极沟道穿透源极选择线;栅极层叠结构,该栅极层叠结构与源极选择线交叠;连接图案,该连接图案设置在源极选择线和栅极层叠结构之间,该连接图案共同连接到所述多个源极沟道;以及多个垂直沟道,所述多个垂直沟道穿透栅极层叠结构,所述多个垂直沟道共同连接到连接图案。

4.根据本公开的实施方式的半导体存储器装置可包括:第一源极沟道和第二源极沟道,该第一源极沟道和该第二源极沟道彼此平行延伸;第一源极选择线,该第一源极选择线围绕第一源极沟道;第二源极选择线,该第二源极选择线围绕第二源极沟道;栅极层叠结构,该栅极层叠结构与第一源极选择线交叠,该栅极层叠结构延伸以与第二源极选择线交叠;第一垂直沟道,该第一垂直沟道穿透栅极层叠结构的与第一源极选择线交叠的第一区域;第二垂直沟道,该第二垂直沟道穿透栅极层叠结构的与第二源极选择线交叠的第二区域;第一连接图案,该第一连接图案在第一源极选择线与栅极层叠结构之间连接第一源极沟道和第一垂直沟道;第二连接图案,该第二连接图案在第二源极选择线与栅极层叠结构之间连接第二源极沟道和第二垂直沟道;以及源极侧狭缝,该源极侧狭缝设置在第一源极选择线与第二源极选择线之间,该源极侧狭缝在第一连接图案与第二连接图案之间延伸。

5.根据本公开的实施方式的半导体存储器装置可包括:多个源极沟道,所述多个源极沟道穿透源极选择线;栅极层叠结构,该栅极层叠结构与源极选择线交叠;多个垂直沟道,所述多个垂直沟道穿透栅极层叠结构;以及连接图案,该连接图案设置在源极选择线和栅极层叠结构之间以将所述多个垂直沟道连接到所述多个源极沟道,其中,所述多个垂直沟道中的各个垂直沟道的厚度不同于所述多个源极沟道中的各个源极沟道的厚度。

6.根据本公开的实施方式的制造半导体存储器装置的方法可包括以下步骤:形成具有交替地层叠在牺牲基板的第一区域上的多个层间绝缘层和多个导电图案的初步栅极层叠结构,其中,该初步栅极层叠结构由存储器层和多个垂直沟道穿透;在初步栅极层叠结构上形成连接到所述多个垂直沟道的导电层;在导电层上形成第一绝缘层和选择栅极层;以及形成穿透第一绝缘层、选择栅极层和导电层的源极侧狭缝,使得选择栅极层被隔离成多个源极选择线,并且导电层被隔离成多个连接图案。

附图说明

7.在附图中,为了例示清晰,尺寸可能被夸大。将理解,当元件被称为在两个元件“之间”时,其可以是这两个元件之间的仅有元件,或者也可存在一个或更多个中间元件。相似的标号始终表示相似的元件。

8.图1是示出根据本公开的实施方式的半导体存储器装置的存储块的电路图。

9.图2是示意性地示出根据本公开的实施方式的半导体存储器装置的立体图。

10.图3a至图3c示出根据本公开的实施方式的半导体存储器装置的源极选择线、栅极层叠结构和位线的布局。

11.图4a和图4b示出根据本公开的实施方式的半导体存储器装置的栅极层叠结构和位线的布局。

12.图5a至图5c是示出源极沟道的各种实施方式的平面图。

13.图6a至图6c是示出根据本公开的实施方式的半导体存储器装置的截面图。

14.图7a至图7b是示出根据本公开的实施方式的垂直沟道的横截面和源极沟道的横截面的放大图。

15.图8a、图8b、图9a、图9b、图10a、图10b、图10c、图10d、图10e、图10f、图11、图12a、图12b和图12c是示出根据本公开的实施方式的半导体存储器装置的制造方法的截面图。

16.图13是示出根据本公开的实施方式的存储器系统的配置的框图。

17.图14是示出根据本公开的实施方式的计算系统的配置的框图。

具体实施方式

18.为了描述根据本公开的概念的实施方式,本文所公开的具体结构或功能描述仅是例示性的。根据本公开的概念的实施方式可按照各种形式实现,它们不应被解释为限于本文所阐述的特定实施方式。

19.以下,术语“第一”和“第二”用于将一个组件与另一组件相区分,并非意在暗示组件的特定数量或顺序。术语可用于描述各种组件,但是组件不受这些术语限制。

20.此外,将理解,当元件被称为“连接”或“联接”到另一元件时,它可直接连接或联接到另一元件,或者可存在中间元件。相反,当元件被称为“直接连接”或“直接联接”到另一元件时,不存在中间元件。

21.实施方式提供了一种半导体存储器装置和该半导体存储器装置的制造方法,其可改进三维半导体存储器装置的制造工艺的稳定性并改进三维半导体存储器装置的操作可靠性。

22.图1是示出根据本公开的实施方式的半导体存储器装置的存储块blk的电路图。

23.参照图1,半导体存储器装置可包括多个存储块blk。各个存储块blk可包括连接到公共源极层csl和位线bl的多个存储器单元串ms1和ms2。

24.多个存储器单元串ms1和ms2可通过源极选择晶体管sst连接到公共源极层csl。多个存储器单元串ms1和ms2可通过漏极选择晶体管dst连接到位线bl。存储器单元串ms1和ms2中的每一个可包括串联连接的多个存储器单元mc。

25.源极选择晶体管sst的栅极可连接到彼此隔离的源极选择线ssl1和ssl2。漏极选择晶体管dst的栅极可连接到彼此隔离的漏极选择线dsl1和dsl2。多个存储器单元mc的栅

极可连接到多条字线wl。字线wl可设置在不同的高度处,并且设置在相同高度处的存储器单元mc的栅极可连接到单条字线wl。

26.以下,将主要基于存储块blk包括彼此隔离的第一源极选择线ssl1和第二源极选择线ssl2以及彼此隔离的第一漏极选择线dsl1和第二漏极选择线dsl2的实施方式来描述本公开。然而,本公开不限于此,存储块blk可包括彼此隔离的三条或更多条源极选择线和彼此隔离的三条或更多条漏极选择线。

27.多个存储器单元串ms1和ms2可连接到各条字线wl。多个存储器单元串ms1和ms2可包括可通过第一源极选择线ssl1和第二源极选择线ssl2单独地选择的第一组和第二组。第一组可包括第一存储器单元串ms1,并且第二组可包括第二存储器单元串ms2。

28.第一存储器单元串ms1可通过连接到第一漏极选择线dsl1的漏极选择晶体管dst分别连接到位线bl。第二存储器单元串ms2可通过连接到第二漏极选择线dsl2的漏极选择晶体管dst分别连接到位线bl。换言之,第一存储器单元串ms1和第二存储器单元串ms2当中的一对第一存储器单元串ms1和第二存储器单元串ms2可连接到与一对第一存储器单元串ms1和第二存储器单元串ms2对应的位线bl。

29.第一存储器单元串ms1可通过连接到第一源极选择线ssl1的源极选择晶体管sst连接到公共源极层csl,第二存储器单元串ms2可通过连接到第二源极选择线ssl2的源极选择晶体管sst连接到公共源极层csl。因此,多个存储器单元串ms1和ms2可被同时隔离成多组,可在读操作或验证操作中为源极选择线ssl1和ssl2中的每一个单独地选择这些组。在实施方式中,在读操作或验证操作中,选择第一源极选择线ssl1和第二源极选择线ssl2中的一个以使得第一存储器单元串ms1的第一组和第二存储器单元串ms2的第二组中的一个可连接到公共源极层csl。因此,在本公开中,与第一存储器单元串ms1和第二存储器单元串ms2在读操作或验证操作中同时连接到公共源极层csl时相比,沟道电阻可减小。因此,在本公开中,读扰动可减少。

30.图2是示意性地示出根据本公开的实施方式的半导体存储器装置的立体图。

31.参照图2,半导体存储器装置可包括:源极选择线ssl1[a]、ssl2[a]、ssl1[b]和ssl2[b],其通过源极侧狭缝ss1和ss2彼此隔离;源极沟道sc1[a]、sc2[a]、sc1[b]和sc2[b],其穿透源极选择线ssl1[a]、ssl2[a]、ssl1[b]和ssl2[b];连接图案cp1[a]、cp2[a]、cp1[b]和cp2[b],其分别与源极选择线ssl1[a]、ssl2[a]、ssl1[b]和ssl2[b]交叠;垂直沟道vc1[a]、vc2[a]、vc1[b]和vc2[b],其与连接图案cp1[a]、cp2[a]、cp1[b]和cp2[b]接触;以及栅极层叠结构gst[a]和gst[b],其围绕垂直沟道vc1[a]、vc2[a]、vc1[b]和vc2[b]。

[0032]

半导体存储器装置可包括通过狭缝si彼此隔离的第一栅极层叠结构gst[a]和第二栅极层叠结构gst[b]。

[0033]

第一栅极层叠结构gst[a]可包括多条字线wl[a]以及与多条字线wl[a]交叠并通过漏极侧狭缝sd彼此隔离的漏极选择线。

[0034]

在实施方式中,第一栅极层叠结构gst[a]可包括与多条字线wl[a]的第一区域r1交叠的第一漏极选择线dsl1[a]以及与多条字线wl[a]的第二区域r2交叠的第二漏极选择线dsl2[a]。多条字线wl[a]可包括第三区域r3。第三区域r3可设置在第一区域r1和第二区域r2之间并且可将第一区域r1和第二区域r2彼此连接。漏极侧狭缝sd可设置在第一漏极选择线dsl1[a]和第二漏极选择线dsl2[a]之间并且可与字线wl[a]的第三区域r3交叠。

[0035]

第一漏极选择线dsl1[a]和字线wl[a]的第一区域r1可由在第一方向d1上延伸的多个第一垂直沟道vc1[a]穿透。第二漏极选择线dsl2[a]和字线wl[a]的第二区域r2可由在第一方向d1上延伸的多个第二垂直沟道vc2[a]穿透。

[0036]

字线wl[a]、第一漏极选择线dsl1[a]和第二漏极选择线dsl2[a]中的每一个可沿着与第一方向d1相交的平面延伸。在实施方式中,字线wl[a]、第一漏极选择线dsl1[a]和第二漏极选择线dsl2[a]中的每一个可在第二方向d2和第三方向d3上延伸。狭缝si和漏极侧狭缝sd可在第二方向d2上延伸。第一漏极选择线dsl1[a]和第二漏极选择线dsl2[a]可在第三方向d3上彼此相邻。第一方向d1、第二方向d2和第三方向d3可分别对应于xyz坐标系中x轴、y轴和z轴面向的方向。

[0037]

字线wl[a]的第三区域r3可由多个虚设沟道dvc[a]穿透。虚设沟道dvc[a]可在第二方向d2上布置成一排。漏极侧狭缝sd可与虚设沟道dvc[a]交叠。在另一实施方式中,可省略虚设沟道dvc[a]。与图2所示的实施方式相比,在省略虚设沟道dvc[a]的实施方式中,在第三方向d3上限定在第一漏极选择线dsl1[a]和第二漏极选择线dsl2[a]之间的距离可变窄。

[0038]

类似于第一栅极层叠结构gst[a],第二栅极层叠结构gst[b]可包括多条字线wl[b]以及通过漏极侧狭缝sd彼此隔离的第一漏极选择线dsl1[b]和第二漏极选择线dsl2[b]。另外,类似于第一栅极层叠结构gst[a],第二栅极层叠结构gst[b]可由多个第一垂直沟道vc1[b]、多个第二垂直沟道vc2[b]和多个虚设沟道dvc[b]穿透。

[0039]

第一栅极层叠结构gst[a]和第二栅极层叠结构gst[b]可与源极选择线ssl1[a]、ssl2[a]、ssl1[b]和ssl2[b]交叠。源极选择线ssl1[a]、ssl2[a]、ssl1[b]和ssl2[b]可在基本上相同的高度处彼此隔离。源极选择线ssl1[a]、ssl2[a]、ssl1[b]和ssl2[b]可包括第一组的第一源极选择线ssl1[a]和第二源极选择线ssl2[a]以及第二组的第一源极选择线ssl2[a]和第二源极选择线ssl2[b]。第一组的第一源极选择线ssl1[a]和第二源极选择线ssl2[a]可设置在第一栅极层叠结构gst[a]和公共源极层csl之间。第二组的第一源极选择线ssl2[a]和第二源极选择线ssl2[b]可设置在第二栅极层叠结构gst[b]和公共源极层csl之间。

[0040]

第一栅极层叠结构gst[a]的多条字线wl[a]可延伸以与第一组的第一源极选择线ssl1[a]和第二源极选择线ssl2[a]交叠。字线wl[a]的第一区域r1可与第一组的第一源极选择线ssl1[a]交叠,字线wl[a]的第二区域r2可与第一组的第二源极选择线ssl2[a]交叠。第一组的第一源极选择线ssl1[a]可通过在第二方向d2上延伸的第一源极侧狭缝ss1与第一组的第二源极选择线ssl2[a]间隔开。

[0041]

类似于第一栅极层叠结构gst[a],第二栅极层叠结构gst[b]的多条字线wl[b]可与彼此间隔开的第二组的第一源极选择线ssl1[b]和第二源极选择线ssl2[b]交叠。第一组的第一源极选择线ssl1[a]和第二源极选择线ssl2[a]可通过在第二方向d2上延伸的第二源极侧狭缝ss2与第二组的第一源极选择线ssl1[b]和第二源极选择线ssl2[b]间隔开。

[0042]

源极沟道sc1[a]、sc2[a]、sc1[b]和sc2[b]可包括第一组的源极沟道sc1[a]和sc2[a]以及第二组的源极沟道sc1[b]和sc2[b]。

[0043]

第一组的源极沟道sc1[a]和sc2[a]可包括多个第一源极沟道sc1[a]和多个第二源极沟道sc2[a]。多个第一源极沟道sc1[a]可由第一组的第一源极选择线ssl1[a]围绕。多

个第二源极沟道sc2[a]可由第一组的第二源极选择线ssl2[a]围绕。

[0044]

类似于第一组的源极沟道sc1[a]和sc2[a],第二组的源极沟道sc1[b]和sc2[b]可包括由第二组的第一源极选择线ssl1[b]围绕的多个第一源极沟道sc1[b]以及由第二组的第二源极选择线ssl2[b]围绕的多个第二源极沟道sc2[b]。

[0045]

第一组和第二组的源极沟道sc1[a]、sc2[a]、sc1[b]和sc2[b]可在第一方向d1上延伸以共同连接到公共源极层csl。

[0046]

第一源极侧狭缝ss1和第二源极侧狭缝ss2可在连接图案cp1[a]、cp2[a]、cp1[b]和cp2[b]之间延伸。连接图案cp1[a]、cp2[a]、cp1[b]和cp2[b]可设置在基本上相同的高度处。连接图案cp1[a]、cp2[a]、cp1[b]和cp2[b]可包括第一组的第一连接图案cp1[a]和第二连接图案cp2[a]以及第二组的第一连接图案cp1[b]和第二连接图案cp2[b]。

[0047]

第一组的第一连接图案cp1[a]可设置在第一组的第一源极选择线ssl1[a]和第一栅极层叠结构gst[a]之间。第一组的第二连接图案cp2[a]可设置在第一组的第二源极选择线ssl2[a]和第一栅极层叠结构gst[a]之间。第一组的第一连接图案cp1[a]和第二连接图案cp2[a]可平行于第一组的第一源极选择线ssl1[a]和第二源极选择线ssl2[a]延伸。

[0048]

多个第一源极沟道sc1[a]可延伸以与第一连接图案cp1[a]接触。多个第一垂直沟道vc1[a]可共同连接到第一连接图案cp1[a],并且可通过第一连接图案cp1[a]连接到多个第一源极沟道sc1[a]。多个第二源极沟道sc2[a]可延伸以与第二连接图案cp2[a]接触。多个第二垂直沟道vc2[a]可共同连接到第二连接图案cp2[a],并且可通过第二连接图案cp2[a]连接到多个第二源极沟道sc2[a]。

[0049]

第二组的第一连接图案cp1[b]和第二连接图案cp2[b]可具有与第一组的第一连接图案cp1[a]和第二连接图案cp2[a]相似的结构。狭缝si可在第一组的第一连接图案cp1[a]和第二连接图案cp2[a]与第二组的第一连接图案cp1[b]和第二连接图案cp2[b]之间延伸,并且狭缝si可连接到第二源极侧狭缝ss2。

[0050]

图3a至图3c示出根据本公开的实施方式的半导体存储器装置的源极选择线、栅极层叠结构和位线的布局。

[0051]

图3a是示出第一组的第一源极选择线ssl1[a]和第二源极选择线ssl2[a]以及第二组的第一源极选择线ssl[b]的实施方式的平面图。

[0052]

参照图3a,源极选择线ssl1[a]、ssl2[a]和ssl1[b]可分别围绕在第一方向d1上延伸的源极沟道sc1[a]、sc2[a]和sc1[b]。源极沟道sc1[a]、sc2[a]和sc1[b]中的每一个的侧壁可由栅极绝缘层gi围绕。换言之,栅极绝缘层gi可设置在源极选择线ssl1[a]、ssl2[a]和ssl1[b]中的每一个与源极沟道sc1[a]、sc2[a]和sc1[b]中的每一个之间。

[0053]

第一源极侧狭缝ss1和第二源极侧狭缝ss2可在第二方向d2上延伸。第一源极侧狭缝ss1和第二源极侧狭缝ss2中的每一个可具有诸如波浪形状和线性形状的各种形状。

[0054]

图3b是示出与图3a所示的第一组的第一源极选择线ssl1[a]和第二源极选择线ssl2[a]交叠的第一栅极层叠结构gst[a]以及与图3a所示的第二组的第一源极选择线ssl1[b]交叠的第二栅极层叠结构gst[b]的平面图。

[0055]

参照图3b,第一栅极层叠结构gst[a]的多条字线wla和漏极选择线dsl1[a]和dsl2[a]可通过狭缝si与第二栅极层叠结构gst[b]的多条字线wl[b]和漏极选择线dsl1[b]间隔开。与字线(例如,wl[a])交叠的漏极侧狭缝sd可与虚设沟道(例如,dvc[a])交叠。

[0056]

狭缝si和漏极侧狭缝sd中的每一个可具有诸如波浪形状和线性形状的各种形状。在实施方式中,狭缝si和漏极侧狭缝sd中的每一个可具有线性形状。

[0057]

字线wl[a]和wl[b]以及漏极选择线dsl1[a]、dsl2[a]和dsl1[b]可围绕垂直沟道vc1[a]、vc2[a]和vc1[b]。垂直沟道vc1[a]、vc2[a]和vc1[b]中的每一个的侧壁可由存储器层ml围绕。换言之,存储器层ml可设置在字线wl[a]和wl[b]以及漏极选择线dsl1[a]、dsl2[a]和dsl1[b]中的每一个与垂直沟道vc1[a]、vc2[a]和vc1[b]中的每一个之间。

[0058]

源极沟道sc1[a]、sc2[a]和sc1[b]中的每一个的横截面面积可比垂直沟道vc1[a]、vc2[a]和vc1[b]中的每一个的横截面面积宽。垂直沟道vc1[a]、vc2[a]和vc1[b]中的一些的中心轴可能不与源极沟道sc1[a]、sc2[a]和sc1[b]的中心轴交叠,而是可与源极沟道sc1[a]、sc2[a]和sc1[b]的中心轴错位。垂直沟道vc1[a]、vc2[a]和vc1[b]中的一些可能不与源极沟道sc1[a]、sc2[a]和sc1[b]交叠。垂直沟道vc1[a]、vc2[a]和vc1[b]中的两个或更多个可与源极沟道sc1[a]、sc2[a]和sc1[b]中的一些交叠。

[0059]

虚设沟道dvc[a]可能不与源极沟道sc1[a]、sc2[a]和sc1[b]交叠。虚设沟道dvc[a]可沿着漏极侧狭缝sd的延伸方向布置成一排。

[0060]

图3c是示出与图3b所示的垂直沟道vc1[a]、vc2[a]和vc1[b]交叠的位线bl的平面图。

[0061]

参照图3c,各条位线bl可通过接触插塞ct连接到参照图3b描述的垂直沟道vc1[a]、vc2[a]和vc1[b]。连接到单条位线的垂直沟道vc1[a]、vc2[a]和vc1[b]可由不同的漏极选择线dsl1[a]、dsl2[a]和dsl1[b]单独地控制,如图3b所示。

[0062]

图4a和图4b示出根据本公开的实施方式的半导体存储器装置的栅极层叠结构和位线的布局。

[0063]

图4a是示出第一栅极层叠结构gst[a]和第二栅极层叠结构gst[b]的平面图。图4a示出第一栅极层叠结构gst[a]的多条字线wl[a]和漏极选择线dsl1[a]和dsl2[a]以及第二栅极层叠结构gst[b]的多条字线wl[b]和漏极选择线dsl1[b]的布局。

[0064]

参照图4a,与多条字线(例如,wl[a])交叠的漏极侧狭缝sd可具有与第一栅极层叠结构gst[a]和第二栅极层叠结构gst[b]之间的狭缝si不同的形状。在实施方式中,狭缝si可在第二方向d2上以线性形状延伸,漏极侧狭缝sd可在第二方向d2上以波浪形状延伸。

[0065]

第一栅极层叠结构gst[a]和第二栅极层叠结构gst[b]可被由存储器层ml围绕的垂直沟道vc1[a]、vc2[a]和vc1[b]穿透。垂直沟道vc1[a]、vc2[a]和vc1[b]可按锯齿形布置。漏极侧狭缝sd可具有与彼此相邻的垂直沟道(例如,vc1[a]和vc2[a])的侧壁形状对应的波浪形侧壁,漏极侧狭缝sd插置在垂直沟道(vc1[a]和vc2[a])之间。

[0066]

图4b是示出与图4a所示的垂直沟道vc1[a]、vc2[a]和vc1[b]交叠的位线bl的平面图。

[0067]

参照图4b,各条位线bl可通过接触插塞ct连接到参照图4a描述的垂直沟道vc1[a]、vc2[a]和vc1[b]。连接到单条位线的垂直沟道vc1[a]、vc2[a]和vc1[b]可由不同的漏极选择线dsl1[a]、dsl2[a]和dsl1[b]单独地控制,如图4a所示。

[0068]

图5a至图5c是示出源极沟道cs的各种实施方式的平面图。

[0069]

参照图5a至图5c,各个源极沟道sc可由源极选择线ssl围绕,栅极绝缘层gi插置在它们之间。源极沟道sc可具有各种布局。

[0070]

参照图5a至图5c,各个源极沟道sc可在第一方向d1上延伸并且具有椭圆形横截面形状。各个源极沟道sc的横截面形状不限于椭圆形形状并且可具有诸如圆形形状和多边形形状的各种形状。

[0071]

参照图5a,在实施方式中,椭圆形形状的短轴和长轴可分别平行于在第二方向d2上延伸的轴和在第三方向d3上延伸的轴。参照图5b和图5c,在另一实施方式中,椭圆形形状的短轴和长轴可分别面向相对于在第二方向d2上延伸的轴和在第三方向d3上延伸的轴的倾斜方向。

[0072]

参照图5a至图5c,源极沟道sc可包括沿着第二方向d2布置的沟道列。在实施方式中,如图5a和图5c所示,源极沟道sc可包括一个沟道列。在另一实施方式中,如图5b所示,源极沟道sc可包括两个沟道列。然而,本公开不限于此,源极沟道sc可包括三个或更多个沟道列。

[0073]

图6a至图6c是示出根据本公开的实施方式的半导体存储器装置的截面图。图6a和图6c示出半导体存储器装置的单元阵列区域,图6b示出半导体存储器装置的连接区域。

[0074]

参照图6a至图6c,半导体存储器装置可包括:外围电路结构10;栅极层叠结构gst,其与外围电路结构10交叠并且围绕多个垂直沟道vc1和vc2;公共源极层csl,其设置在栅极层叠结构gst和外围电路结构gst之间;源极选择线ssl1和ssl2,其设置在公共源极层csl和栅极层叠结构gst之间基本上相同的高度处以彼此间隔开;连接图案cp1和cp2,其设置在源极选择线ssl1和ssl2与栅极层叠结构gst之间基本上相同的高度处以彼此间隔开;以及位线bl,其与连接图案cp1和cp2交叠,栅极层叠结构gst插置在它们之间。

[0075]

栅极层叠结构gst可包括在垂直沟道vc1和vc2延伸的第一方向d1上交替地层叠的层间绝缘层51和导电图案53。导电图案53可由各种导电材料形成。导电图案53可包括分别与源极选择线ssl1和ssl2交叠的漏极选择线dsl1和dsl2以及设置在漏极选择线dsl1和dsl2与源极选择线ssl1和ssl2之间并且彼此间隔开的字线wl。

[0076]

栅极层叠结构gst可由垂直沟道vc1和vc2穿透。垂直沟道vc1和vc2中的每一个可包括垂直芯绝缘层43和垂直沟道层41。垂直沟道层41可沿着垂直芯绝缘层43的侧壁延伸并且可沿着垂直芯绝缘层43的面向位线bl的表面延伸。垂直沟道层41可包括可用作存储器单元串的沟道的半导体层。在实施方式中,垂直沟道层41可包括硅。

[0077]

垂直沟道vc1和vc2中的每一个的侧壁可由存储器层ml围绕。存储器层ml的部分区域可用作数据存储区域。存储器层ml的部分区域可限定在垂直沟道vc1和vc2中的每一个与字线wl的交叉部分处。

[0078]

位线bl可由各种导电材料形成。位线bl可与栅极层叠结构gst间隔开。在实施方式中,位线bl可通过第一上绝缘层83和第二上绝缘层87与栅极层叠结构gst绝缘。第一上绝缘层83和第二上绝缘层37可在位线bl与栅极层叠结构gst之间延伸。位线bl可通过由导电材料形成的接触插塞ct连接到垂直沟道vc1和vc2。各个接触插塞ct可在垂直沟道层41与位线bl之间穿透上绝缘层83和87以及存储器层ml并且可与垂直沟道层41和位线bl接触。

[0079]

连接图案cp1和cp2中的每一个可包括掺杂半导体层47。在实施方式中,掺杂半导体层47可包括掺杂硅层。掺杂半导体层47可包括导电型杂质。在实施方式中,掺杂半导体层47可包括诸如磷的n型杂质。掺杂半导体层47可包括平行于源极选择线ssl1和ssl2中的每一个延伸的线部47a以及从线部47a朝着垂直芯绝缘层43突出的突出部47b。掺杂半导体层

47的突出部47b可具有由垂直沟道层41围绕的侧壁。

[0080]

垂直沟道层41可朝着掺杂半导体层47的线部47a比垂直芯绝缘层43突出更远,以围绕掺杂半导体层47的突出部74b的侧壁。垂直沟道层41可与掺杂半导体层47的突出部47b接触。由于突出部47b包括导电型掺杂剂,所以突出部47b的比电阻可低于未掺杂半导体层的比电阻。由于垂直沟道层41与具有低比电阻的突出部47b接触,所以垂直沟道层41中的沟道电流可改进。

[0081]

源极选择线ssl1和ssl2可由各种导电材料形成。源极选择线ssl和ssl2可与连接图案cp1和cp2和公共源极层csl间隔开。在实施方式中,源极选择线ssl和ssl2可通过第一绝缘层55与连接图案cp1和cp2绝缘,并且可通过第二绝缘层59与公共源极层csl绝缘。第一绝缘层55可在连接图案cp1和cp2与源极选择线ssl1和ssl2之间延伸。第二绝缘层59可在源极选择线ssl1和ssl2与公共源极层csl之间延伸。

[0082]

第一绝缘层55、源极选择线ssl1和ssl2以及第二绝缘层59可被源极沟道sc1和sc2穿透。源极沟道sc1和sc2中的每一个可包括源极芯绝缘层63和源极沟道层61。源极沟道层61可沿着源极芯绝缘层63的侧壁延伸,并且可沿着源极芯绝缘层63的面向连接图案cp1和cp2的表面延伸。源极沟道层61可包括半导体层,其可用作源极选择晶体管的沟道。在实施方式中,源极沟道层61可包括硅。源极沟道sc1和sc2中的每一个的面向源极选择线ssl和ssl2的侧壁可由栅极绝缘层gi围绕。

[0083]

公共源极层csl可包括平行于源极选择线ssl1和ssl2延伸的线部67a以及从线部67a朝着源极芯绝缘层63突出的突出部67b。公共源极层csl可包括掺杂半导体层。在实施方式中,公共源极层csl可包括掺杂硅层。公共源极层csl的掺杂半导体层可包括导电型杂质。在实施方式中,公共源极层csl的掺杂半导体层可包括诸如磷的n型杂质。公共源极层csl的突出部67b可具有由源极沟道层61围绕的侧壁。

[0084]

源极沟道层61可朝着公共源极层csl的线部67a比源极芯绝缘层63突出更远,以围绕公共源极层csl的突出部67b的侧壁。源极沟道层61可与公共源极层csl的突出部67接触。由于突出部67b包括导电型掺杂剂,所以突出部67b的比电阻可低于未掺杂半导体层的比电阻。由于源极沟道层61与具有低比电阻的突出部67b接触,所以源极沟道层61中的沟道电流可改进。

[0085]

第一接合绝缘层71可设置在公共源极层csl与外围电路结构10之间。第一接合绝缘层71可在第二方向d2上比栅极层叠结构gst、源极选择线ssl1和ssl2和公共源极线csl中的每一个突出更远,如图6b所示。第一上绝缘层83与第一接合绝缘层71的在第二方向d2上比公共源极线csl突出更远的部分之间的空间可由第一绝缘结构90填充,如图6b所示。

[0086]

外围电路结构10可包括:基板1,其包括多个晶体管20;第二绝缘结构31,其覆盖第一基板1;多个互连结构29,其被掩埋在第二绝缘结构31中;以及第二接合绝缘层33,其覆盖多个互连结构29和第二绝缘结构31。互连结构29可连接到晶体管20并且可发送电信号。

[0087]

基板1可包括诸如硅基板或锗基板的半导体基板。第一基板1可包括通过隔离层3分隔的有源区域。晶体管20可设置在有源区域上。各个晶体管20可包括层叠在基板1的有源区域上的栅极绝缘层11和栅电极13以及在栅电极13的两侧限定在基板1中的结15。当在基板1的有源区域中掺杂p型杂质和n型杂质中的至少一种时,可限定结15。

[0088]

多个晶体管20可被包括在外围电路中以控制半导体存储器装置的操作。在实施方

式中,至少一个晶体管20可被包括在源极控制电路5中。源极控制电路5可通过一些互连结构29连接到公共源极层csl,并且可控制公共源极层csl的放电。在实施方式中,连接到源极控制电路5的互连结构29可包括下接触结构21、互连线23和上接触结构25。下接触结构21可连接到源极控制电路5的结15,如图6a所示。下接触结构21可包括依次层叠在结15上的图案21a、21b和21c。上接触结构25可设置在连接区域中。互连线23可与图6a所示的下接触结构21接触,并且可延伸到图6b所示的连接区域以与上接触结构25接触。换言之,下接触结构21和上接触结构25可通过互连线23彼此连接。

[0089]

第二绝缘结构31可包括多层绝缘层,其各自包括两个或更多个层。

[0090]

第一接合绝缘层71和第二接合绝缘层33可彼此接合,从而形成接合结构bs。

[0091]

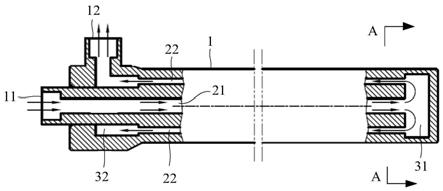

图6a是沿着与位线bl交叉的线截取的半导体存储器装置的截面图,并且对应于沿着图4b所示的线a-a’截取的截面图。

[0092]

参照图6a,源极沟道sc1可在相同区域中以比垂直沟道vc1的密度低的密度连接到连接图案cp1。在实施方式中,连接到连接图案cp1的源极沟道sc1的数量可小于连接到连接图案cp1的垂直沟道vc1的数量。

[0093]

源极沟道层61可包括具有接触图案61a和柱部61b的半导体层。接触图案61a可连接到连接图案cp1。柱部61b可在第一方向d1上从接触图案61a的边缘朝着公共源极层csl延伸。源极芯绝缘层63的侧壁可在接触图案61a和公共源极层csl之间由源极沟道层61的柱部61b围绕。源极沟道层61的柱部61b可延伸以围绕公共源极层csl的突出部67b。

[0094]

掺杂半导体层47的杂质可扩散到接触图案61a中,并且公共源极层csl的杂质可扩散到柱部61b的与公共源极层csl的突出部67b接触的部分中。柱部61b可包括未掺杂区域ua。柱部61b的未掺杂区域ua可被定义为掺杂半导体层47的杂质和公共源极层csl的杂质未扩散到的区域。更具体地,柱部61b的部分区域可作为未掺杂区域ua保留在连接图案cp1和公共源极层csl之间的高度处。在实施方式中,柱部61b的未掺杂区域ua可保留在源极选择线ssl1设置的高度处。可通过柱部61b的未掺杂区域ua改进连接到源极选择线ssl1的源极选择晶体管的截止特性。

[0095]

垂直芯绝缘层43可包括面向彼此相反的方向的第一表面su1和第二表面su2。第一表面su1可面向连接图案cp1,第二表面su2可面向位线bl。垂直沟道层41可沿着垂直芯绝缘层43的第二表面su2延伸,并且可在垂直芯绝缘层43和栅极层叠结构gst之间延伸。

[0096]

位线bl可在第二方向d2上以比垂直沟道vc1的间距窄的间距布置。位线bl可穿透第三上绝缘层99并且可与接触插塞ct接触。

[0097]

图6b示出图6a所示的源极选择线ssl和公共源极层csl的端部。图6b是沿着平行于第二方向d2的线截取的公共源极层csl和源极选择线ssl1的截面图。

[0098]

参照图6b,公共源极线csl和源极选择线ssl1可在第二方向d2上延伸。源极选择线ssl1的端部和公共源极层csl的端部可形成阶梯结构。更具体地,公共源极层csl可包括朝着第二方向d2比源极选择线ssl1突出更远的接触区域cta。

[0099]

公共源极层csl可通过第一垂直接触插塞85a、上导电图案ucp和第二垂直接触插塞85b连接到互连结构29。第一垂直接触插塞85a可与公共源极层csl的接触区域cta接触,并且第二垂直接触插塞85b可与互连结构29接触。上导电图案ucp可将第一垂直接触插塞85a和第二垂直接触插塞85b彼此连接。

[0100]

第一垂直接触插塞85a和第二垂直接触插塞85b可彼此平行延伸以穿透第一绝缘结构90和第一上绝缘层83,并且可由各种导电材料形成。第一绝缘结构90可包括多层绝缘层。在实施方式中,第一绝缘结构90可包括第一填充绝缘层91、第二填充绝缘层95和第三填充绝缘层97。第一填充绝缘层91可如图6a所示设置在与栅极层叠结构gst相同的高度处,并且可延伸到掺杂半导体层47的线部47a设置的高度。第二填充绝缘层95可设置在与源极选择线ssl1和第一绝缘层55的层叠结构相同的高度处。第三填充绝缘层97可设置在与第二绝缘层59和公共源极层csl的层叠结构相同的高度处。

[0101]

第一垂直接触插塞85a可在第一方向d1上延伸以穿透第一上绝缘层83、第一填充绝缘层91、第二填充绝缘层95和第二绝缘层59。第一垂直接触插塞85a可包括与公共源极层csl的接触区域cta接触的表面。

[0102]

第二垂直接触插塞85b可在第一方向d1上延伸以穿透第一上绝缘层83、第一填充绝缘层91、第二填充绝缘层95、第三填充绝缘层97和接合结构bs。第二垂直接触插塞85b可包括与互连结构29的上接触结构25接触的表面。上接触结构25可以是互连结构29的连接到源极控制电路5的部分,如图6a所示。上接触结构25可包括与互连线23接触的通孔插塞以及设置在通孔插塞25a与第二垂直接触插塞85b之间的焊盘图案25b。

[0103]

上导电图案ucp可通过第一通孔插塞89a和第二通孔插塞89b连接到第一垂直接触插塞85a和第二垂直接触插塞85b。第一通孔插塞89a和第二通孔插塞89b可由与接触插塞ct相同的导电材料形成,如图6a所示。第一通孔插塞89a和第二通孔插塞89b可穿透第二上绝缘层87并且可分别与第一垂直接触插塞85a和第二垂直接触插塞85b接触。上导电图案ucp可穿透第三绝缘层99并且可从第一通孔插塞89a朝着第二通孔插塞89b延伸。

[0104]

图6c是沿着平行于位线bl的线截取的半导体存储器装置的截面图。图6c对应于沿着图4b所示的线b-b’截取的截面图。

[0105]

参照图6c,源极沟道sc1和sc2可包括彼此平行延伸的第一源极沟道sc1和第二源极沟道sc2。

[0106]

源极选择线ssl1和ssl2可包括通过源极侧狭缝ss彼此隔离的第一源极选择线ssl1和第二源极选择线ssl2。第一源极选择线ssl1可围绕第一源极沟道sc1的侧壁,第二源极选择线ssl2可围绕第二源极沟道sc2的侧壁。

[0107]

垂直沟道vc1和vc2可包括第一垂直沟道vc1和第二垂直沟道vc2。第一垂直沟道vc1可与第一源极选择线ssl1交叠。第二垂直沟道vc2可与第二源极选择线ssl2交叠。

[0108]

连接图案cp1和cp2可包括通过源极侧狭缝ss彼此隔离的第一连接图案cp1和第二连接图案cp2。第一连接图案cp1可在第一源极选择线ssl1和栅极层叠结构gst之间连接第一源极沟道sc1和第一垂直沟道vc1。第二连接图案cp2可在第二源极选择线ssl2和栅极层叠结构gst之间连接第二源极沟道sc2和第二垂直沟道vc2。

[0109]

第二绝缘层59可延伸以填充源极侧狭缝ss。在实施方式中,第二绝缘层59可设置在第一源极选择线ssl1和第二源极选择线ssl2之间。另外,第二绝缘层59可穿透第一绝缘层55并且可在第一连接图案cp1和第二连接图案cp2之间延伸。

[0110]

漏极选择线dsl1和dsl2可包括通过漏极侧狭缝sd彼此隔离的第一漏极选择线dsl1和第二漏极选择线dsl2。第一漏极选择线dsl1可与第一源极选择线ssl1交叠,并且围绕第一垂直沟道vc1。第二漏极选择线dsl2可与第二源极选择线ssl2交叠,并且围绕第二垂

直沟道vc2。

[0111]

用作字线wl的各个导电图案53可在第一漏极选择线dsl1和第一连接图案cp1之间围绕第一垂直沟道vc1。用作字线wl的各个导电图案53可在第二漏极选择线dsl2与第二连接图案cp2之间延伸以围绕第二垂直沟道vc2。

[0112]

第一上绝缘层83可延伸以填充漏极侧狭缝sd。在实施方式中,第一上绝缘层83可穿透层间绝缘层51当中的与第一上绝缘层83相邻的层间绝缘层,并且可在第一漏极选择线dsl1和第二漏极选择线dsl2之间延伸。第一垂直沟道vc1和第二垂直沟道vc2可延伸到第一上绝缘层83的内部。

[0113]

位线bl可在第三方向d3上延伸以与第一连接图案cp1和第二连接图案cp2交叠。位线bl可通过接触插塞ct连接到与位线bl对应的一对第一垂直沟道vc1和第二垂直沟道vc2。

[0114]

图7a至图7b是示出根据本公开的实施方式的垂直沟道vc的横截面和源极沟道sc的横截面的放大图。

[0115]

参照图7a,垂直沟道vc可由导电图案53围绕,并且存储器层ml插置在垂直沟道vc和导电图案53之间。存储器层ml可包括隧道绝缘层ti、数据存储层ds和阻挡绝缘层bi。

[0116]

隧道绝缘层ti可沿着垂直沟道层41的表面延伸。隧道绝缘层ti可包括电荷可隧穿的绝缘材料。在实施方式中,隧道绝缘层ti可包括氧化硅层。

[0117]

数据存储层ds可沿着隧道绝缘层ti的表面延伸。数据存储层ds可包括能够存储数据的材料层。在实施方式中,数据存储层ds可包括能够存储利用福勒-诺德汉姆(fowler nordheim)隧穿而改变的数据的氮化物层。

[0118]

阻挡绝缘层bi可沿着数据存储层ds的表面延伸。阻挡绝缘层bi可包括氧化物层。

[0119]

垂直沟道vc的垂直芯绝缘层43可通过垂直沟道层41与存储器层ml间隔开。

[0120]

参照图7b,源极沟道sc的源极芯绝缘层63可通过栅极绝缘层gi和源极沟道层61与源极选择线ssl间隔开。源极沟道层61的柱部61b可由源极选择线ssl围绕,并且栅极绝缘层gi插置在柱部61b和源极选择线ssl之间。

[0121]

图8a、图8b、图9a、图9b、图10a、图10b、图10c、图10d、图10e、图10f、图11、图12a、图12b和图12c是示出根据本公开的实施方式的半导体存储器装置的制造方法的截面图。

[0122]

图8a和图8b是示出形成初步栅极层叠结构110、导电层137和选择栅极层143的工艺的截面图。

[0123]

参照图8a,可在包括第一区域a1和第二区域a2的牺牲基板101上形成由存储器层123和多个垂直沟道130穿透的初步栅极层叠结构110。牺牲基板101可以是硅基板。

[0124]

初步栅极层叠结构110可形成在牺牲基板101的第一区域a1上。初步栅极层叠结构110可由在第一方向d1上延伸的多个垂直沟道孔121穿透。多个垂直沟道孔121可延伸到牺牲基板101的第一区域a1中。

[0125]

存储器层123可沿着各个垂直沟道孔121的表面延伸。存储器层123可包括图7a所示的阻挡绝缘层bi、数据存储层ds和隧道绝缘层ti。

[0126]

各个垂直沟道130可包括垂直沟道层131和垂直芯绝缘层133。垂直沟道层131可沿着存储器层123的表面延伸,并且垂直沟道孔121的中央区域可敞开。垂直沟道层131可包括半导体层。在实施方式中,垂直沟道层131可包括未掺杂硅。垂直芯绝缘层133可设置在垂直沟道孔121的通过垂直沟道层131敞开的中央区域中。

[0127]

初步栅极层叠结构110可包括在牺牲基板101的第一区域a1上交替地层叠的层间绝缘层111和导电图案113。层间绝缘层111和导电图案113可围绕多个垂直沟道130,并且存储器层123插置在多个垂直沟道130与层间绝缘层111和导电图案113中的每一个之间。多个垂直沟道130可包括第一垂直沟道130a和第二垂直沟道130b。

[0128]

随后,可在初步栅极层叠结构110上形成连接到多个垂直沟道130的导电层137。导电层137可包括掺杂半导体层。在实施方式中,导电层137可包括掺杂硅层,并且掺杂硅层可包括n型杂质。导电层137可朝着各个垂直沟道孔121的中央区域延伸。

[0129]

在实施方式中,形成导电层137的工艺可包括蚀刻垂直芯绝缘层133的一部分以使得在垂直沟道孔121的中央区域中限定第一凹陷区域135的工艺以及在初步栅极层叠结构110上形成掺杂半导体层以填充第一凹陷区域135的工艺。垂直沟道层131的内壁的一部分可通过第一凹陷区域135暴露。

[0130]

导电层137和初步栅极层叠结构110可被构图以不与牺牲基板101的第二区域a2交叠。第二区域a2可以是从牺牲基板101的第一区域a1延伸的区域。在示例中,第二区域a2可从第一区域a1在与多个垂直沟道130交叉的第二方向d2上延伸。

[0131]

随后,可形成第一填充绝缘层115。第一填充绝缘层115可覆盖牺牲基板101的通过导电层137和初步栅极层叠结构110敞开的第二区域a2。第一填充绝缘层115可延伸直至导电层137设置的高度。

[0132]

参照图8b,可在导电层137上形成第一绝缘层141和选择栅极层143。第一绝缘层141和选择栅极层143可延伸以覆盖第一填充绝缘层115。选择栅极层143可由各种导电材料形成。

[0133]

图9a和图9b是示出在参照图8b描述的工艺之后继续的形成源极选择线143s的工艺的截面图。图9a是沿着平行于源极选择线143s中的一个的轴线截取的截面图。图9b是沿着与源极选择线143s交叉的轴线截取的截面图。

[0134]

参照图9a和图9b,可通过蚀刻选择栅极层143、第一绝缘层141和导电层137来形成穿透图8b所示的选择栅极层143、第一绝缘层141和导电层137的源极侧狭缝145。因此,选择栅极层143可被隔离成多条源极选择线143s,导电层137可被隔离成多个连接图案137cp。

[0135]

多条源极选择线143s可包括第一源极选择线和第二源极选择线,多个连接图案137cp可包括第一连接图案和第二连接图案。第一连接图案可与第一垂直沟道130a接触,并且第二连接图案可与第二垂直沟道130b接触。如图9b所示,第一源极选择线可与第一垂直沟道130a交叠,并且第二源极选择线可与第二垂直沟道交叠。

[0136]

各条源极选择线143s可包括与第一填充绝缘层115交叠的端部eg[s]。

[0137]

图10a至图10f是示出在参照图9a和图9b描述的工艺之后继续的工艺的截面图。图10a至图10f中的每一个是沿着平行于源极选择线143s中的一个的轴线截取的截面图。

[0138]

参照图10a,可在第一填充绝缘层115上形成覆盖源极选择线143s的端部eg[s]的第二填充绝缘层151。

[0139]

随后,可形成第二绝缘层153。第二绝缘层153可覆盖源极选择线143s。第二绝缘层153可延伸以覆盖第二填充绝缘层151。

[0140]

随后,可形成源极沟道孔157。源极沟道孔157可穿透第二绝缘层153、源极选择线143s和第一绝缘层141,并且可暴露连接图案137cp。随后,可在源极选择线143s的通过各个

源极沟道孔157暴露的侧壁上形成栅极绝缘层155。

[0141]

在实施方式中,可通过氧化工艺形成栅极绝缘层155。在形成栅极绝缘层155的氧化工艺期间,可通过回蚀工艺去除形成在连接图案137cp的表面上的氧化物层。

[0142]

参照图10b,可分别以源极沟道160填充图10a所示的源极沟道孔157。源极沟道160可与连接图案137cp接触。

[0143]

形成源极沟道160的工艺可包括沿着图10a所示的各个源极沟道孔157的表面形成未掺杂半导体层161的工艺以及在未掺杂半导体层161上形成源极芯绝缘层163的工艺。在实施方式中,未掺杂半导体层161可包括未掺杂硅。未掺杂半导体层161可通过栅极绝缘层155与源极选择线143s间隔开。源极芯绝缘层163可填充图10a所示的各个源极沟道孔157的中央区域。

[0144]

随后,可蚀刻源极芯绝缘层163的一部分,从而限定第二凹陷区域165。未掺杂半导体层161的内壁的一部分可通过第二凹陷区域165暴露。

[0145]

参照图10c,可在第二绝缘层153上形成掺杂半导体层以如图10b所示填充第二凹陷区域165。在实施方式中,掺杂半导体层可包括n型杂质并且可包括掺杂硅层。

[0146]

随后,可蚀刻掺杂半导体层和第二绝缘层153。因此,掺杂半导体层可保留作为连接到源极沟道160的公共源极层167l。

[0147]

公共源极层167l可包括与第二填充绝缘层151交叠的端部eg[c]。公共源极层167l的端部eg[c]可朝着第二方向d2比源极选择线143s的端部eg[s]突出更远。

[0148]

公共源极层167l可包括线部167a和突出部167b。线部167a可平行于源极选择线143s。突出部167b可从线部167a朝着源极芯绝缘层163延伸。图10b所示的第二凹陷区域165可由与第二凹陷区域165对应的突出部167b填充。另外,与第二凹陷区域165对应的突出部167b可与未掺杂半导体层161的内壁接触。

[0149]

参照图10d,可在第二填充绝缘层151上形成第三填充绝缘层169。第三填充绝缘层169可覆盖公共源极层167l的端部eg[c]。

[0150]

随后,可形成第一接合绝缘层171。第一接合绝缘层171可覆盖公共源极层167l。第一接合绝缘层171可延伸以覆盖第三填充绝缘层169。

[0151]

参照图10e,可提供通过单独的工艺形成的外围电路结构200。如参照图6a和图6b描述的,外围电路结构200可包括具有多个晶体管210的基板201、覆盖基板201的绝缘结构231、掩埋在绝缘结构231中的多个互连结构以及覆盖多个互连结构和绝缘结构231的第二接合绝缘层233。

[0152]

晶体管210可通过形成在基板201中的隔离层203彼此绝缘。至少一个晶体管210可被包括在源极控制电路205中。连接到源极控制电路205的互连结构可包括下接触结构221、上接触结构225和互连线223。下接触结构221可连接到源极控制电路205的晶体管210。上接触结构225可能不与源极控制电路250的晶体管210交叠。互连线223可连接下接触结构221和上接触结构225。下接触结构225可包括依次层叠在源极控制电路205的晶体管210与互连线223之间的图案221a、221b和221c。源极控制电路205的晶体管210可通过下接触结构221连接到互连线223。互连线223可在第二方向d2上朝着上接触结构225延伸。上接触结构225可包括通孔插塞225a和焊盘图案225b。通孔插塞225a可与互连线223接触。焊盘图案225b可设置在通孔插塞225a上。

[0153]

牺牲基板101可与外围电路结构200交叠,使得第一接合绝缘层171面向外围电路结构200的第二接合绝缘层233。随后,可形成将第一接合绝缘层171和第二接合绝缘层233彼此接合的工艺。

[0154]

参照图10f,可去除图10e所示的牺牲基板101。因此,穿透初步栅极层叠结构110的存储器层123可暴露。随后,可将导电型杂质注入到各个垂直沟道130的端部中。在实施方式中,可将n型杂质注入到垂直沟道130的端部中。

[0155]

图11是示出在参照图10f描述的工艺之后继续的形成漏极选择线113d的工艺的截面图。图11是沿着与源极选择线143s交叉的轴线截取的截面图。

[0156]

参照图11,可形成漏极侧狭缝181。漏极侧狭缝181可穿透图10f所示的初步栅极层叠结构110的一部分,使得图10f所示的初步栅极层叠结构110的导电图案113当中的至少一个导电图案被隔离成漏极选择线113d。漏极选择线113d可分别与源极选择线143s交叠。因此,可限定栅极层叠结构110g。

[0157]

漏极侧狭缝181可延伸以穿透如图10f所示的初步栅极层叠结构110的导电图案113当中的至少一个导电图案。

[0158]

层叠在漏极选择线113d与源极选择线143s之间以彼此间隔开的导电图案未被漏极侧狭缝181穿透,而是可作为字线113w保留。漏极选择线113d可包括围绕第一垂直沟道130a的第一漏极选择线和围绕第二垂直沟道130b的第二漏极选择线。

[0159]

图12a至图12c是示出在执行参照图11描述的工艺之后继续的工艺的实施方式的截面图。图12a至图12c中的每一个是沿着平行于源极选择线143s中的一个的轴线截取的截面图。

[0160]

参照图12a,可形成第一上绝缘层183。第一上绝缘层183可覆盖栅极层叠结构110g和存储器层123。第一上绝缘层183可延伸以与外围电路结构200交叠,并且第一填充绝缘层115、第二填充绝缘层151和第三填充绝缘层169插置在第一上绝缘层183与外围电路结构200之间。

[0161]

随后,可形成垂直接触插塞185a和185b。垂直接触插塞185a和185b可穿透第一上绝缘层183、第一填充绝缘层115和第二填充绝缘层151。垂直接触插塞185a和185b可包括第一垂直接触插塞185a和第二垂直接触插塞185b。

[0162]

第一垂直接触插塞185a可朝着公共源极层167l延伸。第一垂直接触插塞185a可延伸以穿透设置在公共源极层167l与第二填充绝缘层151之间的第二绝缘层153。第一垂直接触插塞185a可与公共源极层167l接触。第二垂直接触插塞185b可朝着连接到源极控制电路205的焊盘图案225b延伸。第二垂直接触插塞185b可延伸以穿透设置在焊盘图案225b与第二填充绝缘层151之间的第三填充绝缘层169、第一接合绝缘层171和第二接合绝缘层233。第二垂直接触插塞185b可与焊盘图案225b接触。

[0163]

参照图12b,可在第一上绝缘层183上形成第二上绝缘层187。第二上绝缘层187可延伸以覆盖第一垂直接触插塞185a和第二垂直接触插塞185b。

[0164]

随后,可形成接触孔189a和189b。接触孔189a和189b可穿透第二上绝缘层187。接触孔189a和189b可包括第一接触孔189a和第二接触孔189b。

[0165]

第一接触孔189a可分别朝着垂直沟道130延伸。各个第一接触孔189a可延伸以穿透设置在垂直沟道层131与第二上绝缘层187之间的第一上绝缘层183和存储器层123。垂直

0110556的优先权,其完整公开通过引用并入本文。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。