1.本发明涉及半导体技术领域,尤其一种半导体器件及其制造方法。

背景技术:

2.半导体器件通常通过以下步骤来制造:在半导体衬底上方相继沉积绝缘或介电层、导电层和半导体材料层;以及使用光刻来图案化该多个材料层,以在其上形成电路组件和元件。

3.图1示出了一种现有半导体器件的制造方法的第一步骤状态示意图;图2示出了图1所示的制造方法的第二步骤状态示意图;图3示出了图1所示的制造方法的第三步骤状态示意图;该半导体器件的制造方法包括:步骤s1、提供基础结构,该基础结构包括衬底(图中未示出)以及形成于该衬底上的外延层100,该外延层100上设置有栅极200,栅极200侧壁上形成有阻挡层210,基础结构还包括覆盖在外延层100上并分别与栅极200、阻挡层210齐高的第一介电层300,覆盖形成于栅极200、第一介电层300以及阻挡层210上的掩蔽层400以及覆盖形成于掩蔽层400上的第二介电层500;步骤s2、在第二介电层500上涂布光刻胶600,如图1所示;步骤s3、利用光刻胶600通过光刻工艺,在基础结构的位于栅极200附近的位置上蚀刻形成与外延层100相接的蚀刻孔700,然后去掉光刻胶600,如图2所示;步骤s4、在蚀刻孔700中形成带有隔离层810的金属接触件800,如图3所示。隔离层810一般采用ti或tin。对于该制造方法,由于在蚀刻孔700的与外延层100相接的窗口的形成过程中,掩蔽层400也会同时进行腐蚀,所以,两者需要进行权衡。

4.图4示出了另一种现有半导体器件的制造方法的第一步骤状态示意图;图5示出了图4所示的制造方法的第二步骤状态示意图;图6示出了图4所示的制造方法的第三步骤状态示意图;图7示出了图4所示的制造方法的第四步骤状态示意图;图8示出了图4所示的制造方法的第五步骤状态示意图。该半导体器件的制造方法包括:步骤s1、提供基础结构,该基础结构包括衬底(图中未示出)以及形成于该衬底上的外延层100,该外延层100上设置有栅极200,栅极200侧壁上形成有阻挡层210,基础结构还包括覆盖在外延层100上并分别与栅极200、阻挡层210齐高的第一介电层300,覆盖形成于栅极200、第一介电层300以及阻挡层210上的掩蔽层400以及覆盖形成于掩蔽层400上的第二介电层500;步骤s2、在第二介电层500上涂布光刻胶600,如图4所示;步骤s3、利用光刻胶600通过光刻工艺,在基础结构的位于栅极200附近的位置上蚀刻形成与外延层100相接的蚀刻孔700,然后去掉光刻胶600,如图5所示;步骤s4、通过ald(原子层沉积)技术,在蚀刻孔700内壁沉积形成sin层900,如图6所示;步骤s5、通过蚀刻技术,将sin层900位于蚀刻孔700孔底的部分蚀刻掉,如图7所示;步骤s6、在蚀刻孔700中形成带有隔离层810的金属接触件800,如图8所示。隔离层810一般采用ti或tin。对于该制造方法,由于采用了ald(原子层沉积)技术,造成蚀刻孔700直径缩小,尤其是缩小了蚀刻孔700与外延层100相接的窗口;采用了两次蚀刻步骤,对外延层100造成了两次损伤。

技术实现要素:

5.本发明的目的是针对上述技术问题,提出一种半导体器件及其制造方法。

6.本发明解决其技术问题的技术方案是:

7.本发明提出了一种半导体器件的制造方法,包括以下步骤:

8.步骤s1、提供基础结构,该基础结构包括衬底以及形成于该衬底上的外延层,该外延层上设置有栅极,栅极侧壁上形成有阻挡层;基础结构还包括覆盖在外延层上并分别与栅极、阻挡层齐高的第一介电层,覆盖形成于栅极、第一介电层以及阻挡层上的掩蔽层以及覆盖形成于掩蔽层上的第二介电层;

9.步骤s2、在第二介电层上涂布光刻胶;

10.步骤s3、利用光刻胶通过光刻工艺,在基础结构的位于栅极附近的位置上蚀刻形成与外延层相接的蚀刻孔,然后去掉光刻胶;

11.步骤s4、采用旋转涂布材料填充蚀刻孔,从而在蚀刻孔中形成填充体;

12.步骤s5、对填充体进行蚀刻;并保留填充体的位于蚀刻孔底部的一部分,以此作为支撑体;

13.步骤s6、通过ald技术,在第二介电层顶面、支撑体顶面以及蚀刻孔的位于支撑体上方的内壁上沉积形成ald层;

14.步骤s7、通过蚀刻技术,将ald层的覆盖在第二介电层顶面、支撑体顶面上的部分蚀刻掉,同时剥除支撑体;

15.步骤s8、在蚀刻孔中填充形成金属接触件。

16.本发明上述的半导体器件的制造方法中,支撑体顶面的高度低于栅极顶面的高度。

17.本发明上述的半导体器件的制造方法中,阻挡层由以下材料制成:sin、sicn、sio2、sioc、siocn或它们的组合。

18.本发明上述的半导体器件的制造方法中,ald层为介电材料制成。

19.本发明上述的半导体器件的制造方法中,金属接触件由钨、铜、铝或它们的组合制成。

20.本发明还提出了一种半导体器件,包括基础结构,基础结构包括衬底以及形成于该衬底上的外延层,该外延层上设置有栅极,栅极侧壁上形成有阻挡层;基础结构还包括覆盖在外延层上并分别与栅极、阻挡层齐高的第一介电层,覆盖形成于栅极、第一介电层以及阻挡层上的掩蔽层以及覆盖形成于掩蔽层上的第二介电层;

21.基础结构的位于栅极附近的位置上蚀刻形成有与外延层相接的蚀刻孔;蚀刻孔内壁的靠近开口的部分上沉积形成有ald层;蚀刻孔中填充形成有金属接触件。

22.本发明上述的半导体器件中,ald层底面高度低于栅极顶面高度。

23.本发明上述的半导体器件中,阻挡层由以下材料制成:sin、sicn、sio2、sioc、siocn或它们的组合。

24.本发明上述的半导体器件中,ald层为介电材料制成。

25.本发明上述的半导体器件中,金属接触件由钨、铜、铝等或它们的组合制成。

26.本发明的半导体器件及其制造方法由于采用了ald(原子层沉积)技术,造成蚀刻孔700直径缩小,但蚀刻孔700与外延层100相接的窗口被扩大了;同时,虽然本发明优选实

施例的制造方法采用了三次蚀刻步骤,但对外延层100仅造成了一次损伤。本发明的半导体器件及其制造方法设计新颖,实用性强。

附图说明

27.下面将结合附图及实施例对本发明作进一步说明,附图中:

28.图1示出了一种现有半导体器件的制造方法的第一步骤状态示意图;

29.图2示出了图1所示的制造方法的第二步骤状态示意图;

30.图3示出了图1所示的制造方法的第三步骤状态示意图;

31.图4示出了另一种现有半导体器件的制造方法的第一步骤状态示意图;

32.图5示出了图4所示的制造方法的第二步骤状态示意图;

33.图6示出了图4所示的制造方法的第三步骤状态示意图;

34.图7示出了图4所示的制造方法的第四步骤状态示意图;

35.图8示出了图4所示的制造方法的第五步骤状态示意图;

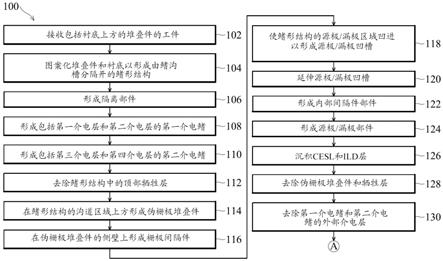

36.图9示出了本发明优选实施例的有半导体器件的制造方法的第一步骤状态示意图;

37.图10示出了图9所示的制造方法的第二步骤状态示意图;

38.图11示出了图9所示的制造方法的第三步骤状态示意图;

39.图12示出了图9所示的制造方法的第四步骤状态示意图;

40.图13示出了图9所示的制造方法的第五步骤状态示意图;

41.图14示出了图9所示的制造方法的第六步骤状态示意图;

42.图15示出了图9所示的制造方法的第七步骤状态示意图。

具体实施方式

43.为了使本发明的技术目的、技术方案以及技术效果更为清楚,以便于本领域技术人员理解和实施本发明,下面将结合附图及具体实施例对本发明做进一步详细的说明。

44.图9示出了本发明优选实施例的有半导体器件的制造方法的第一步骤状态示意图;图10示出了图9所示的制造方法的第二步骤状态示意图;图11示出了图9所示的制造方法的第三步骤状态示意图;图12示出了图9所示的制造方法的第四步骤状态示意图;图13示出了图9所示的制造方法的第五步骤状态示意图;图14示出了图9所示的制造方法的第六步骤状态示意图;图15示出了图9所示的制造方法的第七步骤状态示意图。具体地,本发明优选实施例的半导体器件的制造方法,包括以下步骤:

45.步骤s1、提供基础结构,该基础结构包括衬底(图中未示出)以及形成于该衬底上的外延层100,该外延层100上设置有栅极200,栅极200侧壁上形成有阻挡层210;基础结构还包括覆盖在外延层100上并分别与栅极200、阻挡层210齐高的第一介电层300,覆盖形成于栅极200、第一介电层300以及阻挡层210上的掩蔽层400以及覆盖形成于掩蔽层400上的第二介电层500;

46.在本步骤中,阻挡层210可以由以下材料制成:sin、sicn、sio2、sioc、siocn或它们的组合。

47.步骤s2、在第二介电层500上涂布光刻胶600,如图9所示;

48.步骤s3、利用光刻胶600通过光刻工艺,在基础结构的位于栅极200附近的位置上蚀刻形成与外延层100相接的蚀刻孔700,然后去掉光刻胶600,如图10所示;

49.步骤s4、采用旋转涂布材料填充蚀刻孔700,从而在蚀刻孔700中形成填充体710,如图11所示;

50.步骤s5、对填充体710进行蚀刻;并保留填充体710的位于蚀刻孔700底部的一部分,以此作为支撑体720,如图12所示;

51.支撑体720顶面的高度低于栅极200顶面的高度。

52.步骤s6、通过ald(原子层沉积)技术,在第二介电层500顶面、支撑体720顶面以及蚀刻孔700的位于支撑体720上方的内壁上沉积形成ald层910,如图13所示;

53.ald层910为介电材料制成,可为氮化物或氧化物。

54.步骤s7、通过蚀刻技术,将ald层910的覆盖在第二介电层500顶面、支撑体720顶面上的部分蚀刻掉,同时剥除支撑体720,如图14所示;

55.步骤s8、在蚀刻孔700中填充形成金属接触件800,如图15所示。对于该制造方法,由于采用了ald(原子层沉积)技术,造成蚀刻孔700直径缩小,但蚀刻孔700与外延层100相接的窗口被扩大了;同时,虽然本发明优选实施例的制造方法采用了三次蚀刻步骤,但对外延层100仅造成了一次损伤。

56.金属接触件800可以由钨、铜、铝等或它们的组合制成。

57.优选地,该金属接触件800的外表面带有隔离层810,该隔离层810一般采用ti或tin。

58.进一步地,如图15所示,本发明优选实施例还提出了一种半导体器件,包括基础结构,基础结构包括衬底(图中未示出)以及形成于该衬底上的外延层100,该外延层100上设置有栅极200,栅极200侧壁上形成有阻挡层210;基础结构还包括覆盖在外延层100上并分别与栅极200、阻挡层210齐高的第一介电层300,覆盖形成于栅极200、第一介电层300以及阻挡层210上的掩蔽层400以及覆盖形成于掩蔽层400上的第二介电层500;

59.基础结构的位于栅极200附近的位置上蚀刻形成有与外延层100相接的蚀刻孔700;蚀刻孔700内壁的靠近开口的部分上沉积形成有ald层910;蚀刻孔700中填充形成有金属接触件800。

60.由于采用了ald层910,造成蚀刻孔700直径缩小,但蚀刻孔700与外延层100相接的窗口被扩大了。

61.进一步地,在本实施例中,ald层910底面高度低于栅极200顶面高度。

62.进一步地,在本步骤中,阻挡层210可以由以下材料制成:sin、sicn、sio2、sioc、siocn或它们的组合。

63.ald层910为介电材料制成,可为氮化物或氧化物。

64.金属接触件800可以由钨、铜、铝等或它们的组合制成。优选地,该金属接触件800的外表面带有隔离层810,该隔离层810一般采用ti或tin。

65.应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本发明所附权利要求的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。