1.本公开涉及用于转换速率控制的电路和方法。

背景技术:

2.随着集成电路(ic)技术的发展,ic的速度提高。提高的速度与在ic中一个或多个电路处的较快切换on/off相关联。较快切换on/off可能会产生问题,例如sso(同步切换输出)噪声、相邻信号之间的串扰、emi(电磁干扰)等。在一些情况下,可以通过转换速率(slew rate)控制来解决这类潜在问题。

技术实现要素:

3.根据本公开的一个实施例,提供了一种用于转换速率控制的电路,包括:驱动器电路,所述驱动器电路被配置为生成具有第一边沿的驱动信号;输出电路,所述输出电路经由连接被耦合至所述驱动器电路,以在所述连接上接收所述驱动信号,所述输出电路被配置为响应于所述驱动信号而生成输出信号,所述输出信号的第二边沿具有与所述驱动信号在所述第一边沿上的电压的变化速率相对应的转换速率;以及补偿电路,所述补偿电路被耦合至所述连接,并且被配置为:在所述第一边沿的开始处被启用,以将所述驱动信号在所述第一边沿上的电压拉向阈值电压,以及响应于所述驱动信号在所述第一边沿上的电压达到所述阈值电压并且在所述驱动信号在所述第一边沿上的电压达到所述阈值电压之后被禁用。

4.根据本公开的另一实施例,提供了一种用于转换速率控制的电路,包括:第一连接,所述第一连接被配置为承载第一驱动信号;第一晶体管,所述第一晶体管是第一类型的,所述第一晶体管包括:栅极端子,所述栅极端子被耦合至所述第一连接以接收所述第一驱动信号,第一端子,所述第一端子被耦合至第一电源电压,以及第二端子;第二晶体管,所述第二晶体管是第二类型的,所述第二晶体管包括:栅极端子,所述栅极端子被耦合至所述第一连接以接收所述第一驱动信号,第一端子,所述第一端子被耦合至所述第一晶体管的第二端子,以及第二端子,所述第二端子被耦合至第二电源电压;第三晶体管,所述第三晶体管是所述第一类型的,所述第三晶体管包括:栅极端子,所述栅极端子被耦合至所述第一晶体管的第二端子和所述第二晶体管的第一端子,第一端子,所述第一端子被耦合至所述第一连接,以及第二端子,所述第二端子直接被耦合至所述第二电源电压、或通过晶体管被耦合至所述第二电源电压;以及第四晶体管,所述第四晶体管是所述第一类型的,所述第四晶体管包括:栅极端子,所述栅极端子被耦合至所述第一连接以接收所述第一驱动信号,第一端子,所述第一端子被耦合至所述第一电源电压,以及第二端子,所述第二端子被耦合至输出节点,输出信号将在所述输出节点被输出,其中,所述第一晶体管、所述第三晶体管和所述第四晶体管具有相同的第一阈值电压,所述第一晶体管、所述第三晶体管和所述第四晶体管被配置为在所述第一阈值电压处切换。

5.根据本公开的又一实施例,提供了一种操作电路的方法,所述方法包括:在驱动信

号的第一边沿的开始处,启用补偿电路,将所述驱动信号在所述第一边沿上的电压拉向阈值电压;响应于所述驱动信号在所述第一边沿上的电压达到所述阈值电压,禁用所述补偿电路,并且响应于所述驱动信号的所述第一边沿而使得输出电路开始输出信号的第二边沿,所述第二边沿具有与所述驱动信号在所述第一边沿上的电压的变化速率相对应的转换速率。

附图说明

6.在结合附图阅读下面的具体实施方式时,可以从下面的具体实施方式中最佳地理解本公开的各方面。应当注意,根据行业的标准做法,各种特征不是按比例绘制的。事实上,为了讨论的清楚起见,各种特征的尺寸可能被任意增大或减小。

7.图1a是根据一些实施例的用于转换速率控制的电路的示意性电路图。

8.图1b包括根据一些实施例的图1a的电路中的各种信号的时间图。

9.图2是根据一些实施例的用于转换速率控制的电路的示意性电路图。

10.图3是根据一些实施例的用于转换速率控制的电路的示意性电路图。

11.图4a是根据一些实施例的用于转换速率控制的电路的示意性电路图。

12.图4b包括根据一些实施例的图4a的电路中的各种信号的时间图。

13.图5是根据一些实施例的操作用于转换速率控制的电路的方法的流程图。

具体实施方式

14.下面的公开内容提供了用于实现所提供的主题的不同特征的许多不同的实施例或示例。下文描述了组件、值、操作、材料、布置等的具体示例以简化本公开。当然,这些仅仅是示例而不意图是限制性的。可以预期其他组件、值、操作、材料、布置等。例如,在下面的说明中,在第二特征上方或之上形成第一特征可以包括以直接接触的方式形成第一特征和第二特征的实施例,并且还可以包括可以在第一特征和第二特征之间形成附加特征,使得第一特征和第二特征可以不直接接触的实施例。此外,本公开可以在各种示例中重复参考标号和/或字母。该重复是为了简单和清楚的目的,并且本身并不表示所讨论的各个实施例和/或配置之间的关系。

15.如上所述,较快切换on/off可能会产生问题,例如sso噪声、相邻信号之间的串扰、emi等。在一些情况下,这些问题中的一个或多个可以通过减慢输入至输出电路(该输出电路生成输出信号)的驱动信号来缓解,使得输出信号的转换速率被可控地降低。输出信号的转换速率的受控降低被称为转换速率控制,并且实现转换速率控制的方法包括如上所述的减慢驱动信号。在一些情况下,驱动信号的减慢具有增加输出信号相对于驱动信号的传播延迟的不良后果。

16.为了减少传播延迟,在一些实施例中,在驱动信号的第一边沿的开始处,补偿电路被启用以加速输出电路中的晶体管的切换(例如,导通或关断),从而开始输出信号的相应第二边沿。在输出电路中的晶体管被切换(例如,导通或关断)并且输出信号的第二边沿开始上升或下降时,补偿电路被禁用。此后,通过驱动信号的第一边沿上的电压的变化速率来控制输出信号的第二边沿的转换速率。作为结果,在至少一个实施例中,与没有提供补偿电路的其他方法相比,分别减小了驱动信号和输出信号的相应第一边沿和第二边沿的开始

(或起始)之间的传播延迟。在至少一个实施例中,较短的传播延迟进一步确保了所设计的速度性能。在至少一个实施例中,因为补偿电路在输出信号的第二边沿开始上升或下降时被禁用,所以可以按设计实现对输出信号的转换速率控制,而不受补偿电路的影响。在一些实施例中,信号的边沿的开始是其中信号开始从信号的最大或最小电压电平下降或上升的边沿的起点。在一些实施例中,信号的最大或最小电压电平在给定时刻间段内。

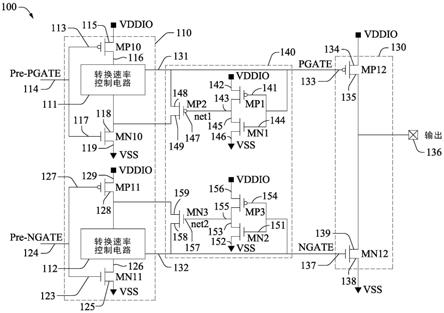

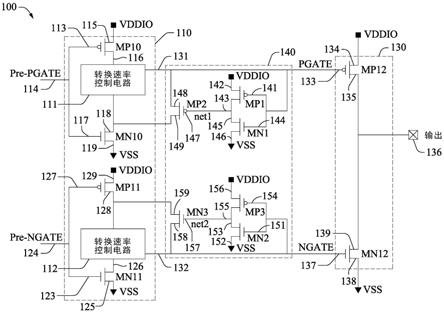

17.图1a是根据一些实施例的用于转换速率控制的电路100的示意性电路图。电路100包括驱动器电路110、输出电路130和补偿电路140。本文描述的示例电路包括一个或多个第一类型的晶体管(例如,p沟道金属氧化物半导体(pmos)晶体管)、以及一个或多个第二类型的晶体管(例如,n沟道金属氧化物半导体(nmos)晶体管)。在至少一个实施例中,nmos晶体管被称为第一类型的晶体管,而pmos晶体管被称为第二类型的晶体管。在附图中,pmos晶体管被标记为“mp”,并且nmos晶体管被标记为“mn”。其他类型的晶体管或开关器件落入各种实施例的范围内。

18.在图1a的示例配置中,驱动器电路110包括晶体管mp10、晶体管mn10、晶体管mp11、晶体管mn11、第一转换速率控制电路111和第二转换速率控制电路112。晶体管mp10包括:栅极端子113,被耦合至第一输入114以接收第一输入信号pre-pgate(以下称为“pre-pgate”);第一端子115,被耦合至第一电源电压vddio(以下称为“vddio”);以及第二端子116。晶体管mn10包括:栅极端子117,被耦合至第一输入114以接收pre-pgate;第一端子118;以及第二端子119,被耦合至第二电源电压vss(以下称为“vss”)。晶体管mn11包括:栅极端子123,被耦合至第二输入124以接收第二输入信号pre-ngate(以下称为“pre-ngate”);第一端子125,被耦合至vss;以及第二端子126。晶体管mp11包括:栅极端子127,被耦合至第二输入124以接收pre-ngate;第一端子128;以及第二端子129,被耦合至vddio。在至少一个实施例中,vddio是正电源电压,并且vss是接地电压。在至少一个实施例中,pre-pgate是pre-ngate的反相信号。

19.电路100还包括第一连接131和第二连接132。第一连接131将驱动器电路110耦合至输出电路130,并且将由驱动器电路110生成的第一驱动信号pgate(以下称为“pgate”)提供至输出电路130。第二连接132将驱动器电路110耦合至输出电路130,并且将由驱动器电路110生成的第二驱动信号ngate(以下称为“ngate”)提供至输出电路130。驱动器电路110被配置为从pre-pgate生成pgate。例如,当pre-pgate处于低电平(例如,vss)时,晶体管mp10导通,晶体管mn10关断,并且第一连接131上的pgate的电压经由导通的晶体管mp10向vddio上升。当pre-pgate处于高电平(例如,vddio)时,晶体管mp10关断,晶体管mn10导通,并且第一连接131上的pgate的电压经由导通的晶体管mn10向vss下降。类似地,驱动器电路110被配置为从pre-ngate生成ngate。例如,当pre-ngate处于低电平(例如,vss)时,晶体管mp11导通,晶体管mn11关断,并且第二连接132上的ngate的电压经由导通的晶体管mp11向vddio上升。当pre-ngate处于高电平(例如,vddio)时,晶体管mp11关断,晶体管mn11导通,并且第二连接132上的ngate的电压经由导通的晶体管mn11向vss下降。

20.第一转换速率控制电路111被耦合至第一连接131以控制pgate的电压随时间在vss和vddio之间变化的变化速率或速度。类似地,第二转换速率控制电路112被耦合至第二连接132以控制ngate的电压随时间在vss和vddio之间变化的变化速率或速度。针对图2-图3描述了第一转换速率控制电路111和第二转换速率控制电路112的示例电路。图1中的配置

(其中第一转换速率控制电路111分别耦合在晶体管mp10和晶体管mn10的端子116、118之间)是示例。在至少一个实施例中,例如,如针对图2所描述的,晶体管mp10和晶体管mn10的端子116、118分别直接彼此耦合。在至少一个实施例中,例如,如针对图3所描述的,晶体管mp10和晶体管mn10的端子116、118分别经由第一转换速率控制电路111的组件(例如,电阻器)彼此耦合。类似地,图1中的配置(其中第二转换速率控制电路112分别耦合在晶体管mn11和晶体管mp11的端子126、128之间)是示例。在至少一个实施例中,例如,如针对图2所描述的,晶体管mn11和晶体管mp11的端子126、128分别直接彼此耦合。在至少一个实施例中,例如,如针对图3所描述的,晶体管mn11和晶体管mp11的端子126、128分别经由第二转换速率控制电路122的组件(例如,电阻器)彼此耦合。用于将第一转换速率控制电路111和/或第二转换速率控制电路112耦合至驱动器电路110的其他部件的其他配置落入各种实施例的范围内。

21.在图1a的示例配置中,在至少一个实施例中,输出电路130包括晶体管mp12和晶体管mn12,它们被称为“后驱动器”。晶体管mp12包括:栅极端子133,被耦合至第一连接131以接收pgate;第一端子134,被耦合至vddio;以及第二端子135,被耦合至输出节点136,输出信号output(以下称为“信号output”)将在该输出节点136被输出。晶体管mn12包括:栅极端子137,被耦合至第二连接132以接收ngate;第一端子138,被耦合至vss;以及第二端子139,被耦合至输出节点136。输出电路130被配置为响应于pgate和ngate而生成信号output。此外,如本文所述,pgate的电压的变化速率对应于由输出电路130生成的信号output的边沿的转换速率,并且ngate的电压的变化速率对应于信号output的另一边沿的转换速率。

22.在图1a的示例配置中,补偿电路140包括耦合至第一连接131的晶体管mp1、晶体管mn1和晶体管mp2。晶体管mp1包括:栅极端子141,被耦合至第一连接131以接收pgate;第一端子142,被耦合至vddio;以及第二端子143。晶体管mn1包括:栅极端子144,被耦合至第一连接131以接收pgate;第一端子145,被耦合至晶体管mp1的第二端子143;以及第二端子146,被耦合至vss。晶体管mp2包括:栅极端子147,经由连接net1被耦合至晶体管mp1的第二端子143和晶体管mn1的第一端子145;第一端子148,被耦合至第一连接131;第二端子149,被耦合至晶体管mn10的端子118。晶体管mp2的第二端子149经由晶体管mn10被耦合至vss。在至少一个实施例中,晶体管mp2的第二端子149经由另一晶体管(未示出)被耦合至vss,或者例如针对图2所描述的直接耦合至vss。

23.补偿电路140还包括耦合至第二连接132的晶体管mn2、晶体管mp3和晶体管mn3。晶体管mn2包括:栅极端子151,被耦合至第二连接132以接收ngate;第二端子152,被耦合至vss端子;以及第二端子153。晶体管mp3包括:栅极端子154,被耦合至第二连接132以接收ngate;第一端子155,被耦合至晶体管mn2的第二端子153;以及第二端子156,被耦合至vddio。晶体管mn3包括:栅极端子157,经由连接net2被耦合至晶体管mn2的第二端子153和晶体管mp3的第一端子155;第一端子158,被耦合至第二连接132;以及第二端子159,被耦合至晶体管mp11的端子128。换句话说,晶体管mn3的第二端子159经由晶体管mp11被耦合至vddio;然而,这是示例。在至少一个实施例中,晶体管mn3的第二端子159经由另一晶体管(未示出)被耦合至vddio,或者例如针对图2所描述的直接耦合至vddio。

24.图1b包括根据一些实施例的图1a的电路100中的各种信号的时间图。具体地,在图1b中给出了第一连接131上的pgate、第二连接132上的ngate、和输出节点136处的信号

output的电压的时间图。

25.在时刻t0处,pgate的电压处于高电压电平,例如vddio。时刻t0是pgate的第一边沿161的开始。第一边沿161是下降边沿,pgate的电压沿着该下降边沿从vddio下降到vss。例如,如针对图1a所描述的,该下降边沿是通过以下方式生成的:当pre-pgate处于vddio时,使得晶体管mp10关断,晶体管mn10导通,并且第一连接131上的pgate的电压经由导通的晶体管mn10向vss下降。pgate的电压沿着第一边沿161从vddio下降至vss的下降速率或速度是由第一转换速率控制电路111控制的,响应于如针对图2所描述的转换速率控制信号而主动地控制,或者通过如针对图3所描述的第一转换速率控制电路111的电路配置而被动地控制,或两者兼而有之。提供补偿电路140以增加pgate在第一边沿161的初始阶段中的下降速率。

26.具体地,在补偿电路140中,pgate的第一边沿161的开始处的高电压电平经由第一连接131分别施加至晶体管mp1和晶体管mn1的栅极端子141、144,使得晶体管mp1关断,晶体管mn1导通。vss经由导通的晶体管mn1和连接net1施加至晶体管mp2的栅极端子147,使得晶体管mp2导通。作为结果,vss经由导通的晶体管mn1和导通的晶体管mp2施加到第一连接131,使得pgate的电压以增加的下降速率向vss下降。

27.在时刻t1处,向vss下降的pgate的电压达到阈值电压vddio-vt(以下称为“vddio-vt”),至少输出电路130和补偿电路140中的pmos晶体管在该vddio-vt处导通。在补偿电路140中,当pgate的电压达到vddio-vt并且进一步下降到vddio-vt以下时,晶体管mp1导通并且晶体管mn1关断。vddio经由导通的晶体管mp1和连接net1施加到晶体管mp2的栅极端子147,使得晶体管mp2关断。作为结果,vss通过至少关断的晶体管mp2从第一连接131被断开。对于在时刻t1之后的第一边沿161的剩余部分,补偿电路140不再影响pgate。如图1b中的示例时间图所示,pgate的电压在第一边沿161的初始阶段期间(在基于pgate启用补偿电路140以进行操作的时刻t0与时刻t1之间)的下降速率大于在第一边沿161的剩余部分期间(在基于pgate禁用补偿电路140的时刻t1之后)的下降速率。

28.在输出电路130中,当pgate的电压达到vddio-vt并且进一步下降到vddio-vt以下时,晶体管mp12导通。vddio经由导通的晶体管mp12施加到输出节点136,使得信号output的第二边沿162(其是上升边沿)在时刻t1处开始上升。响应于从驱动器电路110提供的pgate的第一边沿161,由输出电路130生成信号output的第二边沿162。信号output的第二边沿162以传播延迟td1跟随pgate的相应第一边沿161,该传播延迟td1是pgate的第一边沿161在时刻t0处的开始与信号output的第二边沿162在时刻t1处的开始之间的延迟。

29.第二边沿162的转换速率被确定为δv/δt,其中,δt是信号output从最大电压电平的一个预定百分比上升到最大电压电平的另一个预定百分比所花费的时间。在示例中,用于确定转换速率的预定百分比是10%和90%,即,δv是最大电压电平的80%。在另一示例中,用于确定转换速率的预定百分比是20%和80%,即,δv是最大电压电平的60%。用于确定转换速率的其他预定百分比落入各种实施例的范围内。在本文描述的示例中,用于确定转换速率的预定百分比是最大电压电平的10%和90%,并且δv是最大电压电平的80%。

30.在图1b的示例配置中,第二边沿162的转换速率被确定为δv/t

上升

,其中,t

上升

是从时刻t2(在时刻t2处,信号output在第二边沿162上的电压达到vddio的10%)到时刻t3(在时刻t3处,信号output在第二边沿162上的电压达到vddio的90%)的时间。t

上升

越长,转换速

率越小。第二边沿162的转换速率对应于pgate在第一边沿161上的电压的下降速率(如由第一转换速率控制电路111控制的)。例如,当pgate的电压沿着第一边沿161从时刻t1处的vddio-vt缓慢下降到vss时,信号output的电压也沿着第二边沿162缓慢上升,或者换句话说,第二边沿162具有较小转换速率。当pgate的电压沿着第一边沿161从vddio-vt迅速下降到vss时,信号output的电压也沿着第二边沿162迅速上升,或者换句话说,第二边沿162具有更大转换速率。

31.如本文中所述,补偿电路140在第一边沿161的开始处被启用以将pgate的电压拉向阈值电压vddio-vt。当补偿电路140影响pgate在第一边沿161上的电压的变化速率时,启用补偿电路140。例如,在初始阶段期间(在启用的补偿电路140增加了pgate的电压沿着第一边沿161朝向vddio-vt的下降速率的时刻t0与时刻t1之间),通过晶体管mp2的导通,来启用补偿电路140。作为结果,在至少一个实施例中,与没有补偿电路的其他方法相比,pgate的电压更快地达到vddio-vt,产生信号output的第二边沿162在时刻t1处的较早开始或起点,以及较短传播延迟td1。在至少一个实施例中,较短传播延迟td1确保了所设计的电路100的速度性能。相反,没有补偿电路的其他方法可能会遭受较低操作速度,这是因为由于过度的传播延迟,输出信号可能无法在有限的可用时间内实现全摆幅(full swing)。

32.此外,响应于pgate在第一边沿161上的电压达到阈值电压vddio-vt并且在pgate在第一边沿161上的电压达到阈值电压vddio-vt之后,禁用补偿电路140。当补偿电路140不再影响pgate在第一边沿161上的电压的变化速率时,禁用补偿电路140。例如,在第一边沿161在时刻t1之后的剩余部分期间,通过晶体管mp2的关断,来禁用补偿电路140。作为结果,在至少一个实施例中,信号output的第二边沿162的转换速率由第一转换速率控制电路111按设计进行控制,而不受补偿电路140的影响。

33.电路100基于ngate的操作类似于所描述的基于pgate的操作。具体地,在时刻t4处,ngate的电压处于低电压电平,例如vss。时刻t4是ngate的第三边沿163的开始。第三边沿163是上升边沿,ngate的电压沿着该上升边沿从vss上升到vddio。例如,如针对图1a所描述的,该上升边沿是通过以下方式生成的:当pre-ngate处于vss时,使得晶体管mn11关断,晶体管mp11导通,并且第二连接132上的ngate的电压经由导通的晶体管mp11向vddio上升。ngate的电压沿着第三边沿163从vss上升到vddio的上升速率或速度是由第二转换速率控制电路112控制的,响应于如针对图2所描述的转换速率控制信号而主动地控制,或者通过如针对图3所描述的第二转换速率控制电路112的电路配置而被动地控制,或两者兼而有之。提供补偿电路140以增加ngate在第三边沿163的初始阶段中的上升速率。

34.具体地,在补偿电路140中,ngate的第三边沿163的开始处的低电压电平经由第二连接132分别施加至晶体管mn2和晶体管mp3的栅极端子151、154,使得晶体管mn2关断,晶体管mp3导通。vddio经由导通的晶体管mp3和连接net2施加至晶体管mn3的栅极端子157,使得晶体管mn3导通。作为结果,vddio经由导通的晶体管mp3和导通的晶体管mn3施加到第二连接132,使得ngate的电压以增加的上升速率向vddio上升。

35.在时刻t5处,向vddio上升的ngate的电压达到阈值电压vt(以下称为“vt”),至少输出电路130和补偿电路140中的nmos晶体管在该vt处导通。在补偿电路140中,当ngate的电压达到vt并且进一步上升高于vt时,晶体管mn2导通并且晶体管mp3关断。vss经由导通的晶体管mn2和连接net2施加至晶体管mn3的栅极端子157,使得晶体管mn3关断。作为结果,

vddio通过至少关断的晶体管mn3从第二连接132被断开。对于在时刻t5之后的第三边沿163的剩余部分,补偿电路140不再影响ngate。如图1b中的示例时间图所示,ngate的电压在第三边沿163的初始阶段期间(在基于ngate启用补偿电路140以进行操作的时刻t4与时刻t5之间)的上升速率大于在第三边沿163的剩余部分期间(在基于ngate禁用补偿电路140的时刻t5之后)的上升速率。

36.在输出电路130中,当ngate的电压达到vt并且进一步上升高于vt时,晶体管mn12导通。vss经由导通的晶体管mn12施加到输出节点136,使得信号output的第四边沿164(其是下降边沿)在时刻t5处开始下降。响应于从驱动器电路110提供的ngate的第三边沿163,由输出电路130生成信号output的第四边沿164。信号output的第四边沿164以传播延迟td2跟随ngate的相应第三边沿163,该传播延迟td2是ngate的第三边沿163在时刻t4处的开始与信号output的第四边沿164在时刻t5处的开始之间的延迟。

37.在图1b的示例配置中,第四边沿164的转换速率被确定为δv/t

下降

,其中,t

下降

是从时刻t6(在时刻t6处,信号output在第四边沿164上的电压达到vddio的90%)到时刻t7(在时刻t7处,信号output在第四边沿164上的电压达到vddio的10%)的时间。t

下降

越长,转换速率越小。第四边沿164的转换速率对应于ngate在第三边沿163上的电压的上升速率(如由第二转换速率控制电路112控制的)。例如,当ngate的电压沿着第三边沿163从时刻t5处的vt缓慢上升到vddio时,信号output的电压也沿着第四边沿164缓慢下降,或者换句话说,第四边沿164具有较小转换速率。当ngate的电压沿着第三边沿163从vt迅速上升到vddio时,信号output的电压也沿着第四边沿164迅速下降,或者换句话说,第四边沿164具有更大转换速率。

38.在至少一个实施例中,针对基于pgate的操作所描述的一个或多个优点(例如,减小的传播延迟、确保的速度性能、和/或按设计的转换速率控制),对于基于ngate的操作也是可实现的。

39.在图1a-图1b的示例配置中,具体描述的电路和/或具体描述的各种晶体管的导通或关断是示例。其他配置落入各种实施例的范围内。在示例中,在一个或多个实施例中,补偿电路140的其他电路配置是可能的,只要补偿电路140在pgate或ngate的边沿的初始阶段被启用,并且然后在pgate或ngate达到相应阈值电压时并且在pgate或ngate达到相应阈值电压之后自动地被禁用。在另一示例中,虽然针对图1a-图1b描述了当输出电路130的晶体管(即,晶体管mp12或晶体管mn12)导通时,信号output的边沿开始上升或下降,但是在至少一个实施例中,可以配置电路100,使得当输出电路130中的晶体管关断时,信号output的边沿开始上升或下降。

40.在一些实施例中,电路100中的pmos晶体管都具有相同的阈值电压vddio-vt,和/或电路100中的nmos晶体管都具有相同的阈值电压vt。例如,电路100中的所有晶体管是i/o(输入/输出)器件,或者电路100中的所有晶体管是核心器件。核心器件是具有较薄栅极氧化物层的低压器件,并且被配置为足够大以处理较低电压摆幅信号,但通常不够大且不能处理较大电压摆幅信号。另一方面,i/o器件是具有较厚栅极氧化物层的高压器件,并且被配置为处理较大电压摆幅信号,并且通常比核心器件占用更大的管芯空间。

41.在一些实施例中,在电路100中包括具有不同阈值电压的pmos晶体管和/或具有不同阈值电压的nmos晶体管。例如,补偿电路140中的晶体管mp1和晶体管mp2在与输出电路

130中的晶体管mp12进行切换的阈值电压相比不同的阈值电压处进行切换。在至少一个实施例中,在晶体管mp12导通之前(即,在与pgate相对应的信号output开始上升之前),晶体管mp1导通并且晶体管mp2关断(即,在基于pgate的操作中禁用补偿电路140)。

42.在图1a的示例配置中,相同的正电源电压vddio被提供给电路100中的各种晶体管和/或电路。在一些实施例中,不同的正电源电压被提供给电路100中的各种晶体管和/或电路。例如,如针对图4a所描述的,vddio被提供给驱动器电路和补偿电路,而不同的电源电压vbus(以下称为“vbus”)被提供给输出电路。在至少一个实施例中,vbus高于vddio。

43.例如,如针对图1a所描述的,一些实施例被配置为以具有一对信号(例如,pgate/ngate和/或pre-pgate/pre-ngate)的双信号方案进行操作。至少一个实施例被配置为以单端信号方案进行操作,例如,如针对图4a所描述的。

44.一些实施例适用于使用转换速率控制的各种应用,例如,放大器、音频电子设备、标准opamp(运算放大器)电路等。

45.图2是根据一些实施例的用于转换速率控制的电路200的示意性电路图。电路200包括驱动器电路210、输出电路130和补偿电路240。

46.与驱动器电路110相比,驱动器电路210包括第一转换速率控制电路211和第二转换速率控制电路212,它们分别是第一转换速率控制电路111和第二转换速率控制电路112的示例电路。第一转换速率控制电路211包括晶体管mn13,该晶体管mn13具有:栅极端子213,被耦合以接收第一转换速率控制信号slb(以下称为“slb”);第一端子214,被耦合至第一连接131;以及第二端子215,被耦合至vss。第二转换速率控制电路212包括晶体管mp13,该晶体管mp13具有:栅极端子217,被耦合以接收第二转换速率控制信号sl(以下称为“sl”);第一端子218,被耦合至第二连接132;以及第二端子219,被耦合至vddio。

47.与补偿电路140相比,补偿电路240的不同之处在于,晶体管mp2的第二端子149直接耦合至vss,并且晶体管mn3的第二端子159直接耦合至vddio。

48.除了通过第一转换速率控制电路211和第二转换速率控制电路212实现的特定转换速率控制之外,电路200的操作类似于电路100的操作。第一转换速率控制电路211和第二转换速率控制电路212被配置为分别根据slb和sl主动地执行(或不执行)转换速率控制。在至少一个实施例中,slb是sl的反相信号。在至少一个实施例中,slb和sl分别从电路200外部的电路输入到第一转换速率控制电路211和第二转换速率控制电路212中,以用于在转换速率控制模式和非转换速率控制模式之间对电路200进行切换。

49.在转换速率控制模式中,sl处于逻辑高电平,slb处于低逻辑电平,并且晶体管mp13和晶体管mn13关断。pgate的电压经由导通的晶体管mn10从vddio-vt缓慢下降至vss,使得信号output以较小转换速率缓慢上升。类似地,ngate的电压经由导通的晶体管mp11从vt缓慢上升至vddio,使得信号output以较小转换速率缓慢下降。作为结果,执行转换速率控制。

50.在非转换速率控制模式中,sl处于逻辑低电平,slb处于高逻辑电平,并且晶体管mp13和晶体管mn13导通。pgate的电压经由导通的晶体管mn10和导通的晶体管mn13两者从vddio-vt迅速下降至vss,使得信号output以较大转换速率迅速上升。类似地,ngate的电压经由导通的晶体管mp11和导通的晶体管mp13两者从vt迅速上升至vddio,使得信号output以较大转换速率迅速下降。作为结果,不执行转换速率控制。

51.在至少一个实施例中,针对电路100描述的一个或多个优点和/或应用和/或修改也可以在电路200中实现。

52.图3是根据一些实施例的用于转换速率控制的电路300的示意性电路图。电路300包括驱动器电路310、输出电路130和补偿电路140。

53.与驱动器电路110相比,驱动器电路310包括第一转换速率控制电路311和第二转换速率控制电路312,它们分别是第一转换速率控制电路111和第二转换速率控制电路112的示例电路。第一转换速率控制电路311包括电容器c1和电阻器r1。电容器c1被耦合在第一连接131和输出节点136之间。电阻器r1的一端被耦合至晶体管mn10的第一端子118和晶体管mp2的第二端子149,而另一端被耦合至第一连接131和晶体管mp10的第二端子116。第二转换速率控制电路312包括电容器c2和电阻器r2。电容器c2被耦合在第二连接132和输出节点136之间。电阻器r2的一端被耦合至晶体管mp11的第一端子128和晶体管mn3的第二端子159,并且另一端被耦合至第二连接132和晶体管mn11的第二端子126。

54.除了通过第一转换速率控制电路311和第二转换速率控制电路312实现的特定转换速率控制之外,电路300的操作类似于电路100的操作。第一转换速率控制电路311和第二转换速率控制电路312被配置为通过各自的相应电路配置来被动地执行转换速率控制。

55.在pgate从vddio到vss的下降边沿上,电容器c1(该电容器c1在pgate的先前上升边沿中进行充电)通过电阻器r1和导通的晶体管mn10放电至vss。由于电容器c1通过电阻器r1放电,pgate的电压在下降边沿缓慢下降,产生信号output的相应缓慢上升边沿以及降低的转换速率。类似地,在ngate从vddio到vss的下降边沿上,电容器c2(该电容器c2在ngate的先前上升边沿中进行充电)通过导通的晶体管mn11放电至vss。电容器c2的放电不如电容器c1的放电慢,因为电阻器r2不参与电容器c2的放电。作为结果,ngate的电压下降到vss的速度比pgate的电压下降到vss的速度快,但是仍然比不包括转换速率控制电路的情况慢。

56.在ngate从vss到vddio的上升边沿上,电容器c2通过导通的晶体管mp11和电阻r2从vddio进行充电。由于通过电阻器r2对电容器c2进行充电,ngate的电压在上升边沿缓慢上升,产生信号output的相应缓慢下降边沿以及降低的转换速率。类似地,在pgate从vss到vddio的上升边沿上,电容器c1通过导通的晶体管mp10从vddio进行充电。电容器c1的充电不比电容器c2的充电慢,因为电阻器r1不参与电容器c1的充电。作为结果,pgate的电压上升到vddio的速度比ngate的电压上升到vddio的速度快,但是仍然比不包括转换速率控制电路的情况慢。

57.在至少一个实施例中,针对电路100描述的一个或多个优点和/或应用和/或修改也可以在电路300中实现。

58.图4a是根据一些实施例的用于转换速率控制的电路400的示意性电路图。电路400包括驱动器电路410、输出电路430和补偿电路440。与被配置为以双信号方案进行操作的电路300相比,电路400被配置为以单端信号方案进行操作,并且包括电路300的一半。具体地,驱动器电路410包括驱动器电路310与ngate相关联的一半。输出电路430包括输出电路130与ngate相关联的一半。补偿电路440包括补偿电路140与ngate相关联的一半。在电路400中,输出节点136经由外部电阻器externalr被耦合至电源电压vbus。在至少一个实施例中,电路400是经由输出节点136耦合至由电源电压vbus供电的外部电路的i/o电路。电阻器externalr表示电路400的负载并且对应于外部电路的等效电阻器。

59.图4b包括根据一些实施例的图4a的电路400中的各种信号的时间图。与电路100、电路200和电路300(其中针对信号output的上升边沿和下降边沿两者来实现相应补偿电路140或240的转换速率控制和操作)相比,在电路400中,针对信号output的一个边沿来实现补偿电路440的转换速率控制和操作。

60.具体地,如图4b中的示例时间图所示,并且类似于针对图1b所描述的基于ngate的操作,补偿电路440在与ngate的上升边沿163的开始相对应的时刻t4处被启用,以将ngate的电压拉向阈值电压vt,并且加速输出电路430的晶体管mn12的导通以及信号output的相应下降边沿164的相关联开始。响应于ngate在上升边沿163上的电压达到阈值电压vt,禁用补偿电路340,并且信号output的电压在时刻t5处开始上升。此后,如针对图3所描述的,信号output的下降边沿164的转换速率(与图4b中的t

下降

成反比)由转换速率控制电路312控制,而不受已经被禁用的补偿电路440的影响。

61.在至少一个实施例中,针对电路100描述的一个或多个优点和/或应用和/或修改也可以在电路400中实现。

62.图5是根据一些实施例的操作用于转换速率控制的电路的方法500的流程图。在至少一个实施例中,方法500由本文所描述的电路100、电路200、电路300和电路400中的一个或多个执行。

63.在操作515处,补偿电路在驱动信号的第一边沿的开始处被启用,以将驱动信号的第一边沿上的电压拉向阈值电压。例如,补偿电路140在时刻t0(即,驱动信号pgate的第一边沿161的开始)处被启用,以将驱动信号pgate的第一边沿161上的电压拉向阈值电压vddio-vt,如针对图1a-图1b所描述的。对于另一示例,补偿电路440在时刻t0(即,驱动信号ngate的边沿163的开始)处被启用,以将驱动信号ngate的边沿163上的电压拉向阈值电压vt,如针对图4a-图4b所描述的。

64.在操作525处,响应于驱动信号的第一边沿上的电压达到阈值电压,禁用补偿电路。例如,在驱动信号pgate的第一边沿161上的电压达到vddio-vt的时刻t1处,禁用补偿电路140,如针对图1a-图1b所描述的。对于另一示例,在驱动信号ngate的边沿163上的电压达到vt的时刻t5处,禁用补偿电路440,如针对图4a-图4b所描述的。

65.在操作535处,输出电路开始输出信号的第二边沿,并且第二边沿具有与驱动信号的第一边沿上的电压的变化速率相对应的转换速率。例如,当补偿电路140被禁用时,输出电路130开始信号output的第二边沿162,如针对图1a-图1b所描述的。此外,第二边沿162具有与驱动信号pgate的第一边沿161上的电压的变化速率相对应的转换速率(例如,与图1b中的t

上升

成反比),如针对图1a-图1b、图2和图3所描述的。对于另一示例,当补偿电路440被禁用时,输出电路430开始信号output的边沿164,如针对图4a-图4b所描述的。此外,边沿164具有与驱动信号ngate的边沿163上的电压的变化速率相对应的转换速率(例如,与图1b或图4b中的tfall成反比),如针对图3和图4a-图4b所描述的。

66.所描述的方法和算法包括示例操作,但是不一定需要以所示顺序执行它们。根据本公开的实施例的精神和范围,操作可以被适当地增加、替换、改变顺序和/或消除。对不同特征和/或不同实施例进行组合的实施例落入本公开的范围内,并且对于本领域的普通技术人员在回顾本公开之后将是显而易见的。

67.在一些实施例中,一种电路包括:驱动器电路,该驱动器电路被配置为生成具有第

一边沿的驱动信号;输出电路,该输出电路经由连接被耦合至驱动器电路以在连接上接收驱动信号;以及补偿电路,该补偿电路被耦合至连接。输出电路被配置为响应于驱动信号而生成输出信号。输出信号的第二边沿具有与驱动信号在第一边沿上的电压的变化速率相对应的转换速率。补偿电路被配置为在第一边沿的开始处被启用,以将驱动信号在第一边沿上的电压拉向阈值电压。补偿电路还被配置为响应于驱动信号在第一边沿上的电压达到阈值电压并且在驱动信号在第一边沿上的电压达到阈值电压之后被禁用。

68.在一些实施例中,一种电路,包括:第一连接,该第一连接被配置为承载第一驱动信号;第一类型的第一晶体管;第二类型的第二晶体管;第一类型的第三晶体管;以及第一类型的第四晶体管。第一晶体管包括:栅极端子,被耦合至第一连接以接收第一驱动信号;第一端子,被耦合至第一电源电压;以及第二端子。第二晶体管包括:栅极端子,被耦合至第一连接以接收第一驱动信号;第一端子,被耦合至第一晶体管的第二端子;以及第二端子,被耦合至第二电源电压。第三晶体管包括:栅极端子,被耦合至第一晶体管的第二端子和第二晶体管的第一端子;第一端子,被耦合至第一连接;以及第二端子,直接被耦合至第二电源电压、或经由第二晶体管被耦合至第二电源电压。第四晶体管包括:栅极端子,被耦合至第一连接以接收第一驱动信号;第一端子,被耦合至第一电源电压;以及第二端子,被耦合至输出节点,输出信号将在输出节点被输出。第一晶体管、第三晶体管和第四晶体管具有相同的第一阈值电压,第一晶体管、第三晶体管和第四晶体管被配置为在第一阈值电压处进行切换。

69.在根据一些实施例的一种操作电路的方法中,在驱动信号的第一边沿的开始处,启用补偿电路,并且将驱动信号在第一边沿上的电压拉向阈值电压。响应于驱动信号在第一边沿上的电压达到阈值电压,禁用补偿电路,并且响应于驱动信号的第一边沿而使得输出电路开始输出信号的第二边沿。第二边沿具有与驱动信号在第一边沿上的电压的变化速率相对应的转换速率。

70.以上概述了若干实施例的特征,使得本领域技术人员可以更好地理解本公开的各方面。本领域技术人员应当理解,他们可以容易地使用本公开作为设计或修改其他工艺和结构以实现本文介绍的实施例或示例的相同目的和/或实现本文介绍的实施例或示例的相同优点的基础。本领域技术人员还应该认识到,这样的等同配置不脱离本公开的精神和范围,并且他们可以在不脱离本公开的精神和范围的情况下在本文中进行各种改变、替换和变更。

71.示例1.一种用于转换速率控制的电路,包括:驱动器电路,所述驱动器电路被配置为生成具有第一边沿的驱动信号;输出电路,所述输出电路经由连接被耦合至所述驱动器电路,以在所述连接上接收所述驱动信号,所述输出电路被配置为响应于所述驱动信号而生成输出信号,所述输出信号的第二边沿具有与所述驱动信号在所述第一边沿上的电压的变化速率相对应的转换速率;以及补偿电路,所述补偿电路被耦合至所述连接,并且被配置为:在所述第一边沿的开始处被启用,以将所述驱动信号在所述第一边沿上的电压拉向阈值电压,以及响应于所述驱动信号在所述第一边沿上的电压达到所述阈值电压并且在所述驱动信号在所述第一边沿上的电压达到所述阈值电压之后被禁用。

72.示例2.根据示例1所述的电路,其中:所述输出电路包括晶体管,所述晶体管被配置为响应于所述驱动信号在所述第一边沿上的电压达到所述阈值电压而切换,以开始所述

输出信号的所述第二边沿。

73.示例3.根据示例1所述的电路,其中:所述第一边沿是所述驱动信号的下降边沿,并且所述补偿电路配置为:在所述下降边沿的开始处被启用,以将所述驱动信号的电压下拉向所述阈值电压,以及响应于所述驱动信号在所述下降边沿上的电压达到并且低于所述阈值电压而被禁用。

74.示例4.根据示例3所述的电路,其中:所述输出电路包括晶体管,所述晶体管被配置为响应于所述驱动信号在所述下降边沿上的电压达到所述阈值电压而切换,以开始所述输出信号的所述第二边沿,所述第二边沿是上升边沿。

75.示例5.根据示例1所述的电路,其中:所述第一边沿是所述驱动信号的上升边沿,并且所述补偿电路配置为:在所述上升边沿的开始处被启用,以将所述驱动信号的电压上拉向所述阈值电压,以及响应于所述驱动信号在所述上升边沿上的电压达到并且高于所述阈值电压而被禁用。

76.示例6.根据示例5所述的电路,其中:所述输出电路包括晶体管,所述晶体管被配置为响应于所述驱动信号在所述上升边沿上的电压达到所述阈值电压而切换,以开始所述输出信号的所述第二边沿,所述第二边沿是下降边沿。

77.示例7.根据示例1所述的电路,其中,所述补偿电路包括:第一晶体管,所述第一晶体管是第一类型的,所述第一晶体管包括:栅极端子,所述栅极端子被耦合至所述连接以接收所述驱动信号,第一端子,所述第一端子被耦合至第一电源电压,以及第二端子;第二晶体管,所述第二晶体管是第二类型的,所述第二晶体管包括:栅极端子,所述栅极端子被耦合至所述连接以接收所述驱动信号,第一端子,所述第一端子被耦合至所述第一晶体管的第二端子,以及第二端子,所述第二端子被耦合至第二电源电压;以及第三晶体管,所述第三晶体管是所述第一类型的,所述第三晶体管包括:栅极端子,所述栅极端子被耦合至所述第一晶体管的第二端子和所述第二晶体管的第一端子,第一端子,所述第一端子被耦合至所述连接,以及第二端子,所述第二端子直接被耦合至所述第二电源电压、或通过晶体管被耦合至所述第二电源电压。

78.示例8.根据示例7所述的电路,其中:在所述驱动信号的所述第一边沿的开始处,所述第一晶体管被配置为关断,所述第二晶体管被配置为导通,以向所述第三晶体管的栅极端子提供所述第二电源电压,所述第三晶体管被配置为导通,以将所述驱动信号在所述第一边沿上的电压拉向所述第二电源电压和所述阈值电压,所述第三晶体管导通对应于所述补偿电路被启用,并且响应于所述驱动信号在所述第一边沿上的电压达到所述阈值电压并且在所述驱动信号在所述第一边沿上的电压达到所述阈值电压之后,所述第一晶体管被配置为导通,以向所述第三晶体管的栅极端子提供所述第一电源电压,所述第二晶体管被配置为关断,以及所述第三晶体管被配置为关断,所述第三晶体管关断对应于所述补偿电路被禁用。

79.示例9.根据示例7所述的电路,其中:所述输出电路包括第四晶体管,所述第四晶体管是所述第一类型的,所述第四晶体管包括:栅极端子,所述栅极端子被耦合至所述连接以接收所述驱动信号,第一端子,所述第一端子被耦合至所述第一电源电压,以及第二端子,所述第二端子被耦合至输出节点,所述输出信号将在所述输出节点被输出,所述第四晶体管被配置为:在所述第一边沿的开始处关断,以及响应于所述驱动信号在所述第一边沿

上的电压达到所述阈值电压并且在所述驱动信号在所述第一边沿上的电压达到所述阈值电压之后导通,以在所述输出节点处开始所述输出信号的所述第二边沿。

80.示例10.根据示例9所述的电路,其中,所述驱动器电路包括:第五晶体管,所述第五晶体管是所述第一类型的,所述第五晶体管包括:栅极端子,所述栅极端子被耦合至输入以接收输入信号,第一端子,所述第一端子被耦合至所述第一电源电压,以及第二端子,所述第二端子被耦合至所述连接;第六晶体管,所述第六晶体管是所述第二类型的,所述第六晶体管包括:栅极端子,所述栅极端子被耦合至所述输入以接收所述输入信号,第一端子,所述第一端子被耦合至所述连接,以及第二端子,所述第二端子被耦合至所述第二电源电压。

81.示例11.一种用于转换速率控制的电路,包括:第一连接,所述第一连接被配置为承载第一驱动信号;第一晶体管,所述第一晶体管是第一类型的,所述第一晶体管包括:栅极端子,所述栅极端子被耦合至所述第一连接以接收所述第一驱动信号,第一端子,所述第一端子被耦合至第一电源电压,以及第二端子;第二晶体管,所述第二晶体管是第二类型的,所述第二晶体管包括:栅极端子,所述栅极端子被耦合至所述第一连接以接收所述第一驱动信号,第一端子,所述第一端子被耦合至所述第一晶体管的第二端子,以及第二端子,所述第二端子被耦合至第二电源电压;第三晶体管,所述第三晶体管是所述第一类型的,所述第三晶体管包括:栅极端子,所述栅极端子被耦合至所述第一晶体管的第二端子和所述第二晶体管的第一端子,第一端子,所述第一端子被耦合至所述第一连接,以及第二端子,所述第二端子直接被耦合至所述第二电源电压、或通过晶体管被耦合至所述第二电源电压;以及第四晶体管,所述第四晶体管是所述第一类型的,所述第四晶体管包括:栅极端子,所述栅极端子被耦合至所述第一连接以接收所述第一驱动信号,第一端子,所述第一端子被耦合至所述第一电源电压,以及第二端子,所述第二端子被耦合至输出节点,输出信号将在所述输出节点被输出,其中,所述第一晶体管、所述第三晶体管和所述第四晶体管具有相同的第一阈值电压,所述第一晶体管、所述第三晶体管和所述第四晶体管被配置为在所述第一阈值电压处切换。

82.示例12.根据示例11所述的电路,还包括:第五晶体管,所述第五晶体管是所述第一类型的,所述第五晶体管包括:栅极端子,所述栅极端子被耦合至第一输入以接收第一输入信号,第一端子,所述第一端子被耦合至所述第一电源电压,以及第二端子,所述第二端子被耦合至所述第一连接;以及第六晶体管,所述第六晶体管是所述第二类型的,所述第六晶体管包括:栅极端子,所述栅极端子被耦合至所述第一输入以接收所述第一输入信号,第一端子,所述第一端子被耦合至所述第一连接;以及第二端子,所述第二端子被耦合至所述第二电源电压。

83.示例13.根据示例12所述的电路,还包括:第七晶体管,所述第七晶体管是所述第二类型的,所述第七晶体管包括:栅极端子,所述栅极端子被耦合以接收转换速率控制信号,第一端子,所述第一端子被耦合至所述第一连接;以及第二端子,所述第二端子被耦合至所述第二电源电压。

84.示例14.根据示例12所述的电路,还包括:第一电阻器,所述第六晶体管的第一端子经由所述第一电阻器被耦合至所述第一连接;以及第一电容器,所述第一电容器被耦合在所述第一连接和所述输出节点之间。

85.示例15.根据示例12所述的电路,还包括:第二连接,所述第二连接被配置为承载第二驱动信号;第七晶体管,所述第七晶体管是所述第二类型的,所述第七晶体管包括:栅极端子,所述栅极端子被耦合至所述第二连接以接收所述第二驱动信号,第一端子,所述第一端子被耦合至所述第二电源电压,以及第二端子;第八晶体管,所述第八晶体管是所述第一类型的,所述第八晶体管包括:栅极端子,所述栅极端子被耦合至所述第二连接以接收所述第二驱动信号,第一端子,所述第一端子被耦合至所述第七晶体管的第二端子,以及第二端子,所述第二端子被耦合至所述第一电源电压;第九晶体管,所述第九晶体管是所述第二类型的,所述第九晶体管包括:栅极端子,所述栅极端子被耦合至所述第七晶体管的第二端子和所述第八晶体管的第一端子,第一端子,所述第一端子被耦合至所述第二连接,以及第二端子,所述第二端子直接被耦合至所述第一电源电压、或通过晶体管被耦合至所述第一电源电压;以及第十晶体管,所述第十晶体管是所述第二类型的,所述第十晶体管包括:栅极端子,所述栅极端子被耦合至所述第二连接以接收所述第二驱动信号,第一端子,所述第一端子被耦合至所述第二电源电压,以及第二端子,所述第二端子被耦合至所述输出节点,其中,所述第七晶体管、所述第九晶体管和所述第十晶体管具有相同的第二阈值电压,所述第七晶体管、所述第九晶体管和所述第十晶体管被配置为在所述第二阈值电压处切换。

86.示例16.根据示例15所述的电路,还包括:第十一晶体管,所述第十一晶体管是所述第二类型的,所述第十一晶体管包括:栅极端子,所述栅极端子被耦合至第二输入以接收第二输入信号,第一端子,所述第一端子被耦合至所述第二电源电压,以及第二端子,所述第二端子被耦合至所述第二连接;以及第十二晶体管,所述第十二晶体管是所述第一类型的,所述第十二晶体管包括:栅极端子,所述栅极端子被耦合至所述第二输入以接收所述第二输入信号,第一端子,所述第一端子被耦合至所述第二连接;以及第二端子,所述第二端子被耦合至所述第一电源电压。

87.示例17.一种操作电路的方法,所述方法包括:在驱动信号的第一边沿的开始处,启用补偿电路,将所述驱动信号在所述第一边沿上的电压拉向阈值电压;响应于所述驱动信号在所述第一边沿上的电压达到所述阈值电压,禁用所述补偿电路,并且响应于所述驱动信号的所述第一边沿而使得输出电路开始输出信号的第二边沿,所述第二边沿具有与所述驱动信号在所述第一边沿上的电压的变化速率相对应的转换速率。

88.示例18.根据示例17所述的方法,其中:所述补偿电路在被启用时以增加的变化速率将所述驱动信号在所述第一边沿上的电压拉向所述阈值电压,所述增加的变化速率大于在所述补偿电路在被禁用时所述驱动信号的所述第一边沿上的电压的变化速率。

89.示例19.根据示例17所述的方法,其中:所述驱动信号的所述第一边沿是下降边沿,所述补偿电路在被启用时将所述驱动信号在所述第一边沿上的电压下拉向所述阈值电压,并且所述输出信号的所述第二边沿是上升边沿,所述上升边沿在所述驱动信号在所述第一边沿上的电压达到所述阈值电压并且禁用所述补偿电路时开始上升。

90.示例20.根据示例17所述的方法,其中:所述驱动信号的所述第一边沿是上升边沿,所述补偿电路在被启用时将所述驱动信号在所述第一边沿上的电压上拉向所述阈值电压,并且所述输出信号的所述第二边沿是下降边沿,所述下降边沿在所述驱动信号在所述第一边沿上的电压达到所述阈值电压并且禁用所述补偿电路时开始下降。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。