1.本公开涉及一种用于图像传感器的模数转换器,该模数转换器可以用于读出图像传感器的像素阵列的电压。本公开还涉及一种图像传感器,该图像传感器包括模数转换器以读出该图像传感器的像素阵列的电压。

背景技术:

2.图像传感器通常使用模数转换器(adc)来读出图像传感器的像素阵列的电压。用于图像传感器应用的adc可实现为组并行单斜率adc。在该特定类型的adc中,比较器电路将像素组的像素(例如像素列的像素)的组电压电平(例如列电压电平)与周期性斜坡电压比较。使用n位计数器电路跟踪斜坡起始与比较器电路的输出切换之间的时间。计数器电路的输出信号(例如输出位)用作列电压的数字表征。该值通常在转换之后被存储。

3.期望提供一种用于图像传感器的模数转换器,该模数转换器能够高速地将模拟信号转换成数字信号,并同时最小化所需的功率和面积消耗。此外,需要提供一种使用模数转换器以高速地将像素阵列的读出电压转换成数字值,并同时提供最小化功率和面积消耗的图像传感器。

技术实现要素:

4.在权利要求1中说明了一种用于图像传感器的模数转换器的实施例,该模数转换器允许以增加的速度将模拟信号转换成数字信号,并具有低功耗和小的面积消耗。

5.根据该用于图像传感器的模数转换器的实施例,该模数转换器包括计数器电路,该计数器电路具有用于施加时钟信号的计数器控制连接和用于响应于计数器电路的计数器状态生成相应计数器位的多个计数器输出连接。该模数转换器还包括存储电路,该存储电路包括多个存储单元。存储单元中相应之一连接到计数器输出连接中的相应之一,用于响应于相应计数器位存储相应存储状态。该模数转换器还包括用于响应于输入信号与参考信号的比较来生成比较信号的电平的比较器电路,以及用于施加比较信号和时钟信号并生成用于控制在相应存储单元中相应存储状态的存储的写控制信号的同步电路。

6.计数器电路配置为当时钟信号的周期的第一边沿被施加到计数器电路的计数器控制连接时,改变计数器状态。同步电路配置为当在时钟信号的周期的第一边沿之后的时钟信号的周期的第二边沿被施加到同步电路时,响应于比较信号的电平来生成写控制信号。

7.所述模数转换器仅需要小的硅面积并具有低功耗。这转而提高电路的速度,因为电源下降能够做的小。更小的面积和功耗以及对于模数信号转换的高速尤其对于具有低像素间距和大量像素并由此大量平行性的图像传感器是一个优点。此外,该模数转换器允许很好地扩展到较小的技术节点,在所述技术节点中,供电电压电平降低而晶体管失配增大。

8.计数器电路可以实现为响应于施加到计数器控制连接的时钟信号,在计数器输出连接处生成相应计数器位。计数器电路可以实现为在时钟信号的每个上升沿或下降沿,在

计数器输出连接中的每个处生成新的计数器位。同步电路也受时钟信号控制。然而,与计数器电路相比,在同步输出连接处的写控制信号的输出由同步电路同步化到时钟信号的相对的(上升或下降)沿。然后,写控制信号用于将计数器电路产生的计数器位锁存到存储电路的存储单元中。添加同步电路允许为计数器电路提供时间以在时钟信号的时钟周期的一半时钟周期内稳定,允许使用非同步计数器单元。这还允许通过在时钟信号的不同时钟阶段添加更多的计数器来扩展架构。

9.根据所述模数转换器的一个实施例,该转换器包括用于生成相对于写控制信号被延迟的延迟写控制信号的锁存电路。锁存电路连接到同步电路的同步输出连接,以使得写控制信号施加到存储单元的第一部分,并且延迟的写控制信号施加到存储单元的第二部分。存储单元的第一部分可以连接到计数器电路以存储低有效位(lsb),以使得存储单元的第一部分的存储单元配置为lsb存储单元。存储单元的第二部分连接到计数器电路的计数器输出连接以存储最高有效位(msb),以使得存储电路的第二部分的存储单元配置为msb存储单元。

10.锁存电路使得当msb计数器位在时钟信号的上升沿触发时,用于存储最高有效位的控制信号能够被延迟。这为计数器电路提供较多的时间以使得msb计数器位稳定,这使得纹波计数器单元能够用于生成计数器电路中的所有计数器位,而不是仅使用纹波计数器单元来生成低有效计数器位。

11.所述模数转换器的速度和功耗能够通过同步电路、锁存电路和存储电路的具体实施例被进一步优化。具体地,存储单元可以实现为使得仅单端输入需在分布在存储电路的存储单元上。此外,存储单元可以配置为使得仅需单端写控制信号,由此避免偏移问题。而且,通过针对同步电路和锁存电路两者使用真单相时钟(tspc)单元,能够最小化时钟信号上的负载和用于控制锁存电路的控制信号。

12.在权利要求10中说明了一种使用模数转换器来高速地将像素阵列的读出电压转换成数字值并同时最小化功率和面积消耗的图像传感器的实施例。

13.根据一个实施例,该图像传感器包括像素阵列,该像素阵列包括至少两个像素组,每个像素组包括与该像素组的各自相关联的组总线相连接的多个像素。该图像传感器还包括根据权利要求1至9之一所述实现的模数转换器。该模数转换器配置为读出像素阵列的像素的电压值。

14.该模数转换器可配置为组并行模数转换器,例如列并行模数转换器,以使得对于在具有k

‑

分布的计数器子集的结构中具有n个像素组/列的像素阵列的设计,组/列adc结构能够被拆分,每个子集驱动m个像素列(n=k

×

m)。特别地,adc的具有最高功耗的元件,即用于生成低有效计数器位的计数器元件,在m组/列像素之间共享,降低了功耗。另一方面,在共享计数器电路中,计数器电路的每次计数时,列内没有数字切换。电路的布局能够在面积和功率方面得到优化,这是因为其不受组/列间距限制,这允许计数器位更有效且更低功耗的内部路由。此外,该模数转换器的电路配置不依赖于低压信号和感测放大器,以在多个列之间共享计数器值。

15.该模数转换器预期是可扩展的,在技术方面,在缩小时,由于较低的电源电压和较小技术节点中较高的失配造成的问题较少;在速度方面,例如通过在不同时钟相位添加计数器以提高速度。此外,模数转换器的基础元件的设计的特点是低复杂度,例如通过使用纹

波计数器。

16.附图被包括在内以提供进一步的理解,并且被并入并构成本说明书的一部分。附图示出模数转换器和包括该模数转换器的图像传感器的多个实施例,与说明书一起用于解释该模数转换器和图像传感器的各个实施例的原理和操作。

附图说明

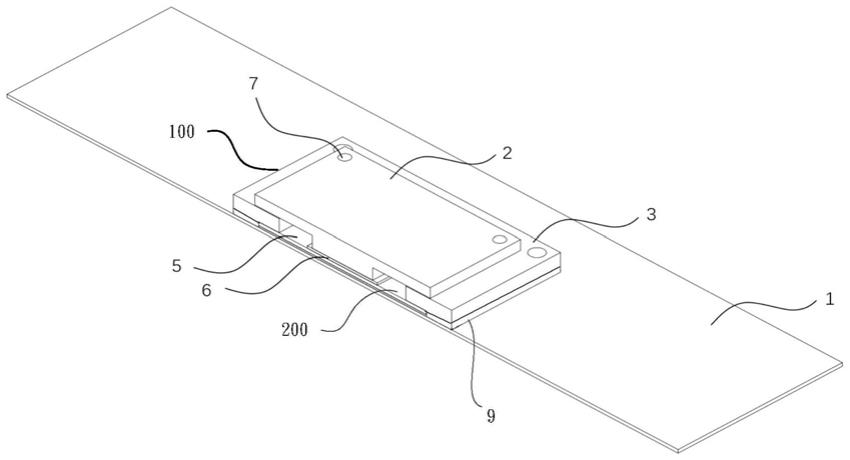

17.图1示出包括用于读出像素阵列的电压的列并行模数转换器的图像传感器的实施例;

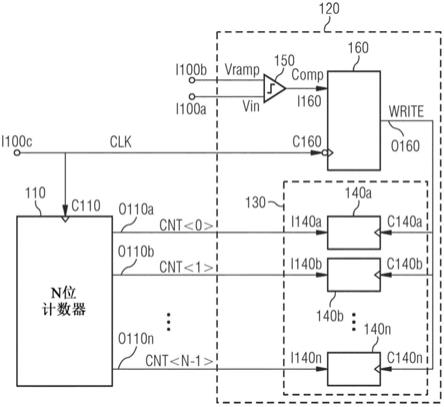

18.图2示出用于图像传感器的模数转换器的第一实施例;

19.图3示出控制模数转换器的操作的控制信号的时序图;

20.图4示出用于图像传感器的模数转换器的第二实施例;

21.图5示出用于读出图像传感器的像素阵列的电压电平的模数转换器的可能架构的实施例;

22.图6示出用于存储低有效计数器位的模数转换器的存储单元的实施例;

23.图7示出用于存储最高有效计数器位的模数转换器的存储单元的实施例;

24.图8示出用于存储最高有效计数器位的模数转换器的存储单元的另一实施例;

25.图9示出模数转换器的同步电路的实施例;

26.图10示出模数转换器的锁存电路的实施例;

27.图11示出模数转换器的计数器电路的架构;

28.图12示出用于生成低有效计数器位的模数转换器的计数器电路的计数器单元的实施例;

29.图13示出用于生成最高有效计数器位的模数转换器的计数器电路的计数器单元的实施例。

具体实施方式

30.图1示出图像传感器1的实施例,该图像传感器包括像素阵列10,该像素阵列包括多个像素组20a、20b、

……

、20m,例如像素列。像素组/列20a、20b、

……

、20m中的每个包括连接到相应像素组/列的相应相关联的组/列总线40a、40b、

……

、40m的多个像素30。该图像传感器还包括用于选择像素行之一以读出设置在所选行中的像素的内容的行选择电路50。图像传感器1还包括配置为读出为读出而选择的像素阵列10的像素30的电压电平的模数转换器100。该模数转换器包括组/列adc电路120a、120b、

……

、120m。组/列adc电路120a、120b、

……

、120m中的每个与像素组/列20a、20b、

……

、20m中的一个相关联。计数器电路110在m个像素组/列之间或m个组/列adc电路120a、120b、

……

、120m之间共享。应当注意,其它部件可位于组/列总线线路40a、

……

、40m与组/列adc电路120a、

……

、120m之间。

31.图2示出用于读出图1的像素阵列10的所选像素30的电压电平的模数转换器100的实施例。模数转换器100配置为组并行模数转换器,例如列并行模数转换器。模数转换器100包括用于施加由所选像素列提供的输入信号vin以读出所选行的像素的电压电平的输入端子i100a。模数转换器100还包括用于施加参考信号vramp的参考端子i100b。参考信号vramp可以由图1所示的斜坡电压发生器60产生。模数转换器100还包括用于施加时钟信号clk的

时钟端子i100c。

32.如图2中进一步示出的,模数转换器100包括计数器电路110,该计数器电路具有施加时钟信号clk的计数器控制连接c110和响应于计数器电路110的计数器状态产生相应计数器位cnt<0>、cnt<1>、

……

、cnt<n

‑

1>的多个计数器输出连接o110a、o110b、

……

、o110n。模数转换器100还包括存储电路130,该存储电路包括多个存储单元140a、140b、

……

、140n。存储单元140a、140b、

……

、140n中的相应之一连接到计数器输出连接o110a、o110、

……

、o110n中的相应之一以用于响应于相应计数器位cnt<0>、cnt<1>、

……

、cnt<n

‑

1>存储相应存储状态。

33.模数转换器100包括用于响应于输入信号vin与参考信号vramp的比较产生比较信号comp的电平的比较器电路150。如还在图1中进一步示出的,模数转换器100包括同步电路160,该同步电路160具有:施加比较信号comp的同步输入连接i160、施加时钟信号clk的同步控制连接c160和生成用于控制在相应存储单元140a、140b、

……

、140n中相应存储状态的存储/写的写控制信号write的同步输出连接o160。相应存储状态在存储单元中的存储过程可以以例如电平敏感或边沿敏感方式之类的各种方式来控制。根据电平敏感存储过程,保持用新计数器位写存储单元,直至比较信号comp切换,则停止在存储单元中存储/写的过程。参照图3描述了边沿敏感写过程的示例。

34.图3示出了时钟信号clk、写控制信号write和在计数器电路110的计数器输出连接o110a、o110b、

……

、o110n处产生的计数器位cnt的时序图。计数器电路110配置为当时钟周期clk的周期cy的第一边沿e1被施加到计数器电路110的控制连接c110时,改变计数器状态。同步电路160配置为当在时钟信号clk的周期cy的第一边沿e1之后的时钟信号clk的周期cy的第二边沿e2被施加到同步电路160的同步控制连接c160时,响应于比较信号comp的电平,生成写控制信号write。

35.根据图2所示的模数转换器100的实施例,计数器电路110配置为在计数器输出连接o110a、o110b、

……

、o110n处提供n个计数器位。在时钟信号clk的每个上升或下降沿上在计数器输出连接处产生计数器位的新值。这n个计数器位cnt<0:n

‑

1>被分配到图1的列adc电路120a、120、

……

、120m的m列。出于简化的原因,图2仅示出图1的列adc电路120中的一个。

36.如图3所示,同步电路160配置为生成迟于时钟信号clk的周期cy的第二边沿e2但在时钟信号clk的周期cy之后的时钟信号clk的第二周期cy’的第一边沿e1’之前的写控制信号write。当比较器电路150生成的比较信号comp的电平切换时,即当斜坡信号vramp与输入信号vin的电平交叉时,比较信号在同步电路160中与时钟信号clk的相对的(上升或下降)沿同步。则使用输出写控制信号write来将计数器位cnt锁存在存储单元140a、140b、

……

、140n中。

37.所提出的共享计数器列并行模数转换器100的架构允许在面积和功率方面优化计数器电路110的布局,这是因为其不受限于图像传感器的像素阵列的组/列间距。此外,存储电路130通常具有比计数器电路110少的晶体管,由此减小整个模数转换器的面积。由于模数转换器需要最大供给功率以生成低有效计数器位的元件(即计数器电路110的元件)在m个像素组/列或组/列adc电路120a、120b、

……

、120m之间共享,因此功耗被进一步有利地减小。此外,如果有利地设计同步电路160,则在比较器电路130的触发期间,仅在adc组单元中

有活动。

38.通过在模数转换器100中引入同步电路,提供额外的优点。由于计数器位在时钟信号clk的相对时钟沿采样,所以计数器触发与写控制信号write的触发之间的值仍处于转换中。这在图3的时序图中示出,其中计数器在时钟信号clk的上升沿e1被触发,而写控制信号write由同步电路160在时钟信号clk的同一时钟周期的下降沿e2生成。

39.计数器电路110有利地具有大约半个时钟周期的时间用于其输出以实现正确的值,这允许使用简单的二进制纹波计数器电路,至少是对于计数器电路150的最低有效位。因此,根据一个有利实施例,计数器电路110配置为二进制纹波计数器电路。作为有利的结果,与例如完全同步或格雷码计数器相反地,在简单触发器以外无需额外逻辑。此外,计数器电路110中的较高位单元的功耗较低。

40.然而,全n位的纹波计数器电路仍要求n个传播延迟以实现其值,这则是该电路实施例的主要速度限制。为了进一步提高模数转换器100的速度,最高有效计数器位可通过使用同步计数器来生成。例如,当用异步纹波计数器生成三个最低有效计数器位并用同步计数器生成其它n

‑

3个计数器位时,计数器延迟大约只有四个传播延迟。

41.图4示出模数转换器100的改进的第二实施例,其中,计数器电路110包括第一计数器电路部分111和至少第二计数器电路部分112。第一计数器电路部分111具有计数器输出连接o110a、

……

、o110x

‑

1的第一部分。第一计数器电路部分111配置为在计数器输出连接o110a、

……

、o110x

‑

1的第一部分的相应计数器输出连接处生成相应最低有效位cnt<0>、

……

、cnt<x

‑

1>。第二计数器电路部分112具有计数器输出连接o110x、

……

、o110n的第二部分。第二计数器电路部分112配置为在计数器输出连接o110x、

……

、o110n的第二部分的相应计数器输出连接处生成相应最高有效位cnt<x>、

……

、cnt<n

‑

1>。

42.第一计数器电路部分111可以配置为响应于时钟信号clk改变其计数器状态,例如,在时钟信号clk的时钟周期cy的第一边沿e1被施加到计数器电路110的计数器控制连接c110时。第二计数器电路部分112可以配置为响应于由第一计数器电路部分111生成的控制信号cnt_clk_msb来改变其计数器状态。

43.如上所述,第一计数器电路部分111可配置为异步纹波计数器,并且第二计数器电路部分112可配置为同步纹波计数器。

44.根据图4所示的模数转换器100的可能实施例,模数转换器100包括用于生成延迟写控制信号write_latch的锁存电路170。锁存电路170可以实现为响应于由第一计数器电路部分111生成的控制信号cnt_clk_msb,生成延迟控制信号write_latch。锁存电路170连接到同步电路160的同步输出连接o160,使得写控制信号write施加到与计数器输出连接的第一部分o110a、

……

、o110x

‑

1的相应之一相连接的存储单元140a、

……

、140x

‑

1中的相应之一,并且延迟的写控制信号write_latch被施加到与计数器输出连接的第二部分o110x、

……

、o110n的相应之一相连接的存储单元140x、

……

、140n中的相应之一。

45.如图4所示,锁存电路170插置于用于控制存储单元140a、

……

、140x

‑

1以存储最低有效计数器位的写控制信号write的路径与发送延迟的写控制信号write_latch以控制在存储单元140x、

……

、140n中最高有效计数器位的存储的路径之间。锁存电路170允许当msb计数器位在第一计数器电路部分111生成的控制信号cnt_clk_msb的上升沿上触发时延迟用于在存储单元140x、

……

、140n中存储最高有效计数器位的写控制信号write并将其用作

msb时钟信号。

46.这给第二/msb计数器电路部分112较多的时间来稳定,这使得能够还在第二计数器电路部分112中使用异步纹波计数器以用于生成最高有效计数器位。因为控制信号cnt_clk_msb被分配给所有列,因此与常规纹波计数器相比,它还允许以略微增大的面积(对于锁存电路170)并略微更高的功耗为代价来使得计数器电路的设计更加容易。此外,功耗仍比使用同步计数器来生成最高有效计数器位的情况低得多。

47.图5示出实现为读出像素阵列的电压的模数转换器100的架构。该模数转换器包括多个组adc电路120a、

……

、120y

‑

1、120y、

……

、120m,例如列adc电路。组/列adc电路中的每个与未在图5中示出的像素阵列的相应像素组(例如像素列)相关联。组/列adc电路120a、

……

、120m中的每个包括相应存储电路130a、

……

、130m和相应同步电路160a、

……

、160m。存储电路130a、

……

、130m中每个和同步电路160a、

……

、160m中每个与像素组/列中的相应之一相关联。

48.模数转换器100包括共享计数器电路110,该共享计数器电路110将其计数器位提供给组/列adc电路120a、

……

、120m中每个、尤其是组/列adc电路120a、

……

、120m内的存储单元140a、

……

、140n中每个。特别地,计数器电路110的计数器输出连接被连接到组/列adc电路120a、

……

、120m中每个的存储电路130a、

……

、130m的存储单元140a、

……

、140n中的每个。

49.根据图5所示的模数转换器100的实施例,计数器电路110包括第一计数器电路单元113和第二计数器电路单元114。对于每个组/列adc电路120a、

……

、120m和由此对于每个存储电路130a、

……

、130m,存在包括第一计数器电路单元113和第二计数器电路单元114的共享双计数器电路。第一计数器电路113和第二计数器电路114可以实现为如图5所示的,即第一和第二计数器电路113和114可分别包括第一计数器电路部分111和第二计数器电路部分112。

50.如图5所示,第一计数器电路单元113的计数器输出连接o113a、

……

、o113z

‑

1连接到存储电路130a、

……

、130m中的每个的存储单元140a、

……

、140z

‑

1的第一部分。此外,第二计数器电路单元114的计数器输出连接o114z、

……

、o114n连接到存储电路130a、

……

、130m中的存储单元140z、

……

、140n的第二部分。

51.根据图5的模数转换器100的一个实施例,第一计数器电路单元113配置为当时钟信号clk的时钟周期的第一边沿(例如上升沿)被施加到第一计数器电路单元113的控制连接c113时,改变(例如增大或减小)其计数器状态。第二计数器电路单元114配置为当与时钟信号的第一边沿相对的时钟信号clk的时钟周期的第二边沿(例如下降沿)施加到第二计数器电路单元114的控制连接c114时,改变(例如增大或减小)其计数器状态。

52.该adc架构的一个优点在于,能够容易地获得2的速度倍数。这通过将计数器电路110重复成第一计数器电路单元113和第二计数器电路单元114,但在相对的时钟边沿对计数器电路单元113和114计时来实现。在该情况下,会有上升沿和下降沿计数器两者,并且相关的同步电路160a、

……

、160m会再次在施加到计数器电路的时钟信号相对的时钟边沿上生成写控制信号write。

53.通过使计数器电路单元的时钟信号异相(例如0、90、180和270度相位偏移的时钟信号)可以进一步扩展多个计数器的概念,由此以增大的面积和功率为代价,以等于相位偏

移数量的因子提高模数转换器的速度。相应地,图5所示的模数转换器的架构必须被修改,因为至少第一时钟信号clk1被施加到第一计数器电路单元113的控制连接c113,并且至少第二时钟信号clk2被施加到第二计数器电路单元114的控制连接c114,而不是在控制连接c113和c114处使用时钟信号clk作为控制信号。该至少第一和第二时钟信号彼此相位偏移。

54.参照图5的模数转换器100的实施例,第一和第二计数器电路单元113和114位于计数器内核的中心并将它们的计数器位分配给列adc电路120a、

……

、120m。计数器电路单元中的一个可以配置为在时钟信号clk的上升沿触发,而另一个在时钟信号clk的下降沿触发,以降低计数器频率。根据图5的模数转换器100的实施例,对于计数器电路110的每个位,存储电路130a、

……

、130m具有两个sram单元。sram单元140a、

……

、140n在比较信号comp的边沿被写,因此写控制信号write的脉冲与其写值的计数器的相对边沿同步。在转换之后,存储在sram单元中的值在输出总线meml、memr上被读出并被进一步处理。

55.对图5的模数转换器100的架构的进一步改进允许在计数器的所有位中使用纹波计数器,这显著地减小adc的功耗。如图4所示,能够在用于传输写控制信号write的路径中插入锁存电路,以给msb存储单元提供延迟的写控制信号write_latch。锁存电路确保当msb计数器位在控制信号cnt_clk_msb的上升沿触发时,用于在msb存储单元中存储计数器位的控制信号被延迟(图4)。由于控制信号cnt_clk_msb被分配给所有列,因此,这给msb计数器电路部分较多时间来稳定,使得计数器电路设计更简单,代价是与常规波纹计数器相比,面积略微增大(对于锁存电路)和功耗略微更高。功耗仍比将同步计数器用于msb计数器电路部分的情况低得多。

56.图6示出存储单元的实施例,例如图4的计数器电路部分111的存储单元140a,以存储最低有效计数器位中的一个。存储单元实现为sram单元。sram单元具有施加计数器位的存储单元输入连接i140a和施加写控制信号write的存储单元控制连接c140a。如图6所示,存储单元输入连接i140a和/或存储单元控制连接c140a分别实现为单端连接。

57.存储单元电路140a包括三级。在包括分支201的晶体管211、212和213和分支202的晶体管221、222、223和224和反向器240的第一级141中,当输入信号/计数器位cnt具有低电平时,如有必要,内部存储节点int处的存储信号被重写。第二级142实现为具有两个背靠背反向器241和242的存储元件。在包括分支203的晶体管231、232、233和234的第三级143中,当控制信号read为高时,所存储的值被放在输出总线上。

58.图6所示的存储单元的实施例具有多个优点。仅单端输入需分配在存储器阵列之上,并且仅需单端写控制信号,由此避免偏移问题。此外,借助于使用动态逻辑,输入连接i140a上的负载相当小,即仅提供一个反相器和附加晶体管。而且,当写控制信号write稳定时,仅反相器240消耗功率。在写控制信号切换之前和之后的功耗是相同的。此外,输入信号cnt相对于写控制信号write的上升沿的建立时间能够非常小。而且,存储单元架构的总晶体管数量相当少。

59.第一级141(重写逻辑)的操作如下。当写控制信号write为低,内部存储节点int处的存储信号被复位为高。写控制信号write为高,如果输入信号cnt高则节点x被拉低。在该情况下,内部节点int处的存储信号的复位值不被重写,这是因为第二分支202中的两个底部晶体管223和224将被切断,存储信号的高电平“1”被存储。需要底部晶体管来避免当节点x处的电势仍在过渡时重写内部存储节点int处的存储信号的复位值。当写控制信号write

变高而输入信号cnt为低,节点x将保持在高电平,并且内部存储节点int将被拉低,由此存储存储信号的低电平“0”。

60.如图7所示,用于存储最高有效计数器位的存储单元略微不同,具有附加的下拉晶体管250和施加到晶体管250的控制连接的stop_write信号。仅当单元已经被写时,即写控制信号write的上升沿之后的一定时间,该stop_write信号才应该变高。为了避免大的静态功耗,它还应该在写控制信号write再次切换成低时为低。

61.在锁存之后拉低x节点,确保当输入信号/计数器位cnt长期是低的时,内部存储节点int不能被重写。使用and门,由延迟写控制信号write_latch生成stop_write信号。该and门确保当延迟写控制信号write_latch低时,stop_write信号低,并且总是能够写存储单元。and门的延迟确保存储单元有足够的时间被重写。

62.图8中示出包括stop_write信号的替代的存储单元的修改的实施例。在该实施方式中,在sram单元中内部避免重写内部存储节点int,并且不依赖于外部写控制信号write。然而,该解决方案要求位于每个sram单元内的两个附加的晶体管。

63.图9示出包括的分离式真单相时钟(tspc)触发器的同步电路160的一个实施例。根据所示实施例,同步电路160配置为上升沿分离式tspc触发器。如图9所示,同步电路160包括输入路径301,该输入路径包括具有背靠背反相器311和312和晶体管313和314的锁存器310。同步电路还包括:电流路径302,其包括晶体管321、322、323和324;和,电流路径303,其包括晶体管331、332和333。同步电路还包括设置在电路路径302与303之间的晶体管361和362。同步电路还包括:电路路径304,其包括晶体管341和342;以及,设置在电流路径303和304之间的晶体管370。同步电路包括输出电流路径305,该输出电流路径包括晶体管351和352。

64.使用分离式触发器具有两个重要的优点。首先,它具有仅两个晶体管的最小clk负载。由于时钟信号clk是具有最高速度的信号,这导致与其它触发器相比较较低的功耗。其次,当输入信号/比较信号comp稳定时,在触发器中不存在功耗。触发器仅在输入连接上的过渡期间消耗功率以施加比较信号comp,其它(tspc)触发器则不是这样的。由于比较信号comp在一行时间期间仅切换两次,这再次导致功率优势,避免在比较信号切换之前和之后的功耗差别。

65.参照图9,比较信号comp首先在时钟信号clk的相对时钟边沿上被锁存。这样做是为了避免触发器的之后部分中的亚稳态问题,这是因为对触发器的建立时间没有控制。如果不会满足建立时间,qn输出潜在地可能会在计数器位仍在改变期间切换。这是应避免的关键情况。

66.参照图5的模数转换器100的架构,图9所示的上升沿tspc触发器的实施例可用于实施计数器电路单元114的写检测。对于计数器电路单元113的写检测,能够容易地构建相同触发器的下降沿版本。在该情况下,在复位时,输出设置为高电平“1”。由此,无需额外的反相器,能够将q输出连接到写控制信号。

67.图10示出在控制信号cnt_clk_msb的高相位上选通写控制信号write的锁存电路170的实施例。该锁存电路可配置为负tspc锁存器。用于写控制信号的tspc锁存器包括:电流路径401,其包括晶体管411、412和413;以及,电流路径402,其包括晶体管421、422和423。电流路径402连接到输出反相器430。

68.在图11中示出用于计数器电路110的架构。使用互补时钟信号clk和clk_n作为包括具有切换触发器113a、

……

、113z

‑

1的计数器电路单元113和包括切换触发器114z、

……

、114n的计数器电路单元114的异步纹波计数器的时钟信号。根据图11所示的计数器电路的实施例,在计数器电路单元113和114两者中仅使用上升沿触发器。最后,在两个计数器电路单元中,计数器单元中的一个(例如第三计数器单元(位3))的时钟信号也被发送到存储单元以锁存用于存储单元存储最高有效计数器位的写控制信号。

69.用于生成最低有效计数器位的计数器电路部分与用于生成最高有效计数器位的计数器电路部分相比使用不同的触发器配置。用于产生最低有效计数器位的计数器电路部分111具有高得多的工作频率,因此对速度和功耗进行优化。在图12中示出用于生成最低有效计数器位的计数器电路部分111的实施例。计数器电路部分111包括:电流路径501,其包括晶体管511、512、513、514;电流路径502,其包括晶体管521、522和523;电流路径503,其包括晶体管530;电流路径504,其包括晶体管541、542和543;和,输出电流路径505,其包括晶体管551和552。在电流路径501和502之间设置有晶体管560。在电流路径504和505之间设置有另一晶体管570。

70.为了在内部节点上具有最小的负载,在计数器电路部分111的电路配置中没有布置保持器电路。这也意味着,由于tspc触发器的动态性质,电路需要最小工作频率来保持其状态。如图12所示,计数器电路部分111能够实现为上升沿tspc触发器。可有利地选择上升沿触发器,这是因为由于在延迟路径中没有设置串联的pmos晶体管,它具有最小的clk负载。

71.关于用于生成最高有效计数器位的计数器电路部分112,工作频率低得多,并且保持器电路的额外负载不大会影响总功耗。

72.在图13中示出用于生成最高有效计数器位的计数器电路部分112的切换触发器电路的实施例。该触发器电路包括:电路路径601,其包括晶体管611、612和613;电路路径602,其具有晶体管621、622和623;以及,电流路径603,其包括晶体管631、632和633。触发器电路还包括:电流路径604,其包括晶体管641、642、643、644和645;电流路径605,其具有晶体管651和652;以及,电流路径606,其包括晶体管661、662、663和664。触发器电路还包括晶体管670、反相器671、耦合到电流路径601的晶体管672,以及设置在电流路径602和603之间的晶体管680。由于用于计数器电路部分112的触发器电路的时钟频率比adc时钟频率低得多,因此在图13示出的动态x、y和qn节点上引入保持器电路,以便当时钟信号不切换时保持状态。

73.附图标记列表

[0074]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

图像传感器

[0075]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

像素阵列

[0076]

20

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

像素组/列

[0077]

30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

像素

[0078]

40

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

组/列总线

[0079]

50

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

行选择电路

[0080]

60

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

斜坡发生器

[0081]

100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

模数转换器

[0082]

110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

计数器电路

[0083]

111、112

ꢀꢀꢀꢀꢀꢀꢀ

计数器电路部分

[0084]

113、114

ꢀꢀꢀꢀꢀꢀꢀ

计数器电路单元

[0085]

120

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列adc电路

[0086]

130

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储电路

[0087]

140

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储单元

[0088]

150

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

比较器电路

[0089]

160

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

同步电路

[0090]

170

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

锁存电路

[0091]

vin

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输入信号

[0092]

vref

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

参考信号

[0093]

clk

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时钟信号

[0094]

write

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

写控制信号

[0095]

comp

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

比较信号

[0096]

write_latch

ꢀꢀꢀꢀ

延迟写控制信号

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。