1.本发明涉及电子部件模块、及氮化硅电路基板。

背景技术:

2.在功率模块等中,从导热率、成本、安全性等方面出发,利用使用了氧化铝、氧化铍、氮化硅、氮化铝等陶瓷基板的电路基板。这些陶瓷基板接合铜、铝等金属电路层、散热层而作为电路基板来使用。它们对树脂基板、以树脂层为绝缘材料的金属基板具有优异的绝缘性和散热性等,因此被用作用于搭载高散热性电子部件的基板。

3.在电梯、车辆、混合动力汽车等之类的功率模块用途中,使用在陶瓷基板的表面用钎料接合金属电路板、再在金属电路板的规定位置搭载半导体元件而成的陶瓷电路基板。近年来,针对与半导体元件的高集成化、高频化、高输出化等相伴的来自半导体元件的散热量增加,使用了具有高导热率的氮化铝烧结体、氮化硅烧结体的陶瓷基板。其中,特别是作为用于搭载电子部件的陶瓷基板,要求机械可靠性高,机械强度、韧性优异的氮化硅基板受到关注。

4.另外,在电子部件模块等中,由于电子部件模块反复受到热应力,若不能耐受该热应力,则有陶瓷基板上产生微小裂纹,或者在构成电子部件模块的各部件之间产生剥落,导致接合强度不良或热阻不良,从而作为电子设备的动作可靠性

·

成品率降低等问题。

5.因此,例如,在专利文献1中记载了用模塑树脂将功率模块密封的树脂密封功率模块的制造方法,所述功率模块包括:功率模块用基板,其在包含氮化硅的陶瓷基板的一面上形成有电路层;半导体元件,其搭载在该功率模块用基板的前述电路层上。另外,专利文献1中记载了,根据该制造方法,通过包括将陶瓷基板的与模塑树脂的接触面的表面粗糙度调整至特定范围的工序等,能够提高半导体元件与功率模块用基板的接合可靠性。

6.现有技术文献

7.专利文献

8.专利文献1:日本特开2018

‑

46192号公报

9.然而,在电子部件模块等中,存在高输出化、高集成化发展,反复施加于电子部件模块的热应力进一步增大的倾向,在现有技术中,陶瓷基板无法耐受热应力,例如,存在在构成电子部件模块的各部件之间产生剥落、或产生微小裂纹,从而产生接合强度不良或热阻不良的情况,而将半导体元件等电子部件搭载于这样的陶瓷电路基板的电子部件模块的可靠性不足。

技术实现要素:

10.发明要解决的课题

11.鉴于上述课题,本发明的目的在于得到可靠性

·

成品率高的电子部件模块、及能够制成可靠性

·

成品率高的电子部件模块的氮化硅电路基板。

12.用于解决课题的手段

13.根据本发明,提供以下所示的电子部件模块、及氮化硅电路基板。

14.即,根据本发明,提供电子部件模块,其具备:

15.氮化硅电路基板;

16.电子部件,其搭载于前述氮化硅电路基板;和

17.密封树脂部,其密封前述氮化硅电路基板的全部或一部分、以及前述电子部件,

18.前述氮化硅电路基板具备:

19.氮化硅基板;

20.第一铜层,其设置于前述氮化硅基板的一面;和

21.第二铜层,其设置于前述氮化硅基板的另一面,

22.前述第二铜层的与设置有前述氮化硅基板的面呈相反侧的面直接或经由接合材料层与散热器接合,

23.在将前述散热器的线膨胀系数设为α

h

(/℃)、将前述散热器的杨氏模量设为e

h

(gpa)、将前述密封树脂部的线膨胀系数设为α

r

(/℃)、将前述密封树脂部的杨氏模量设为e

r

(gpa)时,

24.由以下式(1)算出的s1为

‑

0.38(gpa)以上且

‑

0.23(gpa)以下,

25.由以下式(2)算出的s2为

‑

0.028(gpa)以上且0.019(gpa)以下。

26.式(1):s1=(α

bc

‑

α

h

)

×

e

h

×

(290

‑

25)

27.[其中,α

bc

为前述氮化硅基板以及前述第二铜层的复合层叠体的线膨胀率的近似值,在将前述氮化硅基板的线膨胀系数设为α

b

(/℃)、将前述氮化硅基板的杨氏模量设为e

b

(gpa)、将前述氮化硅基板的厚度设为t

b

(mm)、将前述第二铜层的线膨胀系数设为α

c

(/℃)、将前述第二铜层的杨氏模量设为e

c

(gpa)、将前述第二铜层的厚度设为t

c

(mm)时,α

bc

由以下式(3)算出。

[0028]

式(3):α

bc

=((α

b

×

e

b

×

t

b

) (α

c

×

e

c

×

t

c

))/((e

b

×

t

b

) (e

c

×

t

c

))]

[0029]

式(2):s2=(α

abc

‑

α

r

)

×

e

r

×

(290

‑

25)

[0030]

[其中,α

abc

为前述第一铜层、前述氮化硅基板以及前述第二铜层的复合层叠体的线膨胀率的近似值,在将前述第一铜层的线膨胀系数设为α

a

(/℃)、将前述第一铜层的杨氏模量设为e

a

(gpa)、将前述第一铜层的厚度设为t

a

(mm)、将前述氮化硅基板的线膨胀系数设为α

b

(/℃)、将前述氮化硅基板的杨氏模量设为e

b

(gpa)、将前述氮化硅基板的厚度设为t

b

(mm)、将前述第二铜层的线膨胀系数设为α

c

(/℃)、将前述第二铜层杨氏模量设为e

c

(gpa)、将前述第二铜层的厚度设为t

c

(mm)时,α

abc

由以下式(4)算出。

[0031]

式(4):α

abc

=((α

a

×

e

a

×

t

a

) ((α

b

×

e

b

×

t

b

) (α

c

×

e

c

×

t

c

))/((e

a

×

t

a

) (e

b

×

t

b

) (e

c

×

t

c

))]

[0032]

另外,根据本发明,提供氮化硅电路基板,其具备:

[0033]

氮化硅基板;

[0034]

第一铜层,其设置于前述氮化硅基板的一面;和

[0035]

第二铜层,其设置于前述氮化硅基板的另一面,

[0036]

前述氮化硅电路基板以下述形态被使用:

[0037]

其全部或一部分被密封树脂部密封,并且

[0038]

前述第二铜层的与设置有前述氮化硅基板的面呈相反侧的面直接或经由接合材

料层而与散热器接合,

[0039]

在将前述散热器的线膨胀系数设为α

h

(/℃)、将前述散热器的杨氏模量设为e

h

(gpa)、将前述密封树脂部的线膨胀系数设为α

r

(/℃)、将前述密封树脂部的杨氏模量设为e

r

(gpa)时,

[0040]

由以下式(1)算出的s1为

‑

0.38(gpa)以上且

‑

0.23(gpa)以下,

[0041]

由以下式(2)算出的s2为

‑

0.028(gpa)以上且0.019(gpa)以下。

[0042]

式(1):s1=(α

bc

‑

α

h

)

×

e

h

×

(290

‑

25)

[0043]

[其中,α

bc

为前述氮化硅基板以及前述第二铜层的复合层叠体的线膨胀率的近似值,在将前述氮化硅基板的线膨胀系数设为α

b

(/℃)、将前述氮化硅基板的杨氏模量设为e

b

(gpa)、将前述氮化硅基板的厚度设为t

b

(mm)、将前述第二铜层的线膨胀系数设为α

c

(/℃)、将前述第二铜层的杨氏模量设为e

c

(gpa)、将前述第二铜层的厚度设为t

c

(mm)时,α

bc

由以下式(3)算出。

[0044]

式(3):α

bc

=((α

b

×

e

b

×

t

b

) (α

c

×

e

c

×

t

c

))/((e

b

×

t

b

) (e

c

×

t

c

))]

[0045]

式(2):s2=(α

abc

‑

α

r

)

×

e

r

×

(290

‑

25)

[0046]

[其中,α

abc

为前述第一铜层、前述氮化硅基板以及前述第二铜层的复合层叠体的线膨胀率的近似值,在将前述第一铜层的线膨胀系数设为α

a

(/℃)、将前述第一铜层的杨氏模量设为e

a

(gpa)、将前述第一铜层的厚度设为t

a

(mm)、将前述氮化硅基板的线膨胀系数设为α

b

(/℃)、将前述氮化硅基板的杨氏模量设为e

b

(gpa)、将前述氮化硅基板的厚度设为t

b

(mm)、将前述第二铜层的线膨胀系数设为α

c

(/℃)、将前述第二铜层杨氏模量设为e

c

(gpa)、将前述第二铜层的厚度设为t

c

(mm)时,α

abc

由以下式(4)算出。

[0047]

式(4):α

abc

=((α

a

×

e

a

×

t

a

) ((α

b

×

e

b

×

t

b

) (α

c

×

e

c

×

t

c

))/((e

a

×

t

a

) (e

b

×

t

b

) (e

c

×

t

c

))]

[0048]

发明的效果

[0049]

本发明的电子部件模块、及氮化硅电路基板由于如上所述构成,因此能够制成可靠性

·

成品率高的电子部件模块。

附图说明

[0050]

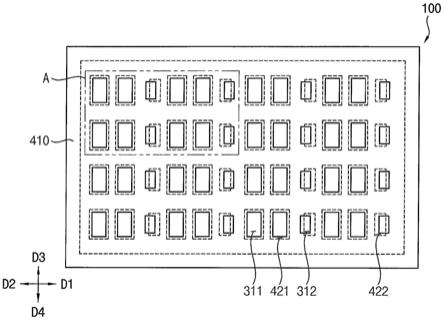

[图1]为本实施方式涉及的氮化硅电路基板的俯视图。

[0051]

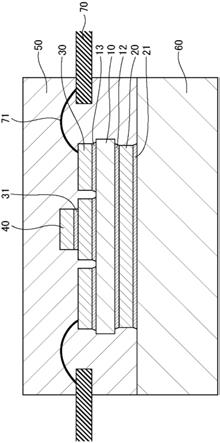

[图2]为本实施方式涉及的氮化硅电路基板的剖视图。

[0052]

[图3]为本实施方式涉及的电子部件模块的剖视图。

[0053]

[图4]为本实施方式涉及的电子部件模块的一部分的放大剖视图。

具体实施方式

[0054]

以下,使用附图对本发明的实施方式进行说明。需要说明的是,在全部附图中,对同样的构成要素标注同样的附图标记,而适当省略说明。另外,图为概略图,与实际的尺寸比率不一致。

[0055]

以下,针对本实施方式的电子部件模块200的构成进行说明。

[0056]

<本实施方式涉及的电子部件模块的构成>

[0057]

本实施方式涉及的电子部件模块200具备:氮化硅电路基板100;电子部件40,其搭

载于氮化硅电路基板100;密封树脂部50,其密封氮化硅电路基板100的全部或一部分以及电子部件40。

[0058]

首先,使用图1、及图2来针对本实施方式涉及的氮化硅电路基板100进行说明。图1为本实施方式涉及的氮化硅电路基板的俯视图,而图2为本实施方式涉及的氮化硅电路基板的剖视图。

[0059]

如图2所示,本实施方式涉及的氮化硅电路基板100具备氮化硅基板10、第一铜层30、和第二铜层20。另外,氮化硅基板10与第二铜层20可以夹着钎料层12而构成层叠状态,氮化硅基板10与第一铜层30可以夹着钎料层13而构成层叠状态。

[0060]

需要说明的是,在本实施方式中,“氮化硅

‑

铜复合体”,是氮化硅基板10、第一铜层30、钎料层13、氮化硅基板10、钎料层12与第二铜层20层叠的状态,是指形成电路图案前的状态。另外,“氮化硅电路基板”,是指在“氮化硅

‑

铜复合体”上形成有电路图案的状态,可以是在形成了电路图案的铜层的一部分上安装有电子部件40等电子部件的状态。

[0061]

接下来,使用图3及图4来对本实施方式涉及的电子部件模块进一步进行说明。图3为本实施方式涉及的电子部件模块的剖视图。另外,图4为本实施方式涉及的电子部件模块的一部分的放大剖视图。

[0062]

如图3所示,在本实施方式中,第二铜层20的与设置有氮化硅基板10的面呈相反侧的面直接或经由接合材料层来与散热器60接合,图3所示的本实施方式的一个例子中,第二铜层20经由接合材料层21而与散热器60接合。在本实施方式中,氮化硅电路基板100的全部或一部分以及电子部件40被密封树脂部50密封。

[0063]

就本实施方式涉及的电子部件模块而言,将散热器60的线膨胀系数设为α

h

(/℃),将散热器60的杨氏模量设为e

h

(gpa),将密封树脂部50的线膨胀系数设为α

r

(/℃),将密封树脂部50的杨氏模量设为e

r

(gpa)时,由以下式(1)算出的s1为

‑

0.38(gpa)以上

‑

0.23(gpa)以下,由以下式(2)算出的s2为

‑

0.028(gpa)以上0.019(gpa)以下。

[0064]

式(1):s1=(α

bc

‑

α

h

)

×

e

h

×

(290

‑

25)

[0065]

式(2):s2=(α

abc

‑

α

r

)

×

e

r

×

(290

‑

25)

[0066]

其中,α

bc

(/℃)表示由氮化硅基板及第二铜层形成的复合层叠体的线膨胀率的近似值,α

abc

(/℃)表示由第一铜层、氮化硅基板及第二铜层形成的复合层叠体的线膨胀率的近似值α

abc

(/℃)。

[0067]

根据本发明,在具有上述构成的电子部件模块中,将由上述式(1)算出的s1、及由上述式(2)算出的s2设为特定的数值范围,由此能够制成可靠性

·

成品率高的电子部件模块。

[0068]

即,电子部件模块、及构成电子部件模块的氮化硅电路基板是将线膨胀系数等不同的材料组合并进行接合而制造的,各构成部件的材料

·

物性

·

形状的选项、及其组合的数量有很多。本技术的发明人经过深入研究,结果发现通过对下述参数进行规定,能够提高电子部件模块的可靠性

·

成品率,从而完成了本发明,所述参数为:蓄积在由氮化硅基板及第二铜层这样的接近于散热器的2层形成的复合层叠体、与散热器之间的残余应力所涉及的参数;以及蓄积在由第一铜层、氮化硅基板及第二铜层这3层形成的复合层叠体(氮化硅电路基板)与密封树脂部之间的残余应力涉及的参数。

[0069]

由上述式(1)算出的s1、即蓄积于由氮化硅基板及第二铜层这样的2层形成的复合

层叠体与散热器之间的残余应力为

‑

0.38gpa以上

‑

0.23gpa以下,优选为

‑

0.36gpa以上

‑

0.24gpa以下,更优选为

‑

0.34gpa以上

‑

0.25gpa以下。

[0070]

上述式(2)算出的s2、即蓄积于由第一铜层、氮化硅基板及第二铜层这样的3层形成的复合层叠体与密封树脂部之间的残余应力为

‑

0.028gpa以上0.019gpa以下,优选为

‑

0.020gpa以上0.015gpa以下,更优选为

‑

0.015gpa以上0.010gpa以下。

[0071]

由式(1)表示的s1、及由式(2)表示的s2可以通过对电子部件模块中使用的各构成部件材料的种类

·

物性

·

形状等适当地进行选择而调整。

[0072]

其中,对于由氮化硅基板及第二铜层形成的复合层叠体的线膨胀率的近似值α

bc

(/℃)而言,在将氮化硅基板的线膨胀系数设为α

b

(/℃),将氮化硅基板的杨氏模量设为e

b

(gpa),将氮化硅基板的厚度设为t

b

(mm),将第二铜层的线膨胀系数设为α

c

(/℃),将第二铜层的杨氏模量设为e

c

(gpa),将第二铜层的厚度设为t

c

(mm)时,α

bc

(/℃)由以下式(3)算出。

[0073]

式(3):α

bc

=((α

b

×

e

b

×

t

b

) (α

c

×

e

c

×

t

c

))/((e

b

×

t

b

) (e

c

×

t

c

))

[0074]

α

bc

(/℃)优选为1.0

×

10

‑6/℃以上3.0

×

10

‑5/℃以下,更优选为3.0

×

10

‑6/℃以上2.0

×

10

‑5/℃以下。

[0075]

另外,对于由第一铜层、氮化硅基板及第二铜层这样的3层形成的复合层叠体的线膨胀率的近似值α

abc

(/℃)而言,在将前述第一铜层的线膨胀系数设为α

a

(/℃),将前述第一铜层的杨氏模量设为e

a

(gpa),将前述第一铜层的厚度设为t

a

(mm),将前述氮化硅基板的线膨胀系数设为α

b

(/℃),将前述氮化硅基板的杨氏模量设为e

b

(gpa),将前述氮化硅基板的厚度设为t

b

(mm),将前述第二铜层的线膨胀系数设为α

c

(/℃),将前述第二铜层杨氏模量设为e

c

(gpa),将前述第二铜层的厚度设为t

c

(mm)时,α

abc

(/℃)由以下式(4)算出。

[0076]

式(4):α

abc

=((α

a

×

e

a

×

t

a

) ((α

b

×

e

b

×

t

b

) (α

c

×

e

c

×

t

c

))/((e

a

×

t

a

) (e

b

×

t

b

) (e

c

×

t

c

))

[0077]

α

abc

(/℃)优选为1.0

×

10

‑6/℃以上3.0

×

10

‑5/℃以下,更优选为5.0

×

10

‑6/℃以上2.0

×

10

‑5/℃以下。

[0078]

α

bc

(/℃)、及α

abc

(/℃)在上述数值范围内,由此可以进一步提高电子部件模块的可靠性。

[0079]

本发明涉及的氮化硅电路基板100表示上述本实施方式涉及的电子部件模块200中的氮化硅电路基板100。即,对于本发明涉及的氮化硅电路基板100而言,其全部或一部分被密封树脂部50密封,并且以第二铜层20的与设置有氮化硅基板10的面呈相反侧的面直接或经由接合材料层21与散热器接合的方式来使用。

[0080]

在本实施方式中,第一铜层30制成形成为电路图案的铜层。需要说明的是,电子部件40经由焊锡层31而接合在第一铜层30上,通过外部连接用的引线框、引线键合线71而将第一铜层30、电子部件40与外部连接端子70连接。在本实施方式中,作为一个例子,示出通过引线键合线71与外部连接端子70连接的例子。另外,外部连接端子70也可以不经由引线键合线71而直接连接于基板。在这种情况下,外部连接端子70例如可以通过焊锡、或超声波接合来进行接合。

[0081]

需要说明的是,电子部件40为半导体元件等电子部件,可以根据所期望的功能来选择例如igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)、mosfet(metal oxide semiconductor field effect transistor,金属

‑

氧化物半导体场效应晶

体管)、fwd(free wheeling diode,续流二极管)等各种半导体元件。

[0082]

另外,将电子部件40接合的焊锡层31可以设为例如sn

‑

sb系、sn

‑

ag系、sn

‑

cu系、sn

‑

in系、或者sn

‑

ag

‑

cu系的焊锡材料(所谓的无铅焊锡材料)。

[0083]

另外,外部连接端子70例如由铜或铜合金形成,引线键合线71例如由铜、铜合金、铝、金等形成。

[0084]

另外,在本实施方式中,第二铜层20设为散热器接合用铜层。

[0085]

在本实施方式中,第二铜层20经由接合材料层21来与散热器60接合。

[0086]

如上所述,在本实施方式中,氮化硅电路基板100的全部或一部分以及电子部件40被密封树脂部50密封。

[0087]

其中,对于第二铜层20的与设置有氮化硅基板10的面呈相反侧的面、即第二铜层下表面22而言,优选具有未被密封树脂部50覆盖的未被覆区域。换言之,对于第二铜层下表面22而言,优选其一部分或全部未被密封树脂部50覆盖。

[0088]

另外,本实施方式涉及的电子部件模块中优选的是,第二铜层20的与设置有氮化硅基板10的面呈相反侧的面(即,第二铜层下表面22)在远离氮化硅基板10的方向上比密封树脂部50更凸出。即,如图4所示,在将密封树脂部50的与散热器60相对的面设为密封树脂部下表面51,将第二铜层20的与散热器60相对的面设为第二铜层下表面22时,设计成在密封树脂部下表面51与接合材料层21之间存在阶差,第二铜层下表面22相对于密封树脂部下表面51凸出。通过这样设计,在将氮化硅电路基板100与散热器60接合的工序中,即,在将第二铜层20露出的第二铜层下表面22(未被密封树脂部50覆盖的未被覆区域)与散热器60接合的工序中,在使氮化硅电路基板100与散热器60抵接接触时,最初与散热器60接触的是第二铜层下表面22,因此能够在密封树脂部50不阻碍接合的情况下,顺利地将第二铜层下表面22与散热器60接合,并且能够提高第二铜层20与散热器60的接合的可靠性。

[0089]

以下,针对本实施方式涉及的氮化硅电路基板100的各构成进行更详细的说明。

[0090]

<氮化硅基板>

[0091]

本实施方式涉及的氮化硅基板10具有支承第一铜层30及第二铜层20的功能。其中,氮化硅基板从其厚度方向观察为矩形。另外,氮化硅基板10的厚度t

b

优选在0.2mm以上1.5mm以下的范围,更优选设定为0.2mm以上0.8mm以下,在本实施方式中,设为0.32mm。需要说明的是,氮化硅基板10的形状等为本实施方式中的一个例子,只要可发挥出本发明涉及的功能,则也可以与本实施方式的情况不同。

[0092]

对于本实施方式涉及的氮化硅基板10而言,其杨氏模量e

b

优选为250gpa以上320gpa以下,更优选为260gpa以上310gpa以下。

[0093]

另外,对于本实施方式涉及的氮化硅基板10而言,其线膨胀率α

b

优选为1.5

×

10

‑6/℃以上4.0

×

10

‑6/℃以下,更优选为1.8

×

10

‑6/℃以上且小于3.0

×

10

‑6/℃。

[0094]

通过以上述方式调整氮化硅基板10的物性,可以易于将s1、及s2调整至上述数值范围内,另外,可以进一步提高电子部件模块中的可靠性

·

成品率。

[0095]

需要说明的是,氮化硅基板10的杨氏模量e

b

、线膨胀率α

b

等物性可以通过控制氮化硅基板10的制造方法(具体而言,原料的配合、煅烧条件等)进行调整。

[0096]

<第一铜层>

[0097]

第一铜层30从其厚度方向观察为多边形。第一铜层30的厚度优选设定在0.10mm以

上1.50mm以下的范围,更优选为0.15mm以上1.40mm以下,进一步优选为0.20mm以上1.20mm以下。在本实施方式中,作为一个例子,设为0.30mm。需要说明的是,第一铜层30的形状等是本实施方式中的一个例子,如果可发挥出本发明涉及的功能,则也可以与本实施方式的情况不同。

[0098]

对于本实施方式涉及的第一铜层30而言,可以将其线膨胀率优选设为16

×

10

‑6/℃以上19

×

10

‑6/℃以下,更优选设为17

×

10

‑6/℃以上18

×

10

‑6/℃以下。

[0099]

第一铜层30的杨氏模量优选为90gpa以上150gpa以下,更优选为100gpa以上140gpa以下,进一步优选为110gpa以上130gpa以下。

[0100]

通过以上述方式调整第一铜层30及第二铜层20的物性,可以易于将s2调整至上述数值范围内,并可以进一步提高电子部件模块中的可靠性

·

成品率。

[0101]

第一铜层30中的铜晶体的平均晶体粒径优选为50μm以上500μm以下,更优选为100μm以上300μm以下。

[0102]

本实施方式涉及的电子部件模块中,电子部件40经由焊锡层31等接合层而搭载在第一铜层30上,并被密封树脂部50覆盖,因此第一铜层30被密封树脂部50、和焊锡层第一铜层30及电子部件40、和氮化硅基板10等夹持,虽然残余应力、热应力施加在这些材料之间,但通过将第一铜层30中的铜晶体的平均晶体粒径设为上述数值范围内,能够进一步降低接合强度不良或热阻不良。上述机理尚不明确,但推测是由于通过使第一铜层30中的铜晶体的平均晶体粒径处于上述数值范围内,在第一铜层30中,铜晶体适度地发生晶界滑移等,从而应力得以适度地缓和。

[0103]

<第二铜层>

[0104]

第二铜层20从其厚度方向观察为多边形。第二铜层20的厚度优选设定在0.10mm以上1.50mm以下的范围,更优选为0.15mm以上1.40mm以下,进一步优选为0.20mm以上1.20mm以下。在本实施方式中,作为一个例子,设为0.30mm。需要说明的是,第二铜层20的形状等是本实施方式中的一个例子,只要可发挥出本发明涉及的功能,则也可以与本实施方式的情况不同。

[0105]

对于本实施方式涉及的第二铜层20而言,其线膨胀率可以优选设为16

×

10

‑6/℃以上19

×

10

‑6/℃以下,更优选设为17

×

10

‑6/℃以上18

×

10

‑6/℃以下。

[0106]

通过将第二铜层20的物性调整为上述方式,可以易于将s1及s2调整至上述数值范围内,并可以进一步提高电子部件模块中的可靠性

·

成品率。

[0107]

第二铜层20中的铜晶体的平均晶体粒径优选为50μm以上500μm以下,更优选为100μm以上300μm以下。

[0108]

如后所述,在将本实施方式涉及的氮化硅电路基板100用作电子部件模块时,在第二铜层20经由焊锡层等接合材料层21与散热器接合,第二铜层20被焊锡层等接合材料层21及散热器60、和氮化硅基板10等夹持,虽然残余应力、热应力施加在这些不同种材料之间,但通过将第二铜层20中的铜晶体的平均晶体粒径设为上述数值范围内,能够进一步降低接合强度不良或热阻不良。上述机理尚不明确,但推测是由于通过使第二铜层20中的铜晶体的平均晶体粒径处于上述数值范围内,在第二铜层20中,铜晶体适度地发生晶界滑移等,从而应力得以适度地缓和。

[0109]

第二铜层20的杨氏模量优选为90gpa以上150gpa以下,更优选为100gpa以上

140gpa以下,进一步优选为110gpa以上130gpa以下。

[0110]

需要说明的是,对于第一铜层30及第二铜层20中的线膨胀率、杨氏模量及铜晶体的平均晶体粒径而言,可以通过适当地选择构成第一铜层30及第二铜层20的铜板,并对在氮化硅基板10上钎焊第一铜层30及第二铜层20时的制造条件等进行控制而进行调整。

[0111]

另外,第一铜层30及第二铜层20中的铜晶体的平均晶体粒径可以用实施例中记载的方法求出。

[0112]

<钎料层>

[0113]

本实施方式涉及的钎料层12及钎料层13可分别配置在氮化硅基板10与第一铜层30之间、氮化硅基板10与第二铜层20之间,使第一铜层30、或第二铜层20与氮化硅基板10接合。典型而言,钎料层12及钎料层13的厚度设定在3μm以上40μm以下的范围,进一步优选为4μm以上25μm以下。

[0114]

需要说明的是,本实施方式涉及的氮化硅电路基板100可以在第一铜层30及第二铜层20上具有镀层。镀层可以由已知的材料形成,例如可以设为ag、ni

‑

p。

[0115]

对于钎料层12及13的组成而言,可以由在钎料中含有选自钛、锆、铪、铌、钽、钒、铝、锡中的至少一种活性金属的银

‑

铜系钎料构成。ag与cu、sn或in的配合比优选可举出下述组成:ag:85.0质量份以上95.0质量份以下,cu:5.0质量份以上13.0质量份以下,sn或in:0.4质量份以上3.5质量份以下。通过设为上述数值范围内,能够防止钎料的熔融温度过度地上升,能够以适度的温度进行接合,能够使来自接合时的热膨胀率差的热应力降低,并能够提高耐热循环性。

[0116]

相对于ag、cu、与sn或in的合计100质量份而言,钛等活性金属的添加量例如可以设为1.5质量份以上5.0质量份以下。通过适当地调整活性金属的添加量,可以进一步提高相对于陶瓷板而言的润湿性,并可以进一步抑制接合不良的产生。

[0117]

<密封树脂部>

[0118]

在本实施方式中,密封树脂部50的线膨胀系数可以优选设为5

×

10

‑6/℃以上30

×

10

‑6/℃以下,更优选设为6

×

10

‑6/℃以上20

×

10

‑6/℃以下,可以进一步优选设为6

×

10

‑6/℃以上15

×

10

‑6/℃以下。密封树脂部50例如可以使用含sio2填料的环氧系树脂等。

[0119]

密封树脂部50的杨氏模量优选为50gpa以上80gpa以下,更优选为10gpa以上60gpa以下,进一步优选为15gpa以上40gpa以下。

[0120]

密封树脂部50可以通过使密封树脂部形成用树脂组合物固化而形成。

[0121]

密封树脂部形成用树脂组合物的种类没有特别限定,可以使用传递模塑用树脂组合物、压塑成型用树脂组合物、液状密封材料等在该技术领域中通常使用的树脂组合物。

[0122]

密封树脂部形成用树脂组合物优选包含热固性树脂,优选包含选自环氧树脂、酚醛树脂、氰酸酯树脂、双马来酰亚胺三嗪树脂、丙烯酸树脂、有机硅树脂中的1种或2种以上,更优选至少包含环氧树脂。

[0123]

密封树脂部形成用树脂组合物可以进一步包含固化剂、填充材料等。

[0124]

作为填充材料,可举出熔融二氧化硅(球状二氧化硅)、结晶二氧化硅、氧化铝、碳化硅、氮化硅、氮化铝、氮化硼、氧化铍、氧化锆等粉末,或将它们球形化而成的珠粒、玻璃纤维、芳纶纤维、碳纤维等。填充材料可以单独使用1种,也可以将2种以上组合而使用。

[0125]

<散热器>

[0126]

散热器60例如由铝、铜、它们的合金等具有高导热率的材料形成,优选由铝、或、铝合金来形成。

[0127]

前述散热器的线膨胀系数优选为20

×

10

‑6/℃以上30

×

10

‑6/℃以下,更优选设为22

×

10

‑6/℃以上28

×

10

‑6/℃以下。

[0128]

散热器60的杨氏模量优选为40gpa以上110gpa以下,更优选为50gpa以上100gpa以下,进一步优选为60gpa以上90gpa以下。

[0129]

需要说明的是,各构成材料的线膨胀率例如可以基于jis r 1618并用热机械分析装置(tma:thermomechanical analyzer)来求出。需要说明的是,在本发明中,线膨胀率设为各构成材料在25~400℃时显示出的线膨胀率(线膨胀系数)。

[0130]

另外,各构成材料的杨氏模量可以基于jis r1602由静态挠曲法进行测定。

[0131]

<氮化硅电路基板的制造方法>

[0132]

本实施方式涉及的电子部件模块200可以由以下方法制造。首先,针对本实施方式涉及的氮化硅电路基板100的制造方法进行说明。

[0133]

首先,准备具有所期望的物性的氮化硅基板10。氮化硅基板10可以由以下制造方法得到。即,将包含氮化硅粉末、y2o3、mgo等烧结助剂的原料粉末、有机溶剂、和根据需要的有机粘结剂、增塑剂等用球磨机均匀地混合而制成原料浆料。将得到的原料浆料进行消泡

·

增粘后,利用刮刀法进行片材成型而得到成型体。将得到的片状成型体切断后,于400~800℃脱脂,进一步在煅烧炉内于1700~1900℃在氮气氛中煅烧1~10小时,由此得到氮化硅基板10。

[0134]

接下来,在氮化硅基板10的两面印刷形成例如添加有作为活性金属的ti的ag

‑

cu系合金糊剂作为包含活性金属的钎料,将与氮化硅基板10大致相同的长方形的铜板于600℃~900℃的温度加热接合至两面。其中,作为铜板,优选使用无氧铜板。另外,作为铜板,更优选使用压延铜板。将铜板经由钎料接合至氮化硅基板10的两面,由此可以得到氮化硅

‑

铜复合体。

[0135]

接着,对第一铜层30进行蚀刻处理而形成电路图案。在第一铜层30的上表面层合光阻剂(省略图示)。在这种情况下,可以涂布液状的光阻剂。

[0136]

接下来,为了利用光阻剂形成电路图案,进行基于电路图案的图案曝光。在这种情况下,可以使形成有电路图案的负图像的膜密合于光阻剂,通过所谓的一并曝光而使光阻剂感光,也可以使用所谓的直描型曝光装置(不使用上述膜)而使光阻剂感光。

[0137]

接下来,基于电路图案对感光后的光阻剂进行蚀刻。

[0138]

接下来,除去残余的光阻剂。

[0139]

此时,针对第二铜层20,可以不进行蚀刻处理,也可以同样地形成图案。此外,也可以对电路图案形成后的第二铜层20及第一铜层30实施镀敷。

[0140]

由此,制造出形成有电路图案状态的氮化硅电路基板100。

[0141]

上述本实施方式涉及的氮化硅电路基板100具备氮化硅基板10、设置于氮化硅基板的一面的第一铜层30、和设置于氮化硅基板的另一面的第二铜层20,氮化硅电路基板100以其全部或一部分被密封树脂部50密封,并且第二铜层20的与设置有氮化硅基板10的面呈相反侧的面以直接或经由接合材料层21与散热器60接合的方式来使用,在将散热器60的线膨胀系数设为α

h

(/℃)、将散热器60的杨氏模量设为e

h

(gpa)、将密封树脂部50的线膨胀系数

设为α

r

(/℃)、将密封树脂部50的杨氏模量设为e

r

(gpa)时,由上述式(1)算出的s1为

‑

0.38(gpa)以上

‑

0.23(gpa)以下,由上述式(1)算出的s2为

‑

0.028(gpa)以上0.019(gpa)以下。

[0142]

接下来,将电子部件40经由焊锡层31搭载在第一铜层30上。在本实施方式中,使用例如sn

‑

sb系、sn

‑

ag系、sn

‑

in系、或者sn

‑

ag

‑

cu系的焊锡材料,将第一铜层30与电子部件40进行焊锡接合。

[0143]

接下来,将电子部件40等利用密封树脂进行树脂密封,形成密封树脂部50。树脂密封可以使用已知的方法,例如可以利用传递模塑进行树脂密封。另外,在树脂密封工序中,例如通过将电子部件模块的第二铜层下表面22在预先抵接于具有可塑性的材料的状态下进行树脂密封,可以在第二铜层20的与设置有氮化硅基板10的面呈相反侧的面(即,第二铜层下表面22)上残存未被密封树脂部50覆盖的未被覆区域,并且可以将第二铜层下表面22设为相对于密封树脂部下表面51凸出。

[0144]

如上所述,可制作本实施方式涉及的电子部件模块200。

[0145]

需要说明的是,本发明不限定于前述实施方式,可以实现本发明目的的范围内的变形、改良等包含在本发明中。实施例

[0146]

以下,参照实施例来对本发明进行详细地说明,但本发明不受这些实施例中记载的任何限定。

[0147]

<氮化硅电路基板>

[0148]

用以下方法准备氮化硅电路基板。

[0149]

<氮化硅基板>

[0150]

准备具有表1中记载的线膨胀率α

b

、杨氏模量e

b

、厚度t

b

的氮化硅基板。

[0151]

具体而言,在平均粒径0.7μm的氮化硅原料粉末91.4质量份中,作为烧结助剂,添加y2o

3 6.0质量份和mgo 1.5质量份,混入有机溶剂、有机粘结剂、增塑剂等并用球磨机均匀地混合,制成原料浆料。将原料浆料消泡

·

增粘后,用刮刀法将片材成型而得到成型体。将得到的片材成型体切断后,于500℃脱脂,进一步在煅烧炉内在1850℃的氮气氛中煅烧5小时,制作氮化硅基板。

[0152]

需要说明的是,准备尺寸为148mm

×

200mm的氮化硅基板。

[0153]

<第一铜层及第二铜层用铜板>

[0154]

准备具有表1中记载的线膨胀率、杨氏模量、厚度的压延铜板。

[0155]

<氮化硅电路基板的制造方法>

[0156]

使用表1所示组合的氮化硅基板和铜板来制造氮化硅电路基板。

[0157]

首先,作为钎料(包含活性金属),准备相对于ag粉末(福田金属箔粉工业株式会社制:ag

‑

hwq 2.5μm)89.5质量份、cu粉末(福田金属箔粉工业株式会社制:cu

‑

hwq 3μm)9.5质量份、sn粉末(福田金属箔粉工业株式会社制:sn

‑

hpn 3μm)1.0质量份的合计100质量份而言,包含氢化钛粉末(toho technical service co.,ltd.制:tch

‑

100)3.5质量份的钎料。

[0158]

将上述钎料、粘结剂树脂和溶剂混合,得到钎料糊剂。以各面的干燥厚度达到约10μm的方式,将该钎料糊剂用丝网印刷法涂布于氮化硅基板的两面。

[0159]

之后,将铜板重叠于氮化硅基板的两面,在1.0

×

10

‑3pa以下的真空中在780℃、30分钟的条件下进行加热,使铜板与氮化硅基板经钎料接合。由此,得到氮化硅基板与铜板经钎料接合而成的氮化硅

‑

铜复合体。此外,在得到的氮化硅

‑

铜复合体铜层上印刷抗蚀阻剂,

经氯化铁溶液蚀刻而形成电路图案,得到氮化硅电路基板。

[0160]

<电子部件模块的制造方法>

[0161]

在得到的氮化硅电路基板的电路图案上,焊锡接合作为电子部件的igbt元件。需要说明的是,作为焊锡材料使用sn

‑

ag

‑

cu系。接下来,通过传递模塑使密封树脂部成型,并使密封树脂部固化。

[0162]

<评价方法>

[0163]

(1)铜板、氮化硅基板的线膨胀率(α

b

)

[0164]

基于jis r 1618,用热机械分析装置(tma:thermomechanical analyzer)测定各铜板、及各氮化硅基板在25℃~400℃时的线膨胀率(线膨胀系数)。

[0165]

(2)氮化硅基板的杨氏模量(e

b

)

[0166]

基于jis r1602,用静态挠曲法进行测定。试验片形状设为3mm

×

4mm

×

40mm。

[0167]

<铜的平均晶体粒径的评价方法>

[0168]

用以下方法求出氮化硅电路基板中的第一铜层及第二铜层的铜的平均晶体粒径。均为50μm以上500μm以下的范围。

[0169]

首先,由以下步骤得到测定用的“截面”。

[0170]

(1)将各实施例及比较例中得到的陶瓷电路基板以垂直于主表面并且通过基板的重心的截面进行切断。使用仿形机床来切断。

[0171]

(2)将切断后的氮化硅电路基板进行树脂包埋,制成树脂包埋体。

[0172]

(3)使用金刚石磨粒对制成的树脂包埋体中的复合体截面进行抛光。

[0173]

针对经上述研磨的氮化硅电路基板截面,利用电子背散射衍射法进行测定。

[0174]

具体而言,首先,在上述研磨后的第一铜层或第二铜层的大致中心附近,在加速电压15kv的条件下,在50倍的观察视野中进行基于电子背散射衍射(ebsd)法的分析,取得数据。在ebsd法中,使用了hitachi high

‑

technologies corporation制的su6600型场发射扫描显微镜,以及株式会社tsl solutions制的解析装置。

[0175]

利用株式会社tsl solutions制的软件:oim data analysis 7.3.0将测定数据可视化来制成晶体取向图。通过用图像处理软件解析该晶体取向图,求出铜层中的铜晶体的平均晶体粒径。

[0176]

在上述中,作为图像处理软件,使用media cybernetics公司制的image

‑

pro plus shape stack版本6.3。需要说明的是,平均晶体粒径的算出使用截线法,在1个观察图像上平行地引出10条以上规定长度的直线,得到上述直线将铜晶体粒子横切的部分的直线长度的平均值,作为铜晶体的平均晶体粒径(这些是软件自动处理而算出的值)。

[0177]

<热循环试验、及可靠性评价>

[0178]

首先,将作为常温(作为一个例子为20℃)下的试验对象的电子部件模块移动到150℃的环境内,并且在150℃的环境内保持15分钟(第1工序)。

[0179]

接下来,将接合基板从150℃的环境内移动至

‑

55℃的环境内,在

‑

55℃的环境内保持15分钟(第2工序)。

[0180]

然后,将第1工序与第2工序交替地重复2000次。

[0181]

接下来,通过超声波探伤测定,观察钎料层13和第一铜层30有无剥离。评价基准示于以下。

[0182]

◎

:不产生剥离。

[0183]

○

:略微产生剥离。

[0184]

具体而言,以产生剥离的实验例5为基准,将发现产生剥离但与实验例5为相同程度、或发现产生剥离的程度比实验例5轻的情况设为

△

。

[0185]

×

:大量产生剥离。

[0186]

具体而言,以发现产生剥离的实验例5为基准,将发现产生剥离且产生剥离比实验例5多的情况设为

×

。

[0187]

将评价结果等汇总而示于表1。

[0188]

[表1]

[0189]

由实施例1~8、比较例1~4可知,通过处于s1和s2规定的范围内,可以稳定地得到可靠性高的电子部件模块。由以上可以理解,为了稳定地得到可靠性高的电子部件模块,将

s1及s2控制在本发明规定的范围内是重要的。

[0190]

本技术主张于2019年4月26日提出申请的日本专利申请特愿2019

‑

085446号为基础的优先权,其公开内容的全部并入于此。

[0191]

附图标记说明

[0192]

10 氮化硅基板

[0193]

12 钎料层

[0194]

13 钎料层

[0195]

20 第二铜层

[0196]

21 接合材料层

[0197]

22 第二铜层下表面

[0198]

30 第一铜层

[0199]

31 焊锡层

[0200]

40 电子部件

[0201]

50 密封树脂部

[0202]

51 密封树脂部下表面

[0203]

60 散热器

[0204]

70 外部连接端子

[0205]

71 引线键合线

[0206]

100 氮化硅电路基板

[0207]

200 电子部件模块

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。