1.本公开涉及包括光学元件的显示装置。

背景技术:

2.显示装置可包括如传感器、相机这样的光学元件。为了避免与画面的干涉,光学元件可配置在显示装置的边框区域(包围画面的区域)。

3.若减小显示装置的边框,则可增加显示装置的屏占比(screen

‑

to

‑

body ratio),即,从正面观察显示装置时画面所占的比率。屏占比反映显示装置的技术水平的同时,在消费者选择产品时起到重要作用。然而,随着显示装置的边框减少,很难将光学元件配置在边框区域,因此需要开发出将光学元件配置在画面内的技术。

技术实现要素:

4.各实施例用于在包括光学元件的显示装置中将光学元件配置在画面内的同时提高显示装置的分辨率和透过率。

5.一实施例涉及的显示装置包括:基板,包括第一显示区域和第二显示区域;光学元件,与所述第二显示区域重叠;半导体层,位于所述基板上;第一绝缘层,被设置成覆盖所述半导体层;栅极导电体,位于所述第一绝缘层上;第二绝缘层,被设置成覆盖所述栅极导电体;数据导电体,位于所述第二绝缘层上;第三绝缘层,被设置成覆盖所述数据导电体;以及像素电极,位于所述数据导电体上,位于所述第一显示区域的所述数据导电体包括不透明导电体,位于所述第二显示区域的所述数据导电体的一部分为透明导电体。

6.可以是,在所述第二显示区域,所述数据导电体包括与所述半导体层连接的源极连接部、漏极连接部和布线部,所述布线部为所述透明导电体。

7.可以是,所述透明导电体由包括上部层、中间层和下部层的三层结构构成,所述上部层和所述下部层包括ito、izo、igzo、azo、gzo和itzo中的至少一种,以及所述中间层包括银(ag)、铜(cu)和铝(al)中的至少一种。

8.可以是,所述中间层的厚度在以下。

9.可以是,所述源极连接部和所述漏极连接部由上部层和下部层包括钛(ti)且中间层包括铝(al)的三层结构构成。

10.可以是,所述像素电极由包括上部层、中间层和下部层的三层结构构成。

11.可以是,所述栅极导电体由包括上部层、中间层和下部层的三层结构构成。

12.可以是,在所述第一显示区域,所述数据导电体由上部层和下部层包括钛(ti)且中间层包括铝(al)的三层结构构成。

13.可以是,所述第二显示区域包括透过区域。

14.一实施例涉及的显示装置包括:基板,包括第一显示区域和第二显示区域;光学元件,与所述第二显示区域重叠;扫描线,位于所述基板上且在第一方向上延伸;数据线和驱动电压线,在与所述第一方向垂直的第二方向上延伸;驱动晶体管,包括与所述驱动电压线

电连接的第一电极和第一栅电极;第二晶体管,包括与所述数据线连接的第一电极;以及像素电极,与所述驱动晶体管电连接,位于所述第一显示区域的所述数据线和所述驱动电压线包括不透明导电体,位于所述第二显示区域的所述数据线和所述驱动电压线中的至少一个的一部分为透明导电体。

15.可以是,在所述第二显示区域,所述数据线包括在所述第二方向上延伸的布线部以及与所述第二晶体管的所述第一电极连接的第二晶体管连接部。

16.可以是,所述数据线的所述布线部为所述透明导电体,并且所述第二晶体管连接部包括所述不透明导电体。

17.可以是,所述显示装置还包括:第五晶体管,包括与所述驱动电压线连接的第一电极。

18.可以是,所述驱动电压线包括在所述第一方向上延伸的横向布线部、在所述第二方向上延伸的纵向布线部、岛型电极连接部、维持电极连接部以及第五晶体管连接部。

19.可以是,所述驱动电压线的所述横向布线部和所述纵向布线部为所述透明导电体,并且所述岛型电极连接部、所述维持电极连接部和所述第五晶体管连接部包括所述不透明导电体。

20.可以是,所述横向布线部与所述维持电极连接部直接接触并被电连接。

21.可以是,所述维持电极与所述第一栅电极构成维持电容器,并且绝缘层位于其间。

22.可以是,所述纵向布线部包括第一纵向布线部和第二纵向布线部,所述第一纵向布线部与所述岛型电极连接部直接接触并被电连接,并且所述第二纵向布线部与所述第五晶体管连接部直接接触并被电连接。

23.可以是,所述岛型电极连接部通过绝缘层的开口而与岛型电极电连接。

24.可以是,所述第五晶体管连接部通过绝缘层的开口而与所述第五晶体管的所述第一电极电连接。

25.(发明效果)

26.根据实施例,在包括光学元件的显示装置中,通过将光学元件配置在画面内,并且使像素区域的布线中的一部分包括透明导电体,从而可提高显示装置的分辨率和透过率。

附图说明

27.图1是一实施例涉及的显示装置的示意性平面图。

28.图2是一实施例涉及的显示装置的示意性剖视图。

29.图3是一实施例涉及的显示装置的第一显示区域和第二显示区域的示意性配置图。

30.图4是关于一实施例涉及的显示装置的第二显示区域的一部分的剖视图。

31.图5是关于一实施例涉及的显示装置的第一显示区域的一部分的剖视图。

32.图6是一实施例涉及的显示装置的第二显示区域中的一个像素的平面图。

33.图7是沿着图6的vii

‑

vii'线截取的剖视图。

34.图8至图12是按照各个层来示出图6的显示装置的一个像素的平面图。

35.图13是一实施例涉及的显示装置的一个像素的电路图。

36.图14是用于说明基于一实施例涉及的显示装置的透明导电体的厚度的透过率改

善效果的图表。

37.符号说明:

38.110:基板;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

130:半导体层;

39.141:第一绝缘层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

142:第二绝缘层;

40.160:第三绝缘层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

180:平坦化层;

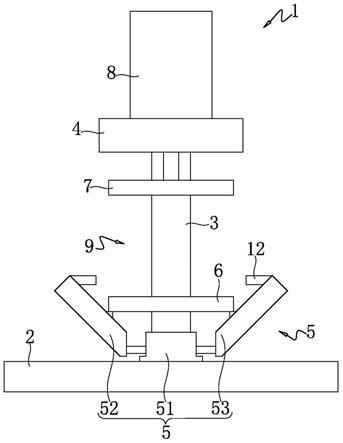

41.151:扫描线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

152:前级扫描线;

42.153:发光控制线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

154:旁路控制线;

43.155:第一栅电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

126:维持电极;

44.127、128:初始化电压线;

ꢀꢀꢀ

171:数据线;

45.172:驱动电压线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

173:第一连接电极;

46.174:第二连接电极;

ꢀꢀꢀꢀꢀꢀꢀꢀ

175:阳极连接电极;

47.176:第三连接电极;

ꢀꢀꢀꢀꢀꢀꢀꢀ

191:像素电极。

具体实施方式

48.以下,参照附图,详细说明本发明的各实施例,以便本领域技术人员能够容易实施。本发明可以由各种不同的形态实现,并不限于在此说明的各实施例。

49.为了明确说明本发明,省略了与说明无关的部分,并在整个说明书中对相同或者类似的构成要素赋予相同的符号。

50.此外,图示的各构成的大小以及厚度为了便于说明而任意示出,本发明并不一定限于图示的情况。在附图中,为了明确表示各层以及区域,有所夸张地示出了厚度。另外,在附图中,为了便于说明,有所夸张地示出了部分层和区域的厚度。

51.此外,层、膜、区域、板等部分位于其他部分上或上方时,不仅包括直接位于其他部分上的情况,还包括其间包括其他部分的情况。相反,某一部分直接位于其他部分上时,是指其间不存在其他部分。另外,位于作为基准的部分上或上方是指位于作为基准的部分的下或下方,并不一定指在重力方向侧位于上或上方的情况。

52.此外,在整个说明书中,某一部分包括某一构成要素时,在没有特别相反的记载的情况下,并不是排除包括其他构成要素,而是指还可以包括其他构成要素。

53.此外,在整个说明书中,“平面上”是指从上观察对象部分的情况,“截面上”是指从侧方观察垂直截取对象部分的截面的情况。

54.在附图中,用于表示方向的符号x是第一方向,y是与第一方向垂直的第二方向,并且z是与第一方向和第二方向垂直的第三方向。

55.以下,参照图1至图2来说明实施例涉及的显示装置。在此,显示装置可为发光显示装置。

56.图1是一实施例涉及的显示装置的示意性平面图,图2是一实施例涉及的显示装置的示意性剖视图。

57.参照图1和图2,显示装置1包括显示面板10、包括与显示面板10相接的柔性印刷电路膜20及集成电路芯片30等的驱动装置以及光学元件40。

58.显示面板10可包括显示图像的显示区域(display area)da以及配置成包围显示区域da且不显示图像的非显示区域(non

‑

display area)na。显示区域da可对应于画面

(screen)。

59.在显示区域da设置有多个像素px。在此,像素px是显示图像的最小单位,各个像素px可根据输入图像信号而以多种亮度显示特定颜色(例如,红色、绿色和蓝色中的任一种颜色)。

60.在非显示区域na配置有用于生成和/或传递施加到显示区域da的各种信号的电路和/或信号线。在各个像素px连接了栅极线、数据线、驱动电压线等信号线,像素px可从这些信号线接收栅极信号、数据电压、驱动电压等。

61.显示区域da包括第一显示区域da1和第二显示区域da2。第二显示区域da2具有比第一显示区域da1高的透过率,以便可执行除了显示图像的固有功能以外的其他功能。在此,透过率意味着在第三方向z上透过显示面板10的光的透过率。光可为可见光和/或可见光以外的波长的光(例如,红外光)。第二显示区域da2的像素px的密度(即,每单位面积的像素px的数量)比第一显示区域da1小。

62.在显示区域da,可以多种方式配置第二显示区域da2。在图示的实施例中,第二显示区域da2位于第一显示区域da1内并且被第一显示区域da1包围。

63.第二显示区域da2可位于与非显示区域na相接的位置处。第二显示区域da2可在显示区域da的上端处位于左侧、右侧和/或中央。第二显示区域da2可被设置为分离成两个以上的区域。第二显示区域da2可完全横穿显示区域da的上端而位于沿着第一方向x的位置处。第二显示区域da2可横穿显示区域da的左侧端和/或右侧端而位于沿着第二方向y的位置处。第二显示区域da2可具有四边形、三角形等多边形、圆形、椭圆形等各种形状。

64.在显示面板10的非显示区域na可设置有生成和/或处理用于驱动显示面板10的各种信号的驱动装置(driving unit)。驱动装置可包括向数据线施加数据电压的数据驱动部(data driver)、向栅极线施加栅极信号的栅极驱动部(gate driver)、控制数据驱动部和栅极驱动部的信号控制部(signal controller)等。

65.驱动装置可被集成到显示面板10,并且可位于显示区域da的左右两侧或一侧。数据驱动部和信号控制部可以集成电路芯片(也称为驱动ic芯片)30的方式被提供,并且集成电路芯片30可被安装于柔性印刷电路膜20而与显示面板10电连接。集成电路芯片30也可被安装于显示面板10的非显示区域na。

66.显示面板10可包括基板110,并且在基板110上可形成有多个像素px。基板110可包括第一显示区域da1和第二显示区域da2。

67.显示面板10可包括整体地覆盖多个像素px的封装层ec。封装层ec可对第一显示区域da1和第二显示区域da2进行密封以阻挡水分或氧渗透到显示面板10的内部。在封装层ec为基板形态的情况下,基板110和封装层ec可通过密封部件被接合。在封装层ec上可设置有用于减少外光反射的反射防止层ar,并且反射防止层ar可包括偏振层和/或相位延迟层。

68.在显示面板10的背面可设置有光学元件40。光学元件40可为传感器、相机、闪光灯等。在光学元件40为传感器的情况下,光学元件40可为接近式传感器或照度传感器。光学元件40所利用的波长的光可因第二显示区域da2而以更高的透过率通过显示面板10。在显示面板10的背面除了光学元件40以外还可设置有各种电子装置。

69.光学元件40可朝向位于显示面板10的前表面的物体ob侧射出预定波长范围的光l或者可接收从物体ob反射的光l的输入。这种预定波长范围的光l可为能够在光学元件40中

处理的波长的光,可为可见光和/或红外光。预定波长的光主要可通过位于第二显示区域da2的透过区域。在光学元件40使用红外光的情况下,预定波长的光可具有约900nm至1000nm的波长区域。光学元件40也可接收照射在显示面板10的前表面的预定波长的光的输入。光学元件40可与第二显示区域da2的整体对应地配置,也可仅与第二显示区域da2的一部分对应地配置。在第二显示区域da2可配置有多个光学元件40。

70.以下,结合图1和图2,参照图3至图5,说明一实施例涉及的显示装置的第一显示区域da1和第二显示区域da2。

71.图3是关于一实施例涉及的显示装置的第一显示区域和第二显示区域的一部分的示意性配置图,图4是关于一实施例涉及的显示装置的第二显示区域的一部分的剖视图,并且图5是关于一实施例涉及的显示装置的第一显示区域的一部分的剖视图。

72.参照图3,第一显示区域da1包括多个第一像素区域pa1,并且第二显示区域da2包括多个第二像素区域pa2、多个透过区域ta以及位于多个第二像素区域pa2与多个透过区域ta之间的多个布线区域wa。多个布线区域wa分别被设置成包围多个透过区域ta。

73.一个第一像素区域pa1的大小和一个第二像素区域pa2的大小可相同,也可不同。

74.在第一显示区域da1,第一像素区域pa1可在作为彼此不同的方向的第一方向x和第二方向y上被排列成行和列。

75.在第二显示区域da2,第二像素区域pa2和透过区域ta可被排列成行和列。第二像素区域pa2和透过区域ta可被排列成棋盘(checkerboard)图案,以便能够使第二像素区域pa2和透过区域ta均匀地混合存在。即,在一个第二像素区域pa2的周边,透过区域ta可沿着第一方向x和第二方向y与其相邻;在一个透过区域ta的周边,第二像素区域pa2可沿着第一方向x和第二方向y与其相邻。在第一方向x和/或第二方向y上,可交替地排列一个以上的第二像素区域pa2和一个以上的透过区域ta。此外,根据实施例,在第二显示区域da2,也可仅连续地排列第二像素区域pa2而不存在透过区域ta。

76.各个透过区域ta的大小可彼此相同,也可不同。可以各种方式变更第二像素区域pa2和透过区域ta的配置和大小。

77.各个像素区域pa1、pa2可包括至少一个像素px。像素px可包括像素电路和发光部。像素电路是用于驱动如发光二极管led的发光元件(light emitting element)的电路,可包括晶体管(transistor)、电容器(capacitor)等。发光部是射出由发光元件发出的光的区域。

78.参照图4和图5,显示装置1在基板110上包括半导体层130、第一绝缘层141、第一栅极导电体、第二绝缘层142、第二栅极导电体、第三绝缘层160、数据导电体、平坦化层180以及像素电极191。图4可为关于图3的第二像素区域pa2的一部分的剖视图,并且图5可为关于图3的第一像素区域pa1的一部分的剖视图。以下,透明导电体意味着使光透过的导电体,并且不透明导电体意味着使大部分光无法透过的导电体。透明导电体可包括如ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)等透明金属物质。此外,在透明导电体包括如铝(al)、铜(cu)等不透明金属的情况下,其也可为以能够使光透过的适当的厚度形成而整体使光透过的导电体。透明导电体可根据所包括的金属物质的种类而形成为单层、双层、三层,并且各层均由透明导电体形成。透明导电体和不透明导电体可根据所包括的物质来决定,在包括相同的物质的情况下,可根据金属层的厚度来

zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)和铜(cu)中的至少一种,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为

89.即,在一实施例涉及的显示装置中,位于第二显示区域da2的第二栅极导电体可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。第二栅极导电体使上部层和下部层包括透明金属(例如,ito)并且使中间层包括厚度为的银(ag),从而可整体成为透明导电体。由此,第二栅极导电体可在第二显示区域da2提高从基板110的下部流入的外部光的透过率。

90.相反,图5所示的第二栅极导电体可为包括钼(mo)、铜(cu)、铝(al)、银(ag)、铬(cr)、钽(ta)或钛(ti)等金属的单层和/或多层结构。

91.在第二绝缘层142上设置有第三绝缘层160以覆盖第二绝缘层142和第二栅极导电体。第三绝缘层160可包括有机绝缘物质。

92.在第三绝缘层160上设置有包括晶体管的源电极70、漏电极71、电容器连接部72以及作为数据线、驱动电压线等的一部分的布线部1172的数据导电体。源电极70可通过第二绝缘层142的开口(opening)连接到半导体层130的源极区域,并且漏电极71可通过第二绝缘层142的开口(opening)连接到半导体层130的漏极区域。此外,源电极70可为源极连接部,漏电极71可为漏极连接部。

93.源电极70和漏电极71可为包括铝(al)、铜(cu)、银(ag)、金(au)、铂(pt)、钯(pd)、镍(ni)、钼(mo)、钨(w)、钛(ti)、铬(cr)或钽(ta)等金属的单层和/或多层结构。具体地,可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。这种源电极70和漏电极71可为使大部分光无法透过的不透明导电体。

94.图4所示的布线部1172可由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)和铜(cu)中的至少一种,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为

95.相反,图5所示的布线部1172与源电极70和漏电极71相同地整体包括不透明导电

体。例如,可为包括铝(al)、铜(cu)、银(ag)、金(au)、铂(pt)、钯(pd)、镍(ni)、钼(mo)、钨(w)、钛(ti)、铬(cr)、钽(ta)等金属的单层和/或多层结构。具体地,可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。

96.即,在一实施例涉及的显示装置中,位于第二显示区域da2的数据导电体的布线部1172可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。数据导电体使上部层和下部层包括透明金属(例如,ito)并且使中间层包括厚度为的银(ag),从而可整体成为透明导电体。由此,图4的布线部1172可在第二显示区域da2提高从基板110的下部流入的外部光的透过率。

97.与位于第一显示区域da1的数据导电体相同地,位于第二显示区域da2的数据导电体的源电极70和漏电极71可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。在包括这种三层结构的数据导电体的源电极70和漏电极71中,上部层和下部层可为透明的,但是可基于中间层的铝(al)的厚度等而整体为不透明。

98.虽然数据导电体的源电极70和漏电极71可比布线部1172厚并且可包括不透明导电体,但是当其为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构时,可维持适当的厚度,从而可与半导体层130稳定地连接。

99.栅电极1155、源电极70和漏电极71与半导体层130一同构成晶体管。第一电极1156和第二电极1125与它们之间的第二绝缘层142一同构成电容器cp。构成像素电路的晶体管和电容器可位于第二像素区域pa2,并且不位于透过区域ta。

100.在第三绝缘层160和数据导电体上设置有平坦化层180。平坦化层180可包括有机物质。为了提高待形成在平坦化层180上的发光元件的发光效率,平坦化层180可消除高低差而实现平坦化。平坦化层180可在第二像素区域pa2覆盖第三绝缘层160和数据导电体。

101.在平坦化层180上设置有像素电极191。像素电极191相当于发光二极管的阳极(anode)。像素电极191可与晶体管的漏电极71电连接以接收电压的施加。

102.图4所示的像素电极191可由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)和铜(cu)中的至少一种,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为由此,图4的像素电极191可在第二显示区域da2提高从基板110的下部流入的外部光的透过率。

103.相反,图5所示的像素电极191也可由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag),并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,

inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。位于第一显示区域da1的像素电极191的中间层的厚度可比位于第二显示区域da2的像素电极191厚。由此,在第一显示区域da1中光的透过率可比第二显示区域da2低。

104.即,在一实施例涉及的显示装置中,位于第二显示区域da2的像素电极191可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。位于第一显示区域da1的像素电极191也可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。然而,位于第二显示区域da2的像素电极191的银(ag)的厚度可比位于第一显示区域da1的像素电极191的银(ag)的厚度薄。在此,位于第二显示区域da2的像素电极191的适当的厚度可为

105.以下,参照图6至图13来说明一实施例涉及的显示装置的第二显示区域的一个像素。

106.图6是一实施例涉及的显示装置的第二显示区域中的一个像素的平面图,图7是沿着图6的vii

‑

vii'线截取的剖视图,图8至图12是按照各个层示出图6的显示装置的一个像素的平面图,并且图13是一实施例涉及的显示装置的一个像素的电路图。

107.首先,参照图6,图6所示的第二显示区域da2中的一个像素px包括第一子像素px1、第二子像素px2和第三子像素px3。虽然第一子像素px1、第二子像素px2和第三子像素px3可分别包括所有电极,并且所有电极可执行相同的作用,但是一部分电极的位置和形状可不同。在图6所示的像素px的周边可设置有透过区域ta,并且还可设置有与图6所示的像素px相同或不同的像素。

108.一实施例涉及的显示装置1主要包括沿着第一方向x延伸并且分别传递扫描信号sn、前级扫描信号sn

‑

1、发光控制信号em、旁路(bypass)信号gb和初始化电压vint的扫描线151、前级扫描线152、发光控制线153、旁路控制线154和初始化电压线127、128。虽然在图6仅示出了一部分,但是扫描线151、前级扫描线152、发光控制线153、旁路控制线154和初始化电压线127、128中的至少一个可被设置成在第一方向x上延伸得很长。

109.显示装置1包括沿着与第一方向x交叉的第二方向y延伸且分别传递数据电压dm和驱动电压elvdd的数据线171和驱动电压线172。虽然在图6仅示出了一部分,但是数据线171和驱动电压线172中的至少一个可被设置成在第二方向y上延伸得很长。

110.在本实施例中,扫描线151、前级扫描线152、发光控制线153、旁路控制线154、初始化电压线127、128、数据线171和驱动电压线172可整体地或者部分地包括透明导电体。由此,本实施例涉及的显示装置可提高外部光的透过率,详细内容将后述。

111.显示装置1包括驱动晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7、维持电容器cst和发光二极管led。

112.在包括如聚酰亚胺(polyimide)、聚酰胺(polyamide)这样的聚合物或玻璃等绝缘物质的基板110上,设置有多个晶体管t1、t2、t3、t4、t5、t6、t7的半导体层130。在图8示出了半导体层130。

113.驱动晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6和第七晶体管t7各自的沟道(channel)位于延伸得很长的半导体层130内。不仅如此,多个晶体管t1、t2、t3、t4、t5、t6、t7的第一电极和第二电极中的至少一部分位于半导体

层130。半导体层130可弯折成各种形状来形成。半导体层130可包括如多晶硅这样的多晶半导体或氧化物半导体。

114.半导体层130包括用n型杂质或p型杂质进行了沟道掺杂的沟道以及位于沟道的两侧且掺杂浓度比掺杂在沟道中的杂质高的第一掺杂区域和第二掺杂区域。第一掺杂区域和第二掺杂区域分别对应于多个晶体管t1、t2、t3、t4、t5、t6、t7的第一电极和第二电极。当第一掺杂区域和第二掺杂区域中的一个为源极区域时,剩余的一个可为漏极区域。此外,在半导体层130中彼此不同的晶体管的第一电极与第二电极之间的区域也可被掺杂以使得两个晶体管彼此电连接。

115.多个晶体管t1、t2、t3、t4、t5、t6、t7的各自的沟道与各个晶体管t1、t2、t3、t4、t5、t6、t7的栅电极重叠,并且位于各个晶体管t1、t2、t3、t4、t5、t6、t7的第一电极与第二电极之间。多个晶体管t1、t2、t3、t4、t5、t6、t7可具有实质上相同的叠层结构。以下,主要对驱动晶体管t1进行详细说明,对剩余的晶体管t2、t3、t4、t5、t6、t7进行简单说明。

116.驱动晶体管t1包括沟道、第一栅电极155、第一电极s1和第二电极d1。驱动晶体管t1的第一电极s1和第二电极d1分别位于沟道的两侧。沟道被弯折,这是为了在有限的区域内将沟道的长度形成得较长。沟道的形状并不限于所示的ω形,可为u形、s形等各种形状。

117.在基板110和半导体层130上设置有第一绝缘层141。

118.在第一绝缘层141上设置有包括多个晶体管的栅电极、扫描线151、前级扫描线152、发光控制线153和旁路控制线154的第一栅极导电体。在图9示出了第一栅极导电体。

119.驱动晶体管t1的第一栅电极155在平面上与沟道重叠。

120.第二晶体管t2的栅电极可为半导体层130与扫描线151重叠的部分的一部分。

121.第三晶体管t3的栅电极可为扫描线151的一部分,并且可由彼此相邻的两个晶体管构成。在图6的像素px内,以第三晶体管t3的半导体层130被弯折的部分为基准,在左侧和下侧示出了t3的符号。这两个部分可分别为第三晶体管t3的栅电极。

122.第四晶体管t4的栅电极可为前级扫描线152的一部分,并且可由彼此相邻的两个晶体管构成。在图6的像素px内,以第四晶体管t4的半导体层130被弯折的部分为基准,在下侧示出了两个t4的符号。这两个部分可分别为第四晶体管t4的栅电极。如上所述的结构可被称为双栅极(dual gate)结构,可阻断漏电流的流动。

123.第五晶体管t5的栅电极可为半导体层130与发光控制线153重叠的部分的一部分。

124.第六晶体管t6的栅电极可为半导体层130与发光控制线153重叠的部分的一部分。

125.第七晶体管t7的栅电极可为半导体层130与旁路控制线154重叠的部分的一部分。

126.在第一栅极导电体上设置有第二绝缘层142。

127.在第二绝缘层142上设置有包括维持电极126、初始化电压线127、128、岛型电极123的第二栅极导电体。在图10示出了第二栅极导电体。

128.维持电极126可与第一栅电极155重叠,并且可彼此被连接并延伸成位于第一子像素px1、第二子像素px2和第三子像素px3处。维持电极126包括开口部41。维持电极126与第一栅电极155在平面上重叠,且第二绝缘层142位于其间,由此构成维持电容器cst。维持电极126为维持电容器cst的第一电极,并且第一栅电极155构成第二电极。

129.维持电极126通过开口56与驱动电压线172电连接。由此,维持电容器cst可存储与通过驱动电压线172传递到维持电极126的驱动电压elvdd和第一栅电极155的栅极电压vg

之间的差对应的电荷。

130.初始化电压线127、128可向第四晶体管t4和第七晶体管t7传递初始化电压vint。初始化电压线127、128可包括向第四晶体管t4的第一电极s4传递初始化电压vint的第一初始化电压线127和向第七晶体管t7的第二电极d7传递初始化电压vint的第二初始化电压线128。向第一初始化电压线127和第二初始化电压线128可分别施加不同的初始化电压vint,也可分别施加相同的初始化电压vint。此时,第一初始化电压线127和第二初始化电压线128可在第一方向x上延伸并且彼此被连接。

131.岛型电极123与维持电极126及初始化电压线127、128间隔开,被设置成岛形状。岛型电极123通过开口50与驱动电压线172电连接。由此,岛型电极123可从驱动电压线172接收驱动电压elvdd的传递。

132.在第二绝缘层142上设置有第三绝缘层160以覆盖第二绝缘层142和第二栅极导电体。第三绝缘层160可包括有机绝缘物质。

133.在第三绝缘层160上设置有包括多个晶体管的第一电极连接部及第二电极连接部、数据线171、驱动电压线172、第一连接电极173、第二连接电极174、第三连接电极176和阳极连接电极175的数据导电体。在图11示出了数据导电体。

134.数据线171包括在第二方向y上延伸的布线部1711和第二晶体管连接部1712。数据线171的布线部1711是指除了与第二晶体管t2的第一电极s2连接的第二晶体管连接部1712以外的部分。第二晶体管连接部1712通过开口53与第二晶体管t2的第一电极s2电连接。

135.数据线171的布线部1711与第二晶体管连接部1712可彼此直接接触,并且可直接被连接以传递数据电压dm。布线部1711和第二晶体管连接部1712可包括不同的物质。

136.数据线171的布线部1711可由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)、铜(cu)等,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为

137.相反,第二晶体管连接部1712包括不透明导电体。例如,可为包括铝(al)、铜(cu)、银(ag)、金(au)、铂(pt)、钯(pd)、镍(ni)、钼(mo)、钨(w)、钛(ti)、铬(cr)、钽(ta)等金属的单层和/或多层结构。具体地,可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。在包括这种三层结构的第二晶体管连接部1712中,上部层和下部层可为透明的,但是可根据中间层的铝(al)的厚度等而整体不透明。

138.即,在一实施例涉及的显示装置中,位于第二显示区域da2的数据线171的布线部1711可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。数据线171的布线部1711使上部层和下部层包括透明金属(例如,ito)并且使中间层包括厚度为的银(ag),从而可整体成为透明导电体。由此,数据线171的布线部1711可在第二显示区域da2

提高从基板110的下部流入的外部光的透过率。

139.与位于第一显示区域da1的数据线相同地,位于第二显示区域da2的第二晶体管连接部1712可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。

140.驱动电压线172包括布线部1721、岛型电极连接部1722、维持电极连接部1723和第五晶体管连接部1724。

141.驱动电压线172的布线部1721为从驱动电压线172中除了岛型电极连接部1722、维持电极连接部1723和第五晶体管连接部1724以外的部分。布线部1721包括在第一方向x上延伸的横向布线部1721a和在第二方向y上延伸的纵向布线部。

142.横向布线部1721a与维持电极连接部1723可彼此直接接触,并且可被直接连接以传递驱动电压elvdd。维持电极连接部1723通过开口56与维持电极126电连接。

143.纵向布线部包括第一纵向布线部1721b和第二纵向布线部1721c。第一纵向布线部1721b可与岛型电极连接部1722彼此接触并且可被电连接。第二纵向布线部1721c可与第五晶体管连接部1724直接接触并且可被直接连接。岛型电极连接部1722通过开口50与岛型电极123电连接。第五晶体管连接部1724通过开口57与第五晶体管t5的第一电极s5电连接。

144.驱动电压线172的布线部1721可由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)、铜(cu)等,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为

145.相反,岛型电极连接部1722、维持电极连接部1723和第五晶体管连接部1724包括不透明导电体。例如,可为包括铝(al)、铜(cu)、银(ag)、金(au)、铂(pt)、钯(pd)、镍(ni)、钼(mo)、钨(w)、钛(ti)、铬(cr)、钽(ta)等金属的单层和/或多层结构。具体地,可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。

146.即,在一实施例涉及的显示装置中,位于第二显示区域da2的驱动电压线172的布线部1721可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。驱动电压线172的布线部1721使上部层和下部层包括透明金属(例如,ito)并且使中间层包括厚度为的银(ag),从而可整体成为透明导电体。由此,驱动电压线172的布线部1721可提高从基板110的下部流入的外部光的透过率。

147.与位于第一显示区域da1的驱动电压线相同地,位于第二显示区域da2的岛型电极连接部1722、维持电极连接部1723和第五晶体管连接部1724可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。在包括这种三层结构的岛型电极连接部1722、维持电极连接部1723和第五晶体管连接部1724中,虽然上部层和下部层可为透明的,但是可根据中间层的铝(al)的厚度等而整体不透明。

tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)、铜(cu)等,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为由此,第二连接电极174的布线部1741可提高从基板110的下部流入的外部光的透过率。

157.第三连接电极176包括布线部1761、第二初始化连接部1762和第七晶体管连接部1763。第三连接电极176的布线部1761是除了第二初始化连接部1762和第七晶体管连接部1763以外的部分。布线部1761可与第二初始化连接部1762和第七晶体管连接部1763直接接触并且可被电连接。

158.第二初始化连接部1762通过开口59与第二初始化电压线128连接,并且第七晶体管连接部1763通过开口60与第七晶体管t7的第二电极d7连接。由此,第三连接电极176可连接第七晶体管t7与第二初始化电压线128。

159.第二初始化连接部1762和第七晶体管连接部1763包括不透明导电体。例如,可包括铝(al)、铜(cu)、银(ag)、金(au)、铂(pt)、钯(pd)、镍(ni)、钼(mo)、钨(w)、钛(ti)、铬(cr)、钽(ta)等金属。具体地,可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。

160.相反,第三连接电极176的布线部1761可由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)、铜(cu)等,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为由此,第三连接电极176的布线部1761可提高从基板110的下部流入的外部光的透过率。

161.阳极连接电极175包括第六晶体管连接部1752。第六晶体管连接部1752可通过开口58与第六晶体管t6的第二电极d6连接。此外,阳极连接电极175可通过开口81与像素电极191连接。在阳极连接电极175中与像素电极191连接的开口81可与第六晶体管连接部1752重叠,也可设置成不重叠。

162.阳极连接电极175可在各个子像素px1、px2、px3中以不同的形状实现。如图6所示,在第一子像素px1中可实现为岛形状,在第二子像素px2中可实现为朝向开口81的下侧延伸得较长以设置开口58的长杆形状,并且在第三子像素px3中可实现为相邻设置开口81和开口58且朝向开口58的上侧延伸得较长的长杆形状。

163.包围开口58的第六晶体管连接部1752包括不透明导电体。例如,可包括铝(al)、铜(cu)、银(ag)、金(au)、铂(pt)、钯(pd)、镍(ni)、钼(mo)、钨(w)、钛(ti)、铬(cr)、钽(ta)等金

属。具体地,可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。

164.相反,阳极连接电极175中除了第六晶体管连接部1752以外的杆形状部分可由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)、铜(cu)等,并且下部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为由此,阳极连接电极175可提高从基板110的下部流入的外部光的透过率。

165.即,在一实施例涉及的显示装置中,位于第二显示区域da2的各个连接电极173、174、175、176的布线部可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。各个连接电极173、174、175、176的布线部使上部层和下部层包括透明金属(例如,ito)并且使中间层包括厚度为以下的银(ag),从而可整体成为透明导电体。

166.位于第二显示区域da2的各个连接部可为上部层由钛(ti)构成、中间层由铝(al)构成并且下部层由钛(ti)构成的三层结构。

167.在数据导电体上设置有平坦化层180。

168.在平坦化层180上设置有像素电极191。在图12示出了像素电极191。

169.像素电极191可为大致菱形形状。此外,在各个子像素px1、px2、px3中,可根据与第六晶体管t6连接的开口81的位置而以不同的形状实现各个子像素。例如,在第一子像素px1中,开口81位于菱形的下方顶点的一侧,从而可为在下方顶点处部分扩张的多边形。在第二子像素px2中,开口81在菱形的下方顶点的下方被隔开设置,从而可为在下方顶点处包括沿着第二方向y延伸的长矩形的多边形。在第三子像素px3中,开口81被设置成与菱形的下方顶点的下方相邻,从而可为在下方顶点处包括沿着第二方向y部分延伸的四边形的多边形。

170.像素电极191可通过平坦化层180的开口81而与阳极连接电极175电连接。由此,像素电极191可通过阳极连接电极175而与第六晶体管t6连接并且可接收驱动晶体管t1的输出电流。

171.像素电极191可整体由包括透明导电体的三层结构构成。上部层可包括ito(indium tin oxide,铟锡氧化物,insno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种,中间层可包括银(ag)、铝(al)、铜(cu)等,并且下部层可包括ito(indium tin oxide,铟锡氧化物,inzno)、izo(indium zinc oxide,铟锌氧化物,inzno)、igzo(indium gallium zinc oxide,铟镓锌氧化物,ingazno)、azo(al

‑

zinc oxide,铝锌氧化物,alzno)、gzo(gallium

‑

zinc oxide,镓锌氧化物,gazno)和itzo

(indium tin zinc oxide,铟锡锌氧化物,insnzno)中的至少一种。中间层的厚度可在以下,并且可使外部光透过的最佳的厚度可为由此,像素电极191可提高从基板110的下部流入的外部光的透过率。

172.即,在一实施例涉及的显示装置中,位于第二显示区域da2的像素电极191可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。位于第一显示区域da1的像素电极191也可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。然而,位于第二显示区域da2的像素电极191的银(ag)的厚度可比位于第一显示区域da1的像素电极191的银(ag)的厚度薄。在此,位于第二显示区域da2的像素电极191的适当的厚度可为

173.根据实施例,像素电极191可包括不透明的部分。不透明的像素电极191可为上部层包括ito、中间层包括银(ag)并且下部层包括ito的三层结构。第二显示区域da2的像素电极191的中间层的厚度可与图5所示的位于第一显示区域da1的像素电极191的中间层的厚度相同。在第二显示区域da2,即使像素电极191的厚度与第一显示区域da1中的像素电极191的厚度相同,由于像素电极191可通过平坦化层180的开口81与透明的阳极连接电极175及透明的第六晶体管t6的第二电极d6连接,因此可提高从基板110的下部流入的外部光的透过率。

174.在像素电极191上可设置有分隔壁(未图示)。在分隔壁可形成有开口,并且可通过开口与像素电极191重叠。在分隔壁的开口可设置有发光层。图12所示的位于像素电极191内的菱形形状可为发光层360。在发光层360上可设置有公共电极(未图示)。像素电极191、发光层360和公共电极可构成发光二极管led。

175.参照图13,多个信号线127、151、152、153、154、171、172、741与一个像素px连接。多个信号线包括初始化电压线127、扫描线151、前级扫描线152、发光控制线153、旁路控制线154、数据线171、驱动电压线172和公共电压线741。

176.扫描线151与栅极驱动部(未图示)连接,从而将扫描信号sn传递到第二晶体管t2和第三晶体管t3。前级扫描线152与栅极驱动部连接,从而将施加到位于前级的像素px的前级扫描信号sn

‑

1传递到第四晶体管t4。发光控制线153与发光控制部(未图示)连接,并且将控制使发光二极管led发光的时间的发光控制信号em传递到第五晶体管t5和第六晶体管t6。旁路控制线154将旁路信号gb传递到第七晶体管t7。

177.数据线171是传递由数据驱动部(未图示)生成的数据电压dm的布线,根据数据电压dm,发光二极管led发光的亮度会变化。驱动电压线172施加驱动电压elvdd,初始化电压线127传递使驱动晶体管t1初始化的初始化电压vint,并且公共电压线741施加公共电压elvss。分别向驱动电压线172、初始化电压线127和公共电压线741施加一定的电压。

178.驱动晶体管t1是根据所施加的数据电压dm来调节输出的电流的大小的晶体管。驱动晶体管t1的第一电极s1经由第五晶体管t5而与驱动电压线172连接。此外,驱动晶体管t1的第一电极s1还与第二晶体管t2的第二电极d2连接,从而还接收数据电压dm。驱动晶体管t1的第二电极d1经由第六晶体管t6而与发光二极管led的阳极(anode)连接。另一方面,栅电极g1与维持电容器cst的一电极(第二维持电极e2)连接。由此,栅电极g1的电压根据存储在维持电容器cst中的电压而变化,由此驱动晶体管t1输出的驱动电流i

d

会变化。

179.第二晶体管t2是将数据电压dm接收到像素px内的晶体管。栅电极g2与扫描线151

连接,并且第一电极s2与数据线171连接。第二晶体管t2的第二电极d2与驱动晶体管t1的第一电极s1连接。当根据通过扫描线151传递的扫描信号sn,第二晶体管t2被导通时,通过数据线171传递的数据电压dm被传递到驱动晶体管t1的第一电极s1。

180.第三晶体管t3是将数据电压dm经过驱动晶体管t1发生了变化的补偿电压(dm vth的电压)传递到维持电容器cst的第二维持电极e2的晶体管。栅电极g3与扫描线151连接,并且第一电极s3与驱动晶体管t1的第二电极d1连接。第三晶体管t3的第二电极d3与维持电容器cst的第二维持电极e2和驱动晶体管t1的栅电极g1连接。第三晶体管t3根据通过扫描线151接收到的扫描信号sn而被导通,从而连接驱动晶体管t1的栅电极g1与第二电极d1,并且还连接驱动晶体管t1的第二电极d1与维持电容器cst的第二维持电极e2。

181.第四晶体管t4使驱动晶体管t1的栅电极g1和维持电容器cst的第二维持电极e2初始化。栅电极g4与前级扫描线152连接,并且第一电极s4与初始化电压线127连接。第四晶体管t4的第二电极d4与维持电容器cst的第二维持电极e2和驱动晶体管t1的栅电极g1连接。

182.第五晶体管t5将驱动电压elvdd传递到驱动晶体管t1。栅电极g5与发光控制线153连接,并且第一电极s5与驱动电压线172连接。第五晶体管t5的第二电极d5与驱动晶体管t1的第一电极s1连接。

183.第六晶体管t6将从驱动晶体管t1输出的驱动电流i

d

传递到发光二极管led。栅电极g6与发光控制线153连接,并且第一电极s6与驱动晶体管t1的第二电极d1连接。第六晶体管t6的第二电极d6与发光二极管led的阳极(anode)连接。

184.第五晶体管t5和第六晶体管t6根据通过发光控制线153接收到的发光控制信号em而被同时导通,并且当通过第五晶体管t5将驱动电压elvdd施加到驱动晶体管t1的第一电极s1时,根据驱动晶体管t1的栅电极g1的电压,驱动晶体管t1输出驱动电流i

d

。输出的驱动电流i

d

通过第六晶体管t6而被传递到发光二极管led。随着电流i

led

流过发光二极管led,发光二极管led发射光。

185.第七晶体管t7使发光二极管led的阳极初始化。栅电极g7与旁路控制线154连接,第一电极s7与发光二极管led的阳极(anode)连接,并且第二电极d7与初始化电压线127连接。当第七晶体管t7根据旁路信号gb而被导通时,初始化电压vint被施加到发光二极管led的阳极,从而进行初始化。

186.维持电容器cst的第一维持电极e1与驱动电压线172连接,第二维持电极e2与驱动晶体管t1的栅电极g1、第三晶体管t3的第二电极d3和第四晶体管t4的第二电极d4连接。其结果,第二维持电极e2决定驱动晶体管t1的栅电极g1的电压,并且通过第三晶体管t3的第二电极d3接收数据电压dm、或者通过第四晶体管t4的第二电极d4接收初始化电压vint。

187.另一方面,发光二极管led的阳极(anode)可与第六晶体管t6的第二电极d6和第七晶体管t7的第一电极s7连接,并且阴极(cathode)与传递公共电压elvss的公共电压线741连接。

188.虽然在图13的实施例中像素电路包括七个晶体管t1至t7和一个电容器cst,但是并不限于此,可以各种方式变更晶体管的数量和电容器的数量以及它们的连接。

189.以下,参照图14说明在一实施例涉及的显示装置中透过率的改善效果。

190.图14是用于说明基于一实施例涉及的显示装置的透明导电体的厚度的透过率改善效果的图表。

191.图14示出了对上部层由ito构成、中间层由银(ag)构成并且下部层由ito构成的透明导电体进行热处理而基于波长的透过率。在本实施例中,这种透明导电体可为前述的第一栅极导电体、第二栅极导电体、数据导电体的布线部和像素电极。

192.下述表1示出了基于波长的透过率。

193.表1:

[0194][0195]

结合上述表1参照图14可确认出,在透明导电体中平均透过率和各波长下的透过率随着银(ag)的厚度变薄而变大。

[0196]

由此,在一实施例中,通过第一栅极导电体、第二栅极导电体、数据导电体的布线部和像素电极包括透明导电体,可改善透过率。

[0197]

此外,在包括透明导电体的一实施例涉及的显示装置中包括与厚度在以下的情况相当的银(ag),从而可确保低的电阻,并且可防止信号延迟。

[0198]

以上,详细说明了本发明的实施例,但是本发明的权利范围并不限于此,本领域技术人员利用权利要求书中定义的本发明的基本概念进行的各种变形以及改良形态均属于本发明的权利范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。