1.本发明涉及一种像素结构,更特别涉及一种即使发生过曝光也能够输出实际曝光信息的像素电路及包含该像素电路的像素阵列及其运行方法。

背景技术:

2.像素电路是使用光二极管在曝光期间接收入射光,以输出与入射光强度相关的电压值来表示环境光强度。然而,当环境光过强而使得像素电路累积电荷在曝光期间结束前即已到达全井容量(full well capacity,fwc)时,像素输出则无法反映真实的入射光强度。

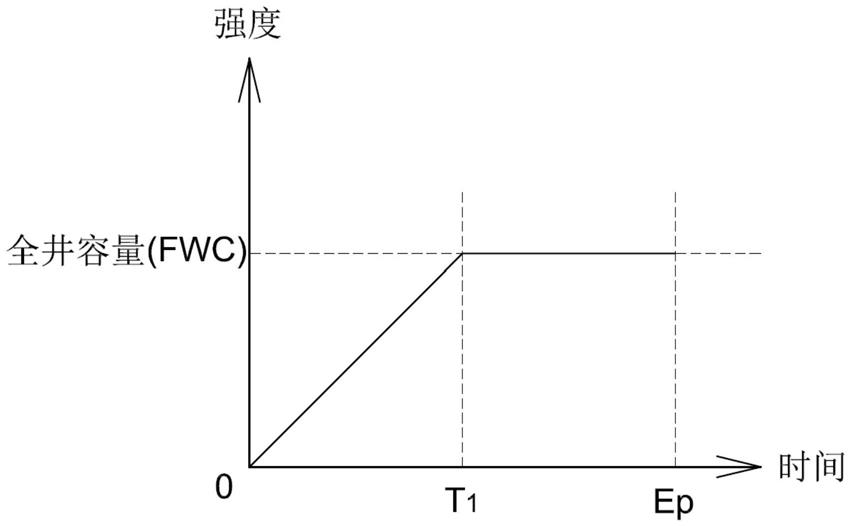

3.例如参照图1所示,在时间t1之前,像素电路正常的累积光能量。当像素电路在时间t1时到达全井容量而发生饱和时,在时间t1之后的光能量无法继续被像素电路累积。此时,处理器仅能接收模拟数字转换器输出的满阶数字值,并无法得知真实的入射光强度。

4.有鉴于此,本发明另提供一种即使发生过曝光也能够输出实际曝光信息的像素电路及包含该像素电路的像素阵列及其运行方法。

技术实现要素:

5.本发明提供一种包含曝光电路及计时电路的像素电路。所述曝光电路用于输出曝光强度相关的第一电压值而所述计时电路用于输出曝光时间相关的第二电压值。

6.本发明还提供一种包含多个正常像素及假像素的像素阵列。每个正常像素用于输出曝光强度相关的第一电压值及曝光时间相关的第二电压值。假像素用于输出参考电压值。处理器使用所述第一电压值、所述第二电压值及所述参考电压值计算实际光强度。

7.本发明提供一种包含第一电路及第二电路的像素电路。所述第一电路包含光二极管、转移晶体管及第一电容。所述光二极管用于在曝光期间进行曝光。所述第一电容用于通过所述转移晶体管储存所述光二极管产生的电荷以产生第一电压值。所述二电路包含控制电路及计时电路。所述控制电路连接所述第一电容,用于在所述转移晶体管被导通以将所述光二极管产生的所述电荷转移至所述第一电容之前,根据所述第一电容上的电压降产生控制信号。所述计时电路连接所述控制电路,用于根据所述控制信号决定所述计时电路内的第二电容的放电时间,以产生第二电压值。所述第一电压值与光强度相关,而所述第二电压值与溢位时间相关。

8.本发明还提供一种包含多个正常像素及至少一个假像素的像素阵列。所述多个正常像素的每一者包含第一电路及第二电路。所述第一电路包含光二极管、转移晶体管及第一电容。所述光二极管用于在曝光期间进行曝光。所述第一电容用于通过所述转移晶体管储存所述光二极管产生的电荷以产生第一电压值。所述二电路包含控制电路及计时电路。所述控制电路连接所述第一电容,用于在所述转移晶体管被导通以将所述光二极管产生的所述电荷转移至所述第一电容之前,根据所述第一电容上的电压降产生控制信号。所述计时电路连接所述控制电路,用于根据所述控制信号决定所述计时电路内的第二电容的放电

时间,以产生第二电压值。所述至少一个假像素与所述正常像素具有相同电路结构,且所述至少一个假像素的第二电容用于产生参考电压值。所述第一电压值与所述参考电压值及所述第二电压值的比值的乘积用作为实际强度值。

9.本发明还提供一种像素电路的实际强度值的計算方法,包含下列步骤:重置所述像素电路;在曝光期间内曝光所述像素电路;在所述曝光期间结束前,读取所述像素电路的第一电容产生电压降的时间点及在所述电压降之后的所述第一电容的第一电压;以及基于所述曝光期间与从所述曝光的开始至所述时间点的时间间隔的比值计算所述实际强度值。

10.本发明实施例中,假像素(dummy pixel)又可称为黑像素(dark pixel),其与正常像素具有相同结构并配置于相同像素阵列中。假像素与正常像素的差异在于假像素上覆盖有不透光层,以使得其内的光二极管在曝光期间无法进行曝光。由于假像素的光二极管不会发生溢位,故其第二电容的输出电压值可用作为计算正常像素检测的实际光强度的参考电压值。

11.本发明实施例中,实际光强度是超过模拟数字转换器的分辨率且被处理器用来进行判断,例如动作检测或位移量,的灰阶值。

12.为了让本发明的上述和其他目的、特征和优点能更明显,下文将配合所附图示,详细说明如下。此外,于本发明的说明中,相同的构件以相同的符号表示,于此合先述明。

附图说明

13.图1是当发生过曝光时的电荷累积的示意图;

14.图2是本发明实施例的光传感器计算实际光强度的示意图;

15.图3是本发明实施例的光传感器的方框示意图;

16.图4是本发明实施例的光传感器的另一方框示意图;

17.图5是本发明实施例的像素电路的电路图;

18.图6是图5的像素电路未发生过曝光时的运行时序图;

19.图7是图5的像素电路发生过曝光时的运行时序图;及

20.图8是本发明实施例的像素阵列的运行方法的流程图。

21.附图标记说明

22.300

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光传感器

23.31

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

像素阵列

24.31d

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

假像素

25.31n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

正常像素

26.35

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

读取电路

27.37

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

模拟数字转换器

28.39

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

处理器

具体实施方式

29.本发明的光传感器即使在曝光期间发生过曝光而导致光二极管发生溢位(overflow)时,仍可通过后处理计算像素电路检测的实际光强度。如图2所示,假设曝光期间为ep,当光二极管在曝光期间ep内没有发生溢位时,则电荷累积显示为线段a,像素电路

输出的检测电位表示实际光强度i(本说明有时称为实际强度值);而当光二极管刚好在曝光期间ep结束时累积电荷到全井容量(fwc)时,像素电路依据线段b输出光强度if。然而,如线段c所示,若光二极管在曝光期间ep内(例如在时间tof)即累积电荷至全井容量,则光二极管发生溢位。只要tof小于ep,像素电路只能输出相对光强度if的电位值,同时连接于其后的模拟数字转换器只能输出满阶数字值,例如255,但不限于此。本发明中,if等于fwc或为fwc的分数(例如,但不限于,80%

‑

90%)。

30.本发明通过检测溢位时间tof,并将光强度if乘上曝光期间ep与溢位时间tof的比值,则可求得像素电路实际检测的光能量ni=if

×

(ep/tof)。藉此,本发明的光传感器可得到高于满阶数字值的数字值。

31.请参照图3所示,其为本发明实施例的光传感器300的方框示意图。光传感器300包含像素阵列31、时序控制电路33、读取电路35、模拟数字转换器(adc)37以及处理器39。时序控制电路33用以产生控制信号以控制像素阵列31内的开关元件(例如晶体管)以进行扫描及信号输出。读取电路35用于读出像素阵列31的各像素的检测电压值,其中读取电路35例如是采用相关性双重取样(cds)来取样像素资料。模拟数字转换器37用于将读取电路35所读取的模拟信号转换为数字值。读取电路35及模拟数字转换器37的运行为已知且并非本发明的主要目的,故于此不再赘述。

32.像素阵列31包含多个正常像素31n(例如显示为空白矩形)及至少一个假像素31d(例如显示为黑色矩形)。该至少一个假像素31d与正常像素31n具有相同电路结构,差异在于假像素31d上覆盖有不透光层以阻止其内的光二极管接收入射光,其中于正常像素上覆盖不透光层以形成假像素的方式为已知,故于此不再赘述。虽然图3显示单一假像素31d,但本发明并不以此为限。其他实施方式中,像素阵列31可包含多个假像素31d,例如相对每列正常像素31n配置一个假像素。本发明中,假像素31d的配置位置及数目并无特定限制。

33.请参照图4所示,其为本发明实施例的光传感器的另一方框示意图。图4显示像素电路31n/31d通过读取线输出第一电压值v1及第二电压值v2至模拟数字转换器37(为简化图式省略了其间的读取电路35),其中,第一电压值v1为光强度相关的电压值,而第二电压值v2为溢位时间tof(例如参照图2)相关的电压值。一种实施方式中,假像素31d例如输出第二电压值v2至模拟数字转换器37而不输出第一电压值v1。另一种实施方式中,假像素31d输出第一电压值v1及第二电压值v2至模拟数字转换器37以转换为数字值。模拟数字转换器37将第一电压值v1及第二电压值v2转换为数字值后传送至处理器39,但处理器39并不处理或使用假像素31d的第一电压值v1。

34.本发明中,假像素31d输出的第二电压值v2是作为参考电压值。

35.处理器39例如是数字处理器(dsp)或特定应用集成电路(asic),其计算相对每个正常像素31n的第一电压值v1与所述参考电压值及第二电压值v2的比值的乘积以作为实际强度值。藉此,即使在过曝光下,处理器39所产生的图像帧可反映实际环境光强度,而不被模拟数字转换器37的满阶灰阶值所限制。

36.当像素阵列31包含单一假像素31d时,该单一假像素31d产生的所述参考电压值供处理器39计算所有正常像素31n的实际强度值。当像素阵列31包含一行假像素31d且所述一行假像素31d的每一者对应一列正常像素31n时,每一假像素31d产生的所述参考电压值供处理器39计算相对应正常像素列的实际强度值。本发明中,当曝光期间中正常像素31n的光

二极管发生溢位时,实际强度值大于正常像素31n输出的第一电压值v1;然而当曝光期间中光二极管未发生溢位时,由于参考电压值大致等于正常像素31n输出的第二电压值v2,运算后所得到的实际强度值大致等于正常像素31n输出的第一电压值v1。

37.请参照图5所示,其为本发明实施例的像素电路500的电路图。像素电路500显示图3所示的正常像素31n及假像素31d的电路架构。像素电路500包含第一电路c10及第二电路c20,其中第一电路c10用于产生第一电压值v1而第二电路c20用于产生第二电压值v2。

38.正常像素31n中,第一电压值v1及第二电压值v2通过相同的读取线pxo(例如第一读取线)依序被读出;亦即,第一读取线连接至正常像素31n的第一电容c

fd

及第二电容c

time

。本发明中,由于假像素31d的第一电压值v1不被处理器29使用,因此连接至假像素31d的读取线pxo(例如第二读取线)不读出假像素31d的第一电压值v1,其中,第二读取线连接至假像素31d的第二电容c

time

但可连接或不连接至假像素31d的第一电容c

fd

。当第二读取线连接至假像素31d的第一电容c

fd

时,根据时序控制电路33产生的控制信号,其第一电压值v1可不被读出。如前所述,另一种实施方式中假像素31d的第一电压值v1被读出但处理器33不处理第一电压值v1。

39.根据假像素31d及正常像素31n的配置位置,第一读取线与第二读取线可为相同读取线或不同读取线,只要处理器39能够分别收到假像素31d及正常像素31n产生的电压值进行后处理即可。

40.第一电路c10包含光二极管pd、转移晶体管t11、重置晶体管t12、源极随耦晶体管t13、读取晶体管t14以及第一电容c

fd

。光二极管pd用于在曝光期间(参照图6及图7)进行曝光以产生电荷。第一电容c

fd

通过转移晶体管t11储存光二极管pd产生的电荷以产生第一电压值v1通过读取线pxo输出。重置晶体管t12用于重置第一电容c

fd

的电位至重置电位,其接近于v

dd

。读取晶体管t14在读取期间被读取信号rs_fd导通以读出第一电容c

fd

的第一电压值v1。源极随耦晶体管t13用于无损耗的将第一电容c

fd

的电压缓冲至读取电路35。

41.第二电路c20包含控制电路c201及计时电路c202。控制电路c201连接第一电路c10的第一电容c

fd

,用于在第一电路c10的转移晶体管t11被导通以将光二极管pd产生的电荷转移至第一电容c

fd

之前,根据第一电容c

fd

上的电压降产生控制信号vy。图5显示控制信号vy是电压vx经过反向器inv所产生。可以了解的是,反向器inv可包含于控制电路c201或计时电路c202内,并无特定限制。

42.控制电路c201包含晶体管t21、t25及t26形成自动归零(auto zero)电路。当闸极控制信号az为高准位而导通晶体管t21时,其自动归零机制会使得电流i1大致等于电流i2。在闸极控制信号az转为低准位而关闭晶体管t21后,电流i1会随着电压v

fd

的变化而改变,以进而改变电压vx的准位,例如参照图7。

43.计时电路c202连接控制电路c201,用于根据控制信号vy决定计时电路c202内的第二电容c

time

的放电时间,以产生第二电压值v2。计时电路c202包含定电流源i

ct

及控制晶体管t27,该控制晶体管t27连接于定电流源i

ct

及第二电容c

time

之间,用于根据控制信号vy关闭定电流源i

ct

对第二电容c

time

的放电。第二电压值v2的大小反映第二电容c

time

从重置阶段的重置后的放电时间(即图7的tof)。

44.计时电路c202还包含重置晶体管t22、读取晶体管t24及源极随耦晶体管t23。重置晶体管t22用于重置第二电容c

time

的电位至重置电位,其接近于v

dd

。读取晶体管t24用于在

读取期间被读取信号rs_ct导通以读出第二电容c

time

的第二电压值v2。源极随耦晶体管t23用于无损耗的将第二电容c

time

的电压缓冲至读取电路35。

45.请参照图6所示,其显示图5的像素电路500在曝光期间内光二极管pd没有发生溢位时的信号时序图。在曝光开始前,先要对光二极管pd、第一电容c

fd

及第二电容c

time

进行重置。重置程序是通过将重置晶体管t12的闸极电压reset_fd、重置晶体管t22的闸极电压reset_ct、转移晶体管t11的闸极电压tx及晶体管t21的闸极电压az全部设为高准位,其中,闸极控制信号reset_fd、reset_ct、tx及az例如,但不限于,是由时序控制器33所产生。第一电容c

fd

及第二电容c

time

被重置至重置电位,其接近于v

dd

,例如v

dd

‑

0.6伏特,但不限于此。如前所述,在重置期间(例如reset_fd及reset_ct为高准位的期间),控制电路c201通过自动归零运行而使得i1=i2。

46.图6显示的是正常像素31n的运行时序图,假像素31d的时序图与图6类似,其差异在于电压值v

fd

、vx、vy会一直维持在大致相同的准位,这是由于其光二极管pd无法接收入射光,其余则与图6的正常像素31n的运行相类似,故于此不再赘述。假像素31d输出的第二电压v2是用作为参考电压vref。

47.在曝光期间开始后,闸极控制信号reset_fd、reset_ct、tx及az均转至低准位。如果光二极管pd没有发生溢位,第一电容c

fd

的电压值v

fd

在曝光期间不会改变且控制信号vy的准位维持在高准位而使得定电流源i

ct

将第二电容c

time

从重置电位持续放电至曝光期间结束,例如图6所示第二电容c

time

上的电压值v

ct

持续降低直到读取期间中晶体管t22被reset_ct导通。可以了解的是,若第二电容c

time

上的电压值v

ct

在被读取前即已放空,则被读出的电压值v

ct

大致为零。

48.本发明中,由于读取电路35是进行相关性双重取样,重置晶体管t22用于在时间读取期间通过改变闸极控制信号reset_ct为高准位以重置第二电容c

time

的电位,以在时间读取期间中第二电容c

time

的重置前后分别读出电压值v

ct_sig

及v

ct_ref

,其中v

ct_ref

>v

ct_sig

。使用读取信号rs_ct导通读取晶体管t24以将该两电压值v

ct_sig

及v

ct_ref

通过读取线pxo依序输出至读取电路35进行差分运算,该差分运算的结果则作为第二电压v2,亦即,v2=v

ct_ref

‑

v

ct_sig

。

49.转移晶体管t11用于在强度读取期间通过改变闸极控制信号tx为高准位以转移光二极管pd的电荷至第一电容c

fd

,以在强度读取期间中转移电荷至第一电容c

fd

的前后分别读出电压值v

fd_ref

及v

fd_sig

,其中v

fd_ref

>v

fd_sig

。使用读取信号rs_fd导通读取晶体管t14以将该两电压值v

fd_ref

及v

fd_sig

通过读取线pxo依序输出至读取电路35进行差分运算,该差分运算的结果则作为第一电压v1,亦即,v1=v

fd_ref

‑

v

fd_sig

。

50.本发明中,读取信号rs_ct、rs_fd例如,但不限于,由时序控制电路33所产生。时间读取期间早于强度读取期间。

51.请参照图7所示,其显示图5的像素电路500在曝光期间内光二极管pd发生溢位时的信号时序图。曝光期间开始前的运行与图6相同且已经说明于上,故于此不再赘述。图7显示光二极管pd在曝光期间中的时间tof发生溢位。如前所述,重置阶段通过导通晶体管t21使得控制电路c201的电流i1大致等于电流i2。当光二极管pd在曝光期间发生溢位时,会产生一些电荷通过转移晶体管t11泄漏至第一电容c

fd

而使得电压值v

fd

在时间tof下降,此电压下降导致电流i1大于电流i2而在时间tof提升电压值vx。经过反向器后inv,控制信号vy

产生电压降而关闭控制晶体管t27。藉此,控制电路c201通过控制信号vy控制所述控制晶体管t27相对溢位(例如时间点tof)关闭定电流源i

ct

对第二电容c

time

的放电。因此本发明中,第二电容c

time

的放电电位用于表示溢位时间。

52.接着,在时间读取期间,读取电路35通过读取线pox依序读取两电压值v

ct_sig

及v

ct_ref

以计算第二电压值v2。在强度读取期间,读取电路35通过读取线pox依序读取两电压值v

fd_ref

及v

fd_sig

以计算第一电压值v1。时间读取期间及强度读取期间的运行相同于上述图6的说明,故于此不再赘述。

53.由于假像素31d不会发生溢位,故假像素31d不会产生图7的运行。

54.处理器39接收到第一电压值v1、第二电压值v2及参考电压值vref后,则计算v1

×

(vref/v2)以得到实际强度值,其中,若未发生溢位,vref大致等于v2;而当发生溢位时,vref>v2而放大第一电压值v1。亦即,第一电压值v1代表图2的if,第二电压值v2代表图2的tof,且参考电压值代表图2的ep。

55.请参照图8所示,其为本发明实施例的像素阵列的运行方法的流程图,本运行方法适用于图3的光传感器300及图5的像素电路500,并包含下列步骤:重置正常像素31n及假像素31d的第一电容c

fd

及第二电容c

time

至重置电压(步骤s81);结束所述重置并进入曝光期间,以对所述正常像素31n及所述假像素31d的所述第二电容c

time

进行放电(步骤s82);当所述曝光期间中所述正常像素31n的光二极管pd发生溢位而导致所述正常像素31n的所述第一电容c

fd

发生电压降时,停止对所述正常像素31n的所述第二电容c

time

的所述放电(步骤s83);结束所述曝光期间并进入读取期间,以分别读取所述正常像素31n的所述第一电容c

fd

的第一电压v1、读取所述正常像素31n的所述第二电容c

time

的第二电压v2以及读取所述假像素31d的所述第二电容c

time

的参考电压vref(步骤s84);以及计算所述第一电压v1值与所述参考电压值vref及所述第二电压值v2的比值的乘积以作为实际强度值。

56.本运行方法的详细实施方式已说明于上,例如参照图7,故于此不再赘述。此外,图8主要用于说明曝光期间内发生溢位时的实施方式,当曝光期间内未发生溢位时,其运行方式可参照图6所示。

57.如图7所示,光传感器300获取的每个图像帧中,每个像素电路的运行包含三个阶段:重置阶段(即图6至图7的曝光期间之前)、曝光阶段以及读取阶段,其中读取阶段包含时间读取阶段及强度读取阶段以分别读取第二电容c

time

及第一电容c

fd

的电压值。

58.在时间读取阶段中,本运行方法还包含步骤:再次重置正常像素31n的第二电容c

time

;在所述再次重置的前后分别读取第二电容c

time

上的电压值v

ct_sig

及v

ct_ref

;及计算所读取的前后电压值的差值v

ct_ref

‑

v

ct_sig

以作为第二电压值v2。一种实施方式中,可以考虑成第二电路c20输出的第二电压值v2包含电压值v

ct_sig

及v

ct_ref

以供处理器39计算其差值。根据不同配置,处理器39计算v

ct_sig

‑

v

ct_ref

。

59.在强度读取阶段中,本运行方法还包含步骤:导通转移晶体管t11以转移光二极管pd的电荷至正常像素31n的第一电容c

fd

;在转移电荷的前后分别读取第一电容c

fd

上的电压值v

fd_ref

及v

fd_sig

;及计算所读取的前后电压值的差值v

fd_ref

‑

v

fd_sig

以作为第一电压值v1。一种实施方式中,可以考虑成第一电路c10输出的第一电压值v1包含电压值v

fd_ref

及v

fd_sig

以供处理器39计算其差值。根据不同配置,处理器39计算v

fd_sig

‑

v

fd_ref

。

60.假像素31d的运行中,可以进行时间读取阶段而不进行强度读取阶段(即不读取假

像素31d的第一电容c

fd

的电压值),因为假像素31d的第一电容c

fd

的电位不会改变且不包含需要的信息。因此即使进行强度读取阶段,经差分后的数值大致为零。假像素31d的时间读取阶段同样包含步骤:再次重置假像素31d的第二电容c

time

;在所述再次重置的前后分别读取第二电容c

time

上的电压值v

ct_sig

及v

ct_ref

;及计算所读取的前后电压值的差值v

ct_ref

‑

v

ct_sig

以作为参考电压值vref。

61.请参照图2及图5至图7,本发明提供一种像素电路的实际强度值的计算方法。如图5所示,像素电路包含第一电容c

fd

及第二电容c

time

。所述计算方法包含下列步骤:重置像素电路500;在曝光期间ep内曝光所述像素电路500;在所述曝光期间ep结束前,读取所述像素电路500的第一电容c

fd

产生电压降的时间点tof及在所述电压降之后的所述第一电容c

fd

的第一电压v1;以及基于所述曝光期间ep与从所述曝光的开始至所述时间点tof的时间间隔的比值计算实际强度值,例如计算所述第一电压v1与所述曝光期间ep与所述时间间隔的比值的乘积。

62.如前所述,所述第一电压v1例如是所述像素电路500的全井容量(fwc)或该全井容量的分数。所述时间点tof例如是根据从所述第二电容c

time

读取的电压,例如v2,所决定。所述曝光期间ep例如是根据从假像素读取的电容电压(亦即其第二电容)所决定。

63.使用本发明实施例的像素阵列的一个优点是,由于处理器39可计算并求出实际曝光信息,光传感器300的自动曝光程序仅需使用一张图像帧即可快速完成,而不需要如已知的自动曝光程序要经过多张图像帧才能完成。

64.综上所述,已知的光传感器在发生过曝光时,只能输出满阶数字值,而无法反映实际的环境光亮度。因此,本发明另提供一种像素电路(参照图5)及包含该像素电路的像素阵列及其运行方法(参照图8),其通过储存与溢位时间相关的电压值,即使模拟数字转换器输出满阶数字值,仍能够通过数字运算来求出实际环境光强度。

65.虽然本发明已通过前述实例披露,但是其并非用以限定本发明,任何本发明所属技术领域中具有通常知识技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与修改。因此本发明的保护范围当视后附的权利要求所界定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。