加重电路及包含其的发送器

1.相关申请的交叉引用

2.本技术要求于2020年5月21日提交的申请号为10

‑

2020

‑

0060846的韩国专利申请的优先权,其公开内容通过引用整体合并于此。

技术领域

3.各种实施例涉及一种用于在各种类型的集成电路中发送信号(例如,数据)的发送器(transmitter)。

背景技术:

4.在半导体系统中,集成电路芯片在与外围芯片交换信号(例如,数据)的情况下工作。例如,诸如dram和快闪存储器的存储芯片与存储器控制器交换数据。中央处理单元(cpu)也与主板上各种类型的芯片交换数据。此外,信号不仅在芯片之间传输,而且在一个集成电路芯片之内的电路之间传输。发送信号的电路被称为发送器或输出驱动器。

5.随着集成电路的运行速度的增大和由发送器发送的信号的数据速率变高,对执行各种操作以提高由发送器发送的信号的质量(即,信号完整性)的需求不断增长。

技术实现要素:

6.各种实施例针对一种使用简单结构来改善发送器的质量的技术。

7.在一个实施例中,发送器可以包括:加重电路(emphasis circuit),其适于响应于第一数据和被延迟的第二数据来产生第一下拉驱动信号,并且响应于第二数据和被延迟的第一数据来产生第一上拉驱动信号,其中第一数据和第二数据是差分对;相位偏移补偿电路,其适于补偿第一上拉驱动信号与第一下拉驱动信号之间的相位偏移(phase skew),以产生第二上拉驱动信号和第二下拉驱动信号;上拉驱动器,其适于响应于第二上拉驱动信号来上拉驱动输出节点;以及下拉驱动器,其适于响应于第二下拉驱动信号来下拉驱动输出节点。

8.在一个实施例中,发送器可以包括:第一反相器,其适于将被施加有第二数据的第一节点的信号反相以驱动第三节点;第二反相器,其适于将被施加有第一数据的第二节点的信号反相以驱动第四节点;第三反相器,其适于将第三节点的信号反相以驱动第二节点;第四反相器,其适于将第四节点的信号反相以驱动第一节点;第五反相器和第六反相器,其串联耦接以将第三节点的信号驱动到第五节点;第七反相器和第八反相器,其串联耦接以将第四节点的信号驱动到第六节点;第九反相器,其适于将第三节点的信号反相以驱动第六节点;第十反相器,其适于将第四节点的信号反相以驱动第五节点;第十一反相器,其适于通过将第五节点的信号反相来输出上拉驱动信号;第十二反相器,其适于通过将第六节点的信号反相来输出下拉驱动信号;上拉驱动器,其适于响应于上拉驱动信号来上拉驱动输出节点;以及下拉驱动器,其适于响应于下拉驱动信号来下拉驱动输出节点。

9.在一个实施例中,一种加重电路可以包括:第一反相器,其被配置为将第一数据反

相以驱动第一输出节点;第二反相器,其被配置为将第二数据反相以驱动第二输出节点;第三反相器,其被配置为将第一输出节点的信号反相以驱动被输入有第一数据的节点;以及第四反相器,其被配置为将第二输出节点的信号反相以驱动被输入有第二数据的节点,其中第一数据和第二数据是差分对。

附图说明

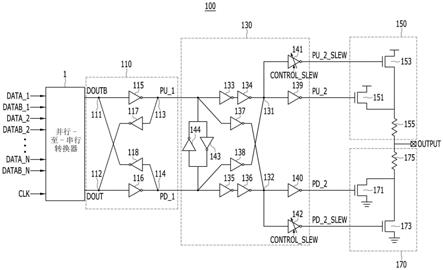

10.图1是示出根据本发明的实施例的发送器的配置的示图。

11.图2是用于描述图1所示的加重电路的操作的示图。

12.图3是示出图1所示的相位偏移补偿电路的相位偏移补偿操作的示图。

13.图4是示出图1所示的相位偏移补偿电路的可变驱动反相器的实施例的示图。

14.图5是图示根据本发明的另一个实施例的发送器的配置的示图。

具体实施方式

15.下面将参考附图更详细地描述各种实施例。然而,本公开可以以不同的形式体现,并且不应被解释为限于本文中所阐述的实施例。准确地说,提供这些实施例使得本公开将是全面和完整的,并且将向本领域技术人员充分传达本公开的范围。在整个本公开中,贯穿本公开的各个附图和实施例,相同的附图标记指代相同的部件。

16.应注意,对“一个实施例”、“另一个实施例”等的引用不一定意味着仅一个实施例,并且对任何这样的短语的不同引用不一定是相同的实施例。

17.将理解的是,尽管在本文中可以使用术语“第一”、“第二”、“第三”等来描述各种元件,但是这些元件不受这些术语的限制。这些术语用于将一个元件与另一个元件区分开。因此,在不脱离本发明的精神和范围的情况下,下面描述的第一元件也可以被称为第二元件或第三元件。

18.还将理解的是,当在本说明书中使用时,术语“包括”、“包括有”、“包含”和“包含有”指定存在所述元件,并且不排除一个或多个其他元件的存在或添加。如本文所使用的,术语“和/或”包括一个或多个相关联的所列项目的任意组合和全部组合。

19.如本文中所使用的,单数形式也可以包括复数形式,反之亦然,除非上下文另外明确指出。除非另有说明,或者从上下文可以清楚地理解为单数形式,否则在本技术和所附权利要求书中使用的数量词“一”和“一个/种”通常应解释为“一个/种或多个/种”。

20.图1是示出根据本发明的一个实施例的发送器100的配置的示图。除了发送器100之外,图1还示出了在发送器100的前端处的并行

‑

至

‑

串行转换器1。

21.并行

‑

至

‑

串行转换器1可以使用时钟clk将n个并行数据data_1至data_n和datab_1至datab_n转换为第一数据dout和第二数据doutb(即,n:1并行

‑

至

‑

串行转换)。被输入到并行

‑

至

‑

串行转换器1的n个并行数据data_1至data_n和datab_1至datab_n可以具有包括n个并行的第一数据data_1至data_n和n个并行的第二数据datab_1至datab_n的差分类型。从并行

‑

至

‑

串行转换器1输出的数据还可以具有包括第一数据dout和第二数据doutb的差分类型。第一数据dout和第二数据doutb是差分对,即,第二数据doutb是第一数据dout的补偿信号。图1示出了并行

‑

至

‑

串行转换器1位于发送器100的前端,但这仅是示例性的。不同类型的电路可以位于发送器100的前端。

22.发送器100可以将数据dout和doutb发送到输出节点output。发送器100可以包括加重电路110、相位偏移补偿电路130、上拉驱动器150和下拉驱动器170。

23.加重电路110可以响应于第二数据doutb和被延迟的第一数据来产生第一上拉驱动信号pu_1,并且可以响应于第一数据dout和被延迟的第二数据来产生第一下拉驱动信号pd_1。加重电路110可以包括:被输入有第二数据doutb的节点111、被输入有第一数据dout的节点112、从其输出第一上拉驱动信号pu_1的节点113、从其输出第一下拉驱动信号pd_1的节点114。加重电路110还可以包括:反相器115,其用于将节点111的信号反相并将被反相的信号驱动到节点113;反相器116,其用于将节点112的信号反相并将被反相的信号驱动到节点114;反相器117,其用于将节点113的信号反相并将被反相的信号驱动到节点112;以及反相器118,其用于将节点114的信号反相并将被反相的信号驱动到节点111。反相器115和116可以用于将第二数据doutb和第一数据dout分别发送到节点113和114。反相器117和118可以通过将被延迟的第二数据和被延迟的第一数据分别交叉反馈回到节点112和节点111来用于加重。因此,反相器115和116的驱动功率可以大于反相器117和118的驱动功率。

24.图2是用于描述加重电路110的操作的示图。在图2中,“201”可以说明第二数据doutb已经被反相器115驱动到节点113。“202”可以说明第一数据dout已经被反相器116、反相器118和反相器115驱动到节点113。“201”和“202”可以被组合(即,相加)以变成第一上拉驱动信号pu_1。每当信号进行转变时,第一上拉驱动信号pu_1就可以被加重。加重时段的长度可以与两个反相器116和118的延迟值之和相同。

25.在图2中,“203”可以说明第一数据dout已经被反相器116驱动到节点114。“204”可以说明第二数据doutb已经被反相器115、反相器117和反相器116驱动到节点114。“203”和“204”可以被组合(即,相加)以变成第一下拉驱动信号pd_1。每当信号进行转变时,第一下拉驱动信号pd_1可以被加重。加重时段的长度可以与两个反相器115和117的延迟值之和相同。

26.返回参考图1,相位偏移补偿电路130可以补偿第一上拉驱动信号pu_1与第一下拉驱动信号pd_1之间的相位偏移,以产生第二上拉驱动信号pu_2和第二下拉驱动信号pd_2。相位偏移补偿电路130还可以产生辅助上拉驱动信号pu_2_slew和辅助下拉驱动信号pd_2_slew。辅助上拉驱动信号pu_2_slew可以是第二上拉驱动信号pu_2的摆率控制信号,所述第二上拉驱动信号pu_2的摆率(slew rate)根据摆率控制信号control_slew而被控制。辅助下拉驱动信号pd_2_slew可以是第二下拉驱动信号pd_2的摆率控制信号,所述第二下拉驱动信号pd_2的摆率根据摆率控制信号control_slew而被控制。

27.相位偏移补偿电路130可以包括两个串联耦接以将节点113的信号(即,pu_1)驱动到节点131的反相器133和134、两个串联耦接以将节点114的信号(即,pd_1)驱动到节点132的反相器135和136。相位偏移补偿电路130还可以包括:反相器137,其被配置为将节点113的信号(即,pu_1)反相并将被反相的信号驱动到节点132;反相器138,其被配置为将节点114的信号(即,pd_1)反相并将被反相的信号驱动到节点131;反相器139,其被配置为将节点131的信号反相并输出被反相的信号作为第二上拉驱动信号pu_2;反相器140,其被配置为将节点132的信号反相并将被反相的信号输出作为第二下拉驱动信号pd_2;可变驱动反相器141,其被配置为将节点131的信号反相并将被反相的信号输出作为第二辅助上拉驱动信号pu_2_slew;以及可变驱动反相器142,其被配置为将节点132的信号反相并将被反相的

信号输出作为第二辅助下拉驱动信号pd_2_slew。相位偏移补偿电路130还可以包括:反相器143,其被配置为将节点113的信号(即,pu_1)反相并将被反相的信号驱动到节点114;以及反相器144,其被配置为将节点114的信号(即,pd_1)反相并将被反相的信号驱动到节点113。两个反相器143和144可以形成锁存器。

28.反相器133、134和138可以对第一上拉驱动信号pu_1的延迟信号和第一下拉驱动信号pd_1的反相信号进行合成,并且将合成信号输出到节点131。合成可以通过将第一上拉驱动信号pu_1的延迟信号和第一下拉驱动信号pd_1的反相信号平均而获得,并将合成信号输出到节点131。反相器139可以通过将节点131的合成信号反相来产生第二上拉上拉驱动信号pu_2。因此,第二上拉驱动信号pu_2可以是通过补偿第一上拉驱动信号pu_1与第一下驱动信号pd_1之间的相位偏移而获得的信号。同样,反相器135、136和137可以对第一上拉驱动信号pu_1的延迟信号和第一下拉驱动信号pd_1的反相信号进行合成,并将合成信号输出到节点132。合成可以通过将第一上拉驱动信号pu_1的延迟信号和第一下拉驱动信号pd_1的反相信号平均而获得。反相器140可以通过将节点132的合成信号反相来产生第二下拉驱动信号pd_2。因此,第二下拉驱动信号pd_2可以是通过补偿第一下拉驱动信号pd_1与第一上拉驱动信号pu_1之间的相位偏移而获得的信号。此外,反相器143可以将节点113的信号反相并将被反相的信号驱动到节点114,并且反相器144可以将节点114的信号反相并将被反相的信号驱动到节点113。因此,反相器143和144可以能够补偿第一上拉驱动信号pu_1与第一下拉驱动信号pd_1之间的相位偏移。

29.图3是示出相位偏移补偿电路130的相位偏移补偿操作的示图。从图3可以看出,尽管在第一上拉驱动信号pu_1和第一下拉驱动信号pd_1之间存在相位偏移,但是在第二上拉驱动信号pu_2和第二下拉驱动信号pd_2之间不存在相位偏移。在图3中,延迟delay指示相位偏移补偿电路130的延迟。该延迟delay可以由反相器133、134和139以及反相器135、136和140产生。

30.图4是示出相位偏移补偿电路130的可变驱动反相器141的实施例的示图。参考图4,可变驱动反相器141可以包括:电流源401和402,其被配置为响应于摆率控制信号control_slew来控制拉出电流(sourcing current)和吸收电流(sinking current);pmos晶体管403;以及nmos晶体管404。pmos晶体管403和nmos晶体管404可以将节点131的信号反相并输出被反相的信号作为第二辅助上拉驱动信号pu_2_slew。电流源401和402可以分别控制供给pmos晶体管403的拉出电流的量和供给nmos晶体管404的吸收电流的量。因此,pmos晶体管403和nmos晶体管404的驱动功率可以通过摆率控制信号control_slew而被控制。当电流源401和402的电流量增大时,第二辅助上拉驱动信号pu_2_slew的摆率可能变高。当电流源401和402的电流量减小时,第二辅助上拉驱动信号pu_2_slew的摆率可能变低。可变驱动反相器142可以以与图4中的可变驱动反相器141相同的方式而被配置。

31.返回参考图1,上拉驱动器150可以响应于第二上拉驱动信号pu_2来上拉驱动输出节点output。上拉驱动器150可以响应于第二辅助上拉驱动信号pu_2_slew来进一步上拉驱动输出节点output。当第二上拉驱动信号pu_2的电平为“高”电平时,上拉驱动器150可以上拉驱动输出节点output。上拉驱动器150可以包括:nmos晶体管151,其被配置为响应于第二上拉驱动信号pu_2来上拉驱动输出节点output;nmos晶体管153,其被配置为响应于第二辅助上拉驱动信号pu_2_slew来上拉驱动输出节点output;以及电阻器155,其耦接在nmos晶

体管151和153与输出节点output之间。通常,上拉驱动器150被配置有pmos晶体管。然而,在图1中,上拉驱动器150被配置有nmos晶体管151和153,以用于更高速运行的目的。

32.下拉驱动器170可以响应于第二下拉驱动信号pd_2来下拉驱动输出节点output。下拉驱动器170可以响应于第二辅助下拉驱动信号pd_2_slew来进一步下拉驱动输出节点output。当第二下拉驱动信号pd_2的电平为“高”电平时,下拉驱动器170可以下拉驱动输出节点output。下拉驱动器170可以包括:nmos晶体管171,其被配置为响应于第二下拉驱动信号pd_2来下拉驱动输出节点output;nmos晶体管173,其被配置为响应于第二辅助下拉驱动信号pd_2_slew来下拉驱动输出节点output;以及电阻器175,其耦接在nmos晶体管171和173与输出节点output之间。

33.发送器100可以通过简单的构造将包括加重波形、具有补偿的相位偏移并且具有受控的摆率的高质量数据发送到输出节点。

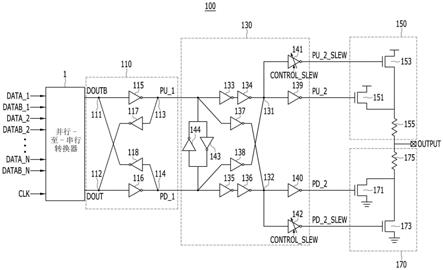

34.图5是示出根据另一个实施例的发送器500的配置的示图。

35.参考图5,发送器500可以包括加重电路510、相位偏移补偿电路530、上拉驱动器550和下拉驱动器570。

36.在加重电路510中,可以看出,图1中示出的加重电路110的反相器117和118已经被可变驱动反相器517和518替换。可变驱动反相器517和518的驱动功率可以被加重控制信号control_emphasis控制。可变驱动反相器517和518中的每个可以以与图4所示的可变驱动反相器141相同的方式来配置。由于可变驱动反相器517和518的驱动功率被加重控制信号control_emphasis控制,因此加重电路510的加重驱动的强度可以被加重控制信号control_emphasis控制。

37.与图1所示的相位偏移补偿电路130相比,相位偏移补偿电路530还可以包括反相器545和546。反相器545可以将节点131的信号反相并将被反相的信号驱动到节点132。反相器546可以将节点132的信号反相并将被反相的信号驱动到节点131。因此,节点131和132之间的相位偏移可以被反相器545和546进一步补偿。

38.上拉驱动器550和下拉驱动器570可以以分别与图1所示的上拉驱动器150和下拉驱动器170相同的方式来配置。

39.根据本公开的实施例,发送器的质量可以通过使用简单的结构而被改善。

40.尽管已经出于说明性目的描述了各种实施例,但是对于本领域技术人员将显而易见的是,在不脱离如所附权利要求所限定的本公开的精神和范围的情况下,可以进行各种改变和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。