一种低emi自动变频的pwm控制电路

技术领域

1.本发明涉及的是雾化电子技术相关的集成电路领域,尤其涉及一种低emi(电磁干扰)自动变频的pwm(pwm:pulse width modulation,脉冲宽度变调)控制电路。

背景技术:

2.超声波雾化技术主要应用于加湿器、香薰机、雾化电子烟和雾化器等电子电气设备中,该技术利用雾化片的高频谐振,使液体的自然结构被打散并形成水雾。

3.常用的雾化片谐振频率为1.7mhz、2.4mhz、3mhz和3.3mhz,雾化片的谐振一般通过pwm(pwm:pulse width modulation,脉冲宽度变调)信号控制功率开关实现。当pwm频率与雾化片的中心谐振频率相同时,雾化片谐振幅度最大且转换效率最高,出雾效果最佳。然而雾化片的主频信号及其高次谐波会在pcb(printed circuit board,印制电路板)板上震荡,成为主要的emi(电磁干扰)干扰源,严重干扰其他信号的传输。

4.为使雾化器能顺利通过emi测试,一般通过在电路板上增加电容、磁珠或更改pcb走线等硬件整改方式,减小emi干扰。这不仅会增加pcb板上的硬件成本,也会增加方案的调试成本。目前有方案尝试通过软件变频的方法,改变pwm频率,减小谐振主频附近的信号强度,以降低emi干扰的强度。然而软件变频的步进非常大,若以170mhz的时钟为源时钟产生1.7mhz的pwm,改变pwm频率的最小步进也达到了1%。这将导致变频后的pwm频率相对中心谐振频率偏移过多,转换效率变低,出雾效果变差,出雾量变低。而且软件变频速度比较慢,降低emi干扰的效果不明显。

技术实现要素:

5.本发明要解决的技术问题在于:克服现有技术中emi干扰大、硬件成本高、方案调试难度高的问题,提出本发明提供了一种低emi自动变频的pwm控制电路,不仅实现了很好的出雾效果,并在不增加硬件成本的条件下,有效降低了emi。

6.为了解决上述技术问题,本发明提出下列技术方案:一种低emi自动变频的pwm控制电路,其特征在于,其包括自动变频控制模块、频率可编程时钟模块和pwm模块;

7.自动变频控制模块的输出为ctrl<11:0>,连接到频率可编程时钟模块;

8.频率可编程时钟模块的输出时钟clk作为pwm模块的源时钟;

9.pwm模块的输出pwmout为最终的pwm输出信号,而输出信号pwmtrg为自动变频控制模块的输入;

10.自动变频控制模块包含一个定时器和一个加减法器,且需要设置定时计数寄存器、中心频率寄存器、步进寄存器和步进计数寄存器;

11.定时器为一个8位定时器,tunm<7:0>为定时器的定时计数寄存器,用以设置多少个pwm周期后,更新一次源时钟频率;pwmtrg信号作为定时器的输入时钟,定时器从0开始计数,每来一个pwmtrg信号,定时器加1;当定时器的计数值等于tnum<7:0>的值,将产生一个加减法器的触发信号trig,并重新从0数值开始计数;

12.加减法器为12位计数器,每次被trig信号触发,都会计算一次值;center<11:0>为中心频率寄存器的值,是根据雾化片的谐振频率而设置好的源时钟值;初始时加减法器的值为center<11:0>,触发工作时会加上步进寄存器step<7:0>的值;里面的8位步进计数器会加1,步进计数器的初始值为步进计数寄存器stepnum<7:0>的值;之后加减法器每触发一次,都会再加上一个step<7:0>,且步进计数器再加1;直到步进计数器值等于2*stepnum<7:0>,加减法器会转变方向,加减法器每触发一次,都会减去一个step<7:0>,且步进计数器减1,直到步进计数器值0,再转变加减法器的方向;

13.加减法器的输出结果ctrl<11:0>作为频率可编程时钟模块的调节控制信号,频率可编程时钟模块采用电流镜阵列的振荡器结构,以实现精密单调线性调节的时钟频率;频率可编程时钟模块的时钟范围为18mhz~36mhz,共有12位调节信号;假定中心时钟频率为24mhz,则可实现的最小调节步进为4.4khz,精度达到0.18

‰

;

14.该pwm模块由预分频器、16位的计数器和比较器组成;

15.频率可编程时钟模块的输出时钟clk作为pwm模块的源时钟,由预分频器对源时钟再次分频,div<7:0>为预分频寄存器,预分频器的输出信号ckd为计数器的时钟;

16.计数器初始从0开始计数,每一个时钟加1,当计数器数值cnt<15:0>等于周期寄存器perd<15:0>的值时,计算器清0且重新计数;且同时产生一个脉宽为一个周期的高电平pwmtrg信号,输出给自动变频控制模块;

17.比较器将比较cnt<15:0>和比较寄存器cmp<15:0>的值,当cnt<15:0>小于或等于cmp<15:0>时,pwm模块的输出pwmout为高电平;当cnt<15:0>大于cmp<15:0>时,pwm模块的输出pwmout为低电平。

18.与现有技术相比,本发明具有下列有益效果:本发明通过硬件集成电路的设计方法,实现了雾化片pwm控制信号的快速且小步进的自动变频,在保证出雾效果的前提下,有效的降低了emi干扰,节省了硬件成本,减小了方案调试难度。

附图说明

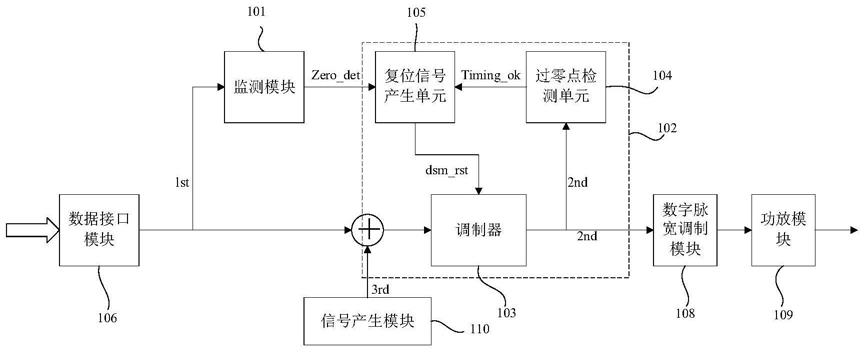

19.图1为本发明低emi自动变频的pwm控制电路的结构框图。

20.图2为自动变频控制模块的结构框图。

21.图3为频率可编程时钟模块输出频率的波形图。

22.图4为pwm模块的结构框图

具体实施方式

23.请参阅图1,其为本发明低emi自动变频的pwm控制电路的结构框图。

24.该低emi自动变频的pwm控制电路包括自动变频控制模块、频率可编程时钟模块和pwm模块。

25.自动变频控制模块的输出为ctrl<11:0>,连接到频率可编程时钟模块。

26.频率可编程时钟模块的输出时钟clk作为pwm模块的源时钟。

27.pwm模块的输出pwmout为最终的pwm输出信号,而输出信号pwmtrg为自动变频控制模块的输入。

28.如图2所示,其为自动变频控制模块的结构框图。该自动变频控制模块包含一个定

时器和一个加减法器,且需要设置定时计数寄存器、中心频率寄存器、步进寄存器和步进计数寄存器。

29.定时器为一个8位定时器,tunm<7:0>为定时器的定时计数寄存器,用以设置多少个pwm周期后,更新一次源时钟频率。pwmtrg信号作为定时器的输入时钟,定时器从0开始计数,每来一个pwmtrg信号,定时器加1;当定时器的计数值等于tnum<7:0>的值,将产生一个加减法器的触发信号trig,并重新从0数值开始计数。

30.加减法器为12位计数器,每次被trig信号触发,都会计算一次值。center<11:0>为中心频率寄存器的值,是根据雾化片的谐振频率而设置好的源时钟值。初始时加减法器的值为center<11:0>,触发工作时会加上步进寄存器step<7:0>的值。里面的8位步进计数器会加1,步进计数器的初始值为步进计数寄存器stepnum<7:0>的值;之后加减法器每触发一次,都会再加上一个step<7:0>,且步进计数器再加1。直到步进计数器值等于2*stepnum<7:0>,加减法器会转变方向,加减法器每触发一次,都会减去一个step<7:0>,且步进计数器减1,直到步进计数器值0,再转变加减法器的方向。

31.加减法器的输出结果ctrl<11:0>作为频率可编程时钟模块的调节控制信号,频率可编程时钟模块可采用电流镜阵列的振荡器结构,以实现精密单调线性调节的时钟频率。频率可编程时钟模块的时钟范围为18mhz~36mhz,共有12位调节信号。假定中心时钟频率为24mhz,则可实现的最小调节步进为4.4khz,精度达到0.18

‰

。

32.如图3所示,其为频率可编程时钟模块的输出频率波形,设置center<11:0>=400h,step<7:0>=2h和stepnum<7:0>=4h,可以看出clk信号的频率fclk随着ctrl<11:0>信号阶梯的变化。

33.如图4所示,其为pwm模块的结构框图。该pwm模块由预分频器、16位的计数器和比较器组成。

34.频率可编程时钟模块的输出时钟clk作为pwm模块的源时钟,由预分频器对源时钟再次分频,div<7:0>为预分频寄存器,预分频器的输出信号ckd为计数器的时钟。

35.计数器初始从0开始计数,每一个时钟加1,当计数器数值cnt<15:0>等于周期寄存器perd<15:0>的值时,计算器清0且重新计数。且同时产生一个脉宽为一个周期的高电平pwmtrg信号,输出给自动变频控制模块。

36.比较器将比较cnt<15:0>和比较寄存器cmp<15:0>的值,当cnt<15:0>小于或等于cmp<15:0>时,pwm模块的输出pwmout为高电平;当cnt<15:0>大于cmp<15:0>时,pwm模块的输出pwmout为低电平。

37.以上所述,只是本发明的较佳实施例而已,本发明并不局限于上述实施方式。以相同的手段达到本发明的技术效果,都应属于本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。