1.本公开为一种工作周期校正,特别是一种用于有效减少闪烁及电源供应噪声的工作周期校正电路及其方法。

背景技术:

2.许多现代电子电路需要精确的时钟才能正常运行。时钟是一种电压信号,它在低电压准位和高电压准位之间周期性地来回切换。电压信号保持高电压准位的时间百分比称为工作周期(duty cycle)。许多电路需要特定的时钟工作周期以提供最佳效能。例如,在同时使用时钟的上升缘(rising edge)及下降缘(falling edge)的多相时钟系统中,通常需要50%的工作周期。然而,时钟的实际工作周期可能会偏离期望值。工作周期校正电路通常用于使时钟具有近似所期望的工作周期。

3.如图1a所示,现有技术的工作周期校正电路依赖于使用反相器110,反相器110包含pmos(p通道金属氧化物半导体)晶体管111及nmos(n通道金属氧化物半导体)晶体管112,作为设置以接收输入时钟及输出输出时钟的时钟缓冲器。在一实施例中,“v

dd

定义为电源供应节点,并且“v

ss”定义为接地节点。输入时钟的高至低转换会导致输出时钟的低至高转换,其延迟取决于pmos晶体管111提供的上拉强度,当输入时钟的低至高转换导致输出时钟的高至低转换,其延迟取决于nmos晶体管112提供的下拉强度。当上拉强度和下拉强度相等时,相对应转换的延迟没有差异,并且输出时钟的工作周期近似为输入时钟的工作周期的互补。例如,如果输入时钟的工作周期为45%,则输出时钟的工作周期将为55%。当上拉强度大于(小于)下拉强度时,输出时钟从高至低的转换要比低至高的转换更快(更慢),从而导致输出时钟在高电压准位上停留的时间更长(更短),因此工作周期更大(更小)。因此,调整反相器的上拉和下拉之间的相对强度可以调整输出时钟的工作周期。mos晶体管的强度取决于所述mos晶体管的宽长比。pmos晶体管111(nmos晶体管112)较高的宽长比使得pmos晶体管111(nmos晶体管112)提供的上拉(下拉)强度更大(更小)。通过调整pmos晶体管111(nmos晶体管112)的宽度,可以调整上拉(下拉)的强度,从而调整输出时钟的工作周期。

4.使用反相器110作为时钟缓冲器并调整其中的mos晶体管的宽度以调整工作周期的缺点在于,mos晶体管是主要的噪声贡献者。尤其是,mos晶体管会产生一种称为“闪烁噪声”的低频噪声,这在许多应用中都为有害的。此外,反相器110对电源供应节点v

dd

或接地节点v

ss

中的噪声敏感。电源供应节点v

dd

或接地节点v

ss

上的任何噪声都可调制输出时钟的工作周期。

5.boerstler等人在美国专利7,913,199中公开了一种工作周期校正电路,所述电路依靠使用与电阻器串联连接的pmos(nmos)晶体管来决定上拉(下拉)的强度,并通过调整电阻器的电阻值来调整输出时钟的工作周期。如图1b所示,工作周期校正电路120包含pmos晶体管121、nmos晶体管122、第一电阻器123及第二电阻器124。pmos晶体管121与第一电阻器123共同决定输出时钟的上拉强度,而nmos晶体管122和第二电阻器124共同决定输出时钟的下拉强度。可通过调整第一电阻器123或第二电阻器124中的一者的电阻值并由此调整上

拉相对于下拉的相对强度以调整输出时钟的工作周期。然而,boerstler等人的主要目标是减少pvt(执行、电压、温度)的变化,同时不考虑噪声的影响。因此,boerstler等人教导了选择第一(第二)电阻器123(124)的电阻值小于pmos晶体管121(nmos晶体管122)的电阻值的十分之一,如此,通过pmos晶体管121(nmos晶体管122)产生的噪声大于通过第一(第二)电阻器123(124)产生的噪声,并且没有解决通过pmos晶体管121或nmos晶体管122产生的闪烁噪声的问题,除此之外,并未考虑电源供应节点v

dd

或接地节点v

ss

处的噪声会调制输出时钟的工作周期。

6.所期望的是一种工作周期校正电路,其可以有效地减轻闪烁噪声及电源供应或接地的噪声。

技术实现要素:

7.在一些实施例中,一种电路包含:第一反相缓冲器,设置以自第一节点接收第一电压并将第二电压输出至第二节点;以及第二反相缓冲器,设置以自第二节点接收第二电压并将第三电压输出至第三节点,其中,第一反相缓冲器包含通过第一数位字(digital word,数字字)控制的第一p型可调电阻器,第一pmos(p通道金属氧化物半导体)晶体管设置以在第一电压自高至低转换时,通过第一p型可调电阻器向第二节点注入第一上拉电流,通过第二数位字控制第一n型可调电阻器,及第一nmos(n通道金属氧化物半导体)晶体管设置以在第一电压自低至高转换时,自第二节点通过第一n型可调电阻器汲取第一下拉电流。第二反相缓冲器包含第二p型可调电阻器,第二p型可调电阻器通过与第二数位字互补的第三数位字控制,第二pmos晶体管设置以在第二电压自高至低转换时,通过第二p型可调电阻器将第二上拉电流注入至第三节点,第二n型可调电阻器通过与第一数位字互补的第四数位字控制,第二nmos晶体管设置以在第二电压自低至高转换时,自第三节点通过第二n型可调电阻器汲取第二下拉电流。

8.在一些实施例中,一种电路包含:第一反相缓冲器,设置以将第一节点处的作为逻辑信号的第一电压转换为第二节点处的第二电压;第二反相缓冲器,设置以将第二节点的第二电压转换为第三节点的第三电压,其中,第一反相缓冲器包含具有第一上拉电阻值的第一上拉电路,第一上拉电路设置以在所第一电压自高至低转换时上拉第二电压,以及具有第一下拉电阻值的第一下拉电路,第一下拉电路设置以在第一电压自低至高转换时下拉第二电压;第二反相缓冲器包含具有第二上拉电阻值的第二上拉电路,设置以在第二电压自高至低转换时上拉第三电压,及具有第二下拉电阻值的第二下拉电路,设置以在第二电压自低至高转换时下拉第三电压;第一上拉电阻值与第一下拉电阻值之间的差值近似等于第二下拉电阻值与第二上拉电阻值之间的差值。

9.在一些实施例中,一种方法包含接收为逻辑信号的第一电压;使用具有第一上拉电阻值及第一下拉电阻值的第一反相缓冲器将第一电压转换为第二电压;使用具有第二上拉电阻值及第二下拉电阻值的第二反相缓冲器将第二电压转换为第三电压,其中,第一上拉电阻值、第一下拉电阻值、第二上拉电阻值、第二下拉电阻值皆为可调的,且第一上拉电阻值与第一下拉电阻值之间的差值近似等于第二下拉电阻值与第二上拉电阻值之间的差值。

10.在一些实施例中,一种方法包含自第一节点接收第一电压,其中,第一电压为周期

性地在低电压准位与高电压准位之间来回切换的逻辑信号;在第一电压自高至低转换时,通过经由第一数位字控制的第一p型可调电阻器,使用第一pmos晶体管向第二节点注入第一上拉电流,从而在第二节点上拉第二电压;在第一电压自低至高转换时,通过经由第二数位字控制的第一n型可调电阻器,使用第一nmos晶体管向第二节点注入第一下拉电流,从而在第二节点下拉第二电压;在第二电压自高至低转换时,通过经由与第二数位字互补的第三数位字控制的第二p型可调电阻器,使用第二pmos晶体管向第二节点注入第二上拉电流,从而在第三节点上拉第三电压;在第二电压自低至高转换时,通过经由与第三数位字互补的第四数位字控制的第二n型可调电阻器,使用第二nmos晶体管向第二节点注入第二下拉电流,从而在第三节点下拉第三电压。

附图说明

11.图1a示出了反相器的示意图。

12.图1b示出了现有技术的工作周期校正电路的示意图。

13.图2为根据本公开的工作周期校正电路的一实施例的示意图。

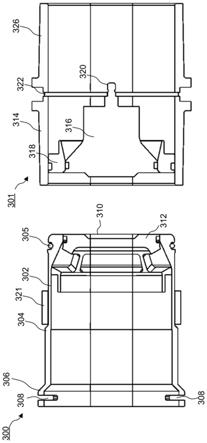

14.图3为根据本公开的p型可调电阻器的一实施例的示意图。

15.图4为根据本公开的n型可调电阻器的一实施例的示意图。

16.图5为根据本公开的方法的一实施例的流程图。

17.符号说明

18.110:反相器

19.111:pmos晶体管

20.112:nmos晶体管

21.120:工作周期校正电路

22.121:pmos晶体管

23.122:nmos晶体管

24.123:第一电阻器

25.124:第二电阻器

26.200:工作周期校正电路

27.300:p型可调电阻器

28.311:pmos晶体管

29.312:pmos晶体管

30.313:pmos晶体管

31.321:电阻器

32.322:电阻器

33.323:电阻器

34.400:n型可调电阻器

35.411:nmos晶体管

36.412:nmos晶体管

37.413:nmos晶体管

38.421:电阻器

39.422:电阻器

40.423:电阻器

41.500:流程图

42.510:步骤

43.520:步骤

44.530:步骤

45.540:步骤

46.550:步骤

47.pu1:第一上拉电路

48.pu2:第二上拉电路

49.pd1:第一下拉电路

50.pd2:第二下拉电路

51.mp1:第一pmos晶体管(pmos晶体管)

52.mp2:第二pmos晶体管(pmos晶体管)

53.mn1:第一nmos晶体管(nmos晶体管)

54.mn2:第二nmos晶体管(nmos晶体管)

55.rp1:第一p型可调电阻器(p型可调电阻器)

56.rp2:第二p型可调电阻器(p型可调电阻器)

57.rn1:第一n型可调电阻器(n型可调电阻器)

58.rn2:第二n型可调电阻器(n型可调电阻器)

59.inv1:第一反相缓冲器

60.inv2:第二反相缓冲器

61.n1:第一节点(节点)

62.n2:第二节点(节点)

63.n3:第三节点(节点)

64.w1:第一数位字(数位字)

65.w2:第二数位字(数位字)

66.w3:第三数位字(数位字)

67.w4:第四数位字(数位字)

68.w1[0]:逻辑信号

[0069]

w1[1]:逻辑信号

[0070]

w1[2]:逻辑信号

[0071]

w2[0]:逻辑信号

[0072]

w2[1]:逻辑信号

[0073]

w2[2]:逻辑信号

[0074]

v

dd

:电源供应节点(电压准位)

[0075]

v

ss

:接地节点(电压准位)

[0076]

v1:第一电压

[0077]

v2:第二电压

[0078]

v3:第三电压

[0079]

i

u1

:第一上拉电流(电流)

[0080]

i

u2

:第二上拉电流(电流)

[0081]

i

d1

:第一下拉电流(电流)

[0082]

i

d2

:第二下拉电流(电流)

具体实施方式

[0083]

本公开为一种工作周期校正。尽管说明书描述数个本公开的具体示范实施例,其涉及本公开的一实施例实施时的优选模式,但是应该理解,本公开的一实施例可通过多种方式来实现,并不限于下面描述的特定实施范例或特定方式,且特定实施范例或方式具有被实施的任何特征。在其他情况下,众所周知的细节不会被显示或描述,以避免模糊本公开的一实施例的特征。

[0084]

本领域的技术人员应理解与本公开的一实施例中使用与微电子相关的术语和基本概念,例如,“电压”、“电流”、“信号”、“功率”、“互补金属氧化物半导体(complementary metal

‑

oxide semiconductor;cmos)”、“n通道金属氧化物半导体(n

‑

channel metal

‑

oxide semiconductor;nmos)晶体管”、“p通道金属氧化物半导体(p

‑

channel metal

‑

oxide semiconductor;pmos)晶体管”、“电阻器”、“电阻值”及“开关”。这些术语用于微电子学的背景中,并且相关概念对于本领域的技术人员来说是显而易见的,因此不会在这里详细解释。

[0085]

本领域的技术人员亦可识别电容器符号及接地符号,可识别pmos晶体管和nmos晶体管的mos(金属氧化物半导体)晶体管符号,并识别其“源极(source)”、“栅极(gate)”和“漏极(drain)”端子。本领域技术人员可阅读包含电容器、nmos晶体管和pmos晶体管的电路示意图,并且不需要在示意图中对一晶体管如何与另一晶体管进行连接的详细描述。本领域技术人员亦可理解诸如伏特(v)、微米(μm)、纳米(nm)之类的单位。

[0086]

从工程角度来呈现本公开的一实施例,例如,关于两个变量x和y,当描述“x等于y”时,表示“x近似等于y”,即“a和b之间的差值小于一特定的工程公差”。当描述“x为零”时,表示“x近似为零”,即“x小于一特定的工程公差”。当描述“x实质上小于y”时,表示“相对于y而言,x可以忽略不计(negligible)”,即“x与y之间的比值小于一特定的工程公差,因此相对于y而言,x可以忽略不计”。

[0087]

在一些实施例中,“v

dd”定义为电源供应节点(power supply node),并且“v

ss”定义为接地节点。注意的是,接地节点为电压准位(voltage level)实质上为零的节点,而电源供应节点为电压准位实质上稳定且高于零的节点。在一些实施例中,取决于对于本领域技术人员显而易见的内文,有时“v

dd”是指电源供应节点v

dd

上的电压准位,而“v

ss”有时是指电源供应节点v

ss

上的电压准位。例如,显而易见的是,诸如“电压准位v

dd

为1.05v”的表述意味着电源供应节点v

dd

上的电压准位为1.05v。

[0088]

在一些实施例中,信号是可以随时间变化的可变电位的电压。某一时刻信号的(电压)电位表示所述时刻信号的状态。

[0089]

一逻辑信号为两个逻辑状态的信号:高状态和低状态。高状态也被称为“1”状态,而低状态也被称为“0”状态。关于逻辑信号q,诸如“q为高”或“q为低”之类的意思为“q处于高状态”或“q处于低状态”。同样,“q为1”或“q为0”等表示“q处于1状态”或“q处于0状态”。

(数位字w4)的值决定。在一些实施例中,当数位字w1(数位字w3)的增加导致第一(第二)p型可调电阻器rp1(rp2)的电阻值更大,数位字w2(数位字w4)的增加导致第一(第二)n型可调电阻器rn1(rn2)的电阻值减小。

[0097]

第一电压v1为在低准位与高准位之间周期性地来回切换的时钟。在一个实施例中,低准位为电压准位v

ss

,而高准位为电压准位v

dd

。如前所述,即表示:低准位为接地节点v

ss

的电压准位,而高准位为电源供应节点v

dd

的电压准位。当第一电压v1自低(高)切换至高(低)时,其经历自低至高(高到低)的过渡。

[0098]

在下文中,有时为了简洁起见省略了明确的术语“第一”,“第二”,“第三”和“第四”,但是省略将不会引起任何混淆。例如,有时将“第一pmos晶体管mp1”简称为“pmos晶体管mp1”,因为在这些规格中除了“第一pmos晶体管”以外没有其他的“pmos晶体管mp1”,因此下拉第二电压v2并迫使第二电压v2自电源供应节点v

dd

至接地节点v

ss

发生自高至低转换。

[0099]

在第一电压v1自低至高转换时,pmos晶体管mp1截止,而nmos晶体管mn1导通,以通过n型可调电阻器rn1自节点n2汲取电流i

d1

,第二电压v2的高至低转换的速度取决于第一下拉电路pd1的下拉电阻值,即nmos晶体管mn1与n型可调电阻器rn1串联连接的总电阻值,较小的下拉电阻值会导致第二电压v2更快自高至低转换。在第一电压v1自高至低转换时,nmos晶体管mn1截止,当pmos晶体管mp1导通以通过p型可调电阻器rp1向节点n2注入电流i

u1

时,因此,上拉第二电压v2并迫使第二电压v2自接地节点v

ss

至电源供应节点v

dd

的低至高转换。第二电压v2自低至高转换的速度取决于第一上拉电路pu1的上拉电阻值,即pmos晶体管mp1与p型可调电阻器rp1串联连接的总电阻值;较小的上拉电阻值会导致第二电压v2更快自低至高转换。当上拉电阻值小于(大于)下拉电阻值时,第二电压v2将比高至低转换更快(慢)地完成自低至高的转换,从而使第二电压v2停留在高准位的时间更长(短),因此工作周期更大(小)。因此,通过通过改变数位字w1来改变p型可调电阻器rp1的电阻值,可通过调整上拉电阻值和下拉电阻值之间的差值来调整第二电压v2的工作周期,或通过改变数位字w2或同时改变两者来改变n型可调电阻器rn1的电阻值。

[0100]

就电路拓扑和功能而言,第二反相缓冲器inv2与第一反相缓冲器inv1相同,因此这里不再详细说明。关于第一反相缓冲器inv1的任何描述都适用于第二反相缓冲器inv2,只需简单地分别用第二电压v2、第三电压v3、数位字w3、数位字w4、nmos晶体管mn2、rn2、pmos晶体管mp2、p型可调电阻器rp2、电流i

u2

、i

d2

及节点n3替换第一电压v1、第二电压v2、数位字w1、数位字w2、nmos晶体管mn1、n型可调电阻器rn1、pmos晶体管mp1、p型可调电阻器rp1、电流i

u1

、i

d1

及节点n2。

[0101]

图3为根据本公开的p型可调电阻器300的一实施例的示意图,p型可调电阻器300可用于实现第一p型可调电阻器rp1。作为示例而非限制,数位字w1具有四个可能的值0、1、2及3,并且被编码为三个逻辑信号w1[0]、w1[1]、w1[2]。p型可调电阻器300包含三个pmos晶体管311、312、313以及三个电阻器321、322、323。三个电阻器321、322、323串联连接并且设置以提供用于电流i

u1

流向节点n2的传导路径。三个pmos晶体管311、312、313包含三个分别由逻辑信号w1[0]、w1[1]、w1[2]控制的开关,并设置以有条件地短路(short)一部分传导路径。r

321

、r

322

及r

323

分别表示电阻器321、322、323的电阻值。pmos晶体管311、312、313皆具有实质上小于r

321

、r

322

及r

323

中的任一者的导通电阻值,以及实质上大于r

321

、r

322

及r

323

中任一者的截止电阻值。在一些实施例中,根据下表对数位字w1进行编码:

[0102]

w10123w1[0]0111w1[1]0011w1[2]0001总电阻值0r

321

r

321

r

322

r

321

r

322

r

323

[0103]

当数位字w1为0时,逻辑信号w1[0]为低,并且pmos晶体管311导通以使整个传导路径短路,并使传导路径的电阻值近似为零。当数位字w1为1时,逻辑信号w1[0]为高,逻辑信号w1[1]为低,pmos晶体管311截止,但是pmos晶体管312导通以使包含电阻器322、323的传导路径部分短路,并使传导路径的电阻值为r

321

。当数位字w1为2时,逻辑信号w1[0]、w1[1]为高,逻辑信号w1[2]为低,pmos晶体管311、312截止,但是pmos晶体管313导通以使包含电阻器323的传导路径部分短路并使传导路径的电阻值为r

321

r

322

。当数位字w1为3时,逻辑信号w1[0]、w1[1]、w1[2]均为高准位,pmos晶体管311、312、313全部截止,并且传导路径的电阻值为r

321

r

322

r

323

。如此,p型可调电阻器300可以根据数位字w1的值来提供可编程电阻值,并且数位字w1的值的增加导致可编程电阻值的增加。

[0104]

通过将图3中的数位字w1、电流i

u1

及节点n2分别替换为数位字w3、电流i

u2

及节点n3,p型可调电阻器300还可用于实现图2的p型可调电阻器rp2。

[0105]

图4为根据本公开的n型可调电阻器400的一实施例的示意图,n型可调电阻器400可用于实现第一n型可调电阻器rn1。作为示例而非限制,数位字w2具有四个可能的值0、1、2及3,并且被编码为三个逻辑信号w2[0]、w2[1]、w2[2]。n型可调电阻器400包含三个nmos晶体管411、412、413以及三个电阻器421、422、423。三个电阻器421、422、423串联连接并且设置以提供用于电流i

d1

流向节点n2的传导路径。三个nmos晶体管411、412、413包含三个分别由逻辑信号w2[0]、w2[1]、w2[2]控制的开关,并设置以有条件地短路一部分传导路径。r

421

、r

422

及r

423

分别表示电阻器421、422、423的电阻值。nmos晶体管411、412、413皆具有实质上小于r

421

、r

422

及r

423

中的任一者的导通电阻值,以及实质上大于r

421

、r

422

及r

423

中任一者的截止电阻值。在一些实施例中,根据下表对数位字w2进行编码:

[0106]

w20123w2[0]0001w2[1]0011w1[2]0111总电阻值r

421

r

422

r

423

r

421

r

422

r

4210[0107]

当数位字w2为0时,逻辑信号w2[0]、w2[1]、w2[2]全部为低,并且nmos晶体管411、412、413全部截止,并且传导路径的电阻值为r

421

r

422

r

423

。当数位字w2为1时,逻辑信号w2[2]为高、逻辑信号w2[0]、w2[1]为低,nmos晶体管411、412截止,但是nmos晶体管413导通,以使包含电阻器423的传导路径部分短路,并使传导路径的电阻值为r

421

r

422

。当数位字w2为2时,逻辑信号w2[1]及逻辑信号w2[2]为高,w2[0]为低,nmos晶体管411截止,但是nmos晶体管412导通以使包含电阻器422、423的传导路径部分短路并使传导路径的电阻值为r

421

。当数位字w2为3时,逻辑信号w2[0]、w2[1]、w2[2]均为高准位,nmos晶体管411导通以使整个传导路径短路,并且传导路径的电阻值近似为零。如此,n型可调电阻器400可以根据w2的值来提供可编程电阻值,并且数位字w2的值的增加导致可编程电阻值的减小。

[0108]

通过将图4中的数位字w2、电流i

d1

和节点n2分别替换为数位字w4、电流i

d2

和节点n3,n型可调电阻器400还可用于实现图2的n型可调电阻器rn2。

[0109]

在一些实施例中,r

421

等于r

321

、r

422

等于r

322

,且r

423

等于r

323

。

[0110]

mos晶体管将产生一种称为“闪烁噪声(flicker noise)”的低频噪声,所述噪声可调制(modulate)mos晶体管的电阻值。pmos晶体管mp1及nmos晶体管mn1都将产生闪烁噪声,所述闪烁噪声可调制它们各自的导通电阻值,从而调制工作周期并在第二电压v2中产生抖动(jitter)。同样地,pmos晶体管mp2和nmos晶体管mn2都将产生闪烁噪声,所述噪声可以调制其各自的导通电阻值,从而调制工作周期并在第三电压v3中产生抖动。为了减轻闪烁噪声的影响,在一些实施例中,pmos晶体管mp1的导通电阻值实质上小于p型可调电阻器rp1的电阻值(极端情况除外,其中p型可调电阻器rp1中的整个传导路径都被短路,并且p型可调电阻器rp1的电阻值设置为最小值),pmos晶体管mp2的导通电阻值实质上小于p型可调电阻器rp2的电阻值(极端情况除外,其中p型可调电阻器rp2中的整个传导路径都被短路,并且p型可调电阻器rp2的电阻值设置为最小值),nmos晶体管mn1的导通电阻值实质上小于n型可调电阻器rn1的电阻值(除了极端情况下,其中n型可调电阻器rn1中的整个传导路径被短路,并且n型可调电阻器rn1的电阻值被设置为最小值);nmos晶体管mn2的导通电阻值实质上小于n型可调电阻器rn2的电阻值(除了极端情况下,其中rn2中的整个传导路径被短路并且rn2的电阻值被设置为最小值)。如此,由于闪烁噪声引起的对图2中任何mos晶体管的导通电阻值的调制可以忽略不计,因所述mos晶体管的导通电阻值实质上小于与所述mos晶体管串联连接的可调电阻器。

[0111]

在一些实施例中,如果第一数量(quantity)不大于第二数量的10%,则第一数量的第一变量(variable)被认为实质上小于第二数量的第二变量。在另一些实施例中,如果第一数量不大于第二数量的20%,则第一数量的第一变量实质上小于第二数量的第二变量。

[0112]

第一反相缓冲器inv1级联(cascade)第二反相缓冲器inv2,从而总体上形成非反相缓冲器,其中,第一电压v1的低至高转换导致第三电压v3的低至高转换,而第一电压v1的高至低转换导致第三电压v3的高至低转换。在一些实施例中,由工作周期校正电路200提供的工作周期校正量近似均匀地分布在第一反相缓冲器inv1与第二反相缓冲器inv2之间。例如,如果第一电压v1的工作周期为44%,而我们希望第三电压v3的工作周期为50%,我们需工作周期校正电路200来提供6%的工作周期校正量,然后将第一反相缓冲器inv1及第二反相缓冲器inv2中的每一者设置以提供3%的工作周期校正量;在这种情况下,第二电压v2的工作周期为53%(注意,如果第一反相缓冲器inv1不提供工作周期校正,则第二电压v2的工作周期将为56%)。

[0113]

进行以下配置以确保通过工作周期校正电路200提供的工作周期校正可以近似均匀地分布在第一反相缓冲器inv1与第二反相缓冲器inv2之间。首先,pmos晶体管mp1、pmos晶体管mp2、nmos晶体管mn1及nmos晶体管mn2具有近似相同的导通电阻值。如此,在第二电压v2或第三电压v3的任何转换上,晶体管受到的影响没有差异。再者,p型可调电阻器rp1的电阻值近似等于n型可调电阻器rn2的电阻值,而n型可调电阻器rn1的电阻值近似等于p型可调电阻器rp2的电阻值。如此,第一上拉电路pu1的上拉电阻值与第一下拉电路pd1的下拉电阻值之间的差值近似等于第二下拉电路pd2的下拉电阻值与第二上拉电路pu2的上拉电

阻值之间的差值。因此,第一反相缓冲器inv1及第二反相缓冲器inv2可以提供近似相等的工作周期校正量,尽管由于第一反相缓冲器inv1的逻辑反相而极性相反。当图3的p型可调电阻器300用于实现p型可调电阻器rp1、rp2,而图4的n型可调电阻器400用于实现n型可调电阻器rn1和n型可调电阻器rn2,当r

421

等于r

321

、r

422

等于r

322

、r

423

等于r

323

、数位字w4与数位字w1(即逻辑信号w4[0]、w4[1]、w4[2]分别为逻辑信号w1[0]、w1[1]、w1[2]的逻辑反相)互补(complementary),以及数位字w3与数位字w2(即逻辑信号w3[0]、w3[1]、w3[2]分别为逻辑信号w2[0]、w2[1]、w2[2]的逻辑反相)互补时,满足第二种配置。

[0114]

使用两个反相缓冲器的级联来形成工作周期校正电路以执行工作周期校正,并且在两个反相缓冲器(而不是仅依靠一个反相缓冲器来实现所需的工作周期校正量)之间均匀分配所需的工作周期校正量具有两个优点。首先,由于使用两个反相缓冲器,对于每个反相缓冲器,闪烁噪声可影响转换的持续时间可减少一半。闪烁噪声的能量随时间平方增加,因此,每个反相缓冲器中的闪烁噪声的能量减少到四分之一。总闪烁噪声能量是两个反相缓冲器中的闪烁噪声能量的和。因此,整个工作周期校正电路的总闪烁噪声能量减少了一半。再者,电源供应节点v

dd

处的电源供应噪声或接地节点v

ss

处的接地噪声也会造成损害。电源供应节点v

dd

或接地节点v

ss

处的低频噪声的影响类似于mos晶体管的闪烁噪声的影响。因此,出于同样的原因,通过使用两个反相缓冲器并且在两个反相缓冲器之间均匀地分配校正量,还可将自电源供应节点v

dd

或接地节点v

ss

中的低频噪声产生的总噪声能量减少一半。

[0115]

在一些实施例中,作为示例而非限制:使用28nm cmos执行在硅基板上制造工作周期校正电路200;电压准位v

dd

为1.05v;电压准位v

dd

为1.05v;电压准位v

ss

为0v;nmos晶体管mn1、mn2的宽度/长度为60微米(μm)/200纳米(nm);pmos晶体管mp1、mp2的宽度/长度为84微米(μm)/200纳米(nm);r

321

、r

322

、r

323

、r

421

、r

422

、r

423

均为130欧姆(ohm);nmos晶体管411、412、413的宽度/长度为120微米(μm)/30纳米(nm);pmos晶体管311、312和313的宽度/长度为156微米(μm)/30纳米(nm)。

[0116]

在一个实施例中,多个工作周期校正电路被级联以扩展工作周期校正的范围。在所述实施例中,可以各自独立地设置所述多个工作周期校正电路中的每一工作周期校正电路的数位字。

[0117]

如图5所示为根据本公开的方法的一实施例的流程图500:自第一节点接收第一电压,其中,第一电压为在低准位与高准位之间周期性地来回切换的逻辑信号(步骤510);在第一电压自高至低转换时,通过经由第一数位字控制的第一p型可调电阻器使用第一pmos晶体管向第二节点注入第一上拉电流,从而在第二节点上拉第二电压(步骤520);在第一电压自低至高转换时,通过经由第二数位字控制的第一n型可调电阻器使用第一nmos晶体管自第二节点汲取第一下拉电流来下拉第二电压(步骤530);在第二电压自高至低转换时,通过经由与第二数位字互补的第三数位字控制的第二p型可调电阻器使用第二pmos晶体管向第二节点注入第二上拉电流,从而在第三节点上拉第三电压(步骤540);以及在第二电压自低至高转换时,通过经由与第一数位字互补的第四数位字控制的第二n型可调电阻器使用第二nmos晶体管自第三节点汲取第二下拉电流来下拉第三电压(步骤550)。

[0118]

以上所述的实施例仅为说明本发明的技术思想及特点,其目的在于使熟悉此项技术者能够了解本发明的内容并据以实施,当不能以之限定本发明的权利要求,即大凡依本

发明所公开的构思所作的均等变化或修饰,仍应涵盖在本发明的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。