技术特征:

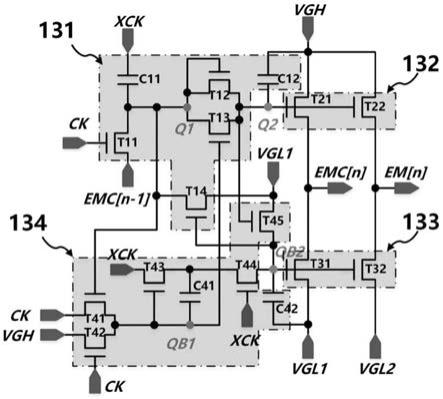

1.一种发射控制驱动器,用于显示像素阵列,其特征在于,所述发射控制驱动器包括多级发射控制驱动电路,其中,每一级发射控制驱动电路包括:第一控制模块,被配置为响应于触发信号、第一时钟信号和第二时钟信号而控制第一节点的电平和第二节点的电平;输出上拉模块,被配置为响应于所述第二节点的电平和第一高电平信号而向所述显示像素阵列中的对应显示像素输出高电平的发射控制信号并向下一级发射控制驱动电路输出高电平的发射级传信号;第二控制模块,被配置为响应于所述第一时钟信号、所述第二时钟信号、所述第一高电平信号和第一低电平信号而控制第三节点的电平和第四节点的电平;输出下拉模块,被配置为响应于所述第四节点的电平、所述第一低电平信号、第二低电平信号而向所述显示像素阵列中的对应显示像素输出低电平的发射控制信号并向下一级发射控制驱动电路输出低电平的发射级传信号;其中,所述多级发射控制驱动电路中的第一级发射控制驱动电路以外部输入的时序信号作为触发信号,其他级发射控制驱动电路均以上一级发射控制驱动电路输出的发射级传信号作为触发信号。2.根据权利要求1所述的发射控制驱动器,其特征在于,所述第一控制模块包括:第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第一电容器和第二电容器;所述第一薄膜晶体管的栅极接收所述第一时钟信号,所述第一薄膜晶体管的第一端接收所述触发信号,所述第一薄膜晶体管的第二端连接至所述第一节点;所述第二薄膜晶体管的栅极和第一端连接至所述第一节点,所述第二薄膜晶体管的第二端连接至所述第二节点;所述第三薄膜晶体管的栅极连接至所述第三节点,所述第三薄膜晶体管的第一端连接至所述第一节点,所述第三薄膜晶体管的第二端连接至所述第二节点;所述第四薄膜晶体管的栅极连接至所述第四节点,所述第四薄膜晶体管的第一端接收所述第一低电平信号,所述第四薄膜晶体管的第二端连接至所述第一节点;所述第一电容器的第一端接收所述第二时钟信号,所述第一电容器的第二端连接至所述第一节点;所述第二电容器的第一端接收所述第一高电平信号,所述第二电容器的第二端连接至所述第二节点。3.根据权利要求1所述的发射控制驱动器,其特征在于,所述输出上拉模块包括:第五薄膜晶体管和第六薄膜晶体管;所述第五薄膜晶体管的栅极连接至所述第二节点,所述第五薄膜晶体管的第一端接收所述第一高电平信号,所述第五薄膜晶体管的第二端输出所述高电平的发射级传信号;所述第六薄膜晶体管的栅极连接至所述第二节点,所述第六薄膜晶体管的第一端接收所述第一高电平信号,所述第六薄膜晶体管的第二端输出所述高电平的发射控制信号。4.根据权利要求1所述的发射控制驱动器,其特征在于,所述第二控制模块包括:第九薄膜晶体管、第十薄膜晶体管、第十一薄膜晶体管、第十二薄膜晶体管、第十三薄膜晶体管、第三电容器、第四电容器;

所述第九薄膜晶体管的栅极连接至所述第一节点,所述第九薄膜晶体管接收所述第一时钟信号,所述第九薄膜晶体管的第二端连接至所述第三节点;所述第十薄膜晶体管的栅极接收所述第一时钟信号,所述第十薄膜晶体管的第一端接收所述第一高电平信号,所述第十薄膜晶体管的第二端连接至所述第三节点;所述第十一薄膜晶体管的栅极连接至所述第三节点,所述第十一薄膜晶体管的第一端接收所述第二时钟信号,所述第十一薄膜晶体管的第二端连接至所述第十二薄膜晶体管的第一端;所述第十二薄膜晶体管的栅极接收所述第二时钟信号,所述第十二薄膜晶体管的第二端连接至所述第四节点;所述第十三薄膜晶体管的栅极连接至所述第二节点,所述第十三薄膜晶体管的第一端接收所述第一低电平信号,所述第十三薄膜晶体管的第二端连接至所述第四节点;所述第三电容器的第一端连接至所述第三节点,所述第三电容器的第二端连接至所述第十二薄膜晶体管的第一端;所述第四电容器的第一端接收所述第一低电平信号,所述第四电容器的第二端连接至所述第四节点。5.根据权利要求1所述的发射控制驱动器,其特征在于,所述输出下拉模块包括:第七薄膜晶体管和第八薄膜晶体管;所述第七薄膜晶体管的栅极连接至所述第四节点,所述第七薄膜晶体管的第一端接收所述第一低电平信号,所述第七薄膜晶体管的第二端输出所述低电平的发射级传信号;所述第八薄膜晶体管的栅极连接至所述第四节点,所述第八薄膜晶体管的第一端接收所述第二低电平信号,所述第八薄膜晶体管的第二端输出所述低电平的发射控制信号。6.根据权利要求2至5中任一项所述的发射控制驱动器,其特征在于,每一级所述发射控制驱动电路中的薄膜晶体管均为n型薄膜晶体管。7.根据权利要求6所述的发射控制驱动器,其特征在于,在周期性变化的所述第一时钟信号和周期性变化的所述第二时钟信号的驱动下,每一级所述发射控制驱动电路的工作过程包括初始化阶段、输出阶段、复位与空闲阶段;在所述初始化阶段,当所述触发信号为低电平、所述第一时钟信号为高电平,以及所述第二时钟信号为低电平时,所述第一薄膜晶体管和所述第九薄膜晶体管导通,使所述第一节点的电平和所述第二节点的电平被初始化至低电平,所述第三节点的电平被初始化至高电平;在所述输出阶段,当所述触发信号为低电平、所述第一时钟信号为低电平,以及所述第二时钟信号为高电平时,所述第十一薄膜晶体管、所述第十二薄膜晶体管导通,使所述第四节点的电平被提升至高电平;响应于所述第四节点的高电平,所述第七薄膜晶体管和所述第八薄膜晶体管导通,使所述输出下拉模块在所述第一低电平信号和所述第二低电平信号的作用下分别输出所述低电平的发射级传信号和所述低电平的发射控制信号。8.根据权利要求7所述的发射控制驱动器,其特征在于,在所述复位与空闲阶段,当所述触发信号为高电平、所述第一时钟信号为高电平,以及所述第二时钟信号为低电平时,所述第一薄膜晶体管和所述第三薄膜晶体管导通,所述第二薄膜晶体管处于二极管状态,使所述第一节点的电平和所述第二节点的电平被提升至高

电平;响应于所述第二节点的高电平,所述第十三薄膜晶体管导通,使所述第三节点的电平被降低至低电平;响应于所述第二节点的高电平,所述第五薄膜晶体管和所述第六薄膜晶体管导通,使所述输出上拉模块在所述第一高电平信号的作用下分别输出所述高电平的发射级传信号和所述高电平的发射控制信号;在所述复位与空闲阶段,当所述触发信号为高电平、所述第一时钟信号为低电平,以及所述第二时钟信号为高电平时,在所述第一电容的耦合作用下,所述第一节点的电平升高,随后所述第一节点通过处于导通状态的所述第二薄膜晶体管向所述第二节点分流,使所述第二节点的电平升高;在所述复位与空闲阶段,在周期性变化的所述第一时钟信号和所述第二时钟信号的作用下,所述第二节点的电平逐步升高,响应于所述第二节点的电平的变化,所述输出上拉模块输出的所述高电平的发射控制信号符合预期的高电平信号。9.根据权利要求8所述的发射控制驱动器,其特征在于,每一级所述发射控制驱动电路均具有与外部连接的多个引脚以接收所述第一高电平信号、第一低电平信号、第二低电平信号、第一时钟信号和第二时钟信号,其中,奇数级的发射控制驱动电路的所述多个引脚中的两个时钟引脚依次与第一时钟的信号端和第二时钟的信号端连接,偶数级的发射控制驱动电路的所述多个引脚中的两个时钟引脚依次与所述第二时钟的信号端和所述第一时钟的信号端连接。10.一种显示装置,其特征在于,所述显示装置包括如权利要求1至9中任一项所述的发射控制驱动器。

技术总结

本公开提供了一种发射控制驱动器和显示装置。其中,所述发射控制驱动器包括多级发射控制驱动电路,用于向显示像素阵列中的对应显示像素输出发射控制信号,所述多级发射控制驱动电路中的第一级发射控制驱动电路以外部输入的时序信号作为触发信号,其他级发射控制驱动电路均以上一级发射控制驱动电路输出的发射级传信号作为触发信号。采用本公开提供的技术方案能够使发射控制驱动器向显示面板输出符合预期的高电平发射控制信号,进而提升显示装置的显示质量。装置的显示质量。装置的显示质量。

技术研发人员:陈俊伟

受保护的技术使用者:深圳市华星光电半导体显示技术有限公司

技术研发日:2021.09.06

技术公布日:2021/11/24

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。