用于高性能连接器的触点几何结构的结构优化

附图说明

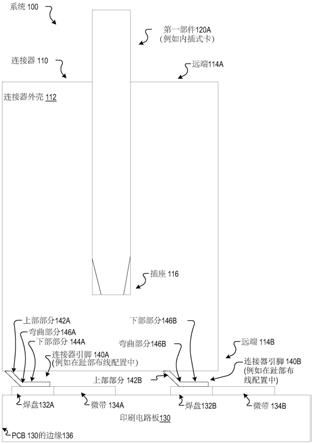

1.图1示出了根据某些实施例的系统,该系统包括通过具有在趾部布线(toe

‑

routing)配置中的连接器引脚的连接器耦合的内插式卡(add

‑

in card)和印刷电路板(pcb)。

2.图2a示出了根据某些实施例的在趾部布线配置中的连接器的连接器引脚的透视图。

3.图2b示出了根据某些实施例的在趾部布线配置中的连接器的连接器引脚的俯视图。

4.图2c示出了根据某些实施例的具有在趾部布线配置中的连接器引脚的连接器的俯视图。

5.图2d示出了根据某些实施例的具有在趾部布线配置中的连接器引脚的连接器的仰视图。

6.图2e示出了根据某些实施例的具有在趾部布线配置中的连接器引脚的连接器的侧视图。

7.图2f示出了根据某些实施例的具有在趾部布线配置中的连接器引脚的连接器的正视截面图。

8.图3a

‑

图3c是示出根据某些实施例的具有在趾部布线配置中的连接器引脚的连接器与具有在跟部布线配置中的连接器引脚的连接器之间的比较的曲线图。

9.图4示出了根据某些实施例的具有多个互连的计算机系统。

10.图5示出了根据某些实施例的片上系统(soc)设计。

具体实施方式

11.本文描述了针对高性能连接器(例如,针对被配置为经由外围部件互连协议等传送信号的连接器)的触点几何结构的结构优化的技术。

12.连接器,例如表面安装(smt)连接器,可用于将第一部件(例如内插式卡)与设置在印刷电路板(pcb)上的第二部件连接。与通孔安装(thm)连接器不同,smt连接器具有位于pcb表面上的焊盘上的长引脚(例如,连接器引脚)。连接器引脚具有从连接器外壳朝向焊盘定向的上部部分、设置在焊盘上的下部部分、以及设置在上部部分和下部部分之间的弯曲部分(例如,以在上部部分和下部部分之间形成过渡)。微带在pcb上从焊盘布线到设置在pcb上的第二部件。smt连接器的连接器引脚中的每一个具有趾部布线或跟部布线的布线方向的配置(例如,引入(lead

‑

in)、引出(break

‑

out))。弯曲部分和连接器引脚的下部部分之间的结合部靠近焊盘的第一远端,而连接器引脚的下部部分的另一端(例如,连接器引脚在该处终止)靠近焊盘的第二远端。在趾部布线配置中,微带紧邻连接器引脚终止处连接到焊盘的第二远端。在跟部布线配置中,微带紧邻在弯曲部分和连接器引脚的下部部分之间的结合部连接到焊盘的第一远端。焊盘桩部(stub)长度是指焊盘的不在信号从微带到内插式卡所经过的最短距离内的部分的长度。跟部布线配置(例如,跟部侧引入/引出)具有较长的

焊盘桩部长度(例如,从弯曲部分到焊盘的第二远端),而趾部布线配置(例如,趾部侧引入/引出)具有较短的焊盘桩部(例如,从弯曲部分到焊盘的第一远端)。跟部布线配置的较长焊盘桩部长度在性能上产生阻抗下降和谐振特性,这使smt连接器信号完整性(si)性能劣化。

13.例如,对于卡机电(cem)规范smt连接器,焊盘为2毫米(mm)长和0.7mm宽。焊盘桩部长度对于趾部布线配置(例如,趾部侧布线)为0.37mm,对于跟部布线配置(例如,跟部侧布线)为1.63mm。16ghz处的插入损耗(il)对于趾部布线配置约为0.84分贝(db),而对于跟部布线配置约为4.1db,这对于pcie gen5操作是不允许的。pcie 5.0cem规范(例如rev0.7规范草案)对于连接器在16ghz下仅允许1.5db il的最大值。

14.在smt连接器使用中,对于高速输入输出(io)(例如,对于被配置为通过协议传送信号的连接器等)推荐趾部布线配置。

15.通常,smt连接器的左侧具有向左定向的连接器引脚(例如,连接器引脚向左弯曲,下部部分从弯曲部分向左延伸),并且smt连接器的右侧具有向右定向的连接器引脚(例如,连接器引脚向右弯曲,下部部分从弯曲部分向右延伸)。有两行连接器引脚(例如,在左侧有一行连接器引脚,在右侧有一行连接器引脚)。第一行中的连接器引脚被布线成远离第二行中的连接器引脚,并且第二行中的连接器引脚被布线成远离第一行中的连接器引脚。

16.当smt连接器的一侧上的连接器引脚紧挨着pcb的边缘(例如,由于平台/底盘架构的板边缘)或紧挨着障碍物(例如,在pcb上布线的微带、位于pcb上的部件)定位时,传统上防止在趾部布线配置中布线连接器引脚(例如,不具有足以用于常规趾部布线配置的板空间)。

17.在一些传统系统中,将焊盘尺寸减到最小以减小焊盘桩部长度。这种焊盘尺寸的减小会导致机械可靠性(例如,开路、短路)或对冲击、振动、老化等的耐久性的问题。

18.在一些传统系统中,在焊盘的中心处使用焊盘中过孔上镀覆(via

‑

in

‑

pad plated over)(vippo)而不是跟部布线配置。这使pcb成本增加了约20%,并且当pcb尺寸大时,这种成本增加是显著的。

19.如本文所公开的设备、系统和方法提供了连接器的触点几何结构的结构优化,所述连接器诸如被配置为经由协议、协议、intel架构实验室(ial)协议、以太网协议等中的一个或多个来传送信号的高性能连接器。连接器包括形成插座的连接器外壳,该插座被配置为接收第一部件,例如内插式卡。连接器还包括第一连接器引脚和第二连接器引脚。第一连接器引脚和第二连接器引脚被配置为响应于第一部件被插入到插座中而电耦合到第一部件。第一连接器引脚从连接器外壳延伸以接触设置在pcb上的第一焊盘,第二连接器引脚从连接器外壳延伸以接触设置在pcb上的第二焊盘。第一焊盘经由设置在pcb上的第一微带连接到设置在pcb上的第二部件,第二焊盘经由设置在pcb上的第二微带连接到第二部件。第一连接器引脚在趾部布线配置中朝向第二连接器引脚定向以耦合到pcb,并且第二连接器引脚在趾部布线配置中远离第一连接器引脚定向以耦合到pcb。

20.本文公开的设备和系统具有优于常规解决方案的优点。与跟部布线配置中的连接器相比,本文所述的连接器具有较小的阻抗下降、较好的谐振特性和改进的信号完整性(si)。本文所述的连接器被配置为具有显著改进的il,并且在高速和/或高频下不符合规范的风险较低(例如,在高达16ghz下最大il为1.5db)。

21.pcie 5.0cem规范(例如rev0.7规范草案)对于高达16ghz的频率需要[

‑

0.1

‑

0.05625*f]db的差分插入损耗(ddil),对于大于16ghz且小于24ghz的频率需要[3

‑

0.25*f]db的差分插入损耗(ddil),其中f是频率。本文公开的设备和系统即使在紧邻pcb的边缘或紧邻障碍物定位时也遵循5.0(例如rev 0.7)规范。

[0022]

本文所述的连接器被配置为紧邻pcb的边缘或pcb上的障碍物设置。本文所述的连接器避免了与减小焊盘尺寸相关联的机械可靠性和耐久性问题。本文所述的连接器避免了焊盘中过孔上镀覆配置的成本、材料和劳动力的增加。

[0023]

尽管本说明书的部分涉及将由连接器外壳接收的内插式卡与设置在pcb上的部件耦合,但是本说明书可应用于耦合柔性附件、线缆组件、pcb、内插式卡等中的一个或多个。本说明书可以应用于耦合两种相同类型的部件(例如,两个pcb、两个内插式卡等)。本说明书可应用于耦合两种不同类型的部件(例如,内插式卡和设置在pcb上的部件等)。尽管本说明书的部分涉及用于通过协议传送信号的连接器,但是该连接器也可以用于通过其它协议传送信号,所述其它协议例如以太网、ial、双倍数据速率(ddr)存储器接口等。

[0024]

图1示出了根据某些实施例的包括连接器110(例如,互连组件、smt gen4 cem连接器、smt gen5 cem连接器等)的系统100。

[0025]

连接器110包括连接器外壳112,其包括第一远端114a和第二远端114b。在一些实施例中,第一远端114a被配置为耦合到第一部件120a,并且第二远端114b被配置为耦合到pcb 130(例如,基板)。在一些实施例中,第一远端114形成被配置为接收第一部件120a的插座116。在一些实施例中,第一部件120a是内插式卡、另一pcb、柔性附件、线缆组件(例如,与内插式卡配合)、调制解调器内插式卡、图形卡内插式卡、随机存取存储器(ram)内插式卡、ddr存储器接口等中的一个或多个。

[0026]

连接器110还包括连接器引脚140a

‑

b(下文中称为连接器引脚140)。连接器引脚140被配置为响应于第一部件120a被插入到插座116中而电耦合到第一部件120a(例如,内插式卡)。连接器引脚140从连接器外壳112延伸以接触设置在pcb 130上的焊盘132。在一些实施例中,每个连接器引脚140(例如,连接器引脚140的下部部分144)被焊接到对应的焊盘132上。在一些实施例中,连接器110具有两行连接器引脚140。第一行连接器引脚140基本上与连接器引脚140a对准(例如,具有与其基本上相同的轮廓),并且第二行连接器引脚140基本上与连接器引脚140b对准(例如,具有与其基本上相同的轮廓)。

[0027]

在一些实施例中,第一部件120a具有电耦合到(例如,直接接触、间接接触)连接器引脚140的接触焊盘(例如,金手指焊盘)(例如,每个连接器引脚140接触第一部件120a的不同接触焊盘)。在一些实施例中,连接器引脚140从连接器110的插座116延伸到pcb 130的焊盘132。在一些实施例中,一个或多个导电部件设置在连接器引脚140和插座116之间,以将连接器引脚140电耦合到第一部件120a,而无需连接器引脚140和第一部件120a彼此直接接触。

[0028]

每个连接器引脚140包括从连接器外壳112(例如,从插座116)朝向焊盘132定向的上部部分142、设置在焊盘132上的下部部分144、以及设置在上部部分142和下部部分144之间的弯曲部分146。

[0029]

连接器110的每个连接器引脚140都在趾部布线配置中(例如,即使当连接器110位

于pcb 130的边缘或接近障碍物时)。在趾部布线配置中,连接器引脚140的下部部分144从紧邻焊盘132的第一远端的第一位置(例如,弯曲部分146和下部部分144的结合部)延伸到紧邻焊盘132的第二远端的第二位置(例如,连接器引脚140的端部)。微带134(例如,设置在pcb 130上的导体、微带线)紧邻焊盘132的第二远端(例如,紧邻连接器引脚140的端部)接触焊盘132。微带134被布线到与pcb 130相关联(例如,设置在其上)的第二部件。在一些实施例中,第二部件是处理器、计算机处理单元(cpu)、图形处理单元(gpu)、端点设备或其他部件。在一些实施例中,至少一组(例如,差分对、线路、链路等)连接器引脚140经由一对微带134耦合到第二部件120b。

[0030]

在一些实施例中,第一行中的两个连接器引脚140a提供第一差分对,并且第二行中的两个连接器引脚140b提供第二差分对。第一差分对提供第一通道,第二差分对提供第二通道。在一些实施例中,链路包括第一通道和第二通道。在一些实施例中,链路包括一个、两个、四个、十八个等通道。在一些实施例中,在每个差分对的两侧上是对应的接地接触引脚。

[0031]

在一些实施例中,第二部件120b(例如cpu)接触微带134,微带接触焊盘132,焊盘132接触(例如焊接到)连接器引脚140,连接器引脚140接触第一部件120a(例如内插式卡)。在一些实施例中,参考层(例如,接地层等)被设置在焊盘132、微带等中的一个或多个的下方(例如,参考层被设置在pcb 130中或上)。

[0032]

与在跟部布线配置中的连接器相比,通过处于趾部布线配置中,连接器引脚140具有较小的阻抗下降、较好的谐振特性和改进的信号完整性(si)。焊盘132具有与趾部布线配置相关的机械可靠性和耐久性(例如,对于跟部布线配置而言与不减小焊盘132尺寸相关)。通过处于趾部布线配置中,连接器引脚140具有满足规范的插入损耗(il)(例如,在高达16ghz下最大il为1.5db)。通过处于趾部布线配置中,连接器引脚140可用于高速io通道信号传送、经由协议传送信号、经由协议传送信号、经由以太网协议传送信号、经由ial协议传送信号等(例如,并且仍在规范内)中的一个或多个。

[0033]

连接器引脚140a在趾部布线配置中朝向连接器引脚140b定向以耦合到pcb 130(例如,附接到pcb 130上的焊盘132a)。在一些实施例中,连接器引脚140a朝向连接器引脚140b弯曲。在一些实施例中,连接器引脚140a的下部部分144朝向连接器引脚140b延伸。在一些实施例中,在焊盘132a上的连接器引脚140a的端部与连接器引脚140b之间的距离比连接器引脚140a的弯曲部分146与连接器引脚140b之间的距离短。在一些实施例中,微带134a从焊盘132a朝向焊盘132b延伸。

[0034]

连接器引脚140b在趾部布线配置中远离连接器引脚140a定向以耦合到pcb 130(例如,附接到pcb 130上的焊盘132b)。在一些实施例中,连接器引脚140b远离连接器引脚140a弯曲。在一些实施例中,连接器引脚140b的下部部分144远离连接器引脚140a延伸。在一些实施例中,连接器引脚140b的弯曲部分与连接器引脚140a之间的距离比焊盘132b上的连接器引脚140b的端部与连接器引脚140a之间的距离短。在一些实施例中,微带134b从焊盘132b远离焊盘132a延伸。

[0035]

在一些实施例中,焊盘132a(和连接器110)紧邻pcb 130的边缘136或障碍物(例如,微带、部件等)设置。在一些实施例中,如本文所述,具有趾部布线配置的连接器110用于优化(例如,缩短)微带134布线(例如,在紧邻或不紧邻pcb 130的边缘或障碍物的情况下)。

在一些示例中,在趾部布线配置中沿相同方向布线的连接器引脚140具有比在趾部布线配置中沿相反方向布线的连接器引脚更短的微带长度。在一些实施例中,如本文所述,具有趾部布线配置的连接器110为平台设计提供了更大的自由度。

[0036]

图2a示出了根据某些实施例的系统200a(例如,图1的系统100)的连接器110的连接器引脚140的透视图。在一些实施例中,连接器引脚140被设置成两行。例如,图2a示出了包括连接器引脚140a的连接器引脚140的行220a和包括连接器引脚140b的连接器引脚140的行220b。每行220对应于连接器110的不同侧。在一些实施例中,来自行220a的连接器引脚140a的第一差分对和来自行220b的连接器引脚140b的第二差分对被配置为将第一部件120a(例如,内插式卡)耦合到与pcb 130相关联(例如,设置在其上)的对应第二部件120b。在一些实施例中,连接器引脚140的不同的差分对组将第一部件120a耦合到不同的部件120b。在一些实施例中,连接器引脚140的多个差分对组将第一部件120a耦合到相同的部件120b。在一些实施例中,接地连接器引脚位于每个连接器引脚差分对旁边。

[0037]

每个连接器引脚140具有从连接器外壳(未示出)朝向焊盘132定向的上部部分142、设置在焊盘132上的下部部分144、以及设置在上部部分142和下部部分144之间的弯曲部分146。在一些实施例中,上部部分142、下部部分144和弯曲部分146构成一个整体件。

[0038]

焊盘132连接到设置在pcb 130上的微带134。通常,当焊盘132(例如,连接器110)紧邻pcb 130的边缘和/或障碍物定位时,连接器引脚以跟部布线配置来布线。焊盘桩部(stub)长度210是指焊盘132的不在信号将从微带134传播到插入到连接器的连接器外壳的插座中的部件(例如,内插式卡)的最短距离(例如,最快路线)内的部分的长度。焊盘桩部长度超过最短的信号距离,并且当其比阈值量长时,产生振动、噪声、谐振和/或空腔效应。

[0039]

在趾部布线配置中的焊盘桩部长度210a(例如,信号不通过其传播的焊盘132的长度)比在跟部布线配置中的焊盘桩部长度210b短得多。在一些实施例中,焊盘132大约2mm长和大约0.7mm宽,在趾部布线配置中的焊盘桩部长度210a小于0.4mm(例如,0.37mm、0.3556mm、14密耳(千分之一英寸)),在根部布线配置中的焊盘桩部长度210b大于1.5mm(例如,1.63mm、1.778mm、70密耳)。在一些实施例中,焊盘桩部长度210b大约比焊盘桩部长度210a大4到5倍。趾部布线配置的较短焊盘桩部长度210a避免了跟部布线配置的较长焊盘桩部长度210b的性能上的阻抗下降、谐振特性以及smt连接器信号完整性(si)性能劣化。

[0040]

每个连接器引脚140具有触点几何形状,使得所有连接器引脚(例如,触点、引脚)以相同方向落在pcb 130(例如,焊盘132)上。这允许连接器110具有最佳性能,假定即使当连接器110(例如smt连接器)位于pcb 130的边缘或以其它方式被阻碍时也能够进行趾部布线配置。这允许针对高速io通道信号传送(诸如gen4、gen5、ial、以太网等)的smt触点几何结构中的结构优化。这解决了当将smt连接器放置在有限空间中时平台设计中的冲突,而不牺牲连接器性能并且不增加成本(例如,pcb成本)。

[0041]

图2b示出了根据某些实施例的系统200b(例如,图1的系统100、图2a的系统200a)的连接器110的连接器引脚140的俯视图。每个连接器引脚140都处于趾部布线配置中。微带134a朝向焊盘132b布线,而微带134b远离焊盘132a布线。

[0042]

图2c示出了根据某些实施例的具有在趾部布线配置中的连接器引脚140的连接器110的俯视图。在一些实施例中,插座116被配置为接收第一部件120a,例如内插式卡。

[0043]

图2d示出了根据某些实施例的具有在趾部布线配置中的连接器引脚140的连接器

110的仰视图。连接器引脚140a在趾部布线配置中朝向连接器引脚140b定向以耦合到pcb 130,且连接器引脚140b在趾部布线配置中远离连接器引脚140a定向以耦合到pcb 130。

[0044]

图2e示出了根据某些实施例的具有在趾部布线配置中的连接器引脚140的连接器110的侧视图。连接器引脚140a在趾部布线配置中朝向连接器引脚140b定向以耦合到pcb 130。

[0045]

图2f示出了根据某些实施例的具有在趾部布线配置中的连接器引脚140的连接器110的正视截面图。每个连接器引脚140从插座116定向以耦合到pcb 130。在一些实施例中,当第一部件120a插入到插座116中时,下部部分144被配置为耦合到设置在pcb 130上的焊盘132,并且上部部分142被配置为耦合到第一部件120a(例如,内插式卡)。上部部分142从插座116延伸(例如,紧邻连接器外壳112的第一远端114a)以在连接器外壳112的第二远端114b处离开连接器外壳112。弯曲部分146设置在上部部分142和下部部分144之间。

[0046]

图3a

‑

c是示出根据某些实施例的在跟部布线配置中的连接器引脚与在趾部布线配置中的连接器引脚之间的比较的曲线图。在一些实施例中,连接器引脚(例如,在趾部布线配置中的连接器引脚和在跟部布线配置中的连接器引脚)的引脚形状、引入迹线(lead

‑

in trace)、内插式卡等的设计是相同的,仅引入迹线的布线方向是不同的。

[0047]

图3a是根据某些实施例的示出在跟部布线配置中的连接器引脚与在趾部布线配置中的连接器引脚(例如,当pcb上的引入迹线在趾部布线配置中时的连接器)的插入损耗比较310的曲线图300。曲线图300示出了插入损耗的规范(例如,gen4和gen5 rev.0.7cem连接器il限制)。如曲线图300所示,在跟部布线配置中的连接器引脚在大约5ghz不满足5.0插入损耗规范,而在趾部布线配置中的连接器引脚在超过15ghz时满足5.0插入损耗规范(例如,具有窄偏移(excursion))。在趾部布线配置中的连接器引脚和在跟部布线配置中的连接器引脚之间的il增量沿着较高频率是相当大的(例如,在8ghz下为0.4db,在16ghz下为2.1db)。朝向/离开跟部的引入方向的影响是如此显著,使得它对于gen5信号传送是不允许的。

[0048]

图3b是示出根据某些实施例的在跟部布线配置中的连接器引脚与在趾部布线配置中的连接器引脚的阻抗比较360的曲线图350。在一些实施例中,当使用上升时间为20ps,20

‑

80%的信号时,根据时域反射(tdr)响应针对趾部和跟部布线绘制了阻抗。如曲线图350所示,在趾部布线配置中的连接器引脚比在跟部布线配置中的连接器引脚具有小得多的阻抗下降。连接器足部(foot)处的阻抗增量约为22欧姆。

[0049]

图3c是示出根据某些实施例的在跟部布线配置中的连接器引脚与在趾部布线配置中的连接器引脚的回波损耗比较380的曲线图370。如曲线图380所示,在趾部布线配置中的连接器引脚比在跟部布线配置中的连接器引脚具有小得多的回波损耗。在跟部布线配置中的连接器引脚不满足pcie 5.0回波损耗规范的频率范围内,在趾部布线配置中的连接器引脚满足pcie 5.0回波损耗规范。

[0050]

图4示出了根据某些实施例的具有多个互连的计算机系统400。系统400包括耦合到控制器集线器415的处理器405和系统存储器410。处理器405包括任何处理元件,诸如微处理器、主处理器、嵌入式处理器、协处理器或其他处理器。处理器405通过前端总线(fsb)406耦合到控制器集线器415。在一个实施例中,fsb 406是如下所述的串行点对点互连。在另一个实施例中,fsb 406(例如,链路)包括符合不同互连标准的串行、差分互连架构。

[0051]

系统存储器410包括任何存储器设备,诸如随机存取存储器(ram)、非易失性(nv)存储器、或系统400中的设备可访问的其他存储器。系统存储器410通过存储器接口416耦合到控制器集线器415。存储器接口的示例包括ddr存储器接口、双通道ddr存储器接口和动态ram(dram)存储器接口。

[0052]

在一个实施例中,控制器集线器415是根集线器、根联合体(root complex)或根控制器。控制器集线器415的示例包括芯片组、存储器控制器集线器(mch)、北桥、互连控制器集线器(ich)、南桥和根控制器/集线器。通常,术语芯片组指两个物理上分离的控制器集线器,即耦合到互连控制器集线器(ich)的存储器控制器集线器(mch)。注意,当前系统通常包括与处理器405集成的mch,而控制器415将以如下所述的类似方式与i/o设备通信。在一些实施例中,可选地通过根联合体(例如,控制器415)支持对等(peer

‑

to

‑

peer)布线。

[0053]

此处,控制器集线器415通过串行链路419耦合到交换机/网桥420。输入/输出模块417和421(也可以称为接口/端口417和421)包括/实现分层协议栈,以提供控制器集线器415和交换机420之间的通信。在一个实施例中,多个设备能够耦合到交换机420。

[0054]

交换机/网桥420将分组/消息在上游方向(即,朝向根联合体的层级向上)从设备425路由到控制器集线器415,并在下游方向(即,远离根控制器的层级向下)将分组/消息从处理器405或系统存储器410路由到设备425。在一个实施例中,交换机420被称为多个虚拟pci到pci桥接设备的逻辑组件。设备425包括要耦合到电子系统的任何内部或外部设备或部件,诸如i/o设备、网络接口控制器(nic)、内插式卡、音频处理器、网络处理器、硬盘驱动器、存储设备、cd/dvd rom、监视器、打印机、鼠标、键盘、路由器、便携式存储设备、火线设备、通用串行总线(usb)设备、扫描仪、以及其他输入/输出设备。通常在术语中,诸如设备,被称为端点。尽管没有具体示出,但是设备425可以包括至pci/pci

‑

x网桥以支持传统或其他版本的pci设备。中的端点设备通常被分类为传统的、或根联合体集成的端点。

[0055]

图形加速器430也通过串行链路432耦合到控制器集线器415。在一个实施例中,图形加速器430耦合到mch,mch耦合到ich。然后,交换机420以及相应的i/o设备425耦合到ich。i/o模块431和418还实现分层协议栈以在图形加速器430和控制器集线器415之间进行通信。类似于以上所讨论的mch,图形控制器或图形加速器430本身可以集成在处理器405中。

[0056]

i/o设备425包括接口426,并且交换机/网桥420包括接口422。接口426经由串行链路423耦合到接口422。

[0057]

在一个实施例中,包括wlan单元和单元的短距离无线引擎可以经由根据协议(例如,根据pci规范基础规范版本3.0(于2004年1月17日公布的),或诸如串行数据输入/输出(sdio)标准的另一此类协议)的互连耦合到处理器405。当然,可以在一个或多个内插式卡上配置的这些外围设备之间的实际物理连接可以借助于适配于母板的ngff连接器。使用wlan单元,可以实现根据给定的电气和电子工程师协会(ieee)802.11标准的通信,而经由使用技术的单元,可以进行经由协议的短距离通信。在另一个实施例中,这些单元可经由例如usb链路或通用异步接收机发射机(uart)链路与处理器405通信。

[0058]

系统400的一个或多个部件可通过具有全都处于如本文所述的趾部布线配置中的连接器引脚140的连接器110耦合。例如,fsb 406、存储器接口416、串行链路419、串行链路423或串行链路432中的一个或多个可包括具有全都在趾部布线配置中的连接器引脚140的一个或多个连接器110。

[0059]

接下来转到图5,示出了根据本公开内容的片上系统(soc)设计的实施例。作为特定的说明性示例,soc 500被包括在用户设备(ue)中。在一个实施例中,ue是指由终端用户使用以进行通信的任何设备,诸如手持电话、智能电话、平板电脑、超薄笔记本、具有宽带适配器的笔记本、或任何其他类似的通信设备。通常,ue连接到基站或节点,其本质上潜在地对应于gsm网络中的移动站(ms)。

[0060]

此处,soc 500包括2个核心

‑

506和507。类似于以上的讨论,核心506和507可以符合指令集架构,诸如基于architecture core

tm

的处理器、advanced micro devices公司(amd)处理器、基于mips的处理器、基于arm的处理器设计或其客户,以及其许可证持有者或采用者。核心506和507耦合到与总线接口单元509和l2高速缓存504相关联的高速缓存控制装置508,以与系统500的其它部分通信。互连510包括片上互连,诸如iosf、amba或以上讨论的其他互连,其潜在地实现所描述的公开内容的一个或多个方面。

[0061]

互连510(例如,接口)提供到其他部件的通信信道,其他部件诸如与sim卡接口连接的用户识别模块(sim)530、保存由核心506和507执行以初始化和引导soc 500的引导代码的引导rom 535、与外部存储器(例如,dram 560)接口连接的sdram控制器540、与非易失性存储器(例如,闪存565)接口连接的闪存控制器545、与外围设备接口连接的外设控制装置550(例如,串行外设接口)、显示和接收输入(例如,触摸使能的输入)的视频编解码器520和视频接口525、执行图形相关计算的gpu 515等。这些接口中的任何接口可以并入本文描述的本公开内容的各方面。

[0062]

在一些实施例中,互连510可以包括具有全都在如本文所述的趾部布线配置中的连接器引脚140的一个或多个连接器110。互连510可以包括具有全都在趾部布线配置中的连接器引脚140的连接器110,以耦合soc 500的一个或多个部件。

[0063]

此外,该系统示出了用于通信的外围设备,例如模块570、3g调制解调器575、gps 585和585。注意,如上所述,ue包括用于通信的无线电装置。结果,这些外围设备通信模块不全都是必需。然而,在ue中,将包括用于外部通信的某种形式的无线电装置。soc 500可经由具有全都在如本文描述的趾部布线配置的连接器引脚140的连接器110耦合到外围设备。

[0064]

以下示例涉及进一步的实施例。

[0065]

示例1是一种连接器,包括:连接器外壳,形成被配置为接收内插式卡的插座;第一连接器引脚,被配置为响应于内插式卡被插入插座中而电耦合到内插式卡,其中,第一连接器引脚从连接器外壳延伸以接触设置在印刷电路板(pcb)上的第一焊盘;以及第二连接器引脚,被配置为响应于内插式卡被插入插座中而电耦合到内插式卡,其中,第二连接器引脚从连接器外壳延伸以接触设置在pcb上的第二焊盘,其中,第一连接器引脚在趾部布线配置中朝向第二连接器引脚定向以耦合到pcb,并且第二连接器引脚在趾部布线配置中远离第一连接器引脚定向以耦合到pcb。

[0066]

在示例2中,示例1的主题,其中,第一连接器引脚包括:上部部分,从连接器外壳朝

向第一焊盘定向;下部部分,设置在第一焊盘上;以及弯曲部分,设置在上部部分和下部部分之间。

[0067]

在示例3中,示例1

‑

2中任一项的主题,其中:下部部分从紧邻第一焊盘的第一远端的第一位置延伸到紧邻第一焊盘的第二远端的第二位置;弯曲部分紧邻第一焊盘的第一远端;并且第一微带紧邻第一焊盘的第二远端接触第一焊盘。

[0068]

在示例4中,示例1

‑

3中任一项的主题,其中,连接器的每个连接器引脚在趾部布线配置中耦合到pcb。

[0069]

在示例5中,示例1

‑

4中任一项的主题,其中,与在跟部布线配置中的连接器相比,在趾部布线配置中的第一连接器引脚和第二连接器引脚具有较小的阻抗下降、改进的谐振特性和改进的信号完整性(si)。

[0070]

在示例6中,示例1

‑

5中任一项的主题,其中,第一连接器引脚和第二连接器引脚中的每一个具有小于0.4毫米的焊盘桩部长度。

[0071]

在示例7中,示例1

‑

6中任一项的主题,其中,第一连接器引脚和第二连接器引脚中的每一个具有在高达16千兆赫(ghz)下最高1.5分贝(db)的插入损耗(il)。

[0072]

在示例8中,示例1

‑

7中任一项的主题,其中,第一连接器引脚和第二连接器引脚中的每一个被配置用于高速输入输出(io)通道信号传送。

[0073]

在示例9中,示例1

‑

8中任一项的主题,其中,连接器被配置为经由外围部件互连协议来传送信号。

[0074]

在示例10中,根据示例1

‑

9中任一项的主题,其中,第一焊盘的第一远端紧邻pcb的边缘设置,并且其中,微带耦合到第一焊盘的第二远端,第二远端与第一焊盘的第一远端相对。

[0075]

示例11是一种系统,包括:第一部件;第二部件,第二部件设置在印刷电路板(pcb)上;以及连接器,包括:连接器外壳,其形成被配置为接收第一部件的插座;第一连接器引脚,被配置为响应于第一部件被插入插座中而电耦合到第一部件,其中,第一连接器引脚从连接器外壳延伸以接触设置在pcb上的第一焊盘,其中,第一焊盘电耦合到第二部件;以及第二连接器引脚,被配置为响应于第一部件被插入插座中而电耦合到第一部件,其中,第二连接器引脚从连接器外壳延伸以接触设置在pcb上的第二焊盘,其中,第二焊盘电耦合到第二部件,其中,第一连接器引脚在趾部布线配置中朝向第二连接器引脚定向以耦合到pcb,并且第二连接器引脚在趾部布线配置中远离第一连接器引脚定向以耦合到pcb。

[0076]

在示例12中,示例11的主题,其中,设置在pcb上的第一微带将第一焊盘耦合到第二部件,并且其中,设置在pcb上的第二微带将第二焊盘耦合到第二部件。

[0077]

在示例13中,示例11

‑

12中任一项的主题,其中,第一连接器引脚包括:上部部分,从连接器外壳朝向第一焊盘定向;下部部分,设置在第一焊盘上;以及弯曲部分,设置在上部部分和下部部分之间。

[0078]

在示例14中,示例11

‑

13中任一项的主题,其中:下部部分从紧邻第一焊盘的第一远端的第一位置延伸到紧邻第一焊盘的第二远端的第二位置;弯曲部分紧邻第一焊盘的第一远端;并且第一微带紧邻第一焊盘的第二远端接触第一焊盘。

[0079]

在示例15中,示例11

‑

14中任一项的主题,其中,连接器的每个连接器引脚在趾部布线配置中耦合到pcb。

[0080]

示例16是一种互连组件,包括:外壳,外壳包括用于耦合到第一部件的第一远端和用于紧邻印刷电路板(pcb)设置的第二远端;部分地设置在外壳内的第一连接器引脚,第一连接器引脚耦合到位于第一远端处的第一部件的第一接触焊盘并且接触紧邻第二远端设置在pcb上的第一焊盘;以及部分地设置在外壳内的第二连接器引脚,第二连接器引脚耦合到位于第一远端处的第一部件的第二接触焊盘并且接触紧邻第二远端设置在pcb上的第二焊盘,其中,第一连接器引脚在趾部布线配置中朝向第二连接器引脚定向以耦合到pcb,并且第二连接器引脚在趾部布线配置中远离第一连接器引脚定向以耦合到pcb。

[0081]

在示例17中,示例16的主题,其中,设置在pcb上的第一微带将第一焊盘耦合到设置在pcb上的第二部件,并且其中,设置在pcb上的第二微带将第二焊盘耦合到第二部件。

[0082]

在示例18中,示例16

‑

17中任一项的主题,其中,第一连接器引脚包括:上部部分,从外壳朝向第一焊盘定向;下部部分,设置在第一焊盘上;以及弯曲部分,设置在上部部分和下部部分之间。

[0083]

在示例19中,示例16

‑

18中任一项的主题,其中:下部部分从紧邻第一焊盘的第一焊盘远端的第一位置延伸到紧邻第一焊盘的第二焊盘远端的第二位置;弯曲部分紧邻第一焊盘的第一焊盘远端;并且第一微带紧邻第一焊盘的第二焊盘远端接触第一焊盘。

[0084]

在示例20中,示例16

‑

19中任一项的主题,其中,互连组件的每个连接器引脚在趾部布线配置中耦合到pcb。

[0085]

各种实施例可以具有上述结构特征的不同组合。例如,上述计算系统的所有可选特征也可以关于本文描述的方法或过程来实现,并且示例中的细节可以在一个或多个实施例中的任意处使用。

[0086]

虽然已经关于有限数量的实施例描述了本公开内容,但是本领域技术人员将从其领会许多修改和变化。所附权利要求旨在覆盖落入本公开内容的真实精神和范围内的所有这样的修改和变化。

[0087]

在本文的描述中,阐述了许多具体细节,诸如处理器和系统配置的具体类型、具体硬件结构、具体架构和微架构细节、具体寄存器配置、具体指令类型、具体系统部件、具体测量/高度、具体处理器流水线级(pipeline stage)和操作等的示例,以便提供对本公开内容的透彻理解。然而,对于本领域技术人员来说显而易见的是,不需要采用这些具体细节来实践本公开内容。在其它实例中,没有详细描述公知的部件或方法,诸如特定和替代的处理器架构、用于所描述的算法的特定逻辑电路/代码、特定固件代码、特定互连操作、特定逻辑配置、特定制造技术和材料、特定编译器实施例、代码中的算法的特定表达、特定断电和选通技术/逻辑以及计算机系统的其它特定操作细节,以避免不必要地使本公开内容难以理解。

[0088]

可以参考诸如计算平台或微处理器之类的特定集成电路中的高速i/o(hsio)设备中的部件来描述实施例。实施例也可以应用于其它类型的集成电路和可编程逻辑器件。例如,所公开的实施例不限于台式计算机系统或便携式计算机,诸如超级本

tm

(ultrabooks

tm

)计算机,并且还可以用于其他设备,诸如手持设备、平板电脑、其他薄笔记本、片上系统(soc)设备和嵌入式应用。手持设备的一些示例包括蜂窝电话、互联网协议设备、数码相机、个人数字助理(pda)和手持式pc。嵌入式应用通常包括微控制器、数字信号处理器(dsp)、片上系统、网络计算机(netpc)、机顶盒、网络集线器、广域网(wan)交换机或者可以执行下面教导的功能和操作的任何其它系统。描述了该系统可以是任何种类的计算机

或嵌入式系统。所公开的实施例尤其可以用于低端设备,如可穿戴设备(例如手表)、电子植入物、传感和控制基础设施设备、控制器、监控和数据采集(scada)系统等。此外,本文描述的装置、方法和系统不限于物理计算设备,而是还可以涉及用于节能和高效的软件优化。如将在以下描述中容易明白的,本文描述的方法、装置和系统的实施例(无论是参考硬件、固件、软件还是其组合)对于与性能考虑平衡的“绿色技术”未来是至关重要的。

[0089]

尽管参考处理器描述了本文中的实施例,但是其它实施例可应用于其它类型的集成电路和逻辑器件。本公开内容的实施例的类似技术和教导可应用于可受益于较高流水线处理量和改进的性能的其它类型的电路或半导体器件。本公开内容的实施例的教导可应用于执行数据操纵的任何处理器或机器。然而,本公开内容不限于执行512位、256位、128位、64位、32位或16位数据运算的处理器或机器,并且可以应用于执行数据操纵或管理的任何处理器和机器。另外,本文的描述提供了示例,并且附图出于说明的目的示出了各种示例。然而,这些示例不应被解释为限制性的,因为它们仅旨在提供本公开内容的实施例的示例,而不是提供本公开内容的实施例的所有可能实施例的详尽列表。

[0090]

本文使用的模块指的是硬件、软件和/或固件的任意组合。作为示例,模块包括与非暂时性介质相关联的硬件,诸如微控制器,以存储适于由微控制器执行的代码。因此,在一个实施例中,对模块的引用指的是硬件,其被具体地配置为识别和/或执行要保存在非暂时性介质上的代码。此外,在另一实施例中,模块的使用是指包括代码的非暂时性介质,其特别适于由微控制器执行以执行预定操作。并且如可以推断的,在又一实施例中,术语模块(在该示例中)可以指代微控制器和非暂时性介质的组合。通常,被示为分离的模块边界通常变化并且可能重叠。例如,第一和第二模块可以共享硬件、软件、固件或其组合,同时潜在地保留一些独立的硬件、软件或固件。在一个实施例中,术语逻辑的使用包括硬件,例如晶体管、寄存器或其它硬件,例如可编程逻辑器件。

[0091]

在一个实施例中,短语“被配置为”的使用是指安排、集合、制造、提供销售、导入和/或设计装置、硬件、逻辑或元件以执行指定或确定的任务。在该示例中,如果没有操作的装置或其元件被设计、耦合和/或互连以执行指定任务,则该装置或其元件仍然“被配置为”执行所述指定任务。作为纯粹说明性的示例,逻辑门可以在操作期间提供0或1。但是“被配置为”向时钟提供使能信号的逻辑门不包括可以提供1或0的每个潜在逻辑门。相反,逻辑门是以某种方式耦合的逻辑门,使得在操作期间,1或0输出将启用时钟。再次注意,术语“被配置为”的使用不需要操作,而是集中于装置、硬件和/或元件的潜伏状态,其中在潜伏状态中,装置、硬件和/或元件被设计成在装置、硬件和/或元件操作时执行特定任务。

[0092]

此外,在一个实施例中,短语“用于”能够/能够用于”和/或“可操作用于”的使用指的是以使得能够以指定方式使用装置、逻辑、硬件和/或元件的方式设计的一些装置、逻辑、硬件和/或元件。注意,如上所述,在一个实施例中,用于、能够用于或可操作用于的使用是指装置、逻辑、硬件和/或元件的潜在状态,其中装置、逻辑、硬件和/或元件不操作,而是以使得能够以指定方式使用装置的方式来设计。

[0093]

在整个说明书中,对“一个实施例”或“实施例”的引用意味着结合该实施例描述的特定特征、结构或特性被包括在本公开内容的至少一个实施例中。因此,在本说明书通篇中的各个部分出现的短语“在一个实施例中”或“在实施例中”不一定全部指代同一实施例。此外,特定的特征、结构或特性可以以任何合适的方式组合在一个或多个实施例中。

[0094]

在前述说明书中,已经参考具体的示例性实施例给出了具体实施方式。然而,显然,在不偏离如所附权利要求中阐述的本公开内容的更宽的精神和范围的情况下,可以对其进行各种修改和改变。因此,说明书和附图应被认为是说明性的而不是限制性的。此外,实施例和其它示例性语言的前述使用不一定是指相同的实施例或相同的示例,而是可以指不同的和相异的实施例,以及潜在地相同的实施例。

[0095]

具体实施方式的某些部分是按照对计算机存储器内的数据位的操作的算法和符号表示来呈现的。这些算法描述和表示是数据处理领域的技术人员用来最有效地将他们工作的实质传达给本领域的其他技术人员的手段。算法在此处并且通常被认为是导致期望结果的自相容操作序列。这些操作是需要对物理量进行物理操纵的那些操作。通常,尽管不是必须的,这些量采用能够被存储、传送、组合、比较和以其他方式操纵的电或磁信号的形式。主要出于通用的原因,将这些信号称为位、值、元素、符号、字符、项、数字等已被证明有时是方便的。本文所述的块可以是硬件、软件、固件或其组合。

[0096]

然而,应当记住,所有这些和类似的术语都与适当的物理量相关联,并且仅仅是应用于这些量的方便的标记。除非特别声明,否则如从以上讨论中显而易见的,可以理解,在整个描述中,利用诸如“接触”、“耦合”、“传导”、“传送”、“接收”等术语的讨论指的是计算系统或类似电子计算设备的动作和过程,其将表示为计算系统的寄存器和存储器内的物理(例如,电子)量的数据操纵和变换成类似地表示为计算系统存储器或寄存器或其它这样的信息存储、传输或显示设备内的物理量的其它数据。

[0097]

词语“示例”或“示例性”在本文中用于表示用作示例、实例或说明。本文描述为“示例”或“示例性”的任何方面或设计未必应解释为比其它方面或设计优选或有利。相反,词语“示例”或“示例性”的使用旨在以具体的方式呈现概念。如本技术中所使用的,术语“或”旨在表示包含性的“或”而不是排他性的“或”。即,除非另外指定,或者从上下文中是清楚的,否则“x包括a或b”旨在表示任何自然的包含性排列。即,如果x包括a;x包括b;或者x包括a和b,则“x包括a或b”在任何前述情况下都满足。另外,除非另外指定或从上下文中清楚涉及单数形式,否则本技术和所附权利要求中使用的冠词“一(a)”和“一个(an)”一般应当被解释为表示“一个或多个”。此外,除非如此描述,否则通篇使用的术语“实施例”或“一个实施例”或“实施方式”或“一个实施方式”并不旨在表示相同的实施例或实施方式。此外,如本文所用的术语“第一”、“第二”、“第三”、“第四”等意在作为区分不同元件的标记,并且不一定具有根据它们的数字命名的序数含义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。