1.本发明涉及光子芯片,尤其涉及包括边缘耦合器的结构以及制造包括边缘耦合器的结构的方法。

背景技术:

2.光子芯片用于许多应用及系统中,例如数据通信系统及数据计算系统。光子芯片将光学组件(例如波导、光学开关、边缘耦合器,以及偏振片)与电子组件(例如场效应晶体管)集成于统一的平台中。除其它因素以外,布局面积、成本以及操作开销可通过集成两种类型的组件来减小。

3.边缘耦合器通常用于在半导体激光器与光子芯片上的光学组件之间耦合激光。该边缘耦合器可包括一段狭窄的波导芯,其剖面面积显着小于该半导体激光器所发射的激光束。由于模式大小以及模式形状,可能发生该半导体激光器与边缘耦合器的硅波导芯之间的耦合效率低下。这些效率低下可导致严重的耦合损失。

4.需要改进的包括边缘耦合器的结构以及制造包括边缘耦合器的结构的方法。

技术实现要素:

5.在本发明的一个实施例中,一种结构包括具有波导芯的边缘耦合器,以及位于该波导芯的部分上方的成形层。该波导芯由第一材料组成,且该成形层由组分与该第一材料不同的第二材料组成。

6.在本发明的一个实施例中,一种方法包括:形成具有波导芯的边缘耦合器,以及形成位于该波导芯的部分上方的成形层。该波导芯由第一材料组成,且该成形层由组分与该第一材料不同的第二材料组成。

附图说明

7.包含于并构成本说明书的一部分的附图示例说明本发明的各种实施例,并与上面所作的有关本发明的概括说明以及下面所作的有关该些实施例的详细说明一起用以解释本发明的该些实施例。在该些附图中,类似的附图标记表示不同视图中类似的特征。

8.图1显示依据本发明的实施例包括处于处理方法的初始制造阶段的结构的光子芯片的顶视图。

9.图2显示大体沿图1中的线2

‑

2所作的该结构的剖视图。

10.图3显示处于图1之后的制造阶段的该结构的顶视图。

11.图4显示大体沿图3中的线4

‑

4所作的该结构的剖视图。

12.图5显示处于图4之后的制造阶段的该结构的剖视图。

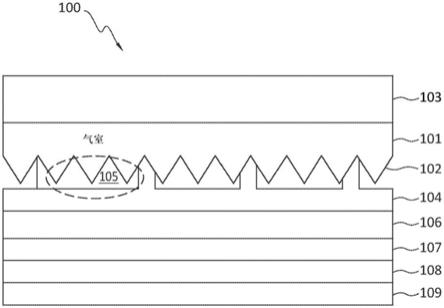

13.图6

‑

8显示依据本发明的替代实施例的结构的顶视图。

具体实施方式

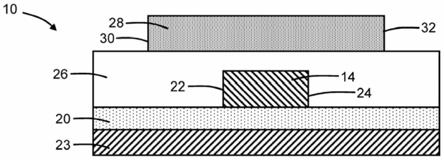

14.请参照图1、2并依据本发明的实施例,边缘耦合器的结构10包括波导芯12,其具有倒锥14、与激光器15相邻的端部表面16,以及与倒锥14直接连接的非锥形段18。在一个实施例中,波导芯12的非锥形段18可为直线段。波导芯12(设于介电层20上方)可沿纵轴17排列。在该代表性实施例中,端部表面16终止于倒锥14且提供与激光器15对接并参与接收自激光器15发射的激光的具有给定剖面面积的表面。

15.波导芯12可由单晶半导体材料(例如单晶硅)组成。在一个实施例中,该单晶半导体材料可源自绝缘体上硅(silicon

‑

on

‑

insulator;soi)晶圆的装置层,该晶圆还包括提供介电层20的埋置氧化物层,以及由单晶半导体材料(例如单晶硅)组成的衬底23。可在光子芯片的前端工艺处理期间通过光刻及蚀刻制程自该单晶半导体材料层图案化波导芯12。

16.激光器15可经配置以发射朝向波导芯12的端部表面16的具有给定的波长、强度、模式形状、以及模式尺寸的激光。激光器15与波导芯12的端部表面16之间的空间可由空气或者替代地由配率材料(index

‑

matching material)填充。激光器15可由iii

‑

v族化合物半导体材料组成。激光器15可为例如磷化铟/磷化铟

‑

镓

‑

砷激光器。激光器15可位于包括波导芯12的光子芯片上,或者替代地,可位于芯片外(off

‑

chip)。

17.倒锥14可从端部表面16沿平行于纵轴17的长度方向延伸至变为非锥形段18的过渡处。波导芯12包括相对的侧壁或侧表面22、24,它们在倒锥14的长度上的间隔随着与端部表面16的距离增加而增加。侧表面22、24相对于介电层20的顶部表面可为垂直,或者替代地,可成锐角。在倒锥14的长度上的波导芯12的宽度尺寸的增加可结束于变为非锥形段18的过渡处。

18.可以侧表面22、24之间的直立距离来测量波导芯12的宽度尺寸。波导芯12在端部表面16可具有宽度w1,且波导芯12在变为非锥形段18的过渡处可具有较大的宽度w2。倒锥14可提供宽度尺寸从较小的宽度w1至较大的宽度w2的过渡。在该代表性实施例中,波导芯12的倒锥14在端部表面16具有宽度w1,且波导芯12的倒锥14在变为非锥形段18的过渡处具有宽度w2。倒锥14的锥形形状在该倒锥的长度上可具有基于线性函数的线性宽度变化,或者替代地,可具有基于非线性函数(例如二次函数、抛物线函数、或指数函数)变化的宽度。在一个代表性实施例中,在端部表面16的宽度w1可在从激光器15接收的激光的波长的0.01倍至从激光器15接收的激光的波长的0.1倍的范围内变化。倒锥14具有以从端部表面16至倒锥14与非锥形段18之间的该过渡处的距离来测量的长度。

19.在一个替代实施例中,波导芯12可由氮化硅而不是单晶硅组成。在一个替代实施例中,衬底23可包括与端部表面16紧邻的凹槽。

20.请参照图3、4,其中,类似的附图标记表示图1、2中类似的特征,且在下一制造阶段,在波导芯12上方形成介电层26。介电层26可由介电材料(例如二氧化硅)组成,通过化学气相沉积来沉积并利用例如化学机械抛光平坦化,以移除形貌(topography)。波导芯12嵌入并埋置于介电层26的该介电材料中。额外的介电层(未显示)可形成于介电层26上方,并例如可分别由氮化硅及二氧化硅组成,以定义异质层堆叠。

21.直接在波导芯12的倒锥14上方的位置的介电层26上可形成成形层28。介电层26的一部分位于波导芯12与成形层28之间。介电层26的该部分防止波导芯12与成形层28之间的直接接触。成形层28与波导芯12的倒锥14以堆叠形式层叠。成形层28位于与波导芯12不同

的平面中,以提供层式堆叠(layered stack)。

22.通过在介电层26上方沉积材料层并用光刻及蚀刻制程图案化该沉积层可形成成形层28。为此,在该沉积层上方通过光刻制程形成蚀刻掩膜,并用蚀刻制程(例如反应离子蚀刻)来蚀刻移除该沉积层的未掩蔽部分。该蚀刻掩膜的形状确定成形层28的图案化形状。在该代表性实施例中,成形层28可具有以外周为特征的块或板的图案化形状。在该代表性实施例中,成形层28的该图案化形状可为外周具有角的矩形。该蚀刻制程可经选择以在完全穿过该沉积介电层以后停止于介电层26的材料上。成形层28包含具有不同于波导芯12的材料的组分的材料。在一个实施例中,成形层28可由通过化学气相沉积沉积的介电材料(例如氮化硅)组成。

23.成形层28具有相对的侧壁或侧表面30、32以及从一个侧表面30延伸至另一个侧表面32的端部表面34、36。成形层28的侧表面30、32及端部表面34、36围绕成形层28的外周。端部表面34可与波导芯12的端部表面16共面或实质上共面(也就是,直接位于上方)。端部表面36可直接位于下方波导芯12的倒锥14与非锥形段18之间的过渡处上方。在该代表性实施例中,成形层28可沿长度方向位于整个倒锥14上方。在替代实施例中,成形层28可沿长度方向仅位于倒锥14的一部分上方。倒锥14的侧表面22、24设于成形层28的侧表面30与侧表面32之间。

24.可从端部表面34至端部表面36沿平行于纵轴17的方向测量成形层28的长度。成形层28的长度可等于或实质上等于倒锥14的长度。在替代实施例中,成形层28的长度可小于倒锥14的长度。可以从侧表面30至侧表面32的直立距离来测量成形层28的宽度w3。成形层28的宽度w3可大于波导芯12的宽度w1(图1),并且还可大于波导芯12的宽度w2(图1)。在一个代表性实施例中,成形层28的宽度w3可大于自激光器15接收的激光的波长的0.25倍。

25.请参照图5,其中,类似的附图标记表示图4中类似的特征,且在下一制造阶段,在成形层28上方形成介电层40。介电层40可由介电材料(例如二氧化硅)组成,通过化学气相沉积来沉积并利用例如化学机械抛光平坦化,以移除形貌。成形层28嵌入或埋置于介电层40的该介电材料中。

26.在介电层40上方形成后端工艺堆叠42。后端工艺堆叠42包括可由介电材料(例如二氧化硅)组成的一个或多个介电层,以及设于一个或多个层间介电层中的由例如铜或铝组成的金属化层。

27.在本文中所述的任意实施例中,结构10可被集成于包括电子组件及额外光学组件的光子芯片中。例如,该电子组件可包括通过cmos前端工艺(front

‑

end

‑

of

‑

line;feol)处理制造的场效应晶体管。

28.结构10提供用于与激光器15进行有效对接端光耦合的整体集成(monolithically

‑

integrated)堆叠边缘耦合器。用于该堆叠边缘耦合器的结构10是异质的,因为波导芯12与成形层28的材料组分不同。结构10可提升模式匹配(也就是,模式形状及/或模式尺寸的匹配),以增强光耦合的效率。可在流程中无需额外掩膜的情况下,将成形层28添加至该结构。

29.请参照图6,其中,类似的附图标记表示图1中类似的特征,且依据本发明的替代实施例,可邻近波导芯12形成条带44、46。在该代表性实施例中,倒锥14横向设于条带44、46之间,条带44邻近侧表面22,且条带46邻近侧表面24。条带44、46可由与波导芯12相同的材料

组成,且可在图案化波导芯12时图案化条带44、46。条带44、46以及倒锥14可位于成形层28正下方并横向位于侧表面30、32之间。在一个实施例中,条带44、46及倒锥14可沿长度方向完全直接位于成形层28下方。在一个实施例中,条带44、46及倒锥14可沿长度方向及宽度方向完全直接位于成形层28下方。如前面结合图3

‑

5所述继续处理。

30.请参照图7,其中,类似的附图标记表示图1中类似的特征,且依据本发明的替代实施例,可修改波导芯12,以在倒锥14与端部表面16之间添加另一个倒锥48。可调节波导芯12的图案化,以提供不同的形状来添加倒锥48。如前面结合图3

‑

5所述继续处理。在一个替代实施例中,可邻近倒锥14、48的相对侧表面22、24添加条带44、46(图6)。

31.请参照图8,其中,类似的附图标记表示图3中类似的特征,且依据本发明的替代实施例,可修改成形层28,以添加锥形段50作为附加至该矩形形状的非矩形形状。锥形段50可位于倒锥14的一部分上方,并与倒锥14的锥形相反。在后一情形中,锥形段50随着与波导芯12的端部表面16的距离增加而变窄,而倒锥14随着与波导芯12的端部表面16的距离增加而加宽。在一个实施例中,锥形段50可直接位于如图7中所示的倒锥14上方,其中,矩形形状直接位于波导芯12的倒锥48上方。

32.本文中引用的由近似语言例如“大约”、“大致”及“实质上”所修饰的术语不限于所指定的精确值。该近似语言可对应于用以测量该值的仪器的精度,且除非另外依赖于该仪器的精度,否则可表示所述值的 /

‑

10%。

33.本文中引用术语例如“垂直”、“水平”等作为示例来建立参考框架,并非限制。本文中所使用的术语“水平”被定义为与半导体衬底的传统平面平行的平面,而不论其实际的三维空间取向。术语“垂直”及“正交”是指垂直于如刚刚所定义的水平面的方向。术语“横向”是指在该水平平面内的方向。

34.与另一个特征“连接”或“耦接”的特征可与该另一个特征直接连接或耦接,或者可存在一个或多个中间特征。如果不存在中间特征,则特征可与另一个特征“直接连接”或“直接耦接”。如存在至少一个中间特征,则特征可与另一个特征“非直接连接”或“非直接耦接”。在另一个特征“上”或与其“接触”的特征可直接在该另一个特征上或与其直接接触,或者可存在一个或多个中间特征。如果不存在中间特征,则特征可直接在另一个特征“上”或与其“直接接触”。如存在至少一个中间特征,则特征可“不直接”在另一个特征“上”或与其“不直接接触”。

35.对本发明的各种实施例所作的说明是出于示例说明的目的,而非意图详尽无遗或限于所揭示的实施例。许多修改及变更对于本领域的普通技术人员将显而易见,而不背离所述实施例的范围及精神。本文中所使用的术语经选择以最佳解释实施例的原理、实际应用或在市场已知技术上的技术改进,或者使本领域的普通技术人员能够理解本文中所揭示的实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。