1.本发明属于半导体超结器件技术领域,特别是涉及一种半导体超结器件的制造方法。

背景技术:

2.半导体超结器件基于电荷平衡技术,可以降低导通电阻和寄生电容,使得半导体超结器件具有极快的开关特性,可以降低开关损耗,实现更高的功率转换效率。现有技术的半导体超结器件的主要制造工艺包括:首先,如图1所示,在n型外延层10上形成硬掩膜层11,然后进行光刻和刻蚀,在硬掩膜层11内形成开口并在n型外延层10内形成沟槽12;接下来,如图2所示,通过外延工艺在所形成的沟槽内形成p型柱13,并进行平坦化处理,之后,如图3所示,再通过一次光刻工艺和刻蚀工艺形成栅介质层14和栅极15,最后在n型外延层10内形成p型体区16和位于p型体区16内的n型源区17。不论是平面型还是沟槽型的半导体超结器件,在形成p型柱时需要进行一次光刻工艺,然后在形成栅极时,还需要再进行一次光刻工艺,由于光刻工艺的成本昂贵,而且存在对准偏差的风险,导致半导体超结器件的制造成本和制造风险较高。

技术实现要素:

3.有鉴于此,本发明的目的是提供一种半导体超结器件的制造方法,以降低半导体超结器件的制造成本并降低半导体超结器件的制造风险。

4.为达到本发明的上述目的,本发明提供了一种半导体超结器件的制造方法,包括:

5.步骤一:在n型外延层上形成硬掩膜层,通过光刻工艺定义p型柱的位置,然后刻蚀所述硬掩膜层,在所述硬掩膜层内形成至少一个开口,所述开口与所述p型柱的位置对应;

6.步骤二:以所述硬掩膜层为掩膜刻蚀所述n型外延层,在所述n型外延层内形成第一沟槽,所述第一沟槽的宽度大于对应所述开口的宽度,所述第一沟槽包括位于对应所述开口下方的p型柱区域和位于所述p型柱区域两侧的栅极区域;

7.步骤三:在所述第一沟槽的表面形成第一绝缘层,淀积第一导电层并回刻,以在所述第一沟槽的栅极区域内形成栅极;

8.步骤四:在所述栅极的暴露侧壁上形成绝缘侧墙,以所述硬掩膜层和所绝缘侧墙为掩膜,对所述n型外延层进行刻蚀,在所述n型外延层内形成第二沟槽,所述第二沟槽位于对应所述p型柱区域的下方;

9.步骤五:在所述p型柱区域和所述第二沟槽内形成p型柱,所述p型柱与所述n型外延层之间形成pn结结构,所述p型柱与所述栅极由所述绝缘侧墙隔离。

10.可选的,所述半导体超结器件的制造方法还包括:

11.步骤六:在所述n型外延层内形成p型体区;

12.步骤七:在所述p型体区内形成n型源区。

13.可选的,所述硬掩膜层为氧化硅层-氮化硅层-氧化硅层的叠层。

14.可选的,所述步骤二中,在刻蚀形成所述第一沟槽时,采用各向异性刻蚀和各向同性刻蚀相结合的刻蚀方法。

15.可选的,所述第一绝缘层的材料为氧化硅。

16.可选的,所述第一导电层的材料为多晶硅。

17.可选的,所述步骤三中,在淀积所述第一导电层时,所形成的第一导电层至少填满所述第一沟槽的栅极区域。

18.可选的,所述第二沟槽的宽度大于对应所述p型柱区域的宽度。

19.可选的,所述步骤四中,在刻蚀形成所述第二沟槽时,采用各向异性刻蚀和各向同性刻蚀相结合的刻蚀方法。

20.可选的,所述绝缘侧墙包括氮化硅层。

21.可选的,所述p型柱的材料为p型多晶硅。

22.本发明提供的半导体超结器件的制造方法,通过一次光刻工艺形成第一沟槽,然后自对准的在第一沟槽的栅极区域内形成栅极,再以覆盖栅极侧壁的绝缘侧墙和硬掩膜层为掩膜刻蚀n型外延层以形成第二沟槽,然后在第一沟槽和第二沟槽内形成p型柱。本发明的半导体超结器件的制造方法,形成栅极和p型柱时只需要进行一次光刻工艺,可以极大的降低半导体超结器件的制造成本,并降低半导体超结器件的制造风险。

附图说明

23.为了更加清楚地说明本发明示例性实施例的技术方案,下面对描述实施例中所需要用到的附图做一简单介绍。

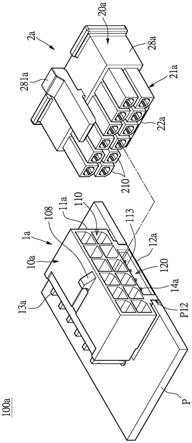

24.图1至图3是现有技术的半导体超结器件的制造工艺中的主要结构的剖面结构示意图;

25.图4至图10是本发明提供的半导体超结器件的制造方法的一个实施例的制造工艺中的主要结构的剖面结构示意图。

具体实施方式

26.以下将结合本发明实施例中的附图,通过具体方式,完整地描述本发明的技术方案。显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。应当理解,本发明所使用的诸如“具有”、“包含”以及“包括”等术语并不配出一个或多个其它元件或其组合的存在或添加。同时,为清楚地说明本发明的具体实施方式,说明书附图中所列示意图,放大了本发明所述的层和区域的厚度,且所列图形大小并不代表实际尺寸。

27.图4至图10是本发明提供的半导体超结器件的制造方法的一个实施例的制造工艺中的主要结构的剖面结构示意图。

28.首先,如图4所示,在提供的n型外延层20之上形成硬掩膜层30,n型外延层20通常为硅,硬掩膜层30通常为氧化硅层-氮化硅层-氮化硅层的叠层。通过光刻工艺定义出p型柱的位置,然后对硬掩膜层30进行刻蚀,在硬掩膜层30中形成至少一个开口31,开口31与所述p型柱的位置对应,开口31的数量(即p型柱的数量)由所设计的半导体超结器件的具体规格确定,本发明实施例中仅示例性的示出了两个开口31。

29.接下来,如图5所示,以硬掩膜层30为掩膜对n型外延层20进行刻蚀,在n型外延层

20内形成第一沟槽32,第一沟槽32与硬掩膜层30中形成的开口一一对应,第一沟槽32包括位于对应开口下方的p型柱区域32a以及位于p型柱区域32a两侧的栅极区域32b。在刻蚀形成第一沟槽32时,可以选用各向异性刻蚀和各向同性刻蚀相结合的方法,比如先采用各向异性刻蚀的方法形成第一沟槽32的p型柱区域32a,再采用各向同性刻蚀的方法形成第一沟槽32的栅极区域32b。

30.接下来,如图6所示,在第一沟槽的表面形成第一绝缘层21,第一绝缘层21通常为氧化硅,通过热氧化的方法形成。然后淀积第一导电层并回刻,在第一沟槽的栅极区域内形成栅极22。在淀积第一导电层时,可以使第一导电层填满整个第一沟槽,也可以使第一导电层不填满整个第一沟槽,但第一导电层应填满第一沟槽的栅极区域。

31.接下来,如图7所示,在栅极22的暴露侧壁上形成绝缘侧墙33,绝缘侧墙33通常包括氮化硅层。然后以硬掩膜层30和缘侧墙33为掩膜,先刻蚀掉暴露出的第一绝缘层,然后继续对n型外延层20进行刻蚀,在n型外延层20内形成位于第一沟槽下方的第二沟槽34。可选的,如图8所示,第二沟槽34的宽度可以大于对应p型柱区域的宽度,对应的,在刻蚀形成第二沟槽34时,可以采用各向异性刻蚀和各向同性刻蚀相结合的刻蚀方法,示例性的,可以先采用各向异性刻蚀的方法进行刻蚀,再采用各向同性刻蚀的方法进行刻蚀,以此来增加第二沟槽34的宽度,也就减小了相邻的第二沟槽34之间的n型外延层的宽度。

32.值得注意的是,绝缘侧墙33可以延伸至硬掩膜层30的暴露侧壁上,如图7和图8所示。

33.接下来,如图9所示,在第一沟槽和第二沟槽内形成p型柱23,p型柱23与n型外延层20之间形成pn结结构,从而形成电荷平衡,p型柱23与栅极22由绝缘侧墙33隔离。p型柱23为通过外延工艺形成的p型多晶硅。可选的,在形成p型柱23前,可以先进行一次p型离子注入,以在第二沟槽下方或者第二沟槽下方及两侧的n型外延层20内形成p型补偿区,进而实现p型柱23与n型外延层20之间更优的电荷平衡。

34.接下来,如图10所示,按照常规工艺在n型外延层20内形成p型体区24,并在p型体区24内形成n型源区25。

35.最后,按照常规工艺形成隔离介质层和金属层等即可得到半导体超结器件。

36.以上具体实施方式及实施例是对本发明提出的半导体超结器件的制造方法的技术思想的具体支持,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在本技术方案基础上所做的任何等同变化或等效的改动,均仍属于本发明技术方案保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。