1.本揭露是有关于一种半导体结构及制造多个半导体结构的方法,特别是所揭露的半导体结构具有透过晶圆堆叠技术而与逻辑结构整合为一的存储器结构。

背景技术:

2.奠基于高性能的前景,系统上晶片(system

‑

on

‑

chip,soc)的实现已被极大地推展;soc作为一种将dram阵列嵌入逻辑元件的结构,被认为是针对高速传输大量数据的较佳解决方案。然而,dram和逻辑元件的合并需要减少两者制程的差异,举例而言,对于soc,逻辑元件和所嵌入的dram的设计规则兼容性,即至关重要。

3.协调逻辑元件和所嵌入的dram的兼容性的过程主要取决于数种不同的方法。例如,将存储器电路整并入经高性能技术优化后的逻辑元件当中,或是将逻辑电路整并入经技术优化后的高密度低性能dram。任一种选择都具有优缺点,通常将dram和逻辑元件合并至同一晶片可产生巨大的优势,但这并不容易达成,而且整合的过程充满挑战性。也就是说,由于逻辑元件的制程和dram的制程在许多方面并不相容,因此针对这些半导体结构的整合,有必要提出新的方法来解决问题。

技术实现要素:

4.本发明的一实施例是关于一种半导体结构,其包含:一第一混合键合结构,其具有一第一表面和一第二表面;一存储器结构,其接触该第一表面;及一控制电路结构,其用于控制该存储器结构,并接触该第二表面。

5.本发明的一实施例是关于一种系统级封装结构,其包含:一第一半导体结构,其具有一第一临界尺寸;一第二半导体结构,其与该第一半导体结构相堆叠,其具有一第二临界尺寸且经一混合键合界面而与该第一半导体结构相接触;及一基板,其经一第一导电凸块而电性连接于该第一半导体结构及该第二半导体结构;其中,该第一临界尺寸不同于该第二临界尺寸。

6.本发明的一实施例是关于一种制造多个半导体结构的方法,该方法包含:形成一第一混合键合层于具有多个第一存储器结构的一第一晶圆上;形成一第二混合键合层于具有多个控制电路结构的一第二晶圆上;经由一第一混合键合步骤而键合该第一晶圆及该第二晶圆,以连接该第一混合键合层及该第二混合键合层,因此取得一第一键合晶圆;及至少将该第一晶圆、该第二晶圆、该第一混合键合层及该第二混合键合层单体化而取得多个半导体结构。

附图说明

7.当结合附图阅读时,从以下详细描述最佳理解本揭露的态样。应注意,根据产业中的标准实践,各种结构未按比例绘制。事实上,为了清楚论述可任意增大或减小各种结构的尺寸。

8.图1a说明根据本揭露的半导体结构的一些实施例的剖视图。

9.图1b说明半导体结构或半导体晶圆的正面及背面的定义。

10.图2说明根据本揭露的半导体结构的一些实施例的剖视图。

11.图3说明根据本揭露的半导体结构的一些实施例的剖视图。

12.图4a至图4j说明根据本揭露的形成半导体结构的一些实施例的剖视图。

13.图5a至图5b说明根据本揭露的形成半导体结构的一些实施例的剖视图。

14.图6a至图6b说明根据本揭露的形成半导体结构的一些实施例的剖视图。

15.图7说明根据本揭露的半导体结构的一些实施例的剖视图。

16.图8说明根据本揭露的半导体结构的一些实施例的剖视图。

17.图9a至图9b说明根据本揭露的形成半导体结构的一些实施例的剖视图。

18.图10说明根据本揭露的半导体结构的一些实施例的剖视图。

19.图11a至图11b说明根据本揭露的形成半导体结构的一些实施例的剖视图。

20.图12说明根据本揭露的半导体结构的一些实施例的剖视图。

21.图13a至图13b说明根据本揭露的形成半导体结构的一些实施例的剖视图。

22.图14说明根据本揭露的半导体结构的一些实施例的剖视图。

23.图15a至图15c说明根据本揭露的形成半导体结构的一些实施例的剖视图。

具体实施方式

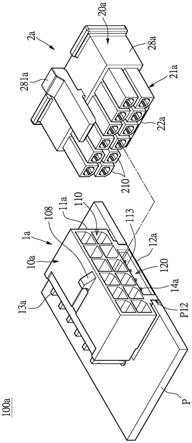

24.本技术案主张2020年5月7日申请的美国临时专利申请案第63/021,608号的优先权,该案的全部揭示内容以引用方式全部并入本文中。

25.以下揭露提供用于实施所提供的标的的不同构件的许多不同实施例或实例。下文描述元件及配置的特定实例以简化本揭露。当然,此等仅为实例且非旨在限制。举例而言,在以下描述中的一第一构件形成于一第二构件上方或上可包含其中该第一构件及该第二构件经形成为直接接触的实施例,且亦可包含其中额外构件可形成在该第一构件与该第二构件之间,使得该第一构件及该第二构件可不直接接触的实施例。另外,本揭露可在各个实例中重复元件符号及/或字母。此重复出于简化及清楚的目的且本身不指示所论述的各个实施例及/或组态之间的一关系。

26.此外,为便于描述,诸如「在

…

下面」、「在

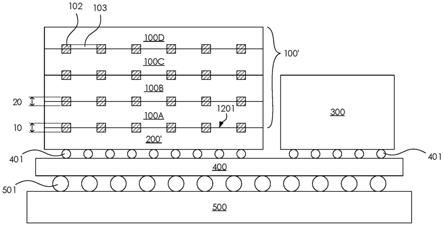

…

下方」、「下」、「在

…

上方」、「上」、「在

…

上」及类似者的空间相对术语可在本文中用于描述一个元件或构件与另一(些)元件或构件的关系,如图中图解说明。空间相对术语意欲涵盖除在图中描绘的定向以外的使用或操作中的装置的不同定向。设备可以其他方式定向(旋转90度或按其他定向)且因此可同样解释本文中使用的空间相对描述词。

27.如本文中使用,诸如「第一」、「第二」及「第三」的术语描述各种元件、组件、区、层及/或区段,此等元件、组件、区、层及/或区段不应受此等术语限制。此等术语可仅用来区分一个元件、组件、区、层或区段与另一元件、组件、区、层或区段。除非由上下文清楚指示,否则诸如「第一」、「第二」及「第三」的术语当在本文中使用时并不暗示一序列或顺序。

28.举例来说,高频宽存储器(high bandwidth memory,hbm)是一种将存储器晶粒垂直堆叠于逻辑晶粒的cpu或gpu存储器系统。堆叠的存储器晶粒是以可区分层次的存储器塔的形式坐落于逻辑晶粒上,其中,每两个相邻的存储器晶粒是透过被封模材料侧向环绕的

微凸块所相连接。虽然这些hbm堆叠并非于物理上被整合至cpu或gpu当中,但他们已经相当靠近,且是透过中介板快速地与cpu或gpu连接,因此hbm的特性几乎与整合至晶片的存储器没有区别。

29.一般而言,在透过微凸块操作堆叠存储器晶粒之前,这些用于hbm结构中的存储器晶粒通常已经过切割测试,例如是透过一些标准电性测试操作而获得的已知良好晶粒(known good die,kgd)。接着这些kgd可被堆叠或封装以用于高端应用。每个存储器晶粒都经微凸块键合而形成存储器堆叠(当中可包含控制电路晶粒),且该存储器晶粒是进一步以覆晶方式键合至硅中介板而形成晶圆上晶片(chip

‑

on

‑

wafer,cow)结构。不过,微凸块操作会导致高成本、挑选出kgd的流程会降低生产效率,且微凸块操作引起的堆叠缺陷会降低生产良率。

30.因此,本揭露的一些实施例提供了一种整合有控制电路的存储器结构,其是透过晶圆堆叠而非cow操作所完成。控制电路可包含一个或多个逻辑结构。换句话说,可透过以晶圆堆叠(wafer

‑

on

‑

wafer或wafer

‑

to

‑

wafer)为基础的混合键合操作来制造控制电路上的存储器结构。存储器堆叠(当中可包含控制电路)可以在完成混合键合操作后进行切割或分离。藉由这个方式,形成存储器堆叠的生产效率可以极大地提高,也可以显著降低微凸块操作引起的堆叠缺陷的风险。至于在省略对存储器晶粒的kgd挑选的面向上,则可藉由提供控制电路对存储器晶粒的存储器区块执行测试操作,不需要使用到探针量测或试验机。例如美国专利申请号us 16/899,166的「半导体装置及其制造方法」,其是作为本案的参考资料。

31.图1a展示了一半导体结构,该半导体结构包含透过晶圆堆叠而与控制电路结构整合的存储器结构。在一些实施例中,控制电路结构可包含至少一个逻辑结构,例如,包含具有半导体结构最小线宽的一晶体管。如图所示,半导体结构包含一混合键合结构10、一存储器结构100及一控制电路结构200。混合键合结构10包含一第一表面101a及相反于第一表面101a的一第二表面201a。混合键合结构10是夹于存储器结构100及控制电路结构200之间。混合键合结构10是用于整合存储器结构100及控制电路结构200。在一些实施例中,存储器结构100与混合键合结构10的第一表面101a相接触。控制电路结构200与混合键合结构10的第二表面201a相接触。

32.在一些实施例中,混合键合结构10包含一第一混合键合层101靠近于存储器结构100,及一第二混合键合层201靠近于控制电路结构200。第一混合键合层101是形成于存储器结构100上,且用于键合第二混合键合层201。第二混合键合层201是形成于控制电路结构200上,且用于键合第一混合键合层101。在一些实施例中,每一第一混合键合层101及第二混合键合层都包含多个被介电材料所侧面环绕的键合垫,介电材料的例子包含氧化物。

33.混合键合是一种可同时藉由金属键合和氧化物键合而连接两个基板或晶圆的方法,意即,其可允许两个基板或晶圆以「面对面」、「面对背」或「背对背」的方式连接。出于说明的目的,图1b展示了半导体结构或半导体晶圆的正面与背面的定义。对于一半导体结构80(例如前揭图1a所示的存储器结构100或控制电路结构200)或是一晶圆而言,半导体结构可包含一半导体基板83及一后段制程结构85,而一前段制程结构84则是形成于半导体基板83上或其中。根据一些实施例,后段制程结构85的表面可为半导体结构80的正面81,而半导体基板83的表面则可为半导体结构80的背面82。不过,这并不构成本实施例的限制。对于半

导体结构的正面或背面,其定义也可以交换。在一些实施中,存储器结构100的位置及控制电路结构200的位置可经由键合而垂直对齐,并且第一混合键合层101的多个第一键合垫102可因此与第二混合键合层201的多个第二键合垫202相接触;与此同时,第一混合键合层101的多个第一氧化物部分103是与第二混合键合层201的多个第二氧化物部分203相接触。在这些实施例中,第一混合键合层101的第一键合垫102与第二混合键合层201的第二键合垫202为镜像分布。

34.在一些实施例中,第一键合垫102及第二键合垫202是由铜(cu)所制成。在一些实施例中,第一氧化物部分103及第二氧化物部分203是由诸如二氧化硅(sio2)等介电材料所制成。为了强化铜

‑

铜的连结,对于键合垫表面平坦度的控制是重要的因素。例如,在一些实施例中,铜键合垫的表面可透过实施化学机械研磨(cmp)操作而被控制为实质上与二氧化硅部分齐平。在一些实施例中,取决于所进行的混合键合操作,二氧化硅部分可些微地凸出于铜键合垫。在本揭露中,举例而言,可以透过先让第一氧化物部分103与第二氧化物部分203相接触来使得存储器结构100及控制电路结构200键合;前述氧化物部分之间的键合可以透过凡德瓦力。之后,可实施退火操作以促成第一键合垫102和第二键合垫202之间的连接。

35.在一些实施例中,控制电路结构200是一种dram控制逻辑。在一些实施例中,控制电路结构200除了用于控制存储器结构100之外,还可以进一步用作与gpu或cpu整合的系统上晶片(soc)。

36.如图2所示,本揭露的半导体结构可包含一系统级封装(sip)结构。在该些实施中,系统及封装结构包含一第一半导体结构100’、一第二半导体结构200’以及一基板500。第二半导体结构200’是与第一半导体结构100’堆叠在一起。第二半导体结构200’是经混合键合界面1201而与第一半导体结构100’相接触。基板500是经一第一导电凸块连接部501而电性连接于第一半导体结构100’及第二半导体结构200’。第一导电凸块连接部501可包含多个焊料(solder),其中这些焊料可被合适的底部填充胶材料(未示于图中)所环绕。

37.在一些实施例中,第一半导体结构100’可包含堆叠于第二半导体结构200’之上的多个存储器晶粒(即存储器晶粒100a、100b、100c、100d等)。在一些实施例中,至少两个存储器晶粒是经一第二混合键合结构20而混合键合。在一些实施例中,相邻的两个存储器晶粒是经第二混合键合结构20而混合键合。第二混合键合结构20的详细内容乃相同于之前曾阐述过的第一混合键合结构10,只不过此时镜像分布的键合垫是形成于相邻的存储器晶粒上。在一些实施例中,第一半导体结构100’的每一存储器晶粒皆可包含具有一第一临界尺寸的dram结构(即经微影制程操作而在所述结构中能实现的最小线宽)。同样地,第二半导体结构200’可包含至少具有一第二临界尺寸的逻辑结构(即经微影制程操作而在所述结构中能实现的最小线宽)。由于可以实施不同的技术节点来制造第一半导体结构100’和第二半导体结构200’,因此第一临界尺寸不同于第二临界尺寸。在一些实施例中,当实施于制造第一半导体结构100’的技术节点较为先进时,第一临界尺寸小于第二临界尺寸。在另一实施例中,当实施于制造第二半导体结构200’的技术节点较为先进时,第一临界尺寸大于第二临界尺寸。值得注意的是,当第一半导体结构100’和第二半导体结构200'是由相同的技术节点制造时,第一临界尺寸可等于第二临界尺寸。

38.在本揭露中,透过混合键合而垂直堆叠于第二半导体结构200’上的存储器晶粒的

数量是可客制化的。举例而言,有鉴于在传统结构中,通常会有四个或是八个存储器晶粒透过微凸块而堆叠于控制电路或逻辑晶粒上,据此,本揭露的部分实施例是以四个存储器晶粒透过混合键合而垂直堆叠于第二半导体结构200’作为范例,但实际上,存储器晶粒的数量并不限于此数字或范围。

39.在一些实施例中,第二半导体结构200’是一个dram控制逻辑。在一些实施例中,第二半导体结构200’是经前揭图1a所示的第一混合键合结构10而键合于第一半导体结构100’的存储器晶粒100a。在一些实施例中,第一半导体结构100’当中的键合结构及第一半导体结构100’与第二半导体结构200’之间的键合结构,是不同于第二半导体结构200’与基板500之间的键合结构。举例而言,第一混合键合结构10和第二混合键合结构20是透过适当的混合键合操作而形成,其特征在于混合键合界面1201;而第一导电凸块连接部501则是透过适当的微凸块操作而形成,其可被观察到多个焊料凸块。

40.在一些实施例中,sip结构可包含经一第二导电凸块连接部401而与第一半导体结构100’及第二半导体结构200’电性连接的一第三半导体结构300。第二导电凸块连接部401可包含多个焊料,其中这些焊料可被合适的底部填充胶材料(未示于图中)所环绕。在一些实施例中,第三半导体结构300具有一第三临界尺寸,其小于第一半导体结构100’的第一临界尺寸。在一些实施例中,第三半导体结构300是紧邻于第一半导体结构100’及第二半导体结构200’所构成的一堆叠。在一些实施例中,第三半导体结构300是用以作为gpu或cpu的soc。

41.在一些实施例中,sip结构可包含在基板500与第二半导体结构200’之间的中介板400。中介板400可用以支撑第一半导体结构100’、第二半导体结构200’和第三半导体结构300。虽未示于图2当中,但中介板400是透过第二导电凸块连接部401、第一导电凸块连接部501及位于第三半导体结构300与第二半导体结构200’之间横向发送信号的一重分布层,从而电性连接于第一半导体结构100’、第二半导体结构200’及基板500。中介板400的重分布层也可使靠近第二半导体结构200’的较高密度i/o被改编为较靠近基板500的较低密度i/o。

42.如前所述,混合键合可允许两个基板或晶圆以「面对面」或「面对背」等排列方式连接。在一些实施例中,凭借着不同的混合键合方案及在制造每一存储器晶粒和逻辑晶粒的通孔时的诸多可选顺序,存储器晶粒和逻辑晶粒的基板或晶圆的堆叠可因此有不同的应用形式。

43.如图3所示,在一些实施例中,每一存储器结构和控制电路结构是经后钻孔制程(via

‑

last process)所制造。经所述后钻孔制程,硅穿透通孔(tsv)即是在制备晶体管和打线之后才形成;易言之,前段制程(feol)结构和后段制程(beol)结构皆是形成于通孔蚀刻和通孔填充等操作之前。在该些实施例中,逻辑晶粒和存储器晶粒可以「面对面」的排列为堆叠,而存储器结构中的存储器晶粒之间则是以「背对背」的排列为堆叠(方案i)。另一方面,分散于逻辑晶粒上的键合垫和分散于存储器晶粒上的键合垫是为镜像分布。另外,在具有方案i的堆叠排列的实施例中,前揭图1所示的混合键合结构10的第二表面201a是较靠近于控制电路结构200的后段制程结构,并且较远离于控制电路结构200的前段制程结构。

44.如图3所示,由于存储器晶粒是自一第一晶圆61(后揭示于图4a)所制造,每一存储器晶粒包含一第一正面61a及一第一背面61b;而控制电路结构200则是自一第二晶圆62(后

揭示于图4a)所制造,并且具有一第二正面62a及一第二背面62b。第一混合键合结构10是夹于控制电路结构200及存储器晶粒100a之间。另外,每一第二混合键合结构20是夹于相邻的存储器晶粒之间,例如存储器晶粒100a、100b之间。在一些实施例中,每一第二混合键合结构20包含两个第一混合键合层101,其中,位于这些第一混合键合层101当中的键合垫是沿着混合键合界面1201而为镜像分布。

45.可参考图4a至图4j以制造如图3所示的半导体结构。如图4a所示,在一些实施例中,存储器结构100(即存储器晶粒)及控制电路结构200(即逻辑晶粒)于混合键合操作前,是分别形成于第一晶圆61及第二晶圆62。每一第一晶圆61及第二晶圆62可包含多个晶粒区域,而本揭露仅以展示其中一个晶粒区域做为示意。在一些实施例中,每一存储器结构100的范围内可包含一第一保留区域631。同样地,每一控制电路结构200的范围内可包含一第二保留区域632。第一保留区域631及第二保留区域632是保留给后续操作以在该处形成tsv,因为键合垫的位置可与tsv的所在位置相关。如前所述,由于混合键合层中的键合垫应为镜像分布,因此在设计每一存储器结构100(即存储器晶粒)及控制电路结构200(即逻辑晶粒)的布局时,可预先规划出前述第一保留区域631及第二保留区域632。

46.如图4b所示,一第一tsv 104及一第二tsv 204可分别形成于邻近第一晶圆61的第一正面61a及第二晶圆62的第二正面62a。在一些实施例中,第一tsv 104及第二tsv204是经通孔蚀刻操作而形成,而通孔的孔洞结构是经电镀操作而被导电材料所填充。在如图4b所示的操作阶段中,第一tsv 104及第二tsv 204可分别仅有一端暴露于第一晶圆61及第二晶圆62外;然而,在接续的晶圆薄化操作中(如图4f及图4i所示),第一tsv 104及第二tsv 204的两端都可分别暴露于第一晶圆61及第二晶圆62外。

47.如图4c所示,在一些实施例中,在形成第一tsv 104及第二tsv 204后,一第一金属层105可形成于第一晶圆61的第一正面61a上,以连接第一tsv104及一顶部金属106。同样地,一第二金属层205可形成于第二晶圆62的第二正面62a上,以连接第二tsv 204及一顶部金属206。

48.如图4d所示,在一些实施例中,第一混合键合层101是形成于第一晶圆61的第一正面61a上。同样地,第二混合键合层201是形成于第二晶圆62的第一正面62a上。在一些实施例中,第一混合键合层101包含如前揭图1a所示的第一键合垫102。在一些实施例中,第一混合键合层101进一步包含位在其一第一混合键合部分107的多个第一导电通孔108。换言之,第一混合键合部分107可包含一金属通孔结构以连接第一键合垫102及第一金属层105。由于第一导电通孔108可设计为具有小临界尺寸(例如具有小直径),从而为了增加产品良率,可藉由形成多个相对应于第一键合垫102的第一导电通孔108而防止因制造操作所引起的连接缺陷。第一tsv 104可经第一金属层105而耦接于第一导电通孔108的一端,且第一键合垫102可与第一导电通孔108的另一端相接触。同样地,在一些实施例中,第二混合键合层201进一步包含多个位在其一第二混合键合部分207的多个第二导电通孔208。第二tsv 204可经第二金属层205而耦接于第二导电通孔208的一端,且第二键合垫202可与第二导电通孔208的另一端相接触。该些实施例中的导电通孔可强化键合垫与tsv之间的导电性。

49.另外,在一些实施例中,第一混合键合部分107可进一步包含一第三键合垫102’,其电性断接于存储器结构100。也就是说,第三键合垫102’是一个假性键合垫,其仅用于进行混合键合而不耦接于第一金属层105。同样地,第二混合键合部分207可进一步包含一第

四键合垫202’,其是电性断接于控制电路结构200。第三键合垫102’可用于在接续的混合键合操作中,混合键合于第四键合垫202’。

50.如图4e所示,第一晶圆61是经翻转并透过一混合键合操作而堆叠于第二晶圆62上,其中,第一正面61a是面对第二正面62a,从而是执行了两者之间的「面对面」堆叠。于此堆叠,第一键合垫102是与第二键合垫202相接触而混合键结并电性连接;而第三键合垫102’则是与第四键合垫202’相接触而仅用于混合键结。在一些实施例中,第一晶圆61和第二晶圆62是在合适的条件下进行混合键合。在一些实施例中,第一tsv 104及第二tsv 204是分别形成于第一保留区域631及第二保留区域632。在混合键合操作后,可以观察到第一tsv 104及第二tsv 204是位于第一键合垫102与第二键合垫202在堆叠结构中的同一侧。

51.透过上述混合键合操作而混合键合第一晶圆61及第二晶圆62,第一晶圆61上的第一键合层101是与第二晶圆62上的第二键合层201相连接,从而获得一第一键合晶圆64。在一些实施例中,第一键合晶圆64可接续着被单体化而获得多个半导体结构,其中,每一半导体结构包含如前揭图1a所示的存储器结构100及控制电路结构200。在一些其他的实施例中,并且将于接下来的图4f至图4g所提及的,取决于产品要求和当下工艺技术的程度,还可以有其他相同于第一晶圆61的额外晶圆可以键合于第一键合晶圆64上,即借着晶圆对晶圆的封装基础而于逻辑晶粒上堆叠额外数量的存储器晶粒。

52.如图4f所示,在一些实施例中,在键合第一晶圆61及第二晶圆62后,是自第一背面61b薄化第一晶圆61而暴露出第一tsv 104。薄化操作可透过机械研磨、化学机械研磨、湿蚀刻、干蚀刻或是它们的组合而实施。在一些实施例中,第一晶圆61的厚度可以被薄化至小于50微米。

53.如图4g所示,在一些实施例中,另一第一混合键合层(例如图中所示的一第四混合键合层101b)可形成于第一键合晶圆64上并且电性连接于暴露的第一tsv 104。除此之外,如图4h所示,在一些实施例中,另一第一晶圆(例如图中所示的具有第三混合键合层101c的第三晶圆61c)可经混合键合操作而堆叠在前揭图4g所形成的第四混合键合层101b上。就第三晶圆61c的部分而言,可在第三晶圆61c上形成第三混合键合层101c前,先行于第三晶圆61c相邻于第一正面61a的处形成一第三tsv 104c。

54.第三混合键合层101c及第四混合键合层101b得经混合键合操作而相连接,且可因此获得一第二键合晶圆65。第二键合晶圆65可被薄化而暴露第三tsv 104c,以供另一轮堆叠操作之用。也就是说,存储器晶粒的堆叠,实质上就是透过重复地形成与其上具有第一混合键合层101的第一晶圆61相似的存储器晶圆,并且再次形成第一混合键合层101,直到共有四或八个晶圆经多个混合键合操作而堆叠。在该些实施例中,与第一晶圆61相似的存储器晶圆是以相同的方向进行堆叠,换言之,存储器结构的存储器晶粒是以「面对背」的排列进行堆叠。

55.如图4i所示,在一些实施例中,一顶部第一晶圆61’可省略如前揭图4f所示的薄化操作,因为其上方已不须再形成第一混合键合层。据此,一顶部第一tsv 104’可不暴露于顶部第一晶圆61’的一顶部第一背面61b’,且一顶部存储器晶粒的厚度是大于位于顶部存储器晶粒和控制电路结构200之间的至少一存储器晶粒的厚度。在一些实施例中,在存储器晶粒透过混合键合而堆叠后,是自第二背面62b薄化第二晶圆62而暴露出第二tsv 204。薄化操作可透过机械研磨、化学机械研磨、湿蚀刻、干蚀刻或是它们的组合而实施。在一些实施

例中,第二晶圆62的厚度可以被薄化至小于50微米。

56.如图4j所示,在第二晶圆62自第二背面62b薄化后,一底部金属层209可形成于第二背面62b以电性连接于第二tsv 204。接着,可设置第二导电凸块连接部401与底部金属层209相接触,以电性连接于中介板400。

57.在设置控制电路结构200及存储器结构100堆叠于中介板400前,经堆叠的第二晶圆62和第一晶圆61可被单体化而获得多个如前揭图3所示的半导体结构。如图5a所示,在一些实施例中,对键合晶圆(即第一键合晶圆64或第二键合晶圆65)的单体化操作包含执行一激光划片操作。在一些实施例中,一激光70可被用于切割堆叠晶圆的至少一部分。在一些实施例中,未薄化的晶圆(例如图4i所示的顶部第一晶圆61’)可被用于作为一块体基板,而激光划片所形成的切割道71可停止于块体基板当中。在一些实施例中,一机械切割操作可接续激光划片操作;举例而言,如图5b所示,使用一机械锯72以切穿顶部第一晶圆61’的块体基板,从而完全地分离出单一的存储器堆叠。

58.在一些实施例中,单体化第一晶圆及第二晶圆的操作可包含执行一电浆蚀刻操作。如图6a所示,一光阻层73可被设置于晶圆堆叠相反于顶部第一晶圆61’的块体基板的一侧,而一非等向电浆蚀刻可对堆叠结构形成停止于块体基板的一沟槽。如图6b所示,接续地,可在电浆蚀刻操作后接着对顶部第一晶圆61’的块体基板执行一研磨操作,从而完全地分离出单一的存储器堆叠。然而,此并非作为本实施例的限制。在另一些实施例中,可先对顶部第一晶圆61’的块体基板执行研磨操作,而后再接着对堆叠的第二晶圆62和第一晶圆61执行电浆蚀刻操作,以分离出单一的存储器堆叠。

59.透过应用上述的单体化操作,第一晶圆61、第二晶圆62、位于第一晶圆61和第二晶圆62之间的第一混合键合结构10及位于相邻的第一晶圆61之间的第二混合键合结构20,可被完全地分离而获得包含上述结构的多个半导体结构。在一些实施例中,如图7所示,存储器结构100具有一第一侧表面100c’,第一混合键合结构10具有一第二侧表面10c,及控制电路结构200具有一第三侧表面200c;其中,第一侧表面100c’、第二侧表面10c及第三侧表面200c于一剖视角度实质上具有一连续线的特征。另外,出自于单体化操作的缘故,此连续线可能因为激光划片或电浆蚀刻所产生的切割边缘并非完美的垂直,意即在大多数的案例中可能切割形成锥形沟槽,从而使得连续线包含一斜度。在切割完成后,锥形沟槽即转变为在存储器结构100、第一混合键合结构10及控制电路结构200等侧表面处可观察到的斜度。

60.如图8所示,在一些实施例中,逻辑晶粒(即控制电路结构200)及存储器晶粒100a、100b、100c、100d可皆为「面对背」的排列(方案ii)。在这些实施例中,逻辑晶粒当中用于tsv的保留区域即实质上相同于存储器晶粒当中用于tsv的保留区域,且如前所提及的,第一tsv 104、第二tsv 204是位于特定的一对键合垫的同一侧。另外,在具有方案ii的堆叠排列的实施例中,在前揭图1所示的第二表面201a是较靠近于控制电路结构200的前段制程结构,并且较远离控制电路结构200的后段制程结构。

61.图9a及图9b展示了制备图8的半导体结构的步骤。如图9a及图9b所示,第二晶圆62可在形成第二混合键合层201于其上之前,先于第二背面62b被薄化而于暴露第二tsv 204。之后,底部金属层209可形成于第二正面62a以电性连接于暴露的第二tsv 204。进一步地,在该些实施例中,第二晶圆62是经翻转以形成第二混合键合层201于第二晶圆62的第二背面62b,且第二混合键合层201可接着与第一晶圆61的第一正面61a上的第一混合键合层101

混合键合。此处所提及的混合键合操作是相同于前述的混合键合操作,并展示于前揭图4e。进一步关于透过混合键合堆叠与第一晶圆61相同的数个额外晶圆、形成第二导电凸点连接部401及晶圆的切割操作,则可参考前揭图4f至图4j,为简洁起见而在此省略。

62.如图10所示,在一些实施例中,每一存储器结构及控制电路结构都是透过中段钻孔制程(via

‑

middle process)所制造;该中段钻孔制程在部分实施例中也被称为前钻孔制程(via

‑

first process)。经中段钻孔制程,tsv的形成是执行于晶体管形成之后,并且早于后段制程操作;也就是说,通孔蚀刻和通孔填充等操作都是实施于前段制程结构形成之后,但先于后段制程阶段的金属化前。

63.在该些实施例中,混合键合的逻辑晶粒和存储器晶粒可以如前揭的方案i和方案ii的形式进行安排。详言之,如图10所示,逻辑晶粒(即控制电路结构200)及存储器晶粒100a是以「面对面」的排列为堆叠,而存储器结构中的存储器晶粒100a、100b、100c、100d则是以「面对背」的排列为堆叠(方案i)。因为控制电路结构200当中的第二tsv 204是经中段钻孔制程或前钻孔制程而形成,因此其已电性连接于控制电路结构200当中的一金属化结构210的一底部。就控制电路结构200已以「面对面」的排列堆叠于存储器晶粒100a上的情况而言,形成于第二晶圆的第二正面62a上的第二混合键合层201’可省略形成第二金属层205(如前揭图3所示);取而代之的,如图11a及图11b所示,第二导电通孔208可形成于接近第二晶圆的第二正面62a之处,并且接触金属化结构210的顶部金属206。类似地,形成于第一晶圆的第一正面61a上的第一混合键合层101’可省略形成第一金属层105(如前揭图3所示);取而代之的,第一导电通孔108可形成于接近第一晶圆的第二正面61a之处,并且接触金属化结构的顶部金属106。

64.如图10所示,与形成于晶圆正面上的第一混合键合层101’和第二混合键合层201’所相反,形成于第一晶圆的第一背面61b的第一混合键合层101和第二晶圆的第二背面62b仍可分别具有第一金属层105及底部金属层209串接tsv至相对应的键合垫。进一步关于透过混合键合堆叠与第一晶圆相同的数个额外晶圆、形成第二导电凸点连接部401及晶圆的切割操作,则可参考前揭图4f至图4j,为简洁起见而在此省略。

65.如图12所示,在一些实施例中,逻辑晶粒(即控制电路结构200)及存储器结构中的存储器晶粒100a、100b、100c、100d皆是经中段钻孔制程或前钻孔制程而形成,并且以「面对背」的排列为堆叠(方案ii)。在这些实施例中,由于是「面对背」的排列,如图13a及图13b所示,第二混合键合层201可形成在第二晶圆62的第二背面62b上,并且其中包含第二金属层205。此第二混合键合层201可用于混合键合于形成在第一晶圆61的第一正面61a上的第一混合键合层101’,并且此第一混合键合层101’不包含第一金属层105。进一步关于透过混合键合堆叠更多第一晶圆、形成第二导电凸点连接部401及底部金属层209及晶圆的切割操作,则可参考前揭图4f至图4j,为简洁起见而在此省略。

66.在一些实施例中,逻辑晶粒的tsv结构可透过背面tsv制程而形成。也就是说,如图14所示,控制电路结构200中的一背面tsv(btsv)是在控制电路结构200及存储器晶粒100a是以「面对面」的排列而堆叠后才形成,而存储器结构中的存储器晶粒100a、100b、100c、100d则是以「面对背」的排列而堆叠(方案i)。参考如图15a、图15b及图15c所示的结构变化,在一些实施例中,在控制电路结构200及存储器晶粒100a、100b、100c、100d经混合键合操作而堆叠后(如图15a),第二晶圆62即接着自其第二背面62b被薄化(如图15b)。在一些实施例

中,第二晶圆62经薄化而使得其在第二晶圆62的后段制程结构中的第一金属层2102(例如图示中底部的金属层)与第二晶圆的第二背面62b之间的厚度小于约10微米。接续地,一通孔蚀刻和一通孔填充操作实施于第二晶圆62的第二背面62b以形成btsv 211,其是电性连接于金属化结构210。进一步关于透过混合键合堆叠第一晶圆的细节、形成第二导电凸点连接部401及底部金属层209及晶圆的切割操作,则可参考前揭图4f至图4j,为简洁起见而在此省略。

67.如图10、图12及图14所示,在一些实施例中,第二tsv 204实质上是为半穿透通孔,其一端是与后端制程结构相接触,例如后段制程金属线。

68.简言之,基于上述提及的诸多实施例,形成存储器堆叠的制程效率可以被显著地提高,且肇因于微凸块操作所产生的堆叠缺陷的风险也大幅地降低。除此之外,相较于现有工艺,本揭露使用大量的键合垫以连接存储器结构和控制电路结构,以及使用大量的键合垫连接存储器结构,也可以增加现有存储器系统的存储器存取频宽。

69.在一个例示性态样中,本揭露提供一种半导体结构。该半导体结构包含:一第一混合键合结构、一存储器结构及一控制电路结构。该第一混合键合结构具有一第一表面和一第二表面。该存储器结构是接触该第一表面。该控制电路结构是用于控制该存储器结构,该控制电路结构是接触该第二表面。

70.在另一个例示性态样中,本揭露提供一种系统级封装结构。该系统级封装结构包含一第一半导体结构、一第二半导体结构及一基板。该第一半导体结构具有一第一临界尺寸。该第二半导体结构是与该第一半导体结构相堆叠。该第二半导体结构具有一第二临界尺寸且经一混合键合界面而与该第一半导体结构相接触。该基板是经一第一导电凸块而电性连接于该第一半导体结构及该第二半导体结构。该第一临界尺寸不同于该第二临界尺寸。

71.在再一个例示性态样中,本揭露提供一种制造多个半导体结构的方法。其包含以下步骤:一第一混合键合层形成于具有多个第一存储器结构的一第一晶圆上;一第二混合键合层形成于具有多个控制电路结构的一第二晶圆上;该第一晶圆及该第二晶圆经由一第一混合键合步骤而键合,以连接该第一混合键合层及该第二混合键合层,因此取得一第一键合晶圆;及至少该第一晶圆、该第二晶圆、该第一混合键合层及该第二混合键合层被单体化而取得多个半导体结构。

72.前述内容概述数项实施例的结构,使得熟习此项技术者可更佳地理解本揭露的态样。熟习此项技术者应了解,其等可容易地使用本揭露作为用于设计或修改其他制程及结构的一基础以实行本文中介绍的实施例的相同目的及/或达成相同优点。熟习此项技术者亦应了解,此等等效构造不背离本揭露的精神及范畴,且其等可在不背离本揭露的精神及范畴的情况下在本文中作出各种改变、置换及更改。

73.符号说明

74.10:第一混合键合结构

75.10c:第二侧表面

76.20:第二混合键合结构

77.61:第一晶圆

78.61’:顶部第一晶圆

79.61a:第一正面

80.61b:第一背面

81.61b’:顶部第一背面

82.62:第二晶圆

83.62a:第二正面

84.62b:第二背面

85.64:第一键合晶圆

86.65:第二键合晶圆

87.70:激光

88.71:切割道

89.72:机械锯

90.73:光阻层

91.80:半导体结构

92.81:正面

93.82:背面

94.83:半导体基板

95.84:前段制程结构

96.85:后段制程结构

97.100:存储器结构

98.100’:第一半导体结构

99.100a:存储器晶粒

100.100b:存储器晶粒

101.100c:存储器晶粒

102.100c’:第一侧表面

103.100d:存储器晶粒

104.101:第一混合键合层

105.101’:第一混合键合层

106.101a:第一表面

107.101b:第四混合键合层

108.101c:第三混合键合层

109.102:第一键合垫

110.102’:第三键合垫

111.103:第一氧化物部分

112.104:第一tsv

113.104’:顶部第一tsv

114.104c:第三tsv

115.105:第一金属层

116.106:顶部金属

117.107:第一混合键合部分

118.108:第一导电通孔

119.200:控制电路结构

120.200’:第二半导体结构

121.200c:第三侧表面

122.201:第二混合键合层

123.201’:第二混合键合层

124.201a:第二表面

125.202:第二键合垫

126.202’:第四键合垫

127.203:第二氧化物部分

128.204:第二tsv

129.205:第二金属层

130.206:顶部金属

131.207:第二混合键合部分

132.208:第二导电通孔

133.209:底部金属层

134.210:金属化结构

135.2102:第一金属层

136.211:btsv

137.300:第三半导体结构

138.400:中介板

139.401:第二导电凸块连接部

140.500:基板

141.501:第一导电凸块连接部

142.631:第一保留区域

143.632:第二保留区域

144.1201:混合键合界面

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。