1.本发明涉及电子基板。

背景技术:

2.已知一种安装有多个半导体部件(mcu

‑

chip,ddr2

‑

sdram)的多芯片模块基板(参照专利文献1)。在专利文献1中,在多芯片模块基板上设置有电源层。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2011-96268号公报

技术实现要素:

6.发明要解决的问题

7.通常,由于电源层(plane)与半导体部件的所有电源供给用的球形电极连接,因此在导体层上占据较大的范围。由于这样的电源层会妨碍信号线等其他布线图案,因此需要设置用于电源层的专用的导体层。因此,存在基板的层数增加的问题。尤其是,在专利文献1中,由于电源层遍布多个半导体部件的球形电极设置,因此电源层在导体层上占据较大的范围。

8.本发明是鉴于上述问题而提出的,其目的在于,提供一种能够减少电子基板的层数的技术。

9.用于解决问题的手段

10.为了实现所述目的,本发明的电子基板经由在表面阵列状地配置的多个表面端子与半导体部件连接,并且经由在背面阵列状地配置的多个背面端子与主基板连接,其中,电子基板包括:第一布线,在电子基板内电连接表面端子和背面端子,并且从主基板经由背面端子供给电源;以及第二布线,在电子基板内电连接表面端子和背面端子,从主基板经由背面端子供给与第一布线相同电位的电源,并且在电子基板内不与第一布线电连接。

11.在构成为如上所述的本发明中,通过与第一布线连接的表面端子和与第二布线连接的表面端子两方,能够向半导体部件供给相同电位的电源。在此,由于第一布线和第二布线不在电子基板内电连接,因此可以在电子基板内不形成将与第一布线连接的表面端子和与第二布线连接的表面端子电连接的布线图案。即,能够在电子基板内减少电源的布线图案,从而能够提高信号线等其他布线图案的自由度。其结果,能够省略用于电源的布线图案的专用的导体层,从而能够减少电子基板的层数。

附图说明

12.图1是电子基板的剖面示意图。

13.图2a是电子基板的表面透视图,图2b是电子基板的背面透视图。

14.图3a是电子基板的表面透视图,图3b是电子基板的背面透视图。

15.图4是电子基板的剖面示意图。

具体实施方式

16.在此,按照下述顺序,对本发明的实施方式进行说明。

17.(1)第一实施方式:

18.(2)第二实施方式:

19.(3)第三实施方式:

20.(4)其他实施方式:

21.(1)第一实施方式:

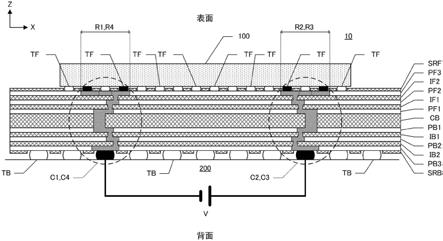

22.图1是本发明的一个实施方式的电子基板10的剖面示意图。电子基板10是矩形板状的他层基板,在厚度方向z上层叠有多个层。将电子基板10的厚度方向z的一方(纸面上方)定义为表面,而将厚度方向z的另一方(纸面下方)定义为表面。电子基板10包括6层导体层pf1、pf2、pf3、pb1、pb2、pb3和7层绝缘层cc、if1、if2、srf、ib1、ib2、srb。本实施方式的电子基板10是在作为芯基板的绝缘层cc上层叠有各层的双面积层基板。但是,电子基板10可以是单面基板,也可以是不具有芯基板的基板。电子基板10的层数不限定于图1例示的层数。

23.在导体层pf1、pf2、pf3、pb1、pb2、pb3形成有平面方向xy(厚度方向z的正交方向)的布线图案。布线图案的形成方法没有特别的限定,例如可以通过加成法或部分加成法或减成法形成。在绝缘层cc上形成有通孔(through hole),导体层pf1、pb1通过形成于通孔的通孔导体电连接。通孔导体可以覆盖通孔的壁面,也可以填充通孔的内部。

24.在绝缘层if1上形成有导通孔(vias),导体层pf1、pf2通过绝缘层if1的导通孔电连接。同样地,导体层pf2、pf3通过绝缘层if2的导通孔电连接,导体层pb1、pb2通过绝缘层ib1的导通孔电连接,导体层pb2、pb3通过绝缘层ib2的导通孔电连接。导通孔的形成方法没有特别的限定,例如导通孔可以是光刻导通孔,也可以是激光导通孔。

25.表面侧的绝缘层srf是阻焊层,形成在最表面侧的导体层pf3上。在绝缘层srf形成有多个开口部,并且在多个开口部中分别形成有表面端子tf。表面端子tf是通过焊料等形成的凸块,用于将半导体部件100以倒装芯片的方式安装于电子基板10上。

26.背面侧的绝缘层srb也是阻焊层,形成在最背面侧的导体层pb3上。在绝缘层srb形成有多个开口部,并且在多个开口部中分别形成有背面端子tb。背面端子tb是通过焊料等形成的焊球,用于将电子基板10表面安装于主基板200。需要说明的是,电子基板10以安装了半导体部件100的状态安装于主基板200。

27.图2a示出了电子基板10的表面。在图2a中,表面端子tf由白圆圈或黑圆圈示出。如图2a所示,多个表面端子tf在电子基板10的表面上以阵列状配置。表面端子tf配置为在平面方向xy的各个方向上隔开恒定的凸块间距d。

28.图2b示出了电子基板10的背面。图2b示出了将电子基板10从图2a的状态绕y轴翻转过来的状态。在图2b中,背面端子tb由白圆圈或黑圆圈示出。如图2b所示,多个背面端子tb在电子基板10的背面上以阵列状配置。需要说明的是,图1是图2a、图2b的向视线a

‑

a、b

‑

b(点划线)线的向视剖视图。

29.如上所述,电子基板10经由在表面上以阵列状配置的多个表面端子tf而与半导体

部件100连接。另外,电子基板10经由在背面上以阵列状配置的多个背面端子tb而与主基板200连接。

30.在主基板200形成有生成用于向半导体部件100供给到的电源v的电源电路(未图示)。在图1中,假想地示出了用于将电源v供给到电子基板10的电路的电路图。电源v供给到在图1、图2b中由黑色示出的四个背面端子tb中的每一个。

31.电子基板10包括第一布线c1、第二布线c2、第三布线c3以及第四布线c4,作为与电源v连接的布线。第一布线c1至第四布线c4分别是,使表面端子tf和背面端子tb在电子基板10内电连接,并且使电源从主基板200经由背面端子tb进行供给的一体导体。第一布线c1至第四布线c4在电子基板10内彼此没有电连接。

32.需要说明的是,第一布线c1至第四布线c4具有在平面方向xy上关于中心点g旋转对称的结构,向视线a

‑

a、b

‑

b的剖面能在共同的剖视图(图1)示出。在图1中,利用灰色和黑色示出了第一布线c1至第四布线c4。如图1所示,第一布线c1至第四布线c4分别由在导体层pf1、pf2、pf3、pb1、pb2、pb3的平面方向xy上形成的布线图案、形成于绝缘层if1、if2、ib1、ib2的导通孔、形成于绝缘层cc的通孔导体、表面端子tf和背面端子tb构成。需要说明的是,在图1中,对第一布线c1至第四布线c4以外的布线省略了图示。

33.在图2a、图2b中,由灰色示出了第一区域r1至第四区域r4(透视图),该第一区域r1至第四区域r4是在最表面侧的导体层pf3形成有用于构成第一布线c1至第四布线c4的布线图案的区域。在导体层pf3的布线图案中,在表面侧的绝缘层srf(阻焊层)的开口部形成凸块的部位就是表面端子tf。第一布线c1至第四布线c4分别与由黑色示出的五个表面端子tf电连接。用于向半导体部件100供给电源v的表面端子tf总共有二十个。

34.在此,在电子基板10的平面方向xy上可以定义有一条直线l1,该直线l1用于对与第一布线c1连接的表面端子tf所分布的第一区域r1和与第二布线c2、第四布线c4连接的表面端子tf所分布的第二区域r2、第四区域r4进行分隔。另外,可以定义一条直线l2,该直线l2用于对与第一布线c1连接的表面端子tf所分布的第一区域r1和与第三布线c3、第四布线c4连接的表面端子tf所分布的第三区域r3、第四区域r4进行分隔。

35.这样,通过使第一区域r1和第二区域r2能够由一条直线l1分隔,能够防止与第一布线c1连接的表面端子tf和与第二布线c2连接的表面端子tf错综复杂地存在于电子基板10的表面上。由此,能够使导体层中的第一布线c1的布线图案和第二布线c2的布线图案不形成为复杂的形状,并且能够提高信号线等其他布线图案的自由度。

36.与第一布线c1连接的表面端子tf彼此之间的距离中的最大值为d2 (2d)2的平方根,约2.24d。分别与第二布线c2至第四布线c4连接的表面端子tf彼此之间的距离中的最大值也是约2.24d。

37.另一方面,与第一布线c1连接的表面端子tf和与第二布线c2连接的表面端子tf之间的距离中的最小值为7d。同样地,与第一布线c1连接的表面端子tf和与第三布线c3连接的表面端子tf之间的距离中的最小值也是7d,与第二布线c2连接的表面端子tf和与第四布线c4连接的表面端子tf之间的距离中的最小值也是7d,与第三布线c3连接的表面端子tf和与第四布线c4连接的表面端子tf之间的距离中的最小值也是7d。另外,与第一布线c1连接的表面端子tf和与第四布线c4连接的表面端子tf之间的距离中的最小值为(7d)2 (7d)2的平方根,约9.90d。同样地,与第二布线c2连接的表面端子tf和与第三布线c3连接的表面端

子tf之间的距离中的最小值也是约9.90d。

38.如上所述,与第一布线c1连接的表面端子tf彼此之间的距离以及与第二布线c2连接的表面端子tf彼此之间的距离,比与第一布线c1连接的表面端子tf和与第二布线c2连接的表面端子tf之间的距离短。同样地,与第一布线c1连接的表面端子tf彼此之间的距离以及与第三布线c3连接的表面端子tf彼此之间的距离,比与第一布线c1连接的表面端子tf和与第三布线c3连接的表面端子tf之间的距离短。与第一布线c1连接的表面端子tf彼此之间的距离以及与第四布线c4连接的表面端子tf彼此之间的距离,比与第一布线c1连接的表面端子tf和与第四布线c4连接的表面端子tf之间的距离短。

39.进而,与第二布线c2连接的表面端子tf彼此之间的距离以及与第三布线c3连接的表面端子tf彼此之间的距离,比与第二布线c2连接的表面端子tf和与第三布线c3连接的表面端子tf之间的距离短。与第二布线c2连接的表面端子tf彼此之间的距离以及与第四布线c4连接的表面端子tf彼此之间的距离,比与第二布线c2连接的表面端子tf和与第四布线c4连接的表面端子tf之间的距离短。与第三布线c3连接的表面端子tf彼此之间的距离以及与第四布线c4连接的表面端子tf彼此之间的距离,比与第三布线c3连接的表面端子tf和与第四布线c4连接的表面端子tf之间的距离短。

40.这样,通过使彼此接近的表面端子tf与第一布线c1连接,能够减少用于第一布线c1的布线图案(第一区域r1)的面积,并且能够提高信号线等其他布线图案的自由度。同样地,通过分别使彼此接近的表面端子tf与第二布线c2至第四布线c4连接,能够减少用于第二布线c2至第四布线c4的布线图案(第二区域r2至第四区域r4)的面积。

41.进而,在电子基板10的平面方向xy上,与第一布线c1连接的背面端子tb位于与第一布线c1连接的表面端子tf所分布的第一区域r1的内侧。如图1、图2b所示,与第一布线c1连接的背面端子tb位于,在最表面侧的导体层pf3中形成有构成第一布线c1的布线图案的第一区域r1的正下方。这是因为,第一布线c1在最表面侧的导体层pf3以外的层,形成为几乎仅在厚度方向z上连接导体的布线。同样地,在电子基板10的平面方向xy上,与第二布线c2至第四布线c4连接的背面端子tb,分别位于在最表面侧的导体层pf3中与第二布线c2至第四布线c4连接的表面端子tf所分布的第二区域r2至第四区域r4的内侧。

42.由此,能够使与第一布线c1至第四布线c4连接的背面端子tb配置在与第一布线c1至第四布线c4连接的表面端子tf所分布的第一区域r1至第四区域r4的正下方。其结果,能够缩短第一布线c1至第四布线c4的布线长度,并且能够减少第一布线c1至第四布线c4的电阻。

43.在以上说明的本实施方式中,通过与第一布线c1连接的表面端子tf和与第二布线c2连接的表面端子tf两方,能够向半导体部件100供给相同电位的电源v。在此,由于第一布线c1和第二布线c2在电子基板10内不电连接,因此无需在电子基板10内形成使与第一布线c1连接的表面端子tf和与第二布线c2连接的表面端子tf电连接的布线图案。即,能够在电子基板10内减少电源v的布线图案,从而能够提高信号线等其他布线图案的自由度。其结果,能够省略用于电源的布线图案的专用的导体层,从而能够减少电子基板10的层数。

44.需要说明的是,在电子基板10内,除了第一布线c1至第四布线c4以外,还设置有信号线等布线图案(未图示)。在最表面侧的导体层pf3中,这些信号线等其他布线图案必须以避开第一区域r1至第四区域r4的方式形成。信号线等其他布线图案中的大部分从中心点g

沿放射方向走线,但第一区域r1至第四区域r4在放射方向形成为细长的形状(放射方向上的长度大于与放射方向正交的方向上的长度的形状),因此能够降低第一区域r1至第四区域r4妨碍信号线等其他布线图案的可能性。另外,如上所述,第一布线c1至第四布线c4在最表面侧的导体层pf3以外的层,形成为几乎仅在厚度方向z上连接导体的布线,因此能够使信号线等其他布线图案在导体层pf3以外的导体层pf2、pf1、pb1、pb2、pb3自由布线。

45.另外,第一布线c1至第四布线c4具有在平面方向xy上关于中心点g旋转对称的结构,因此能够使第一布线c1至第四布线c4的电气特性(电阻等)大致一致,从而能够向半导体部件100均匀地供给电源。

46.(2)第二实施方式:

47.图3a、图3b示出了第二实施方式的电子基板1010的表面和背面。在本实施方式中,在最表面侧的导体层pf3也形成有构成第一布线c1和第二布线c2的布线图案。在导体层pf3的布线图案中,将在存在被供给电源v的表面端子tf(黑圆圈)的部位形成的部分表示为第一基本区域r1和第二基本区域r2,并且用深灰色图示出该第一基本区域r1和第二基本区域r2(透视图)。另外,在导体层pf3的布线图案中,将在不存在被供给电源v的表面端子tf的部位形成的部分表示为第一扩张区域k1和第二扩张区域k2,并且用浅灰色图示出该第一扩张区域k1和第二扩张区域k2(透视图)。

48.第一基本区域r1和第一扩张区域k1构成为一体的布线图案,第二基本区域r2和第二扩张区域k2也构成为一体的布线图案。在第一扩张区域k1和第二扩张区域k2中,不与第一扩张区域k1和第二扩张区域k2连接的一侧的端部和背面端子tb(黑圆圈),经由导通孔或通孔导体在厚度方向z上连接。

49.在本实施方式中,在电子基板1010的平面方向xy上,与第一布线c1连接的背面端子tb位于与第一布线c1连接的表面端子tf所分布的第一基本区域r1的外侧。同样地,与第二布线c2连接的背面端子tb也位于与第二布线c2连接的表面端子tf所分布的第二基本区域r2的外侧。由此,可以在电子基板1010的外缘附近配置与第一布线c1和第二布线c2连接的背面端子tb。相反地,可以将与信号线等连接的背面端子tb配置于电子基板1010的中央附近。需要说明的是,第一扩张区域k1和第二扩张区域k2也可以不形成在与第一基本区域r1和第二基本区域r2相同的导体层pf3,而是可以形成在与第一基本区域r1和第二基本区域r2不同的导体层pf2、pf1、pb1、pb2、pb3上。

50.(3)第三实施方式:

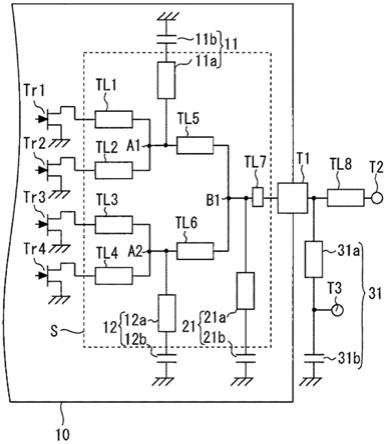

51.图4是第三实施方式的电子基板2010的剖面示意图。电子基板2010是mcm(multi

‑

chip module:多芯片模块)基板,在电子基板2010的表面上安装有第一半导体部件100a和第二半导体部件100b。并且,第一布线c1连接于与第一半导体部件100a连接的表面端子tf和与第二半导体部件100b连接的表面端子tf两方。由此,能够经由第一布线c1向第一半导体部件100a和第二半导体部件100b两方供给电源v。

52.(4)其他实施方式:

53.以上,例示了与电源v连接的布线的个数为四个和两个的电子基板10、1010、2010,但只要供给电源v的布线的个数为两个以上即可。另外,供给电源v的布线的形状也可以不是彼此对称的形状。另外,与供给电源v的布线连接的表面端子tf的个数也可以不必一定相等。进而,与供给电源v的布线连接的背面端子tb的个数也可以是两个以上。

54.本发明的电子基板是在厚度方向上的一侧具有表面,而在厚度方向上的另一侧具有背面的基板,并且是在其表面以倒装芯片的方式安装有半导体部件的基板。表面端子可以在面方向上配置为阵列状,并且可以经由凸块与半导体部件连接。凸块只要具有导电性即可,材料不受限制。另一方面,同样地,背面端子可以在面方向上配置为阵列状,并且可以形成焊球(bga),或者也可以形成针脚(pga),或者也可以是栅格(lga)。

55.电子基板只要是具有导体层和绝缘层的基板即可,导体层和绝缘层的形成方法不受特别限制。第一布线和第二布线分别是在电子基板内电连接表面端子和背面端子的一体导体,由导体层中的面内布线和绝缘层中的层间布线构成。面内布线是指面方向上的布线图案,而层间布线是厚度方向上的布线(导通孔、通孔等)。

56.第一布线和第二布线可以从主基板供给相同电位的电源,可以构成为主基板向与第一布线和第二布线连接的背面端子分别供给相同电位的电源。第一布线和第二布线可以不在电子基板内电连接,当然,也可以经由半导体部件内的布线或主基板内的布线电连接。另外,第一布线和第二布线分别连接的表面端子的个数不受特别限制。同样地,第一布线和第二布线分别连接的背面端子的个数不受特别限制。

57.除了第一布线和第二布线以外,还可以设置有具有与第一布线和第二布线同样的结构的第n布线(n为3以上的整数)。并且,第n布线可以构成为,使表面端子和背面端子在电子基板内电连接,从主基板经由背面端子供给与第一布线相同电位的电源,并且在电子基板内,不与第一布线至第(n

‑

1)布线中的任一个电连接。

58.另外,在电子基板的面方向上,可以定义对与第一布线连接的表面端子所分布的第一区域和与第二布线连接的表面端子所分布的第二区域进行分隔的一条直线。这样,通过使第一区域和第二区域由一条直线分隔,能够防止与第一布线连接的表面端子和与第二布线连接的表面端子错综复杂地存在于电子基板的表面上不复杂。由此,能够使导体层中的第一布线的布线图案和第二布线的布线图案不形成为复杂的形状,并且能够提高信号线等其他布线图案的自由度。

59.进而,与第一布线连接的表面端子彼此之间的距离以及与第二布线连接的表面端子彼此之间的距离,可以比与第一布线连接的表面端子和与第二布线连接的表面端子之间的距离短。这样,通过使彼此接近的表面端子构成为与第一布线连接的表面端子,能够减少用于第一布线的布线图案的面积,并且能够提高信号线等其他布线图案的自由度。同样地,通过使彼此接近的表面端子构成为与第二布线连接的表面端子,能够减少用于第二布线的布线图案的面积。

60.另外,第一半导体部件和第二半导体部件可以安装于电子基板,第一布线可以连接于与第一半导体部件连接的表面端子和与第二半导体部件连接的表面端子两方。由此,能够经由第一布线向第一半导体部件和第二半导体部件两方供给电源。当然,不仅是第一布线,第二布线也可以连接于与第一半导体部件连接的表面端子和与第二半导体部件连接的表面端子两方。

61.进而,在电子基板的面方向上,与第一布线连接的背面端子可以位于与第一布线连接的表面端子所分布的第一区域的内侧。由此,能够使与第一布线连接的背面端子配置在与第一布线连接的表面端子所分布的第一区域的正下方。其结果,能够缩短第一布线的布线长度,并且能够减少第一布线的电阻。

62.另外,在电子基板的面方向上,与第一布线连接的背面端子也可以位于与第一布线连接的表面端子所分布的第一区域的外侧。由此,可以在例如电子基板的外缘附近配置与第一布线连接的背面端子。相反地,可以将与信号线等连接的背面端子配置于电子基板的中央附近。

63.附图标记说明

64.10、1010、2010:电子基板

65.100、100a、100b:半导体部件

66.200:主基板

67.c1~c4:第一布线~第四布线

68.g:中心点

69.srb、ib1~ib2、cc、if1~if2、srf:绝缘层

70.pb1~pb3、pf1~pf3:导体层

71.r1~r4:第一区域~第四区域

72.tb:背面端子

73.tf:表面端子

74.v:电源

75.d:凸块间距

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。