1.本公开涉及高频放大器,特别是涉及以多赫蒂放大器为代表的高频放大器。

背景技术:

2.作为被用于无线通信等的高效率的高频放大器,已知将进行ab类动作或者b类动作的载波放大器、和进行c类动作的峰值放大器组合而构成的多赫蒂放大器。在多赫蒂放大器中,在输出功率低的动作区域中,仅载波放大器进行动作,在输出功率高的动作区域中,载波放大器和峰值放大器这双方进行动作,载波放大器以及峰值放大器的输出信号被合成。

3.为了输出信号的合成,在多赫蒂放大器中,具有通信频带中的中心频率的1/4波长的电长度的第一传输线路被连接于载波放大器的输出端子和峰值放大器的输出端子之间。在此,作为使用1/4波长的第一传输线路的问题,可列举载波放大器的负载阻抗分散导致的宽带域特性的降低、和高频功率的损失增加导致的效率的降低、还有传输线路变长导致的电路的大型化。另外,某电路元件的“负载阻抗”是,从该电路元件向输出侧(也就是说,负载侧)观察的阻抗。此外,“分散”意味着频率依赖性,“分散”是指频率依赖性变大。

4.因此,以往,为了实现多赫蒂放大器的宽带域化,各种各样的技术被提出(例如,参考专利文献1)。

5.在专利文献1的技术中,具有通信频带中的中心频率的1/2波长的电长度的第二传输线路被连接于第一传输线路和峰值放大器的输出端子之间。由此,在峰值放大器不进行动作的多赫蒂放大器的输出功率低的动作区域中,载波放大器的负载阻抗的频率特性被补偿,多赫蒂放大器的宽带域特性被改善。

6.现有技术文献

7.专利文献

8.专利文献1:日本特开2014

‑

197755号公报

技术实现要素:

9.发明要解决的课题

10.但是,在专利文献1的技术中,在载波放大器和峰值放大器这双方进行动作的多赫蒂放大器的输出功率高的动作区域中,由于载波放大器的输出信号不流过第二传输线路,载波放大器的负载阻抗的频率特性不被补偿。因此,在这样的输出功率高的动作区域中,依然,在多赫蒂放大器的宽带域特性的降低上有问题。此外在专利文献1的技术中,在多赫蒂放大器的效率的降低、和电路的大型化上残留问题。另外,放大器的“效率”是指,功率变换效率(也就是说,输出功率相对于输入功率之比)。

11.因此,本公开的目的在于,提供与以往相比能够更宽带域、高效率以及小型的高频放大器。

12.用于解决课题的手段

13.为了达成上述目的,本公开的一方式所涉及的高频放大器是,对规定的频带的第一信号以及第二信号进行放大而从输出端子输出信号的高频放大器,其中,具备:第一放大器,对所述第一信号进行放大;第二放大器,对所述第二信号进行放大;第一匹配电路,被连接于所述第一放大器的输出端子;第二匹配电路,被连接于所述第二放大器的输出端子;第一传输线路,被连接于所述第一匹配电路的输出端子和所述第二匹配电路的输出端子之间且具有小于所述规定的频带的中心频率的1/4波长的电长度;第二传输线路,被连接于所述第一放大器以及所述第二放大器之中的一方的输入端子且具有小于所述规定的频带的中心频率的1/4波长的电长度;以及第三传输线路,被连接于所述第一传输线路的一端和所述输出端子之间且具有所述规定的频带的中心频率的1/4波长的电长度,被连接于所述第一放大器以及所述第二放大器之中的另一方的输出端子的所述第一匹配电路或者所述第二匹配电路带来的相位旋转与所述第一传输线路带来的相位旋转相反朝向。

14.此外,为了达成上述目的,本公开的其他一方式所涉及的高频放大器是,对规定的频带的第一信号以及第二信号进行放大而从输出端子输出信号的高频放大器,其中,具备:基板;一或者二个半导体芯片,被安装在所述基板上;第一放大器,被形成于所述半导体芯片,对所述第一信号进行放大;第二放大器,被形成于所述半导体芯片,对所述第二信号进行放大;第八传输线路,被形成于所述半导体芯片,一端被连接于所述第一放大器的输出端子;第九传输线路,被形成于所述半导体芯片,一端被连接于所述第二放大器的输出端子;第一电容器,被形成于所述半导体芯片;第二电容器,被形成于所述半导体芯片;第四传输线路,被形成于所述基板上,一端被连接于所述第八传输线路的另一端;第五传输线路,被形成于所述基板上,一端被连接于所述第九传输线路的另一端;第一传输线路,被形成于所述基板上,被连接于所述第四传输线路的一端和所述第五传输线路的一端之间且具有小于所述规定的频带的中心频率的1/4波长的电长度;第二传输线路,被连接于所述第一放大器或者所述第二放大器的其中一个的输入端子且具有小于所述规定的频带的中心频率的1/4波长的电长度;以及第三传输线路,被连接于所述第一传输线路的一端和所述输出端子之间且具有所述规定的频带的中心频率的1/4波长的电长度,所述第四传输线路的另一端和所述第一电容器被连接,所述第五传输线路的另一端和所述第二电容器被连接。

15.发明效果

16.通过本公开,与以往相比能够更宽带域、高效率以及小型的高频放大器被提供。

附图说明

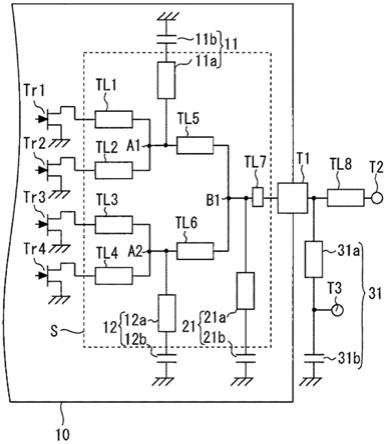

17.图1是比较例所涉及的高频放大器的电路图。

18.图2是表示比较例所涉及的高频放大器中的阻抗变换的史密斯图表。

19.图3是表示比较例所涉及的高频放大器所具备的匹配电路的相位角的图。

20.图4a是表示比较例所涉及的高频放大器中的pa接通时的zc11的史密斯图表。

21.图4b是表示比较例所涉及的高频放大器中的pa接通时的效率的频率特性的图。

22.图5a是表示比较例所涉及的高频放大器中的pa断开时的zc11的史密斯图表。

23.图5b是表示比较例所涉及的高频放大器中的pa断开时的效率的频率特性的图。

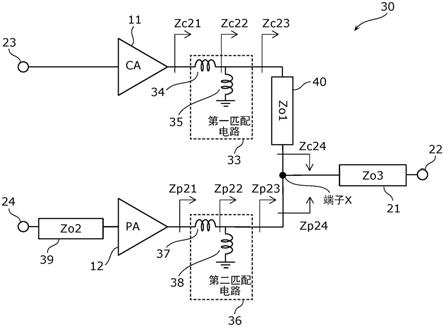

24.图6是实施方式1所涉及的高频放大器的电路图。

25.图7是表示实施方式1所涉及的高频放大器中的阻抗变换的史密斯图表。

26.图8是表示实施方式1所涉及的高频放大器所具备的匹配电路的相位角的图。

27.图9a是表示实施方式1所涉及的高频放大器中的pa接通时的zc21的史密斯图表。

28.图9b是表示实施方式1所涉及的高频放大器中的pa接通时的效率的频率特性的图。

29.图10a是表示实施方式1所涉及的高频放大器中的pa断开时的zc21的史密斯图表。

30.图10b是表示实施方式1所涉及的高频放大器中的pa断开时的效率的频率特性的图。

31.图11是实施方式2所涉及的高频放大器的电路图。

32.图12是实施方式3所涉及的高频放大器的电路图。

33.图13是实施方式4所涉及的高频放大器的电路图。

34.图14是实施方式5所涉及的高频放大器的电路图。

35.图15是表示实施方式1~5所涉及的高频放大器中的负载阻抗的区域的史密斯图表。

36.图16是实施方式6所涉及的高频放大器的布局图。

37.图17是实施方式7所涉及的高频放大器的布局图。

38.图18是实施方式8所涉及的高频放大器所具备的载波放大器用以及峰值放大器用的半导体芯片的布局图。

39.图19是实施方式8所涉及的高频放大器的布局图。

具体实施方式

40.图1是比较例所涉及的高频放大器10的电路图。图中的箭头及其附近记载的标号zci、zpi(i为数字)表示从该处向箭头的方向观察时的阻抗(也就是说,负载阻抗)。高频放大器10是,对规定的频带的第一信号以及第二信号进行放大而从输出端子22输出信号的多赫蒂放大器,其具备载波放大器(ca)11、峰值放大器(pa)12、第一匹配电路13、第二匹配电路16、第一传输线路20、第二传输线路19、第三传输线路21、输出端子22、第一输入端子23以及第二输入端子24。第一匹配电路13由串联电感器14和一端被接地的并联电容器15构成。第二匹配电路16由串联电感器17和一端被接地的并联电容器18构成。另外,“串联电感器”是被插入至从输入端子至输出端子的传输路径上的电感器。此外,“并联电容器”是被连接于从输入端子至输出端子的传输路径和基准电位(也就是说,接地电位)之间的电容器。此外,“接地”不仅是直流地接地(也就是说,与基准电位直接连接),还包含高频地接地(也就是说,经由在规定的频带中成为极低的阻抗的电容器等而与基准电位连接)。

41.载波放大器11是进行ab类或者b类动作,对第一信号进行放大的放大器,在高频放大器10的输出功率的全部区域中进行动作。峰值放大器12是进行c类动作,对第二信号进行放大的放大器,在高频放大器10的输出功率高的动作区域中进行动作。

42.第一传输线路20被连接于载波放大器11的输出端子和峰值放大器12的输出端子之间,具有规定的频带的中心频率的1/4波长的电长度。第一传输线路20的特性阻抗zo1为50ω。在高频放大器10中第一传输线路20的长度为1/4波长,所以载波放大器的负载的分散大而宽带域特性的降低成为问题。此外,高频功率损失大而放大器效率的降低成为问题。此外,电路面积的增大成为问题。

43.第二传输线路19被连接于峰值放大器12的输入侧,为了补偿第一传输线路20导致的相位旋转而被设定为与第一传输线路20相同的电长度。在该情况下,第二传输线路19的长度为1/4波长,所以高频功率损失大而放大器增益的降低成为问题。此外,电路面积的增大成为问题。另外,基于某电路元件的“相位旋转”是,被输入至该电路元件的信号的相位角及从该电路元件被输出的信号的相位角之差(也就是说,(输出信号的相位角)

‑

(输入信号的相位角))。

44.现在,将第一传输线路20和第二匹配电路16的连接处设为端子x。第三传输线路21被连接于端子x和输出端子22之间,具有规定的频带的中心频率的1/4波长的电长度。第三传输线路21的特性阻抗zo3是将端子x的阻抗(例如,25ω)变换为输出端子22的阻抗(例如,50ω)的值(例如,35.36ω)。

45.在峰值放大器12进行动作时(pa接通时),zc14被设计为50ω j0ω。在峰值放大器12不进行动作时(pa断开时),zc14被设计为25ω j0ω。

46.在此,说明在高频放大器10中,对载波放大器11以及峰值放大器12分别使用了总栅极宽度3mm的gan的情况的具体的电路常数。在规定的频带的中心频率4.5ghz中,在pa接通时设定为zc11=10ω j43ω、zp11=10ω j43ω,在pa断开时设定为zc11=6ω j39ω从而得到最佳的特性。另外,针对所得到的特性,使用图4a、图4b、图5a、图5b在后面叙述。因此,将串联电感器14设定为2.2nh,将并联电容器15设定为1.4pf,将串联电感器17设定为2.2nh,将并联电容器18设定为1.4pf即可。

47.图2是表示比较例所涉及的高频放大器10中的阻抗变换的史密斯图表,更详细而言,表示基于第一匹配电路13以及第一传输线路20的阻抗变换。在图2的(a)所示的pa接通时,从zc14=50ω j0ω被变换为zc11=10ω j43ω。在此,就从zc14向zc13的变换而言,第一传输线路20的特性阻抗为50ω,所以保持50ω而不被变换。在图2的(b)所示的pa断开时,从zc14=25ω j0ω被变换为zc11=6ω j39ω。通过第一传输线路20,从zc14=25ω j0ω被变换为zc13=100ω j0ω。

48.图3是表示比较例所涉及的高频放大器10所具备的匹配电路的相位角的图。在pa接通时,zc14的相位角为0

°

,zc11的相位角为189

°

,zc14和zc11之间的相位差为189

°

(图3的实线)。同样,在pa断开时zc14和zc11之间的相位差为201

°

(图3的虚线)。都有超过180

°

的较大的相位差。在这样高频放大器10中,从端子x至载波放大器11的相位差变大,所以zc11的分散大成为问题(针对zc11的分散,通过图4a在后面叙述)。

49.图4a是表示比较例所涉及的高频放大器10中的pa接通时的zc11的分散的史密斯图表。表示频率4.3ghz、4.5ghz、4.7ghz中的zc11的分散。在zc11的分散大的情况下,例如以中心频率4.5ghz进行最佳设计的情况下,在两端的频率4.3ghz、4.7ghz中从最佳设计偏离而高频放大器10的特性降低。若观察从频率4.3ghz至4.7ghz的zc11的变化量(δzc11),则δzc11=

‑

1.4ω j6.7ω。

50.图4b表示比较例所涉及的高频放大器10中的pa接通时的效率的频率特性。在中心频率4.5ghz中得到效率70%,但在两端的频率4.3ghz和4.7ghz中,效率降低为60%。该特性的降低起因于如图4a所示δzc11较大。

51.图5a是表示比较例所涉及的高频放大器10中的pa断开时的zc11的分散的史密斯图表。若观察从频率4.3ghz至4.7ghz为止的δzc11,δzc11=

‑

1.6ω j8.6ω。从图5b,在中

心频率4.5ghz中得到效率50%,但在两端的频率4.3ghz和4.7ghz中,效率降低为42%。该特性的降低起因于δzc11较大。

52.因此,本公开的一方式所涉及的高频放大器是,对规定的频带的第一信号以及第二信号进行放大而从输出端子输出信号的高频放大器,其中,具备:第一放大器,对所述第一信号进行放大;第二放大器,对所述第二信号进行放大;第一匹配电路,被连接于所述第一放大器的输出端子;第二匹配电路,被连接于所述第二放大器的输出端子;第一传输线路,被连接于所述第一匹配电路的输出端子和所述第二匹配电路的输出端子之间且具有小于所述规定的频带的中心频率的1/4波长的电长度;第二传输线路,被连接于所述第一放大器以及所述第二放大器的一方的输入端子,具有小于所述规定的频带的中心频率的1/4波长的电长度;以及第三传输线路,被连接于所述第一传输线路的一端和所述输出端子之间且具有所述规定的频带的中心频率的1/4波长的电长度,基于被连接于所述第一放大器以及所述第二放大器的另一方的输出端子的所述第一匹配电路或者所述第二匹配电路的相位旋转与基于所述第一传输线路的相位旋转相反朝向。

53.由此,基于第一匹配电路的相位旋转与基于第一传输线路的相位旋转相反朝向,所以载波放大器的负载阻抗的分散被减少,与以往相比能够更宽带域、高效率以及小型。

54.以下,针对本公开的实施方式,使用附图详细地进行说明。另外,在以下说明的实施方式都表示本公开的一具体例。以下的实施方式所示的频率、阻抗、特性阻抗、电路元件的常数、材料等是一例,并非限定本公开的主旨。此外,各图并不一定严密地图示。在各图中,针对实质上同一结构赋予同一标号,有时省略或者简化重复的说明。规定的频带是被用于通信的频带,例如是被用于无线通信的3thz以下的频带。

55.(实施方式1)

56.图6是实施方式1所涉及的高频放大器30的电路图。高频放大器30是,对规定的频带(例如中心频率为4.5ghz的频带)的第一信号以及第二信号进行放大而从输出端子22输出信号的多赫蒂放大器,其中,具备:载波放大器11,是第一放大器的一例;峰值放大器12,是第二放大器的一例;第一匹配电路33;第二匹配电路36;第一传输线路40;第二传输线路39;第三传输线路21;输出端子22;第一输入端子23以及第二输入端子24。第一匹配电路33由串联电感器34和一端被接地的并联电感器35构成。第二匹配电路36由串联电感器37和一端被接地的并联电感器38构成。

57.被用于高频放大器30的载波放大器11以及峰值放大器12具体而言,通过由gan、gaas、sige或者si等构成的场效应管即fet或者三极管即bjt等进行高频放大的设备而构成。此外,传输线路(第一传输线路40、第二传输线路39以及第三传输线路21)例如是微带线或者带状线,通过半导体类、陶瓷类或者树脂类等被用于一般的高频电路的基板材料、和由电特性上优秀的cu等材料构成的传输高频信号的传输线而构成。在实际的电路中,并联电感器35以及38经由接地用的电容器被接地,但在本图中省略接地用的电容器。此外,省略来自电源的功率供应用的线路。

58.以下,针对本实施方式所涉及的高频放大器30,以与比较例所涉及的高频放大器10的差异为中心进行叙述。在比较例所涉及的高频放大器10中,第一匹配电路13由串联电感器14和一端被接地的并联电容器15构成,相对于此,在本实施方式所涉及的高频放大器30中,第一匹配电路33由串联电感器34和一端被接地的并联电感器35构成。此外,在比较例

所涉及的高频放大器10中,第二匹配电路16由串联电感器17和一端被接地的并联电容器18构成,相对于此,在本实施方式所涉及的高频放大器30中,第二匹配电路36由串联电感器37和一端被接地的并联电感器38构成。另外,“并联电感器”是,被连接于从输入端子至输出端子的传输路径和基准电位(也就是说,接地电位)之间的电感器。

59.在此,针对本实施方式所涉及的高频放大器30,说明对载波放大器11以及峰值放大器12分别使用了总栅极宽度3mm的gan(也就是说,与比较例所涉及的高频放大器10同一gan)的情况的具体的电路常数。

60.用于在频率4.5ghz中得到最佳的特性的条件与比较例所涉及的高频放大器10相同,在pa接通时zc21=10ω j43ω、zp21=10ω j43ω,在pa断开时zc21=6ω j39ω。因此,将串联电感器34设定为0.82nh,将并联电感器35设定为0.89nh,将串联电感器37设定为0.82nh,将并联电感器38设定为0.89nh即可。第一传输线路40的电长度设定为小于1/4波长而并非1/4波长即可,在此,被设定为1/10波长。此外,第二传输线路39为了补偿基于第一传输线路40的相位旋转,被设定为与第一传输线路40相同的电长度、也就是说、电长度被设定为1/10波长。第一传输线路40以及第二传输线路39的特性阻抗都是50ω。第一传输线路40的电长度为1/10波长与比较例相比更短,所以zc21的分散变小而宽带域特性提高。此外,高频功率的损失变小而放大器的效率提高。进而电路的小型化成为可能。

61.图7是表示实施方式1所涉及的高频放大器30中的阻抗变换的史密斯图表,更详细而言,表示第一匹配电路33以及第一传输线路40带来的阻抗的变换。如图7的(a)所示,在pa接通时从zc24=50ω j0ω被变换为zc21=10ω j43ω。若详细来看,从zc24向zc23变换是由特性阻抗为50ω的第一传输线路40带来的,所以zc24和zc23都为50ω。从zc23向zc22的变换是基于一端被接地的并联电感器35的,成为绕逆时针的旋转。与在图2的(a)中从zc13向zc12的变换是绕顺时针相比,从zc23向zc22的变换的旋转的朝向成为相反。此外,从zc22向zc21的变换是由串联电感器34带来的。与图2的(a)的从zc12向zc11的变换相比,串联电感器34的电感从2.2nh变小为0.82h,所以从zc22向zc21的变换的变换量变小。

62.如图7的(b)所示,在pa断开时从zc24=25ω j0ω被变换为zc21=6ω j39ω。若详细来看,由第一传输线路40带来的从zc24向zc23的变换与图2的(b)的基于第一传输线路20的从zc14向zc13的变换相比,变换量从1/4波长变小为1/10波长。从zc23向zc22的变换是由一端被接地的并联电感器35带来的,成为绕逆时针的旋转。与图2的(b)所示的从zc13向zc12的变换相比,从zc23向zc22的变换成为相反朝向的旋转。此外,从z22向z21的变换是由串联电感器34带来的,与图2的(b)的从zc12向zc11的变换相比,变换量变小。

63.图8是表示实施方式1所涉及的高频放大器30所具备的匹配电路的相位角的图。在pa接通时,zc24和zc21的相位差仅为7

°

(图8的实线)。与图3所示的比较例所涉及的高频放大器10的相位差189

°

相比大幅被减少。在比较例所涉及的高频放大器10中,第一传输线路20带来的相位差为90

°

,对其加上第一匹配电路13带来的相位差,因此相位差之和必然成为90

°

以上。相对于此,在本实施方式所涉及的高频放大器30中,基于第一匹配电路33的相位差和基于第一传输线路40的相位差之和小于90

°

,可以说是显然的差异。在以下分析其主要原因。

64.也就是说,在本实施方式所涉及的高频放大器30中,zc24和zc23的相位差为36

°

,与比较例所涉及的高频放大器10的情况的zc14和zc13的相位差即90

°

相比大幅被减少。这

是第一传输线路40的长度被缩短为1/10波长的效果。第一匹配电路33带来的变换是从zc23向zc21的相位旋转,成为相位差=20

°‑

36

°

=

‑

16

°

。第一匹配电路33带来的相位旋转与第一传输线路40带来的相位旋转相反朝向,有对第一传输线路40的相位差进行补偿的作用。进而若详细来看,第一匹配电路33带来的相位差成为负的理由是由于由一端被接地的并联电感器35带来的相位差成为负。若观察从zc23向zc22的变换则该相位差为0

°‑

36

°

=

‑

36

°

。这样,具备具有与第一传输线路40相反朝向的相位旋转的结构元件,对补偿第一传输线路40带来的相位差是有效的。zc22和zc21的相位差小反映出串联电感器37的电感小。

65.在同图中,即使在pa断开时,在本实施方式所涉及的高频放大器30中,zc24和zc21之间的相位差与图2所示的比较例所涉及的高频放大器10的相位差相比大幅被减少(图8的虚线)。作为其理由,与pa接通时同样地,可列举第一传输线路40被缩短、第一匹配电路33对第一传输线路40的相位差进行补偿、作为第一匹配电路33的结构元件的并联电感器35具有与第一传输线路40带来的相位旋转相反朝向的相位旋转、以及串联电感器37的电感小。

66.图9a是表示实施方式1所涉及的高频放大器30中的pa接通时的zc21的分散的史密斯图表。表示频率4.3ghz、4.5ghz、4.7ghz中的zc21的分散。各频率中的zc21分别是9.3ω j41.5ω、10.0ω j43.1ω、10.7ω j44.6ω。若观察从频率4.3ghz至4.7ghz为止的δzc21,则δzc21=1.4ω j3.1ω,与图4a所示的比较例所涉及的高频放大器10相比分散被减少。其理由是由于如图8所示,第一匹配电路33对第一传输线路40带来的相位旋转进行补偿。即,第一匹配电路33用于减少第一传输线路40带来的zc21的分散。

67.图9b表示实施方式1所涉及的高频放大器30中的pa接通时的效率的频率特性。在中心频率4.5ghz中得到效率72%。与图4b相比可知,与比较例所涉及的高频放大器10相比效率改善了2%。该理由是由于通过第一传输线路40的缩短而高频损失被减少。在两端的频率4.3ghz和4.7ghz中,维持效率67%,如图9a所示,是δzc21被减少的效果。

68.图10a是表示实施方式1所涉及的高频放大器30中的pa断开时的zc21的分散的史密斯图表。若观察从频率4.3ghz至4.7ghz的δzc21,则δzc21=0.5ω j3.3ω,与图5a所示的比较例所涉及的高频放大器10相比分散被减少。与pa接通时同样,第一匹配电路33用于减少第一传输线路40带来的zc21的分散。

69.图10b表示实施方式1所涉及的高频放大器30中的pa断开时的效率的频率特性。在中心频率4.5ghz中得到效率52%。与图4b相比可知,与比较例所涉及的高频放大器10相比效率改善了2%。该理由是由于通过第一传输线路40的缩短而高频损失被减少。在两端的频率4.3ghz和4.7ghz中,也维持效率48%,如图10a所示,是δzc21被减少的效果。

70.另外,在上述例中,将第一传输线路40的电长度设为1/10波长,但若第一传输线路40的电长度小于1/4波长,则同样的效果被实现。作为例,将第一传输线路40的电长度设定为1/8波长,将其他电路常数调整为最佳而验证了zc21的分散。若观察从频率4.3ghz至4.7ghz的δzc21,则针对pa接通时而δzc21=1.2ω j4.5ω,针对pa断开时而δzc21=0.3ω j4.8ω。在将第一传输线路40的电长度设定为1/8波长的情况下,与图4a以及图5a所示的比较例所涉及的高频放大器10相比分散也被减少。针对将第一传输线路40的电长度设定为1/10波长、1/8波长、1/4波长的情况,将各δzc21的值汇总于表1。

71.[表1]

[0072][0073]

通过将第一传输线路40的电长度设为小于1/4波长,从而就pa接通时以及pa断开时的δzc21而言,与具备电长度为1/4波长的第一传输线路20的比较例所涉及的高频放大器10相比,δzc21被减少。其结果是,本实施方式所涉及的高频放大器30与比较例所涉及的高频放大器10相比,能够更宽带域、更高效率以及更小型。

[0074]

如以上那样,本实施方式所涉及的高频放大器30是,对规定的频带的第一信号以及第二信号进行放大而从输出端子22输出信号的放大器,其中,具备:第一放大器,对第一信号进行放大;第二放大器,对第二信号进行放大;第一匹配电路33,被连接于第一放大器的输出端子;第二匹配电路36,被连接于第二放大器的输出端子;第一传输线路40,被连接于第一匹配电路33的输出端子和第二匹配电路36的输出端子之间且具有小于规定的频带的中心频率的1/4波长的电长度;第二传输线路39,被连接于第一放大器以及第二放大器之中的一方(在本实施方式中,第二放大器)的输入端子且具有小于规定的频带的中心频率的1/4波长的电长度;以及第三传输线路21,被连接于第一传输线路40的一端和输出端子22之间且具有规定的频带的中心频率的1/4波长的电长度,被连接于第一放大器以及第二放大器之中的另一方的输出端子的第一匹配电路33或者第二匹配电路36(在本实施方式中,第一匹配电路33)带来的相位旋转与第一传输线路40带来的相位旋转相反朝向。

[0075]

由此,第一传输线路40的电长度小于1/4波长,所以第一传输线路40中的高频功率的损失变小而高频放大器30的效率提高,且能够进行高频放大器30的小型化。进而,被连接于第一放大器以及第二放大器之中的另一方的输出端子的第一匹配电路33或者第二匹配电路36(在本实施方式中,第一匹配电路33)带来的相位旋转与第一传输线路40带来的相位旋转相反朝向,因此第一传输线路40带来的相位旋转通过第一匹配电路33或者第二匹配电路36(在本实施方式中,第一匹配电路33)被补偿(也就是说,被用于消除)。具体而言,被连接于第一放大器以及第二放大器之中的另一方的输出端子的第一匹配电路33或者第二匹配电路36(在本实施方式中,第一匹配电路33)带来的相位旋转量与第一传输线路40带来的相位旋转量之和小于90

°

。因此,被连接于第一放大器以及第二放大器之中的另一方的输出端子的第一匹配电路33或者第二匹配电路36(在本实施方式中,第一匹配电路33)能够减少第一传输线路40带来的、从第一放大器的输出端子向输出侧观察时的阻抗的频率依赖性即分散,高频放大器的宽带域特性提高。

[0076]

在此,第一放大器为载波放大器11,第二放大器为峰值放大器12。由此,与以往相比能够更宽带域、更高效率以及更小型的多赫蒂放大器被实现。

[0077]

此外,第一匹配电路33以及第二匹配电路36分别具有一端被接地的第四传输线路以及第五传输线路。在此,第四传输线路以及第五传输线路之中的至少一方(在本实施方式中,双方)由电感器(并联电感器35以及38)构成。由此,发生与第一传输线路40带来的相位旋转相反朝向的相位旋转的第一匹配电路33或者第二匹配电路36(在本实施方式中,第一匹配电路33),使用电感器被简易地实现。

[0078]

另外,第一匹配电路33以及第二匹配电路36分别具有串联电感器34以及串联电感器37。由此,发生与第一传输线路40带来的相位旋转相反朝向的相位旋转的第一匹配电路33以及第二匹配电路36都能够至少由两个电感器构成。

[0079]

(实施方式2)

[0080]

图11是实施方式2所涉及的高频放大器50的电路图。以与图6所示的实施方式1所涉及的高频放大器30的差异为中心进行说明。在同图所示的高频放大器50中,代替图6所示的并联电感器35而具备一端被接地的第四传输线路55,同样地代替并联电感器38而具备一端被接地的第五传输线路58。针对第四传输线路55以及第五传输线路58,在频率4.5ghz中,若分别将线路长度设定为1/15波长则能够得到期望的特性。此外,在同图所示的高频放大器50中,代替图6所示的串联电感器34以及37,具有等价的阻抗变换的第八传输线路54以及第九传输线路57分别被使用。另外,第四传输线路55、第五传输线路58、第八传输线路54以及第九传输线路57在本实施方式中,都是微带线或者带状线。

[0081]

一端被接地的第四传输线路55带来的相位旋转与一端被接地的并联电感器35等价,能够得到与图7以及图8同样的变换。这样电感器能够作为传输线路的一种来处理。此外,高频放大器50能够得到与图9a、图9b、图10a以及图10b所示的效率特性同样的效率特性。

[0082]

如以上那样,在本实施方式所涉及的高频放大器50中,第一匹配电路53以及第二匹配电路56分别具有一端被接地的第四传输线路55以及第五传输线路58。由此,发生与第一传输线路40带来的相位旋转相反朝向的相位旋转的第一匹配电路53,使用微带线等第四传输线路55被简易地实现。

[0083]

(实施方式3)

[0084]

图12是实施方式3所涉及的高频放大器60的电路图。一般来说,有时将图6所示的高频放大器30区分为顺多赫蒂放大器,将图12所示的高频放大器60区分为逆多赫蒂放大器。以与高频放大器30的差异为中心进行说明。在同图中,将第一传输线路40和第一匹配电路33的连接处设为端子y。第三传输线路21被连接于端子y和输出端子22之间。第二传输线路39被连接于载波放大器11的输入侧,为了对第一传输线路40带来的相位旋转进行补偿而被设定为与第一传输线路40相同的电长度。

[0085]

针对第一传输线路40,在以往的逆多赫蒂放大器中需要1/4波长的传输线路,但在本实施方式所涉及的高频放大器60中能够缩短为小于1/4波长。进而,在第二匹配电路36对第一传输线路40的相位差进行补偿、作为第二匹配电路36的结构元件的一端被接地的并联电感器38具有与第一传输线路40带来的相位旋转相反朝向的相位旋转、以及串联电感器37的电感比以往的逆多赫蒂放大器小等特征上,有与使用图7以及图8说明的内容同样的特征。作为这些结果,在高频放大器60中,将第一匹配电路33、第二匹配电路36、第一传输线路40、第二传输线路39设定为最佳,从而能够得到与图9a、图9b、图10a以及图10b所示的效率特性同样的效率特性。

[0086]

如以上那样,在本实施方式所涉及的高频放大器60中,是逆多赫蒂放大器。并且,与实施方式1同样,第一传输线路40的电长度小于1/4波长,所以第一传输线路40中的高频功率的损失小而高频放大器60的效率提高,且能够进行高频放大器60的小型化。进而,被连接于第一放大器以及第二放大器之中的另一方的输出端子的第一匹配电路33或者第二匹

配电路36(在本实施方式中,第二匹配电路36)带来的相位旋转与第一传输线路40的相位旋转相反朝向,因此第一传输线路40带来的相位旋转通过第一匹配电路33或者第二匹配电路36(在本实施方式中,第二匹配电路36)被补偿(也就是说,被用于消除)。因此,被连接于第一放大器以及第二放大器之中的另一方的输出端子的第一匹配电路33或者第二匹配电路36(在本实施方式中,第二匹配电路36)能够减少第一传输线路40带来的、从第二放大器的输出端子向输出侧观察时的阻抗的频率依赖性即分散,高频放大器的宽带域特性提高。

[0087]

(实施方式4)

[0088]

图13是实施方式4所涉及的高频放大器70的电路图。在高频放大器70中,第四传输线路55以及第五传输线路58分别被连接于电源端子75以及电源端子76。一端被接地的接地用的第一电容器72被连接于电源端子75和第四传输线路55之间。此外,一端被接地的接地用的第二电容器74被连接于电源端子76和第五传输线路58之间。由此,就第四传输线路55以及第五传输线路58而言,一端被高频地接地,因此在高频放大器70中,也能够得到与实施方式1所涉及的高频放大器30同样的特性。这样,通过将第四传输线路55以及第五传输线路58使用于阻抗匹配和供应来自电源的功率这两个目的,能够实现电路的小型化。

[0089]

如以上那样,本实施方式所涉及的高频放大器70除了实施方式2所涉及的高频放大器50的结构外,还具备用于将第四传输线路55的一端接地、并被连接于第四传输线路55的一端和基准电位之间的第一电容器72、用于将第五传输线路58的一端接地、并被连接于第五传输线路58的一端和基准电位之间的第二电容器74。由此,第四传输线路55以及第五传输线路58被高频地接地,高频放大器70能够发挥与实施方式2所涉及的高频放大器50相同的效果。

[0090]

此外,本实施方式所涉及的高频放大器70中,第四传输线路55以及第五传输线路58的至少一方(在本实施方式中,双方)除了阻抗变换的用途外,还被使用于供应来自电源的功率的用途。由此,能够削减高频放大器70所需的电路元件,能够进行电路的小型化。

[0091]

(实施方式5)

[0092]

图14是实施方式5所涉及的高频放大器77的电路图。与图13所示的实施方式4所涉及的高频放大器70的差异是,在高频放大器77中,第一电源用电感器78被连接于作为第四传输线路55和第一电容器72的连接点的点s与电源端子75之间。在实施方式4所涉及的高频放大器70中,由于优先阻抗匹配而选定第四传输线路55的长度,在第四传输线路55的长度短的情况下,高频信号从电源端子75向电源侧泄漏成为问题。在本实施方式中,如图14所示,通过使用第一电源用电感器78,能够防止高频信号的泄漏。同样,第二电源用电感器79被连接于作为第五传输线路58和第二电容器74的连接点的点s’与电源端子76之间。通过使用第二电源用电感器79,能够防止高频信号向电源侧的泄漏。

[0093]

如以上那样,本实施方式所涉及的高频放大器77除了实施方式4所涉及的高频放大器70的结构外,还具备被连接于第四传输线路55和第一电容器72的连接点与电源之间的第一电源用电感器78、和被连接于第五传输线路58和第二电容器74的连接点与电源之间的第二电源用电感器79。由此,能够防止从高频放大器77向电源侧的高频信号的泄漏。

[0094]

(针对负载阻抗)

[0095]

针对本公开的经过,使用图15所示的表示实施方式1~5所涉及的高频放大器中的负载阻抗的区域的史密斯图表进行说明。在此,参考实施方式1进行说明。在图6所示的高频

放大器30中,对第一匹配电路33以及第二匹配电路36分别使用一端被接地的并联电感器35以及38是特征。能够使用这样的第一匹配电路33以及第二匹配电路36的原因是,载波放大器11以及峰值放大器12的负载阻抗被限于如图15所示的可匹配区域(斜线区域)的情况,该可匹配区域(斜线区域)处于去除以r=50ω的点和短路的点的中点为中心并穿过r=50ω的点和短路的点的圆(也就是说,穿过r=50ω的等导纳圆)的内部的区域。在至此为止以高输出用途为中心而研究的多赫蒂放大器中,由于所处理的晶体管的尺寸大,放大器的负载处于上述圆的内部,不能使用高频放大器30所具备的那样的第一匹配电路33以及第二匹配电路36。

[0096]

在被期待今后的发展的第五代通信(通称5g)中,被使用于无线基站装置的天线数大幅地增加(例如从以往的4个增加为256个)。在这样的无线基站装置中,使用阵列天线通过波束成形来输出从多个高频放大器被输出的高频信号,所以各个高频放大器有低输出化的倾向。且所使用的放大器的宽带域、高效率以及小型化比以往任何时候都重要,为了解决本课题而设计本公开所涉及的高频放大器。

[0097]

在此,详细地说明高频放大器的输出的降低和本公开所涉及的高频放大器的关系。通过发明人们的研究,在对高频晶体管使用gan的fet的情况下,在总栅极宽度为5mm以下的fet中,最佳负载显然进入图15所示的可能匹配区域。在总栅极宽度为5mm的gan的fet中输出的饱和功率为30w,在将其使用于载波放大器11以及峰值放大器12的情况下得到的高频放大器30的饱和输出为60w,能够使用高频放大器30作为第五代通信的无线基站装置用的高频放大器。此情况可以说针对在本说明书的全部实施方式中公开的高频放大器。

[0098]

如以上那样,在本实施方式所涉及的高频放大器中,从第一放大器的输出端子向输出侧观察的阻抗以及从第二放大器的输出端子向输出侧观察的阻抗的至少一方处于史密斯图表上的等导纳圆的外侧。

[0099]

为了将其满足,第一放大器以及第二放大器由使用了gan的fet构成,优选将该fet的高频的最大输出设为30w以下。由此,实施方式所涉及的高频放大器能被使用于使用阵列天线来输出高频信号的第五代通信等用途的无线基站装置。

[0100]

(实施方式6)

[0101]

图16是实施方式6所涉及的高频放大器80的布局图。本实施方式所涉及的高频放大器80具备与图14所示的实施方式5所涉及的高频放大器77相同的电路。因此,图16相当于针对图14所示的实施方式5所涉及的高频放大器77的电路图而示出基板80a上的具体的布局的图。

[0102]

图14和图16的对应如下面那样。也就是说,图14中的第八传输线路54对应于图16的线路ab。同样,图14的第四传输线路55对应于图16的线路bc。此外,图14的第一传输线路40对应于图16的线路bx。图14的接地用的第一电容器72由图16中的、一端被连接于接地部87的元件电容器82构成。图14的第一电源用电感器78对应于图16中的元件电感器85和作为第六传输线路的一例的线路cd这两个被连接的器件。在此,通过将线路cd并用,能够减小元件电感器85的电感,作为结果而能够提高元件电感器85的q值。载波放大器11的输出端子(点p)和线路ab的输入端子(点a)通过键合线而被连接。另外,载波放大器11被形成于半导体芯片80b上。

[0103]

同样,图14中的第九传输线路57对应于图16的线路a’b’。图14的第五传输线路58

对应于图16的线路b’c’。图14的接地用的第二电容器74对应于图16中的、一端被连接于接地部88的元件电容器84。图14的第二电源用电感器79对应于图16中的元件电感器86和作为第七传输线路的一例的线路c’d’这两个被连接的器件。在此,通过将线路c’d’并用,能够减小元件电感器86的电感,作为结果而能够提高元件电感器86的q值。峰值放大器12的输出端子(点p’)和线路a’b’的输入端子(点a’)通过键合线而被连接。另外,峰值放大器12被形成于半导体芯片80c上。

[0104]

从图16可知,在本实施方式所涉及的高频放大器80的布局中,从载波放大器11至电源端子75的配置、即芯片80b、相当于第八传输线路54的线路ab、相当于第四传输线路55的线路bc、相当于第六传输线路的线路cd、第一电容器82以及第一电源用电感器85的配置;和从峰值放大器12至电源端子76的配置、即芯片80c、相当于第九传输线路57的线路a’b’、相当于第五传输线路58的线路b’c’、相当于第七传输线路的线路c’d’、第二电容器84以及第二电源用电感器86的配置被线对称地制作。此外,线路bx以1/10波长(在基板80a上在频率4.5ghz中3mm左右)来实现,所以较短就可以。

[0105]

如以上那样,在本实施方式所涉及的高频放大器80中,代替实施方式5中的第一电源用电感器78而由元件电感器85和作为第六传输线路的一例的线路cd构成,代替实施方式5中的第二电源用电感器79而由元件电感器86和作为第七传输线路的一例的线路c’d’构成。也就是说,实施方式5中的第一电源用电感器78包含第六传输线路(线路cd),实施方式5中的第二电源用电感器79包含第七传输线路(线路c’d’)。

[0106]

由此,在载波放大器11以及峰值放大器12的附近,能够配置与以往相比线路长度被缩短化的传输线路,高频放大器80的电路的小型化被实现。

[0107]

另外,在本实施方式中,被形成了载波放大器11的半导体芯片80b和被形成了峰值放大器12的半导体芯片80c是不同芯片,但不限于此,也可以是同一芯片。

[0108]

此外,图16所例示的第八传输线路54、第九传输线路57、第四传输线路55、第五传输线路58、第一传输线路40、第二传输线路39(图16中未图示)以及第三传输线路21也可以是同一材料(例如铜)。

[0109]

(实施方式7)

[0110]

图17是实施方式7所涉及的高频放大器90的布局图。本实施方式所涉及的高频放大器90具备与图14所示的实施方式5所涉及的高频放大器77相同的电路。因此,图17相当于针对图14所示的实施方式5所涉及的高频放大器77的电路图而示出基板90a上的具体的布局的图。

[0111]

在本实施方式所涉及的高频放大器90中,在被形成了载波放大器91的半导体芯片90b上,不仅形成有作为载波放大器91的fet,还形成有线路pq、和第一电容器95。第一电容器95的一端经由贯通孔(图17中未图示)被连接于半导体芯片90b的背面的接地。同样,在被形成了峰值放大器92的半导体芯片90c上,不仅形成有作为峰值放大器92的fet,还形成有线路p’q’、和第二电容器96。第二电容器96的一端经由贯通孔(图17中未图示)被连接于半导体芯片90c的背面的接地。

[0112]

图14和图17的对应如下面那样。也就是说,图14中的第八传输线路54对应于在图17中半导体芯片上的线路pq和在点q

‑

点h间被连接有键合线的部分。同样,图14的第四传输线路55对应于图17的线路hj。图14的第一传输线路40对应于图17的线路hx。图14的接地用

的第一电容器72对应于图17中的、被形成于半导体芯片90b上的第一电容器95。同样,图14中的第九传输线路57在图17中由半导体芯片上的线路p’q’和在点q

’‑

点h’间的键合线构成。图14的第五传输线路58对应于图17的线路h’j’。图14的接地用的第二电容器74对应于图17中的、被形成于导体芯片90c上的第二电容器96。

[0113]

此外,图17中的点j和电源端子75之间的线路对应于第六传输线路,以及点j’和电源端子76之间的线路对应于第七传输线路。

[0114]

在毫米波段以上的高的频带中,由于波长变短而能够将传输线路形成于半导体芯片上。此外,与波长相比较而键合线的长度变得有意义,因此能够使用键合线来构成匹配电路的一部分。此外,由于在较高的频带中能够以较小的容量值来实现接地用的电容器,因此能够形成于半导体芯片上。

[0115]

如以上那样,本实施方式7所涉及的高频放大器90是,对规定的频带的第一信号以及第二信号进行放大而从输出端子22输出信号的放大器,其中,具备:基板90a;一或者二个半导体芯片(在本实施方式中,半导体芯片90b以及90c),被安装在基板90a上;第一放大器,被形成于半导体芯片90b,对第一信号进行放大;第二放大器,被形成于半导体芯片90c,对第二信号进行放大;第八传输线路54的一部分(线路pq),被形成于半导体芯片90b,一端被连接于第一放大器的输出端子;第九传输线路57的一部分(线路p’q’),被形成于半导体芯片90c,一端被连接于第二放大器的输出端子;第一电容器95,被形成于半导体芯片90b;第二电容器96,被形成于半导体芯片90c;第四传输线路55(线路hj),被形成于基板90a上,一端被连接于第八传输线路54的一部分(线路pq)的另一端;第五传输线路58(线路h’j’),被形成于基板90a上,一端被连接于第九传输线路57的一部分(线路p’q’)的另一端;第一传输线路40(线路hx),被形成于基板90a上,被连接于第四传输线路55的一端(点h)和第五传输线路58的一端(点h’)之间且具有小于规定的频带的中心频率的1/4波长的电长度;第二传输线路39(图17中未图示),被连接于第一放大器或者第二放大器的其中一个的输入端子且具有小于规定的频带的中心频率的1/4波长的电长度;以及第三传输线路21(点x和输出端子22之间的传输线路),被连接于第一传输线路40(线路hx)的一端和输出端子22之间且具有规定的频带的中心频率的1/4波长的电长度,第四传输线路55的另一端和第一电容器95被连接,第五传输线路58的另一端和第二电容器96被连接。更具体而言,第四传输线路55的另一端和第一电容器95通过第一键合线97而被连接,第五传输线路58的另一端和第二电容器74通过第二键合线98而被连接。

[0116]

由此,能够使用键合线来构成匹配电路的一部分,需要匹配电路的传输线路的长度被缩短化。此外,接地用的电容器被形成于形成有放大器的半导体芯片上,因此针对放大器以及电容器,能够作为从其他电路独立的元件来设计。

[0117]

另外,在本实施方式中,被形成了载波放大器91的半导体芯片90b和被形成了峰值放大器92的半导体芯片90c是不同芯片,但不限于此,也可以是同一芯片。此外,图17中例示的第八传输线路54、第九传输线路57、第四传输线路55、第五传输线路58、第一传输线路40、第二传输线路39(图17中未图示)以及第三传输线路21也可以是同一材料(例如铜)。

[0118]

(实施方式8)

[0119]

图18是实施方式8所涉及的载波放大器用的半导体芯片101的布局图(图18的(a))、以及峰值放大器用的半导体芯片102的布局图(图18的(b))。在图18的(a)所示的载波

放大器用的半导体芯片101,不仅形成有放大用fet,还形成有线路pq、第一电容器105。此外,在半导体芯片101和外部传输线路的连接点即点q、作为第一电容器105的一端的上部电极106、以及作为另一端的下部电极107形成有凸点(bump)。同样,在图18的(b)所示的峰值放大器用的半导体芯片102,不仅形成有放大用fet,还形成有线路p’q’、第二电容器108。此外,在半导体芯片102和外部传输线路的连接点即点q’、作为第二电容器108的一端的上部电极109、以及作为另一端的下部电极110形成有凸点。

[0120]

图19是实施方式8所涉及的高频放大器100的布局图。本实施方式所涉及的高频放大器100具备与图14所示的实施方式5所涉及的高频放大器77相同的电路。因此,图19相当于针对图14所示的实施方式5所涉及的高频放大器77的电路图而示出基板100a上的具体的布局的图。

[0121]

如本图所示,图18所示的载波放大器用的半导体芯片101以及峰值放大器用的半导体芯片102以倒装(facedown)的形式被安装在基板100a上。在此,安装为,点q上的凸点与点h重叠,上部电极106的凸点与点j重叠,点q’的凸点与点h’重叠,上部电极109的凸点与点j’重叠。此外,作为第一电容器105以及第二电容器108的另一端的下部电极107以及110的凸点分别经由基板100a被接地。

[0122]

图14和图19的对应如下面那样。也就是说,图14中的第八传输线路54对应于在图19中线路pq。此外,图14的第四传输线路55对应于图19的线路hj。此外,图14的第一传输线路40对应于图19的线路hx。同样,图14中的第九传输线路57在图19中由线路p’q’构成。此外,图14的第五传输线路58对应于图19的线路h’j’。

[0123]

这样,载波放大器用的半导体芯片101具有作为第一导体的凸点,该作为第一导体的凸点被形成于在平面图中半导体芯片101的至少一部分与第四传输线路55的另一端(也就是说,点j)重叠的区域,同样,峰值放大器用的半导体芯片102具有作为第二导体的凸点,该第二导体的凸点被形成于在平面图中半导体芯片102的至少一部分与第五传输线路58的另一端(也就是说,点j’)重叠的区域。并且,第四传输线路55的另一端(也就是说,点j)和第一电容器72经由作为第一导体的凸点被连接,同样,第五传输线路58的另一端(也就是说,点j’)和第二电容器74经由作为第二导体的凸点被连接。

[0124]

在实施方式7中,使用第一键合线97以及第二键合线98构成了匹配电路的一部分,但若频率进一步变高则键合线的电感过大而难以取得匹配。在该情况下,凸点的电感远小于键合线,所以如本实施方式那样,代替键合线而使用凸点来取得与外部电路的接触即可。

[0125]

以上,针对本公开所涉及的高频放大器,基于实施方式1~8进行了说明,但本公开并非被限定于这些实施方式1~8。只要不脱离本公开的主旨,将本领域技术人员所想到的各种变形施加于各实施方式的方式、将各实施方式中的一部分结构元件组合而构筑的别的方式也被包含于本公开的范围内。

[0126]

例如,在上述实施方式中,高频放大器以50ω的负载为对象而被设计,但对象的负载阻抗不被限定于50ω,也可以以75ω等其他负载为对象而被设计。在该情况下,使构成高频放大器的各传输线路的特性阻抗与对象的负载阻抗一致即可。

[0127]

工业上的可利用性

[0128]

本公开所涉及的高频放大器例如能够作为被用于无线通信的小型、高效率以及宽带域的多赫蒂放大器以及逆多赫蒂放大器,更具体而言,作为第五代通信的无线基站装置

用的高频放大器来利用。

[0129]

标号说明

[0130]

11,91 载波放大器

[0131]

12,92 峰值放大器

[0132]

21 第三传输线路

[0133]

22 输出端子

[0134]

23 第一输入端子

[0135]

24 第二输入端子

[0136]

30,50,60,70,77,80,90,100 高频放大器

[0137]

33,53 第一匹配电路

[0138]

34,37 串联电感器

[0139]

35,38 并联电感器

[0140]

36,56 第二匹配电路

[0141]

39 第二传输线路

[0142]

40 第一传输线路

[0143]

54 第八传输线路

[0144]

55 第四传输线路

[0145]

57 第九传输线路

[0146]

58 第五传输线路

[0147]

72,95,105 第一电容器

[0148]

74,96,108 第二电容器

[0149]

75,76 电源端子

[0150]

78 第一电源用电感器

[0151]

79 第二电源用电感器

[0152]

80a,90a,100a 基板

[0153]

80b,80c,90b,90c,101,102 半导体芯片

[0154]

82,84 元件电容器

[0155]

97 第一键合线

[0156]

98 第二键合线

[0157]

106,109 上部电极

[0158]

107,110 下部电极

[0159]

线路cd第七传输线路

[0160]

线路c’d’第八传输线路

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。