1.本发明属于显示技术领域,尤其涉及一种基于8080总线接口的显示控制电路及显示系统。

背景技术:

2.在图像显示领域常用的数据接口有hdmi(high definition multimedia interface,高清晰度多媒体接口)、lvds(low voltage differential signaling,即低电压差分信号)、rgb及8080接口。8080总线及接口凭借接口简单、控制方便、无需同步时钟和同步信号等优势在显示领域得到了广泛应用。8080总线接口的显示设备需由带有8080接口的主控芯片驱动。

3.现有技术中,对于不带8080接口的主控芯片用于驱动8080总线接口的显示设备,需通过gpio模拟实现对8080总线接口的显示设备的驱动,速度慢、效率低。

技术实现要素:

4.有鉴于此,本发明实施例提供了一种基于8080总线接口的显示控制电路及显示系统,以解决现有技术中不带8080接口的主控芯片用于驱动8080总线接口的显示设备需通过gpio口模拟,速度慢、效率低的问题。

5.本发明实施例第一方面提供了一种基于8080总线接口的显示控制电路,包括:主控模块;

6.主控模块包括:第一io口、第二io口、第三io口、模拟片选接口、第一数据总线接口及第一rgb接口;

7.主控模块的第三io口用于,与外部的显示设备的8080接口的命令数据选择端连接,并向显示设备发送命令指示信号;其中,命令指示信号用于指示显示设备工作在命令模式或数据模式下;

8.主控模块的第一io口用于,与显示设备的8080接口的片选端连接,并向显示设备发送命令模式下的片选信号;

9.主控模块的第二io口用于,与显示设备的8080接口的写使能端连接,并向显示设备发送命令模式下的写使能信号;

10.主控模块的模拟片选接口用于,与显示设备的8080接口的片选端连接,并向显示设备发送数据模式下的片选信号;其中,数据模式下的片选信号与主控模块的第一rgb接口中的数据使能端输出的信号反相;

11.主控模块的第一rgb接口中的时钟信号端用于,与显示设备的8080接口的写使能端连接,并向显示设备发送数据模式下的写使能信号;

12.主控模块的第一数据总线接口用于,与显示设备的8080接口的数据总线端连接,并向显示设备发送并行数据信号。

13.可选的,主控模块包括:第一主控芯片和反相器;

14.第一主控芯片包括:第四io口、第五io口、第六io口、第二数据总线接口及第二rgb接口;

15.第一主控芯片的第四io口、第一主控芯片的第五io口、第一主控芯片的第六io口、第一主控芯片的第二数据总线接口及第一主控芯片的第二rgb接口分别与主控模块的第一io口、主控模块的第二io口、主控模块的第三io口、主控模块的第一数据总线接口及主控模块的第一rgb接口一一对应连接;

16.第一主控芯片的第二rgb接口中的数据使能端与反相器的输入端连接;

17.反相器的输出端与主控模块的模拟片选接口连接。

18.可选的,第一主控芯片的第四io口与第一主控芯片的第二rgb接口中的数据使能端复用;

19.第一主控芯片的第五io口与第一主控芯片的第二rgb接口中的时钟信号端复用。

20.可选的,反相器集成在第一主控芯片中。

21.可选的,主控模块包括:第二主控芯片和辅助单元;

22.第二主控芯片包括:第七io口、第八io口、第九io口、第三数据总线接口及第三rgb接口;

23.第二主控芯片的第七io口与辅助单元的第一输入端连接,第二主控芯片的第八io口与辅助单元的第二输入端连接,第二主控芯片的第三rgb接口中的数据使能端与辅助单元的第三输入端连接,第二主控芯片的第三rgb接口中的时钟信号端与辅助单元的第四输入端连接,第二主控芯片的第九io口与主控模块的第三io口连接,第二主控芯片的第三数据总线接口与主控模块的第一数据总线接口连接;

24.辅助单元的第一输出端用于,与显示设备的8080接口的片选端连接,并向显示设备发送命令模式下的片选信号及数据模式下的片选信号;

25.辅助单元的第二输出端用于,与显示设备的8080接口的写使能端连接,并向显示设备发送命令模式下的写使能信号及数据模式下的写使能信号。

26.可选的,辅助单元包括:第一单刀双掷模拟开关、第二单刀双掷模拟开关、开关管、第一电阻及第二电阻;

27.第一单刀双掷模拟开关的第一输入端与开关管的第一端及第一电阻的第二端连接,第一单刀双掷模拟开关的第二输入端与辅助单元的第一输入端连接,第一单刀双掷模拟开关的输出端与辅助单元的第一输出端连接,第一单刀双掷模拟开关的使能端与辅助单元的第三输入端连接;

28.第二单刀双掷模拟开关的第一输入端与辅助单元的第四输入端连接,第二单刀双掷模拟开关的第二输入端与辅助单元的第二输入端连接,第二单刀双掷模拟开关的输出端与辅助单元的第二输出端连接,第二单刀双掷模拟开关的使能端与辅助单元的第三输入端连接;

29.开关管的第二端接地,开关管的控制端通过第二电阻与辅助单元的第三输入端连接;

30.第一电阻的第二端与内部电源连接。

31.可选的,当第一单刀双掷模拟开关的使能端为低电平时,第一单刀双掷模拟开关的第一输入端与输出端之间选通;

32.当第一单刀双掷模拟开关的使能端为高电平时,第一单刀双掷模拟开关的第二输入端与输出端之间选通。

33.可选的,主控模块还包括:第十io口;

34.主控模块的第一rgb接口中的帧同步信号端与主控模块的第十io口连接,用于向主控模块发送中断信号。

35.可选的,显示设备为lcd。

36.本发明实施例第二方面提供了一种显示系统,包括:具有8080接口的显示设备及本发明实施例第一方面中的任一种基于8080总线接口的显示控制电路;

37.基于8080总线接口的显示控制电路与显示设备连接。

38.本发明实施例提供了一种基于8080总线接口的显示控制电路及显示系统,上述电路包括:主控模块;主控模块包括:第一io口、第二io口、第三io口、模拟片选接口、第一数据总线接口及第一rgb接口;主控模块,第一io口和第二io口模拟命令模式下的片选信号和写使能信号,第一rgb接口的数据使能端的信号反相后模拟数据模式下的片选信号,第一rgb接口的时钟信号模拟数据模式下的写使能信号,第三io口模拟命令指示信号,第一数据总线接口用于传输数据。本发明实施例采用自带的rgb接口模拟8080总线接口时序,无需全部采用gpio模拟,速度快,效率高。

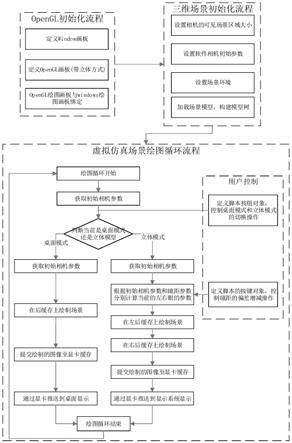

附图说明

39.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

40.图1是rgb接口的时序图;

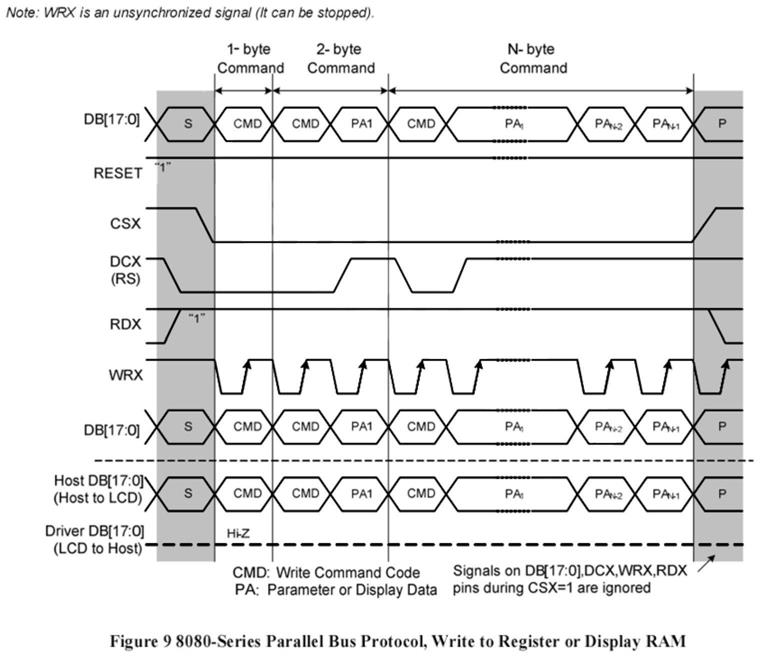

41.图2是8080接口的时序图;

42.图3是本发明实施例提供的一种基于8080总线接口的显示控制电路的示意图;

43.图4是本发明实施例提供的第二种基于8080总线接口的显示控制电路的示意图;

44.图5是本发明实施例提供的第三种基于8080总线接口的显示控制电路的示意图;

45.图6是本发明实施例提供的第四种基于8080总线接口的显示控制电路的示意图;

46.图7是图6所示的基于8080总线接口的显示控制电路对应的时序图;

47.图8是本发明实施例提供的第五种基于8080总线接口的显示控制电路的示意图;

48.图9是本发明实施例提供的辅助单元的电路原理图;

49.图10是图8所示的基于8080总线接口的显示控制电路对应的时序图。

具体实施方式

50.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

51.为了说明本发明的技术方案,下面通过具体实施例来进行说明。

52.使用8080总线接口的屏幕一般自带驱动芯片(例如ili9488、ili9341、ssd1963等),驱动芯片自带显存,上位机只需要把显示数据发送给驱动芯片,驱动芯片首先把数据保存到显存中,再把显存中的数据显示到屏幕上。使用8080总线接口的屏幕的优点是控制简单方便,无需时钟和同步信号,无需上位机提供显存,可省掉sdram(synchronous dynamic random

‑

access memory,同步动态随机存取内存)或sram(static random

‑

access memory,静态随机存取存储器),适用于小尺寸屏幕的应用。例如240x320尺寸,采用rgb565模式(16bit/pixel),加上部分空白区域,所需时钟速度大概在3mbps左右。对于自带硬件8080总线接口的上位机来说实现并不困难,但是对于没有硬件8080总线接口的上位机,如果通过gpio模拟的方式实现的,速度很慢,且会消耗大量的cpu资源,效率低。

53.对于多媒体的上位机来说,通常自带rgb接口。图1示出了rgb接口的时序图,图2示出了8080总线接口的时序图。对比图1和图2可知,两种接口的时序具有一定的相似性,rgb接口时序中的数据使能信号高电平有效,8080接口时序中的片选信号低电平有效,具有一定的相似性;且rgb接口时序中的时钟信号与8080接口时序中写使能信号相似。

54.基于以上,参考图3,本发明实施例提供了一种基于8080总线接口的显示控制电路,包括:主控模块1;

55.主控模块1包括:第一io口gpio1、第二io口gpio2、第三io口gpio3、模拟片选接口csx0、第一数据总线接口data1[15:0]及第一rgb接口;

[0056]

主控模块1的第三io口gpio3用于,与外部的显示设备2的8080接口的命令数据选择端dcx连接,并向显示设备2发送命令指示信号;其中,命令指示信号用于指示显示设备2工作在命令模式或数据模式下;

[0057]

主控模块1的第一io口gpio1用于,与显示设备2的8080接口的片选端csx连接,并向显示设备2发送命令模式下的片选信号;

[0058]

主控模块1的第二io口gpio2用于,与显示设备2的8080接口的写使能端wrx连接,并向显示设备2发送命令模式下的写使能信号;

[0059]

主控模块1的模拟片选接口csx0用于,与显示设备2的8080接口的片选端csx连接,并向显示设备2发送数据模式下的片选信号;其中,数据模式下的片选信号与主控模块1的第一rgb接口中的数据使能端输出的信号反相;

[0060]

主控模块1的第一rgb接口中的时钟信号端clk1用于,与显示设备2的8080接口的写使能端wrx连接,并向显示设备2发送数据模式下的写使能信号;

[0061]

主控模块1的第一数据总线接口data1[15:0]用于,与显示设备2的8080接口的数据总线端data0[15:0]连接,并向显示设备2发送并行数据信号。

[0062]

根据rgb接口的时序和8080接口的时序的相似性,本发明实施例中采用主控模块1自带的rgb接口中的数据使能端输出的数据使能信号取反模拟8080接口时序中数据模式下的片选信号;采用主控模块1自带的rgb接口中的时钟信号端输出的时钟信号模拟8080接口时序中的数据模式下的写使能信号;第一数据总线接口data1[15:0]与显示设备2的8080接口的数据总线端data0[15:0]直连,发送并行数据信号;同时,分别采用3个io口模拟8080接口时序中命令模式下的片选信号、命令模式下的写使能信号及命令指示信号。主控模块1采用自带的rgb接口及io口模拟8080接口时序,无需全部采用io模拟,节省了cpu资源,提高了数据传输速度及效率。

[0063]

其中,主控模块1的模拟片选接口csx0输出的数据模式下的片选信号与主控模块1的第一rgb接口中的数据使能端输出的信号反相,该述特征可以通过硬件或软件实现,本发明实施例对此不做限定。

[0064]

一些实施例中,基于以上,信号反相可通过硬件实现。参考图4,主控模块1可以包括:第一主控芯片11和反相器12;

[0065]

第一主控芯片11包括:第四io口gpio4、第五io口gpio5、第六io口gpio6、第二数据总线接口data2[15:0]及第二rgb接口;

[0066]

第一主控芯片11的第四io口gpio4、第一主控芯片11的第五io口gpio5、第一主控芯片11的第六io口gpio6、第一主控芯片11的第二数据总线接口data2[15:0]及第一主控芯片11的第二rgb接口分别与主控模块1的第一io口gpio1、主控模块1的第二io口gpio2、主控模块1的第三io口gpio3、主控模块1的第一数据总线接口data1[15:0]及主控模块1的第一rgb接口一一对应连接;

[0067]

第一主控芯片11的第二rgb接口中的数据使能端de2与反相器12的输入端连接;

[0068]

反相器12的输出端与主控模块1的模拟片选接口csx0连接。

[0069]

本发明实施例中设置反相器12,通过反相器12实现信号的反相。

[0070]

一些实施例中,参考图5,第一主控芯片11的第四io口gpio4与第一主控芯片11的第二rgb接口中的数据使能端de2复用;

[0071]

第一主控芯片11的第五io口gpio5与第一主控芯片11的第二rgb接口中的时钟信号端clk2复用。

[0072]

一般主控芯片的端口可复用,本发明实施例中第一主控芯片11的第四io口gpio4与第一主控芯片11的第二rgb接口中的数据使能端de2复用,第一主控芯片11的第五io口gpio5与第一主控芯片11的第二rgb接口中的时钟信号端clk2复用,节约端口数量,便于与外部显示设备2连接。

[0073]

一些实施例中,参考图6,反相器12集成在第一主控芯片11中。

[0074]

部分主控芯片内部自带反相功能,第一主控芯片11的第二rgb接口中的数据使能端de2可直接输出反相后的信号,无需单独设置反相器12。参考图6,第一主控芯片11的第二rgb接口中的数据使能端de2与显示设备2的8080接口中的片选端csx直连。

[0075]

例如,图7示出了图6所示基于8080总线接口的显示控制电路的信号时序图,可满足8080接口应用需求。

[0076]

一些实施例中,参考图8,主控模块1包括:第二主控芯片13和辅助单元14;

[0077]

第二主控芯片13包括:第七io口gpio7、第八io口gpio8、第九io口gpio9、第三数据总线接口data3[15:0]及第三rgb接口;

[0078]

第二主控芯片13的第七io口gpio7与辅助单元14的第一输入端csx_gpio连接,第二主控芯片13的第八io口gpio8与辅助单元14的第二输入端wrx_gpio连接,第二主控芯片13的第三rgb接口中的数据使能端de3与辅助单元14的第三输入端csx_de连接,第二主控芯片13的第三rgb接口中的时钟信号端clk3与辅助单元14的第四输入端wrx_de连接,第二主控芯片13的第九io口gpio9与主控模块1的第三io口gpio3连接,第二主控芯片13的第三数据总线接口data3[15:0]与主控模块1的第一数据总线接口data1[15:0]连接;

[0079]

辅助单元14的第一输出端csx_out用于,与显示设备2的8080接口的片选端csx连

接,并向显示设备2发送命令模式下的片选信号及数据模式下的片选信号;

[0080]

辅助单元14的第二输出端wrx_out用于,与显示设备2的8080接口的写使能端wrx连接,并向显示设备2发送命令模式下的写使能信号及数据模式下的写使能信号。

[0081]

一些实施例中,参考图9,辅助单元14包括:第一单刀双掷模拟开关u1、第二单刀双掷模拟开关u2、开关管q1、第一电阻r1及第二电阻r2;

[0082]

第一单刀双掷模拟开关u1的第一输入端与开关管q1的第一端及第一电阻r1的第二端连接,第一单刀双掷模拟开关u1的第二输入端与辅助单元14的第一输入端csx_gpio连接,第一单刀双掷模拟开关u1的输出端与辅助单元14的第一输出端csx_out连接,第一单刀双掷模拟开关u1的使能端与辅助单元14的第三输入端csx_de连接;

[0083]

第二单刀双掷模拟开关u2的第一输入端与辅助单元14的第四输入端wrx_de连接,第二单刀双掷模拟开关u2的第二输入端与辅助单元14的第二输入端wrx_gpio连接,第二单刀双掷模拟开关u2的输出端与辅助单元14的第二输出端wrx_out连接,第二单刀双掷模拟开关u2的使能端与辅助单元14的第三输入端csx_de连接;

[0084]

开关管q1的第二端接地,开关管q1的控制端通过第二电阻r2与辅助单元14的第三输入端csx_de连接;

[0085]

第一电阻r1的第二端与内部电源vcc连接。

[0086]

本发明实施例中通过开关管q1对数据使能信号取反,同时结合两个单刀双掷模拟开关将命令模式下的片选信号与数据模式下的片选信号结合到一个端输出,同时将命令模式下的写使能信号和数据模式下的写使能信号结合到一个端输出。主控模块1仅保留四个输出端子,与外部的显示设备2直连,便于生产及应用。

[0087]

参考图9,第一单刀双掷模拟开关u1和第二单刀双掷模拟开关u2的电源端均与内部电源vcc连接;第一单刀双掷模拟开关u1和第二单刀双掷模拟开关u2的接地端均接地。

[0088]

一些实施例中,当第一单刀双掷模拟开关u1的使能端为低电平时,第一单刀双掷模拟开关u1的第一输入端与输出端之间选通;

[0089]

当第一单刀双掷模拟开关u1的使能端为高电平时,第一单刀双掷模拟开关u1的第二输入端与输出端之间选通。

[0090]

一些实施例中,第一单刀双掷模拟开关u1及第二单刀双掷模拟开关u2的型号均可以为bl1551。

[0091]

一些实施例中,开关管q1可以为npn型三极管。

[0092]

一些实施例中,参考图6及图8,主控模块1还包括:第十io口gpio10;

[0093]

主控模块1的第一rgb接口中的帧同步信号端vsync_out与主控模块1的第十io口gpio10连接,用于向主控模块1发送中断信号。

[0094]

本发明实施例中还可采用rgb接口的帧同步信号作为自身中断,触发数据传输。进一步的,第一主控芯片11或第二主控芯片13中的一个io口和帧同步信号端分别与主控模块1中的第十io口gpio10和帧同步信号端一一对应连接,具体在此不再赘述。

[0095]

图10示出了图8所示基于8080总线接口的显示控制电路的信号时序图,同样可满足8080接口应用需求。

[0096]

一些实施例中,显示设备2可以为lcd。

[0097]

参考图8、图9及图10,结合具体实施例对上述基于8080总线接口的显示控制电路

的工作过程进行说明。

[0098]

1、第二主控芯片13切换至gpio mode模式,驱动gpio9模拟命令指示信号(高电平),驱动第二主控芯片的第三数据总线接口data3[15:0]模拟caset/raset的命令,用于设置屏幕显示的起始位置和显示区域(一般设置成整屏区域范围);

[0099]

2、等待帧同步信号的上升沿,当检测到帧同步信号的上升沿中断时,第二主控芯片13切换至gpio mode模式,拉低命令指示信号(gpio9),进入命令模式;驱动第一主控芯片11的gpio7模拟命令模式下的片选信号、gpio8模拟命令模式下的写使能信号、第三数据总线接口data3[15:0]模拟ramwr的命令、

[0100]

3、完成写命令后,第二主控芯片13配置内部rgb硬件电路,将内部rgb硬件电路需要输出的rgb数据准备好,拉高命令指示信号(gpio9),进入数据模式;

[0101]

4、第二主控芯片13切换至de mode模式,启动硬件驱动第三rgb接口中的数据使能端de3输出数据使能信号、时钟信号端clk3输出时钟信号及第三数据总线接口data3[15:0]输出并行数据信号,第二主控芯片13持续一帧输出rgb数据;

[0102]

5、一帧数据传输完成后,重复执行步骤2。

[0103]

对应于上述任一种基于8080总线接口的显示控制电路,本发明实施例还提供了一种显示系统,该一种显示系统包括:具有8080接口的显示设备2及上述任一种基于8080总线接口的显示控制电路;

[0104]

基于8080总线接口的显示控制电路与显示设备2连接。

[0105]

上述显示系统具有上述基于8080总线接口的显示控制电路所具有的优点,在此不再赘述。

[0106]

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。