1.本发明涉及等离子体处理方法。

背景技术:

2.在半导体器件的制造工序中,要求应对半导体装置所包含的组件的微细化、集成化。例如,在集成电路、纳米电子机械系统中,进一步推进构造物的纳米级化。

3.通常,在半导体器件的制造工序中,为了成型微细图案而使用光刻技术。在该技术中,在抗蚀剂层上应用器件构造的图案,选择性地对通过抗蚀剂层的图案,而露出的基板进行蚀刻去除。在之后的处理工序中,只要在蚀刻区域内堆积其他材料,就能够形成集成电路。

4.特别是近年来,伴随着flash、dram等存储器件的高集成化、高速化,要求能够形成高纵横比的图案构造的蚀刻。以往,使用多晶硅的硬掩模对几微米的绝缘膜进行了蚀刻,但出于对与绝缘膜的选择性的限制、以及担心进一步的厚膜化等原因,作为耐蚀刻材料,研究了硼掺杂多晶硅的应用。例如,在专利文献1中公开了将硼掺杂多晶硅用作硬掩模材料之一。此外,作为对以往的对多晶硅、掺杂的多晶硅进行蚀刻的技术,在专利文献2中公开了使用氯和溴的混合气体。

5.在先技术文献

6.专利文献

7.专利文献1:美国专利公开第2014/0057442号说明书

8.专利文献2:美国专利公开第2013/0244394号说明书

9.专利文献3:日本特开2019

‑

80000号说明书

技术实现要素:

10.发明要解决的课题

11.但是,若在以往的蚀刻条件下对耐蚀刻材料的硼掺杂多晶硅进行蚀刻,则存在伴随着蚀刻速率的降低而导致蚀刻终止(stop)(蚀刻的停止)、锥形形状形成等蚀刻不良等问题。此外,若用氟气蚀刻硼掺杂多晶硅,则还存在导致侧面蚀刻(side etching)(咬边)、翘曲(bowing)形状形成等蚀刻不良等问题。

12.此外,在专利文献3中公开了将含有硼(b)的硅膜作为掩模膜使用。然而,对于如何对含有硼(b)的硅膜的掩模膜进行蚀刻,在专利文献3中没有具体的记载。

13.本发明鉴于这样的现有技术的课题,其目的在于,提供一种等离子体处理方法,在对含有硼的硅膜、多晶硅膜进行等离子体蚀刻时,能够实现蚀刻速率的提高,抑制蚀刻不良。

14.用于解决课题的手段

15.为了解决上述课题,代表性的本发明所涉及的等离子体处理方法之一是,在对含有硼的硅膜进行等离子体蚀刻的等离子体处理方法中,

16.通过使用卤素气体、含有氟的气体、以及三氯化硼气体的混合气体,对含有所述硼的硅膜进行蚀刻来实现。

17.进而,代表性的本发明所涉及的等离子体处理方法之一是,在对含有硼的硅膜进行等离子体蚀刻的等离子体处理方法中,

18.通过使用氯气、三氟化氮气体、三氯化硼气体、以及氧气,对含有所述硼的硅膜进行蚀刻来实现。

19.进而,代表性的本发明所涉及的等离子体处理方法之一是,在对含有硼的硅膜进行等离子体蚀刻的等离子体处理方法中,

20.通过使用氯气、三氟化氮气体、三氯化硼气体、氧气、以及溴化氢气体,对含有所述硼的硅膜进行蚀刻来实现。

21.进而,代表性的本发明所涉及的等离子体处理方法之一是,在对含有硼的多晶硅膜进行等离子体蚀刻的等离子体处理方法中,

22.使用卤素气体、含有氟的气体、以及三氯化硼气体的混合气体,对含有所述硼的多晶硅膜进行蚀刻,

23.所述卤素气体是溴化氢气体、氯化氢气体、碘化氢气体中的至少一种气体。

24.进而,代表性的本发明所涉及的等离子体处理方法之一是,在对含有硼的多晶硅膜进行等离子体蚀刻的等离子体处理方法中,

25.通过使用氯气、三氟化氮气体、三氯化硼气体、以及氧气,对含有所述硼的多晶硅膜进行蚀刻来实现。

26.进而,代表性的本发明所涉及的等离子体处理方法之一是,在对含有硼的多晶硅膜进行等离子体蚀刻的等离子体处理方法中,

27.通过使用氯气、三氟化氮气体、三氯化硼气体、氧气、以及溴化氢气体,对含有所述硼的多晶硅膜进行蚀刻来实现。

28.发明效果

29.根据本发明,提供一种等离子体处理方法,能够在对含有硼的硅膜、多晶硅膜进行等离子体蚀刻时实现蚀刻速率的提高,抑制蚀刻不良。

30.上述以外的课题、结构以及效果通过以下的实施方式的说明而变得明确。

附图说明

31.图1是本实施方式所涉及的等离子体蚀刻装置的概略剖视图。

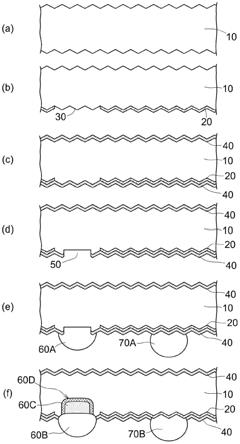

32.图2a是本实施方式所涉及的等离子体蚀刻处理前的被蚀刻材料的剖面示意图。

33.图2b是本实施方式所涉及的等离子体蚀刻处理后的被蚀刻材料的剖面示意图。

34.图3a是表示形状异常的被蚀刻材料的加工剖面的示意图,是表示蚀刻终止等的例子的图。

35.图3b是表示形状异常的被蚀刻材料的加工剖面的示意图,是表示侧面蚀刻等的例子的图。

36.图4a是表示蚀刻气体中的bcl3气体流量的比例与开口尺寸的关系的曲线图。

37.图4b是示出bcl3气体流量的比例与对氮化硅膜、对硅氧化膜选择比的关系的曲线图。

38.图5是表示硅氧化膜残膜量与tm偏压的占空(duty)比(%)的关系的曲线图。

39.图6是表示使处理压力为2pa以下的时的被蚀刻材料的剖面形状的图。

具体实施方式

40.[实施方式]

[0041]

图1是表示在本实施方式中使用的微波ecr(electron cyclotron resonance,电子回旋共振)等离子体方式的蚀刻处理装置的概略纵剖视图。

[0042]

由电源101振荡出的2.45ghz的微波在波导管102中传播,透过电介质窗103供给到处理室104。蚀刻处理用气体从具有多个贯通孔的簇射板(shower plate)106向处理室104供给。在处理室104的外周以及电介质窗103的上方配置有多个螺线管线圈(solenoid coil)105,通过控制螺线管线圈105的电流值,生成所希望的磁场。然后,通过微波与磁场的相互作用来进行电子回旋共振,从而被供给至处理室104的蚀刻处理用气体被激励,生成高密度等离子体107。将使用该高密度等离子体107对被蚀刻材料进行蚀刻称为等离子体蚀刻。

[0043]

具有被蚀刻材料的晶片109载置于收容于处理室104的试样台108的上表面。试样台108具有配置在外周侧的石英制的基座环(susceptor ring)110和配置在其下方的绝缘板111。为了对在晶片109上成膜的晶片109按照曝光图案实施各向异性蚀刻,在试样台108的下部具备匹配器112和高频电源113,并具备控制从等离子体内入射的离子的能量的机构。此外,该高频电源113具有偏压的连续导通[连续波(continuous wave)偏压(以下,称为cw偏压)]的模式和以毫秒级(order)周期性重复偏压的导通/截止的时间调制[时间调制(time modulation)偏压(以下,称为tm偏压)]的模式。

[0044]

使用图1所示的蚀刻处理装置,将应用本实施方式所涉及的等离子体处理方法的半导体晶片的剖面构造示于图2a。半导体晶片在图中从下方起依次具有包含硅氮化膜201、多晶硅202、掺杂硼而成的硼掺杂多晶硅(含有硼的多晶硅膜)203、硅氧化膜204、无定形碳膜205图案化的光致抗蚀剂膜206的多层构造。进而,在硅氮化膜201的下层存在1.2μm左右的硅氧化膜(在图2a中未记载)。

[0045]

首先,为了将孔(hole)图案转印到硅氧化膜204上,对无定形碳膜205和硅氧化膜204进行蚀刻处理,得到图2a的初始形状。然后,对硼掺杂多晶硅203和多晶硅202进行蚀刻处理。

[0046]

在本实施方式中,将电路图案转印(蚀刻)为用于对该1.2μm左右的硅氧化膜进行蚀刻的成为硬掩模的多晶硅202和硼掺杂多晶硅203。包含硼掺杂多晶硅203和多晶硅202的被蚀刻膜具有约800nm的厚度,硼掺杂多晶硅203具有200nm~600nm的膜厚度。此外,硼掺杂多晶硅203与多晶硅202的厚度的比率根据目的而适当变更。

[0047]

在现有技术中,在硼掺杂多晶硅203和多晶硅202中形成孔形状,因此在多晶硅202的蚀刻中,使用了卤素气体cl2以及o2的混合气体。在使用了该以往的多晶硅的蚀刻条件的情况下,硼掺杂多晶硅的蚀刻速率相对于多晶硅降低50%以上,产生导致如图3a所示的蚀刻终止301、锥形形状302这样的形状不良的问题。

[0048]

另一方面,为了避免蚀刻终止301,若用含有氟的气体对硼掺杂多晶硅203进行蚀刻,则存在侧壁保护膜变薄,导致如图3b所示那样的侧面蚀刻303、翘曲形状304、图案消失

305等形状不良的问题。此外,由于作为被蚀刻膜的硼掺杂多晶硅203相对于孔尺寸厚,因此离子和自由基无法充分到达微细形状的下端(底部(bottom))部分,难以扩大底部尺寸。另外,所谓含有氟的气体是nf3气体、sf6气体或hf气体等气体。

[0049]

为了解决这样的问题,在本实施方式中,将卤素气体的cl2气体、含有氟的气体的nf3气体、o2气体、以及bcl3气体的混合气体供给至处理室104而使用。在图2b中示出通过该等离子体处理方法进行了处理的半导体晶片的剖面构造的示意图。通过使用该混合气体,硼系的沉积物(deposit)(以下,简称为沉积物)能够在保护侧壁的同时对硼掺杂多晶硅进行蚀刻。进而,参照图4a、4b对使用bcl3气体的效果进行说明。在此,作为卤素气体,能够使用cl2气体、hbr气体、hcl气体、hi气体中的任一种以上。例如,cl2气体、hbr气体、nf3气体、o2气体、以及bcl3气体的混合气体也能够解决上述问题。此外,在cl2气体、hbr气体、nf3气体、o2气体、以及bcl3气体的混合气体的情况下,能够进一步提高硅氧化膜选择比,因此在对孔进行蚀刻时,能够抑制掉头,能够抑制孔的顶部cd的扩大。

[0050]

图4a是表示蚀刻气体中的bcl3气体流量的比例与开口尺寸(开口端:顶部cd401、底端:底部cd402)的关系的曲线图。所谓cd,意味着关键尺寸(critical dimension)。在此,使用图1所示的蚀刻装置,设为如下的蚀刻条件,即,将处理室104的压力设为0.8pa,将电源101的微波输出设为600w,将试样台108的工作台温度设为50℃,将作为向处理室104供给的蚀刻气体的cl2设为80ml/min,将hbr设为140ml/min,将o2设为20ml/min进行供给。另外,蚀刻处理时间在全部条件下是固定的。

[0051]

在bcl3气体的流量为气体整体流量的0%时,侧面蚀刻过量而产生顶部部分的图案消失305,顶部cd为无限大(无法计测),底部cd为14.3nm。相对于此,随着bcl3气体的流量增加至6.5%、16%,根据硼系保护膜的效果,顶部部分的图案消失305改善,顶部cd分别减少至33nm、28nm,且底部cd分别增加至18nm、22nm。

[0052]

以上的结果是,由等离子体中的b自由基和o自由基生成的bo沉积物和bcl

x

沉积物在孔的两壁生成保护膜,并抑制侧面蚀刻303和翘曲形状304的产生而得到。进而,当bcl3气体的流量变多时,在侧壁附着bo沉积物和bcl

x

沉积物,由此开口部尺寸缩小,但由于因硼系沉积物而在侧壁不消耗蚀刻剂,因此能够使蚀刻进行至深处,底部cd增加。根据以上的结果可知,通过调整bcl3气体相对于气体整体流量的流量,能够控制开口尺寸。

[0053]

图4b是表示在将处理室104的压力设为0.8pa,将电源101的微波输出设为600w,将试样台108的工作台温度设为50℃的条件下,将作为蚀刻气体的cl2设为80ml/min、将hbr设为140ml/min、将o2设为20ml/min进行供给,并向其中添加的bcl3气体流量的比例与对硅氮化膜选择比404、对硅氧化膜选择比403的关系的曲线图。

[0054]

若bcl3气体的流量比例从0%增加至12%,则对硅氧化膜选择比403与对硅氮化膜选择比404增加,但若进一步添加bcl3气体,则对硅氧化膜选择比403减少,相对于此,对硅氮化膜选择比404增加。因而,通过添加bcl3气体,能够仅使对硅氮化膜选择比404增加。

[0055]

在本实施方式中采用的蚀刻条件中,为了使硅氧化膜204的残膜量极大化,bcl3气体的流量设定相对于气体整体流量以9%~13%的比例设定。另外,在不同的蚀刻条件(压力、微波功率、工作台温度等)下,通过同样的方法,相对于bcl3气体相对于总气体流量的比例,取得对硅氧化膜选择比403、对硅氮化膜选择比404的趋势数据,适当调整为可得到所希望的选择比和形状,由此能够得到如图2b那样的图案形状。

[0056]

进而,通过调整tm(time modulation,时间调制)偏压,通过使在偏压截止时间内反应的生成物堆积于侧壁,由此能够保护上部图案,能够控制选择比。图5是表示硅氧化膜残膜量与tm偏压的占空(duty)比(%)的关系的曲线图。另外,所谓tm偏压,是通过向试样台供给脉冲调制后的高频电力而对试样台施加偏压的方法。此外,占空比是高频电力相对于一个周期的tm偏压时间接通的时间的比率。有效功率是偏置电力与占空比(脉冲的导通期间的高频电力与占空比)的积值。

[0057]

表示有效功率90w的残膜量的回归直线501和表示有效功率180w的残膜量的回归直线502均随着占空比的减少,硅氧化膜残膜量增加。因而,只要不受高频电源113的功率特性等限制,就优选选择更高功率,低占空比的tm偏压条件。此时,由于因占空比减少而离子辅助反应时间变短,因此为了使其兼顾蚀刻形状,也可以实施气体组成比率、压力、微波功率等其他参数的调整。例如,在氧化膜残膜目标值为80nm以上的情况下,期望设定为有效功率90w,占空比25%以下。

[0058]

此外,在图6示出使处理压力为2pa以下并进行了蚀刻的情况下的被蚀刻材料的剖面形状。通过使对含有硼的多晶硅膜进行等离子体蚀刻的处理室内的压力低压化,蚀刻气体的离子密度增加,伴随着反应生成物的滞留时间降低,到达孔底部的蚀刻剂和离子比率增加,因此前端变细的形状得到改善,得到垂直(vertical)的形状。根据该结果,处理压力期望设定为2pa以下。

[0059]

如上所述,通过适当调整cl2、nf3、o2、bcl3的气体流量比或cl2、nf3、o2、bcl3、hbr的气体流量比以及其他参数,能够提高蚀刻速率,并且抑制蚀刻终止301、侧面蚀刻303、翘曲形状304以及图案消失305,并且得到期望的形状。

[0060]

此外,即使使用n2、ar、he、xe、kr气体等惰性气体来稀释上述记载的气体,也能够得到与本实施方式同等的效果。进而,在代替含有硼的多晶硅膜而对含有硼的硅膜进行等离子体蚀刻时,也能够同样地应用本实施方式。

[0061]

进而,在本实施方式中,虽然使用了图1所示的微波ecr方式的蚀刻处理装置,但在ccp(capacitively coupled plasma,电容耦合等离子体)方式、icp(inductively coupled plasma,电感耦合等离子体)方式等其他等离子体源的等离子体蚀刻装置中,通过调整压力、气体流量、气体比、偏置电力和频率,也能够得到同样的效果。

[0062]

上述的实施方式是为了容易理解地说明本发明而详细进行了说明的实施方式,并不限定于必须具备所说明的全部结构。此外,能够将某个实施方式的结构的一部分置换为其他实施方式的结构,此外,也能够在某个实施方式的结构中添加其他实施方式的结构。此外,对于各实施方式的结构的一部分,能够进行其他结构的追加、删除、置换。

[0063]

符号说明

[0064]

101:电场产生用电源;

[0065]

102:波导管;

[0066]

103:电介质窗;

[0067]

104:处理室;

[0068]

105:螺线管线圈;

[0069]

106:簇射板;

[0070]

107:高密度等离子体;

[0071]

108:试样台;

[0072]

109:晶片;

[0073]

110:基座环;

[0074]

111:绝缘体;

[0075]

112:匹配器;

[0076]

113:高频电源;

[0077]

201:硅氮化膜;

[0078]

202:多晶硅;

[0079]

203:硼掺杂多晶硅;

[0080]

204:硅氧化膜;

[0081]

205:无定形碳膜;

[0082]

206:光致抗蚀剂膜;

[0083]

301:蚀刻终止;

[0084]

302:锥形形状;

[0085]

303:侧面蚀刻;

[0086]

304:翘曲形状;

[0087]

305:图案消失;

[0088]

401:顶部cd;

[0089]

402:底部cd;

[0090]

403:对硅氧化膜选择比;

[0091]

404:对硅氮化膜选择比;

[0092]

501:表示基于有效功率90w的残膜量的回归直线;

[0093]

502:表示基于有效功率180w的残膜量的回归直线。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。