1.实施方式大体涉及陶瓷铜电路基板及使用了其的半导体装置。

背景技术:

2.陶瓷铜电路基板被用于搭载有功率元件等半导体元件的半导体装置。陶瓷基板与铜电路部经由接合层而彼此接合。对于接合层,使用含有钛(ti)等活性金属的银(ag)钎料。由此,使接合强度及热循环特性提高。伴随着可靠性的提高,陶瓷铜电路基板被用于汽车(包含电动汽车)、电力铁道车辆、太阳能发电设备、产业机械的逆变器等中。

3.在功率模块等半导体装置中,在铜电路部安装有半导体元件。此外,为了半导体元件的导通,有时也接合引线接合或金属端子。在半导体装置的制造中,半导体元件、引线接合、金属端子等与铜电路部接合。

4.随着功率模块的小型化、轻量化及高密度安装化进展,为了低热电阻化及低电感化,铜电路部变厚。铜电路部厚的陶瓷铜电路基板被记载于国际公开wo2018

‑

180965号公报(专利文献1)中。专利文献1通过将铜电路板的表面的晶界的数目最优化,使陶瓷铜电路基板的组装性提高。根据专利文献1的陶瓷铜电路基板,半导体元件的接合性及对位精度提高。

5.现有技术文献

6.专利文献

7.专利文献1:国际公开第2018

‑

180965号公报

技术实现要素:

8.发明所要解决的课题

9.其另一方面,除了上述的接合性或对位精度以外,因铜电路部变厚而产生的课题变得明显。例如,为了提高制品的可靠性,期望实现铜电路部分的精细图案化、作为电路基板整体的应力缓和等。在专利文献1中,主要着眼于控制铜电路部的表面中的粒径,但获知因铜电路变厚而表面和内部的粒径产生差异。即,如果控制铜电路的表面,则能够提高铜板表面的接合性、对位精度,但判明为了提高精细图案化等其他的特性,需要控制铜电路内部。

10.近年来,功率半导体模块的小型化、轻量化、高密度安装化取得进展。伴随于此,为了金属电路部的热电阻的降低、金属电路部的电感的降低,要求增厚金属电路部。此外,为了提高安装的密度,要求金属电路部的精细图案化。

11.此外,伴随着功率半导体芯片的结温(tj)上升,还要求陶瓷电路基板的可靠性提高。

12.实施方式是用于解决这样的问题的方式,涉及能够使电路更加微细、并且提高陶瓷电路基板的可靠性的陶瓷铜电路基板。

13.用于解决课题的手段

14.实施方式的陶瓷铜电路基板包含陶瓷基板及铜电路部。铜电路部被设置于上述陶瓷基板的第1面。在与从上述陶瓷基板朝向上述铜电路部的第1方向平行的上述铜电路部的截面中,与上述第1方向平行的任意的线与多个铜晶粒交叉。与上述第1方向垂直的第2方向上的各个上述铜晶粒的端与上述线之间的上述第2方向上的多个距离的平均为300μm以下。

附图说明

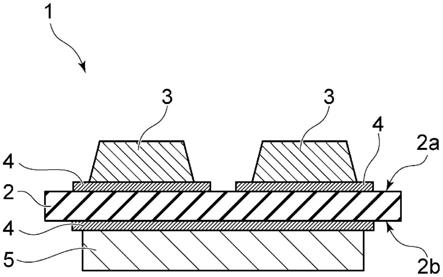

15.图1是表示实施方式的陶瓷铜电路基板的一个例子的图。

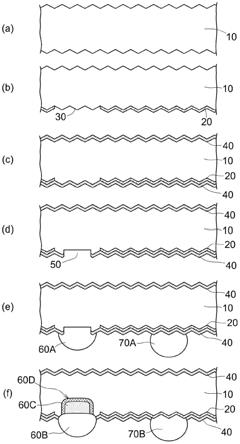

16.图2是表示铜电路部的截面的一个例子的图。

17.图3是表示铜电路部的截面的一个例子的图。

18.图4是表示铜电路的图案尺寸及图案间尺寸的一个例子的图。

19.图5是表示实施方式的半导体装置的一个例子的图。

具体实施方式

20.实施方式的陶瓷铜电路基板包含陶瓷基板及铜电路部。铜电路部被设置于上述陶瓷基板的第1面。在与从上述陶瓷基板朝向上述铜电路部的第1方向平行的上述铜电路部的截面中,与上述第1方向平行的任意的线与多个铜晶粒交叉。与上述第1方向垂直的第2方向上的各个上述铜晶粒的端与上述线之间的上述第2方向上的多个距离的平均为300μm以下。

21.图1表示陶瓷铜电路基板的一个例子。在图1中,1为陶瓷铜电路基板。2为陶瓷基板。3为铜电路部。4为包含钎料的接合层。5为背铜板。陶瓷基板2具有表面2a(第1面)及背面2b。铜电路部3经由接合层4(第1接合层的一个例子)与陶瓷基板2的表面2a接合。在图1的例子中,多个铜电路部3经由多个接合层4与表面2a分别接合。实施方式并不限定于图示的形态。也可以1个铜电路部3或3个以上的铜电路部3与表面2a接合。此外,在图1的例子中,背铜板5与背面2b接合。背铜板5不是电路,而作为散热板发挥功能。背铜板5根据需要而适当设置。代替背铜板5,也可以在背面2b设置图案化的铜电路部。

22.陶瓷基板2优选为氧化铝基板、氮化铝基板及氮化硅基板中的任1种。除此以外,还可列举出阿卢西尔高硅耐热铝合金基板。阿卢西尔高硅耐热铝合金是相对于氧化铝20~80%而剩余部分为氧化锆的烧结体。

23.氮化铝基板或氧化铝基板的三点弯曲强度为300~450mpa左右。阿卢西尔高硅耐热铝合金基板的强度也为550mpa前后。

24.氮化硅基板的三点弯曲强度能够提高至600mpa以上、进而700mpa以上。此外,氮化硅基板的热导率能够提高至50w/(m

·

k)以上、进而80w/(m

·

k)以上。特别是近年来,还有兼具高强度和高导热这两者的氮化硅基板。氮化硅基板的厚度优选为0.635mm以下,更优选为0.3mm以下。氮化硅基板由于为高强度,因此能够减薄,能够进一步提高散热性。厚度的下限值没有特别设定,但优选为0.1mm以上。这是为了确保氮化硅基板的电绝缘性。这里,厚度是指连结陶瓷基板2和铜电路部3的方向上的尺寸。

25.实施方式的陶瓷铜电路基板可以具备1个陶瓷基板,也可以具备2个以上的陶瓷基板。例如,多个陶瓷基板与多个铜电路部也可以在第1方向上交替地层叠。

26.图2是表示铜电路部的截面的一个例子的图。图2是图1的a部分的放大截面图。图2中,7表示假想上的任意的线。该线与从陶瓷基板2朝向铜电路部3的第1方向平行。图2中,d1

表示第1方向。此外,该线相对于表面2a及背面2b垂直。8表示侧面蚀刻量。侧面蚀刻量为铜电路部的表面3a的外周与铜电路部的背面3b的外周之间的与第1方向垂直的一方向上的距离。

27.铜电路部由铜的多晶体制成。画线7的方法如下所述。首先,将陶瓷铜电路基板与第1方向d1平行地切断。拍摄截面的放大照片。此时,放大照片以拍到陶瓷基板并且可确认晶界的程度放大而拍摄。接着,在放大照片中,通过画与表面2a垂直的任意的直线,得到线7。此外,在陶瓷基板面的表面2a的状态含糊并且铜电路部3的背面3b视为与表面2a平行的面的情况下,也可以将与背面3b垂直的任意的直线作为线7处理。

28.图3表示铜电路部内部的截面图的一个例子。图3是将图2的b部分的截面放大。10为铜晶粒,11为铜晶粒的晶界。在铜电路部的截面中,相对于陶瓷基板面沿垂直方向(基板的厚度方向)画任意的线7。在图3中,12表示线7所交叉的铜晶粒10中距离任意的线7最远的铜晶粒10的外缘(晶界11)为止的第2方向d2上的距离lh。13表示线7与铜晶粒10的外缘的交点即第1端10a及第2端10b之间的长度lv。第2方向与第1方向垂直,与截面平行。

29.在实施方式的陶瓷铜电路基板中,距离lh的平均为300μm以下。长度lv的平均优选为300μm以下。

30.在陶瓷基板和在陶瓷基板上接合有铜电路部的陶瓷铜电路基板中,在陶瓷基板的整面或一部分上接合铜板后,大多通过对铜板部分进行蚀刻而形成电路。在利用蚀刻的铜板的溶解中,沿着铜板的晶体晶界进行溶解。因此,铜晶粒的形状对蚀刻产生较大影响。即,在晶粒径大的情况下,不仅在蚀刻液逐渐挖进的厚度方向上,而且在面方向上也变得容易进行溶解。面方向是与第1方向垂直的方向。第2方向是与面方向平行的一方向。

31.关于和与第1方向平行的线交叉的多个铜晶粒,这些距离lh的平均为300μm以下表示第2方向上的尺寸比较小的铜晶粒沿厚度方向排列。由此,能够抑制向面方向的蚀刻的进行,能够减小由蚀刻产生的侧面蚀刻量。其结果是,变得容易形成精细图案电路。

32.这里所谓的精细图案电路是指图案间尺寸与通常的电路相比为60~80%左右的电路基板。此外,电路的至少一部分满足该范围的图案间尺寸的电路为精细图案电路。图4中示出陶瓷铜电路基板1的图案尺寸14和图案间尺寸15。图案尺寸14表示包括接合层4的电导通部分的宽度。图案间尺寸15表示形成于陶瓷表面的接合层4之间的尺寸距离。在图4的例子中,在陶瓷基板2的表面2a接合有多个铜板3。多个铜板3在第2方向d2上彼此并列,经由多个接合层4与陶瓷基板2分别接合。在第2方向d2上相邻的接合层4彼此之间的第2方向d2上的距离与图案间尺寸15相对应。

33.为了电导通、半导体元件或金属端子的接合、引线接合等,图案的宽度(图案尺寸)要求为规定的值以上。例如,铜板厚度为0.1mm以上且低于0.5mm时的图案尺寸优选为0.5mm以上。铜板厚度为0.5mm以上且低于0.7mm时的图案尺寸优选为0.7mm以上。铜板厚度为0.7mm以上且低于0.8mm时的图案尺寸优选为1.0mm以上。

34.这里,在铜板厚度为0.1mm以上且低于0.5mm的情况下,在通常的铜电路基板中,图案间尺寸为0.6mm以上。与此相对,在精细图案电路中,图案间尺寸为0.4mm以上。同样地,在铜板厚度为0.5mm以上且低于0.7mm的情况下,在通常的铜电路基板中,图案间尺寸为1.0mm以上。与此相对,在精细图案电路中,图案间尺寸为0.6mm以上。在铜板厚度为0.7mm以上且低于0.8mm的情况下,在通常的铜电路基板中,图案间尺寸为1.8mm以上。与此相对,在精细

图案电路中,图案间尺寸为1.1mm以上。

35.此外,通过将铜电路部中的长度lv的平均设定为300μm以下,铜板变得容易发生塑性变形。由此,作为接合体的陶瓷铜电路基板中产生的应力被缓和,接合强度、基板弯曲强度及耐热循环性提高,能够得到可靠性高的陶瓷电路基板。

36.此外,在陶瓷铜电路基板中,通过接合时的热处理而铜板的粒径变大。也可以通过控制粒子的粗大化那样的铜中的添加物或加工及调整接合条件来控制粒径的粗大化,但有可能因控制而制造成本变高。例如,通过将距离lh及长度lv设定为50μm以上,能够得到性价比良好的陶瓷铜电路基板。但是,即使是其以下的距离lh及长度lv也能够制造,下限值没有规定。

37.铜电路部3会接合半导体元件等。为了热电阻的降低和电感的降低,铜电路部的厚度优选为0.5mm以上,更优选为0.8mm以上。此时,若铜电路部内部的距离lh的平均小,则可抑制侧面蚀刻量。由此,能够形成精细图案。此外,通过接合体的应力缓和,接合强度、基板弯曲强度及耐热循环性提高。

38.若铜电路部内部的距离lh的平均大于300μm,则铜电路部内部的铜晶粒在横方向上变大,侧面蚀刻量变多。因此,电路图案的尺寸精度降低。

39.若铜电路部内部的长度lv的平均大于300μm,则铜电路部的塑性变形变小。其结果是,接合体的应力变大,接合强度等特性变得容易降低。

40.此外,若按照各个距离lh及各个长度lv变得小于50μm的方式进行调整,则由于因工序控制而产生的负荷,因此花费制造成本。

41.此外,即使是距离lh的平均为300μm以下时,若存在许多距离lh大于400μm的铜晶粒,则侧面蚀刻量也会产生不均。距离lh优选为400μm以下。同样地,即使是长度lv的平均为300μm以下时,若存在许多长度lv大于400μm的铜晶粒,则接合强度也会产生不均。长度lv优选为400μm以下。

42.如上所述,铜电路内部的铜晶粒的距离lh的平均及长度lv的平均中的至少一者优选为300μm以下。更优选距离lh的平均及长度lv的平均这两者优选为300μm以下。进而,各个距离lh及各个长度lv优选为400μm以下。此时,各个距离lh优选为50μm以上。各个长度lv优选为50μm以上。更优选各个距离lh为50μm以上,并且各个长度lv为50μm以上。

43.此外,各个距离lh优选为300μm以下。各个长度lv优选为300μm以下。更优选各个距离lh为300μm以下,并且各个长度lv为300μm以下。此时,各个距离lh优选为70μm以上。各个长度lv优选为70μm以上。更优选各个距离lh为70μm以上,各个长度lv为70μm以上。

44.在实施方式的陶瓷铜电路基板中,在铜电路部3的截面中画沿着第1方向的任意的直线时,关于与该直线交叉的多个铜晶粒,距离lh及长度lv在上述的范围内。即,在铜电路部3的截面中,不论在哪个部分画直线,距离lh及长度lv都在上述的范围内。通过利用该铜电路部3在陶瓷基板上形成电路,能够得到优异的可靠性。

45.在铜电路部通过铜板的加工来形成的情况下,在调整铜板的厚度的轧制工序中,也可以调整晶体尺寸来调整距离lh及长度lv。此外,也可以通过在铜板内添加微量的元素来调整晶体尺寸。此时,也可以预先在铜板内微量添加锡(sn)或锆(zr)等控制粒生长的元素。也可以在制造陶瓷铜电路基板时的接合等工序中,将抑制铜板内的粒生长的元素扩散到铜板内。进而,也可以利用陶瓷铜电路基板的制造工序中的热处理工序。铜的再结晶温度

为约220℃。如下文所述的那样,铜板与陶瓷基板进行活性金属接合。在活性金属接合法中,陶瓷基板及铜板在700~900℃下被加热。在该工序中,铜板被再结晶。若被再结晶,则铜晶粒进行生长。通过控制该现象,也能够调整铜晶粒的大小。

46.此外,铜电路部的第1方向上的厚度优选为0.5mm以上,更优选为0.8mm以上。通过将铜电路部的厚度设定为上述的值,能够更大地获得蚀刻时的精细图案化的效果。即,在铜电路部的厚度比上述的值薄的情况下也可得到本发明的效果。但是,由于与通过以往的制法而制造的制品的差异不大,因此难以得到由本发明带来的效果。

47.陶瓷基板的厚度没有特别限定。通过减薄陶瓷电路基板及增厚铜电路部,散热性提高。铜电路部的厚度的上限没有特别限定,但优选为5mm以下。若铜电路部的厚度超过5mm,则在通过活性金属接合法进行接合时翘曲变大。由此,有可能变得难以减薄陶瓷基板。

48.此外,陶瓷基板2与铜电路部3优选经由接合层4而接合。此外,在设置背铜板5的情况下,背铜板5优选经由接合层与陶瓷基板2接合。此外,优选在陶瓷基板与铜电路部之间设置包含ag(银)及ti(钛)的接合层。包含ag及ti的接合层使用活性金属钎料而形成。ti为活性金属。作为活性金属,除了ti以外,还可列举出zr(锆)。作为活性金属钎料,可列举出ti、ag及cu(铜)的混合物。例如,ti的含量为0.1~10重量%,cu的含量为10~60重量%,剩余部分为ag。此外,在通过接合时的钎料的扩散来控制铜电路部中的粒径的情况下,根据需要,也可以添加1~15重量%的选自由in(铟)、sn(锡)、al(铝)、si(硅)、c(碳)及mg(镁)构成的组中的1种以上。使用了活性金属钎料的活性金属接合法是在陶瓷基板表面涂布活性金属钎料膏糊,在其上配置铜板。将其在700~900℃下加热而接合。根据活性金属接合法,能够使陶瓷基板与铜电路部的接合强度为16kn/m以上。

49.此外,也可以在铜电路表面设置以选自由ni(镍)、ag(银)及au(金)构成的组中的1种作为主要成分的金属薄膜。作为这些金属薄膜,可列举出镀覆膜、溅射膜等。通过设置金属薄膜,能够提高耐蚀性、软钎料润湿性等。

50.这样的陶瓷铜电路基板适于在铜电路部上经由接合层安装半导体元件的半导体装置。

51.图5表示半导体装置的一个例子。图5中,1为陶瓷铜电路基板。16为半导体装置。17为半导体元件。18为接合层(第2接合层的一个例子)。19为引线接合。20为金属端子。图5中,在陶瓷铜电路基板1的铜电路部上,经由接合层18接合有半导体元件17。同样地,经由接合层18接合有金属端子20。相邻的铜电路部的半导体元件与铜电路部通过引线接合19而导通。实施方式的半导体装置并不限定于这样的结构。例如,也可以设置引线接合19和金属端子20中的任一者。此外,半导体元件17、引线接合19及金属端子20也可以在铜电路部3中分别设置多个。此外,在背铜板5上,也可以根据需要而接合半导体元件、引线接合或金属端子20。此外,对于金属端子20,可以适用引线框形状、凸型形状等各种形状。

52.此外,对于接合半导体元件17或金属端子20的接合层18,使用软钎料、钎料等。软钎料优选无铅软钎料。此外,软钎料是指熔点为450℃以下的材料。钎料是指熔点超过450℃的材料。此外,将熔点为500℃以上的材料称为高温钎料。高温钎料可列举出以ag作为主要成分的材料。

53.实施方式的陶瓷铜电路基板由于将距离lh的平均设定为300μm以下,因此电路形成时的蚀刻特性优异。特别是铜电路基板的厚度成为0.8mm以上而铜板变得越厚,则越能够

获得由抑制侧面蚀刻特性带来的精细图案形成的效果。在铜板变厚而精细图案形成困难的情况下,有时因蚀刻残余而产生图案不良。此外,为了防止侧面蚀刻而需要减慢蚀刻速度等应对。从这点出发,根据本实施方式,能够提高陶瓷铜电路基板的可靠性,提高性价比。

54.实施方式的陶瓷铜电路基板由于将长度lv的平均设定为300μm以下,因此能够缓和应力。在陶瓷铜电路基板中,产生铜板与陶瓷的接合的残余应力。进而,通常,通过在铜电路上搭载半导体元件,通过来自半导体元件的发热而因陶瓷基板与铜电路的热膨胀差产生应力。随着铜电路部中的粒径在相对于与陶瓷基板的接合面垂直的方向上变小,铜电路部中产生的应力变小。若应力变小,则即使是铜电路部的厚度厚达0.5mm以上的情况下,也能够抑制因陶瓷基板与铜电路部的应力差而产生裂纹等。

55.从这点出发,根据本实施方式,能够提高陶瓷铜电路基板的可靠性。

56.此外,半导体元件的小型化进展,另一方面,来自芯片的发热量增加。因此,在搭载半导体元件的陶瓷铜电路基板中,散热性的提高变得重要。此外,为了半导体装置(半导体模块)的高性能化,在陶瓷铜电路基板上可安装多个半导体元件。即使是半导体元件中的仅一个,若超过元件的真性温度,则电阻也会变化为负的负侧的温度系数。伴随于此,引起电力集中地流动的热失控,瞬时地产生半导体装置被破坏的现象。因而,提高半导体元件与铜电路部的接合的可靠性是非常有效的。此外,实施方式的半导体装置可以用于汽车(包含电动汽车)、电力铁道车辆、产业机械及空调等的逆变器中使用的pcu、igbt、ipm模块。关于汽车,电动汽车的普及取得进展。半导体装置的可靠性越提高,越能够提高汽车的安全性。关于电力铁道车辆、产业设备等也同样。

57.接着,对实施方式的陶瓷铜电路基板的制造方法进行说明。陶瓷铜电路基板只要具有上述的构成,则其制造方法没有特别限定。这里,列举出用于成品率良好地获得陶瓷铜电路基板的方法的一个例子。

58.首先,准备陶瓷基板和铜板。铜板的厚度为0.5mm以上。

59.此外,陶瓷基板优选为选自氧化铝基板、氮化铝基板及氮化硅基板中的1种。特别是若考虑电路基板整体的散热性,则陶瓷基板优选为热导率50w/(m

·

k)以上并且三点弯曲强度600mpa以上的氮化硅基板。

60.此外,在使设置于陶瓷基板的表面的铜电路部与设置于背面的背铜板通过贯通孔而导通时,准备具有贯通孔的陶瓷基板。在陶瓷基板中设置贯通孔的情况下,也可以预先在成形体的阶段设置贯通孔。此外,也可以在陶瓷基板(陶瓷烧结体)中设置贯通孔。贯通孔通过激光加工、切削加工等而设置。作为切削加工,可列举出利用钻孔等的开孔加工。

61.关于铜板,在以与陶瓷的接合条件进行加热时,优选准备内部的铜晶粒的距离lh的平均为300μm以下的铜板。进而,优选准备各个距离lh为400μm以下的铜板。各个距离lh优选为50μm以上,更优选为70μm以上。

62.此外,关于铜板,在以与陶瓷的接合条件进行加热时,优选准备内部的铜晶粒的长度lv的平均为300μm以下的铜板。进而,优选准备各个长度lv为400μm以下的铜板。各个长度lv优选为50μm以上,更优选为70μm以上。

63.在将陶瓷基板与铜板通过活性金属接合法而接合的情况下,接合温度成为700~900℃左右。若铜板被暴露于该温度下,则铜进行再结晶,因此晶粒变大。优选按照铜晶粒的距离lh及长度lv成为上述的范围内的方式,使用与上述的范围相比包含更短的距离lh及更

短的长度lv的铜晶粒的铜板。

64.此外,陶瓷基板与铜板优选通过活性金属接合法而接合。在活性金属接合法中,使用将ti等活性金属与ag混合而得到的活性金属钎料。作为活性金属钎料,可列举出ti、ag及cu的混合物。在活性金属钎料中,ti的含量为0.1~10重量%,cu的含量为10~60重量%,剩余部分为ag。此外,根据需要,也可以在1~15重量%的范围内添加选自由in、sn、al、si、c及mg构成的组中的1种以上。

65.将活性金属钎料膏糊化。膏糊混合有钎料成分和有机物。在膏糊中,钎料成分优选成分被均匀地混合。这是由于:若钎料成分不均匀地分布,则钎焊不稳定,成为接合不良的原因。

66.为了将钎料均匀地分散,有各种方法。可以使用利用基于干式及湿式的磨、或搅拌机的混合、预先形成合金并进行粉碎等一般将粉体混合的方法。

67.在钎焊时,由于钎料扩散到铜板内部,铜晶粒变大。因此,在钎料制造时,优选按照不扩散至铜板内部的方式调整钎料。上述的钎料成分中,ag与选自由in及sn构成的组中的至少1种的组合是抑制扩散的成分。因此,按照该组合中所含的元素在膏糊中变得均匀的方式进行混合。可以按照钎料成分变得均匀的方式用充分的时间进行混合,也可以预先追加用于将上述组合混合的工序。

68.将像这样操作而制造的活性金属钎料膏糊涂布于陶瓷基板上。在膏糊上配置铜板。接着,将配置有铜板的陶瓷基板在700~900℃下加热而接合。加热工序根据需要在真空中或非氧化性气氛中进行。此外,在真空中进行的情况下,优选为1

×

10

‑2pa以下。作为非氧化性气氛,可列举出氮气氛、氩气氛等。

69.通过设定为真空中或非氧化性气氛,能够抑制接合层被氧化。由此,可谋求接合强度的提高。此外,可以调整接合温度、时间而调整钎料向铜板内的扩散。

70.为了控制钎料成分向铜板内的扩散状态,优选在加热接合工序中,进行活性金属钎料膏糊的脱脂工序。在加热接合工序中,接合温度被保持在700~900℃的范围内。在温度达到该范围之前,通过将膏糊中的有机物进行脱脂,能够控制钎料的成分向铜板内的扩散量。这是由于:若在接合前将钎料膏糊中的有机物进行脱脂,则能够将与铜板相接触的钎料均质化。

71.在钎料膏糊的脱脂工序中,温度被保持在例如250~500℃的范围内。保持时间为5~60分钟的范围内。此外,作为别的方法,将向接合温度的升温速度设定为10℃/分钟以下也是有效的。

72.此外,接合的铜板可以预先加工成图案形状,也可以是平板。在使用平板的情况下,在接合后实施蚀刻加工,加工成图案形状。

73.通过该工序,可以制造陶瓷铜电路基板。接着,进行将半导体元件等与陶瓷铜电路基板接合的工序。在接合半导体元件的部位设置接合层。接合层优选包含软钎料或钎料。设置接合层,在其上设置半导体元件。此外,根据需要,经由接合层而接合金属端子。此外,根据需要设置引线接合。此外,半导体元件、金属端子、引线接合设置必要的数目。

74.(实施例)

75.(实施例1~22、比较例1~9)

76.作为陶瓷基板,准备了氮化硅基板、氮化铝基板及氧化铝(alumina)基板。氮化硅

基板的热导率为90w/(m

·

k),三点弯曲强度为650mp。氮化铝基板的热导率为170w/(m

·

k),三点弯曲强度为300mpa。氧化铝基板的热导率为20w/(m

·

k),三点弯曲强度为350mpa。陶瓷基板的尺寸为纵50mm

×

横40mm。氮化硅基板的厚度为0.32mm。氮化铝基板的厚度及氧化铝基板的厚度为0.635mm。

77.接着,准备表1中所示的铜板。从母材将铜板切取成纵40mmx横30mm,作为用于测定加热后的晶界水平距离及晶界垂直距离的测定用试验铜板。将测定用试验板在氮气氛中600℃下进行1小时间加热后,按照成为横30mm的长度的方式沿横向切断。对切断的试验板的中央部附近(距离端部为约15mm的位置)用扫描型电子显微镜(sem:scanning electron microscope)以倍率20倍进行观察,拍摄照片。对于厚度方向的测定位置,厚度为0.5mm的铜板1~9对从背面至表面为止的整体进行测定。厚度为0.8mm的铜板10~18对厚度方向的端部附近(从上下表面至约150μm的部位为止)进行测定。

78.铜板中的铜晶粒的距离lh及长度lv通过以下的步骤来计算。首先,在所观察的区域,画与第1方向平行的任意的直线。接着,抽出与该直线交叉的5个铜晶粒。5个铜晶粒随机地抽出。但是,被观察区域的端切断的晶粒除外。对于5个铜晶粒各自,测定任意的直线与铜晶粒的外缘之间的第2方向上的距离lh,将其平均值作为距离lh示于表1中。此外,对于5个铜晶粒各自,测定任意的直线与铜晶粒的外缘之间的交点彼此的第1方向上的长度lv,将其平均值作为长度lv示于表1中。

79.表1

[0080][0081]

接着,将陶瓷基板与铜板通过活性金属接合法而接合。所使用的铜板使用与从母材切成纵40mmx横30mm的测定用试验铜板相同尺寸的铜板。关于活性金属接合法中使用的活性金属钎料,ti的含量为2重量%,sn的含量为10重量%,cu的含量为30重量%,剩余部分

为ag。

[0082]

关于活性金属膏糊,准备将所使用的材料同时混合(普通混合)而得到的钎料、和预先将sn与ag混合后混合(预混合)其他的活性金属钎料成分而得到的钎料,分别通过混合有机成分而膏糊化。

[0083]

将活性金属膏糊涂布于陶瓷基板的两面,分别配置铜板而进行加热接合工序。此外,接合温度设定为790~850℃,接合时间设定为5~20分钟,在真空中(1

×

10

‑2pa以下)进行接合。通过改变接合温度及接合时间,控制铜板内部的铜晶粒的粒生长。

[0084]

此外,对表面的铜板(表铜板)进行蚀刻加工而制成电路形状。表铜板加工成2~4个中的任一电路形状,背面的铜板(背铜板)也蚀刻加工成电路形状。在表铜板的精细图案形成中,将图案尺寸设定为0.5mm。关于厚度为0.5mm的表铜板,将侧面蚀刻量及钎料的溢出量设定为零的情况的图案间尺寸设定为0.8mm而进行蚀刻。关于厚度为0.8mm的表铜板,将侧面蚀刻量及钎料的溢出量设定为零的情况的图案间尺寸设定为1.1mm而进行蚀刻。厚度为0.5mm的表铜板与厚度为0.8mm的表铜板以相同条件进行蚀刻。

[0085]

在这些制造条件下,进行了预混合的膏糊通过与普通混合的膏糊相比分散变得均匀,能够抑制铜晶粒的生长。但是,预混合是在普通混合中追加工序。因此,在采用预混合的情况下,与普通混合相比,性价比差。

[0086]

此外,关于790~850℃的接合温度,低的接合温度能够抑制铜晶粒的生长。但是,通过临近可接合温度的下限,有可能变得容易产生剥离、或接合强度降低。

[0087]

此外,关于5~20分钟的接合时间,短的接合时间能够抑制铜的粒生长。但是,接合时间变得越短,则钎料无法充分反应的可能性变得越高,越有可能接合强度降低。

[0088]

因此,在实施例1~22中,基于表1中测定的距离lh及长度lv,对于距离lh、长度lv小的铜板,采用通常的制造条件(普通混合膏糊、接合温度830℃、接合时间10分钟)。对于距离lh、长度lv大的铜板,采用抑制铜晶粒的粒生长的制造条件(预混合膏糊、接合温度790℃、接合时间5分钟)。

[0089]

与此相对,比较例1~3中,对于表1中测定的距离lh及长度lv大的铜板,采用通常的制造条件(普通混合膏糊、接合温度830℃、接合时间10分钟)。比较例4~5中,对于表1中测定的距离lh及长度lv进一步大的铜板,采用抑制铜晶粒的粒生长的制造条件(预混合膏糊、接合温度790℃、接合时间5分钟)。比较例6~9中,采用进一步促进铜晶体的粒生长的制造条件(接合温度850℃、接合时间20分钟)。

[0090]

将所得到的陶瓷铜电路基板示于表2中。

[0091]

表2

[0092][0093]

接着,对于所得到的样品,用sem观察截面组织,测定距离lh及长度lv。基于所测定的距离lh及长度lv,求出距离lh1~lh4及长度lv1~lv4。距离lh1为多个距离lh的最大值。距离lh2为多个距离lh的平均值。距离lh3为多个距离lh的最小值。距离lh4为最大值(lh1)与最小值(lh3)之差。长度lv1为多个长度lv的最大值。长度lv2为多个长度lv的平均值。长度lv3为多个长度lv的最小值。长度lv4为最大值(lv1)与最小值(lv3)之差。

[0094]

将其结果示于表3中。

[0095]

表3

[0096][0097]

如由表获知的那样,实施例的陶瓷铜电路基板的距离lh1及长度lv1为优选的实施方式的范围内。另一方面,关于比较例,距离lh1及长度lv1比实施例大。

[0098]

接着,关于实施例及比较例的陶瓷铜电路基板,调查侧面蚀刻的量。通过光学显微镜测定铜电路部的表面和背面的水平距离,将最远的距离设定为侧面蚀刻量。

[0099]

此外,利用投影仪测定图案间尺寸。作为图案间尺寸,测定在接合层中测定上述的侧面蚀刻量的部位与和该部位相邻的另一接合层之间的距离。

[0100]

此外,作为铜电路部与陶瓷基板之间的接合强度,测定剥离强度。剥离强度通过将预先以3mm宽度形成的铜电路部沿着第1方向以50mm/分钟剥离来测定。此外,陶瓷电路基板的接合强度通过利用三点弯曲夹具从上下方向挤压陶瓷电路基板来测定。

[0101]

接着,对实施例及比较例的陶瓷铜电路基板评价可靠性。作为可靠性,评价半导体元件的接合性。

[0102]

需要说明的是,在本评价中,不使用为了测定铜晶体粒径而切断后的试样、测定接合强度或三点弯曲强度后的试样,而是作为可靠性的评价用,分别使用以与实施例及比较例相同的条件制作的试样。

[0103]

半导体元件的接合性使用无铅软钎料来接合半导体元件及金属端子。进一步设置

引线接合,使半导体元件与金属端子导通。由此,制作半导体装置。接着,对半导体装置进行温度循环试验(tct),调查导通不良的发生率。tct中,将

‑

40℃

×

30分钟

→

室温

×

10分钟

→

150℃

×

30分钟

→

室温

×

10分钟设定为1个循环,通过超音波探伤法(sat:scanning acoustic tomograph)算出300个循环后的因裂纹而产生的剥离面积。然后,评价未剥离面积率η。未剥离面积率η将通过tct完全没有裂纹的产生的情况设定为η=100%,将通过tct而在陶瓷铜电路基板的接合部整面中产生裂纹的情况设定为η=0%。

[0104]

将各个测定结果示于表4中。

[0105]

表4

[0106][0107]

实施例的陶瓷铜电路基板中,关于距离lh2及长度lv2这两者都满足300μm以下的陶瓷铜电路基板,在铜板厚度为0.5mm的情况下,侧面蚀刻量低于0.10mm。在铜板厚度为0.8mm的情况下,低于0.20mm。伴随着侧面蚀刻量的降低,图案间尺寸变大。即,关于实施例的陶瓷铜电路基板,即使是与比较例相同的蚀刻条件,也能够减小图案间尺寸,能够形成精细图案。此外,通过铜电路部的应力缓和的效果,接合强度为24kn/m以上。关于氮化硅基板,三点弯曲强度为600mpa。关于氮化铝基板,三点弯曲强度为250mpa。关于氧化铝基板,三点弯曲强度为300mpa以上。像这样,根据实施例,得到可靠性高的陶瓷铜电路基板。

[0108]

此外,实施例的陶瓷铜电路基板中,距离lh2或长度lv2中的仅任一者为300μm以下的陶瓷铜电路基板分别得到关于侧面蚀刻量良好的陶瓷铜电路基板、或通过应力缓和而接合强度和三点弯曲强度良好的陶瓷铜电路基板。

[0109]

关于距离lh1及长度lv1,分别满足300μm以下的陶瓷铜电路基板得到良好的结果。

[0110]

关于距离lh3及长度lv3,分别满足200μm以下的陶瓷铜电路基板得到良好的结果。

[0111]

关于距离lh4及长度lv4,分别满足220μm以下的陶瓷铜电路基板得到良好的结果。

[0112]

与此相对,比较例的侧面蚀刻量大,产生未形成图案间的状态(短路),并且接合强度、三点弯曲强度低。由该结果获知,距离lh及长度lv对侧面蚀刻量、接合强度、三点弯曲强度造成影响。

[0113]

此外,在实施例和比较例中,未剥离面积率η产生差异。这是由于:实施例中通过控制铜电路内部的距离lh1及长度lv1,侧面蚀刻量、接合强度及三点弯曲强度提高。

[0114]

与此相对,在比较例中存在未剥离面积率η恶化的情况。这是由于:在铜电路部中,铜晶粒的距离lh2及长度lv2大,侧面蚀刻量变大。此外由于:接合强度及三点弯曲强度降低,陶瓷铜电路基板内部的热应力变大,从而对接合部分造成的负荷变大。

[0115]

以上,例示出了本发明的几个实施方式,但这些实施方式是作为例子提出的,并不意图限定发明的范围。这些新颖的实施方式可以以其他的各种方式实施,在不脱离发明的主旨的范围内,可以进行各种省略、置换、变更等。这些实施方式、其变形例包含于发明的范围、主旨中,同时包含于权利要求书中记载的发明和其同等的范围内。此外,上述的各实施方式可以相互组合而实施。

[0116]

符号的说明

[0117]

1陶瓷铜电路基板

[0118]

2陶瓷基板

[0119]

3铜电路部(表铜板)

[0120]

4接合层(钎料)

[0121]

5铜电路部(背铜板)

[0122]

6铜电路截面图(a部放大图)

[0123]

7与基板的厚度方向垂直且任意地画的线

[0124]

8侧面蚀刻量

[0125]

9铜板内部截面图(b部放大)

[0126]

10铜晶粒

[0127]

11铜晶粒的晶界

[0128]

12距离(lh)

[0129]

13长度(lv)

[0130]

14图案尺寸

[0131]

15图案间尺寸

[0132]

16半导体装置

[0133]

17半导体元件

[0134]

18接合层

[0135]

19引线接合

[0136]

20金属端子

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。