技术特征:

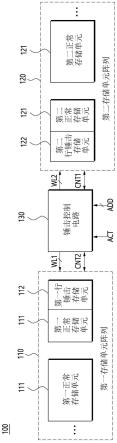

1.一种半导体存储装置,包括:第一存储单元阵列,在所述第一存储单元阵列中,多个第一正常存储单元中的至少一个包括第一行锤击存储单元;第二存储单元阵列,在所述第二存储单元阵列中,多个第二正常存储单元中的至少一个包括第二行锤击存储单元;以及锤击控制电路,其:进行控制以将对连接到所述第一正常存储单元的第一字线的激活操作的次数存储到所述第二行锤击存储单元中;以及进行控制以将对连接到所述第二正常存储单元的第二字线的激活操作的次数存储到所述第一行锤击存储单元中。2.根据权利要求1所述的半导体存储装置,其中:所述第一行锤击存储单元包括具有与所述第二字线对应的数量的计数存储单元;以及所述第二行锤击存储单元包括具有与所述第一字线对应的数量的计数存储单元。3.根据权利要求1所述的半导体存储装置,其中,所述锤击控制电路基于激活命令信号和地址信号来执行对所述第一字线和所述第二字线中的任何一个的正常激活操作以及对另一字线的计数激活操作。4.根据权利要求3所述的半导体存储装置,其中,所述锤击控制电路在所述正常激活操作期间对激活操作的次数进行计数。5.根据权利要求1所述的半导体存储装置,其中:所述第一正常存储单元和所述第一行锤击存储单元通过第一局部数据线发送和接收数据;以及所述第二正常存储单元和所述第二行锤击存储单元通过第二局部数据线发送和接收数据。6.根据权利要求5所述的半导体存储装置,其中,所述锤击控制电路包括:字线驱动电路,其基于激活命令信号和地址信号来激活所述第一字线和所述第二字线;第一读写驱动电路,其连接到所述第一局部数据线并且对所述第一存储单元阵列执行读操作和写操作;第二读写驱动电路,其连接到所述第二局部数据线并且对所述第二存储单元阵列执行读操作和写操作;锤击驱动控制电路,其基于所述激活命令信号和所述地址信号来生成与所述第一读写驱动电路和所述第二读写驱动电路中的每一个相对应的计数读命令信号和计数写命令信号;以及锤击算术电路,其:在正常激活操作期间接收从所述第一读写驱动电路和所述第二读写驱动电路输出的第一计数值和第二计数值;对所述第一计数值和所述第二计数值分别执行加法运算;以及输出相应的加法结果。7.根据权利要求6所述的半导体存储装置,其中,所述第一读写驱动电路和所述第二读

写驱动电路各自执行:基于所述计数读命令信号的计数读操作;以及基于所述计数写命令信号的计数写操作。8.根据权利要求6所述的半导体存储装置,其中:所述第一计数值对应于对所述第一字线的激活操作的次数;以及所述第二计数值对应于对所述第二字线的激活操作的次数。9.根据权利要求6所述的半导体存储装置,其中,所述锤击驱动控制电路包括:第一延迟电路,其将所述激活命令信号延迟与计数读操作相对应的时间,以及输出延迟的信号;第二延迟电路,其将所述激活命令信号延迟与计数写操作相对应的时间,以及输出延迟的信号;以及锤击命令输出电路,其基于所述地址信号以及所述第一延迟电路的输出信号和所述第二延迟电路的输出信号来输出所述计数读命令信号和所述计数写命令信号。10.根据权利要求6所述的半导体存储装置,还包括地址锁存电路,所述地址锁存电路:基于所述第一计数值和所述第二计数值中的每一个以及最大行锤击值来检测行锤击;以及锁存与对应字线相对应的地址信号。11.根据权利要求10所述的半导体存储装置,其中,所述地址锁存电路包括:比较电路,其通过将所述第一计数值和所述第二计数值中的每一个与所述最大行锤击值相比较来生成检测信号;以及锁存电路,其基于所述检测信号来锁存所述地址信号。12.根据权利要求10所述的半导体存储装置,其中,所述字线驱动电路基于锤击刷新命令信号对与其中已发生行锤击的字线相邻的字线执行刷新操作。13.根据权利要求12所述的半导体存储装置,其中,所述字线驱动电路包括:激活驱动电路,其基于所述激活命令信号和所述地址信号来激活所述第一字线和所述第二字线;地址转换电路,其通过转换由所述地址锁存电路锁存的地址信号来生成刷新地址信号;以及刷新驱动电路,其基于所述锤击刷新命令信号对与所述刷新地址信号相对应的字线执行刷新操作。14.根据权利要求12所述的半导体存储装置,还包括:锤击刷新控制电路,当在所述第一字线和所述第二字线中检测到行锤击时,所述锤击刷新控制电路生成所述锤击刷新命令信号。15.根据权利要求1所述的半导体存储装置,还包括:复位电路,其在复位操作期间复位存储在所述第一行锤击存储单元和所述第二行锤击存储单元中的数据。16.根据权利要求15所述的半导体存储装置,其中,所述复位电路包括:字线驱动电路,其基于与所述复位操作相对应的复位信号来对分别连接到所述第一行锤击存储单元和所述第二行锤击存储单元的所述第一字线和所述第二字线执行激活操作;

以及初始化驱动电路,其基于所述复位信号对初始化数据值执行在所述第一行锤击存储单元和所述第二行锤击存储单元中的写操作。17.一种半导体存储装置的操作方法,所述半导体存储装置:包括第一存储单元阵列,在所述第一存储单元阵列中,多个第一正常存储单元中的至少一个包括第一行锤击存储单元;以及包括第二存储单元阵列,在所述第二存储单元阵列中,多个第二正常存储单元中的至少一个包括第二行锤击存储单元,所述操作方法包括:基于激活命令信号和地址信号对连接到所述第一正常存储单元的第一字线执行激活操作;执行关于与对所述第一字线的激活操作的次数相对应的第一计数值的读操作;通过反映对所述第一字线的激活操作的次数来执行对所述第一计数值的算术运算;以及执行将所述第一计数值写入所述第二行锤击存储单元中的写操作。18.根据权利要求17所述的操作方法,其中,执行所述激活操作包括对所述第一字线执行正常激活操作。19.根据权利要求17所述的操作方法,其中,执行所述读操作包括执行:对连接到所述第二行锤击存储单元的第二字线的计数激活操作;以及对存储在所述第二行锤击存储单元中的所述第一计数值的计数读操作。20.根据权利要求17所述的操作方法,其中,执行所述算术运算包括:在对所述第一字线的所述激活操作期间执行对所述第一计数值的加法运算。21.根据权利要求17所述的操作方法,其中,执行所述写操作包括:执行计数写操作以将所述第一计数值写入所述第二行锤击存储单元中。22.根据权利要求17所述的操作方法,还包括:将所述第一计数值与最大行锤击值相比较;以及基于在比较的步骤中生成的检测信号对与其中已发生行锤击的字线相邻的字线执行刷新操作。23.根据权利要求22所述的操作方法,还包括:在所述半导体存储装置的初始化操作区段和所述刷新操作之后,对所述第一行锤击存储单元和所述第二行锤击存储单元执行复位操作。24.根据权利要求23所述的操作方法,其中,执行所述复位操作包括执行:对所述第一字线和所述第二字线的激活操作;以及将初始化数据值写入所述第一行锤击存储单元和所述第二行锤击存储单元中的写操作。25.一种半导体存储系统,包括:半导体存储装置,其包括:第一存储单元阵列,在所述第一存储单元阵列中,多个第一正常存储单元中的至少一个包括第一行锤击存储单元;第二存储单元阵列,在所述第二存储单元阵列中,多个第二正常存储单元中的至少一个包括第二行锤击存储单元;

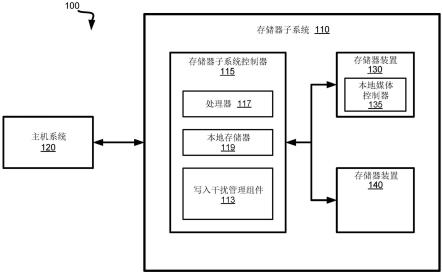

锤击控制电路,其进行控制以将与对连接到所述第一正常存储单元的第一字线的激活操作的次数相对应的第一计数值存储到所述第二行锤击存储单元中,以及进行控制以将与对连接到所述第二正常存储单元的第二字线的激活操作的次数相对应的第二计数值存储到所述第一行锤击存储单元中;以及地址锁存电路,其基于所述第一计数值和所述第二计数值中的每一个以及最大行锤击值生成检测到行锤击的检测信号,以及锁存与对应字线相对应的地址信号;以及控制设备,其基于所述检测信号来提供包括锤击刷新命令信号的外部命令信号,其中,所述锤击控制电路基于所述锤击刷新命令信号和由所述地址锁存电路锁存的所述地址信号来对与其中已发生行锤击的字线相邻的字线执行刷新操作。

技术总结

本申请公开了半导体存储装置、其操作方法以及包括其的半导体存储系统。该半导体存储装置包括第一存储单元阵列、第二存储单元阵列以及锤击控制电路。第一存储单元阵列包括第一行锤击存储单元。第二存储单元阵列包括第二行锤击存储单元。锤击控制电路进行控制以将对第一字线的激活操作的次数存储到第二行锤击存储单元中,以及进行控制以将对第二字线的激活操作的次数存储到第一行锤击存储单元中。作的次数存储到第一行锤击存储单元中。作的次数存储到第一行锤击存储单元中。

技术研发人员:李约瑟

受保护的技术使用者:爱思开海力士有限公司

技术研发日:2022.02.25

技术公布日:2023/2/17

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。