一种mini led cog线路结构及其制作方法

技术领域

1.本发明属于显示技术领域,具体涉及一种mini led cog线路结构及其制作方法。

背景技术:

2.随着科学技术的不断发展,消费者对显示行业的要求越来越高。日益发展的mini led和micro led等新型显示技术,随着mini led和micro led显示技术向更高像素密度产品升级,当mini led背光进入极致控光超高分区阶段,micro led进入十微米级甚至纳米级的区间时,cog(chip on glass,是指将led芯片直接固晶到玻璃基板,利用tft(薄膜晶体管)驱动实现micro led显示)的优势将愈发明显。

3.cog的核心基础工艺是基于玻璃基板上采用镀厚金属工艺,在玻璃上制作超精细的金属集成电路。但是在现阶段,镀膜的膜层厚度和金属膜叠加的工艺存在巨大问题,在各个膜层间的附着力难以控制,且存在膜层与厚金属层之间脱落附着力差的问题。

4.针对镀厚金属层的附着力差和叠加厚度效率低的问题,现有技术提出的主要解决方案是:1)电镀铜:现阶段电镀铜工艺应用在玻璃基板上不成熟,电镀厚金属层的厚度不达标且均匀性较差。2)普通pvd镀厚铜:采用堆叠铜层的方式来完成镀膜,但现阶段pvd镀厚铜工艺的效率不高且膜层附着力问题难以解决。

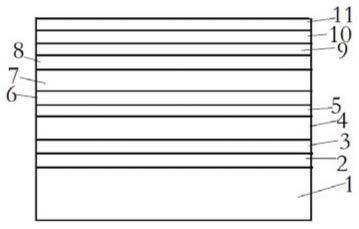

技术实现要素:

5.本发明的目的在于提供一种mini led cog线路结构及其制作方法,过渡膜层和金属层相结合,过渡膜层具有金属键结合和扩散的优势,提高了膜层与金属层之间高附着力,并具有良好的结构稳定性,且金属层与过渡膜层相结合进一步改善厚金属层的厚度和效率问题。且,本技术结构简单,制备方法简单,可量产。

6.本发明具体技术方案如下:

7.一种mini led cog线路结构,包括承载基板,所述承载基板上依次设置:打底层、第一过渡膜层、第一金属层、第二过渡膜层、绝缘层、第一感光保护层、第三过渡膜层、第二金属层、绝缘保护层和第二感光保护层。

8.所述承载基板的厚度为0.1~10mm;

9.所述承载基板材料选择但不限于铝硅玻璃、钠钙玻璃、硼硅玻璃或石英玻璃。

10.所述打底层的厚度为0.01~10μm。

11.所述打底层的材料选择但不限于氮化硅、二氧化硅、钼、钛或镍中的一种或多种,采用以上材料,不仅具有打底保护的作用,而且能增加附着力、完善结构。

12.所述第一过渡膜层的厚度为0.01~10μm。

13.所述第一过渡膜层的材料包括但不限于钼铌合金、钼铜合金、钛铜合金、镍铜合金中的一种或多种。

14.所述第一金属层的厚度为0.1~100μm;

15.所述第一金属层的材料包括但不限于银、金、铜、钼铌合金、钼铜合金、钛铜合金、

镍铜合金的一种或多种。

16.所述第二过渡膜层的厚度为0.1~10μm。

17.所述第二过渡膜层的材料包括但不限于钼铌合金、钼铜合金、钛铜合金、镍铜合金中的一种或多种;

18.所述绝缘层的厚度为0.1~5μm;

19.所述绝缘层的材料包括但不限于氮化硅、二氧化硅中的一种或多种。

20.所述第一感光保护层的厚度为5~30μm。

21.所述第一感光保护层包括但不限于半导体光刻胶、oc胶、紫外光刻胶、负性光刻胶中的一种或多种。

22.所述第三过渡层厚度为0.1~10μm。

23.所述第三过渡层的材料包括但不限于银、金、铜、钼铌、钼铜、钛铜、镍铜合金中的一种或多种。

24.所述第二金属层的厚度为0.1~10μm。

25.所述第二金属层的材料包括但不限于银、金、铜中的一种或多种。

26.所述绝缘保护层的厚度为0.1~5μm;

27.所述绝缘保护层的材料包括但不限于氮化硅、二氧化硅中的一种或多种。

28.所述第二感光保护层的厚度为5~15μm。

29.所述第二感光保护层的材料包括但不限于氮化硅、二氧化硅、半导体光刻胶、oc胶、紫外光刻胶、负性光刻胶中的一种或多种。

30.本发明形成各膜层,可以选择的方法是电镀、化学溶液沉积法、化学气相沉积法、真空蒸镀法、真空磁控溅射法;在形成的膜层制作线路,包括干蚀刻法和湿蚀刻法的工艺。

31.本发明提供的一种mini led cog线路结构的制作方法,包括以下步骤:

32.1)、对承载基板表面处理;

33.2)、在步骤1)得到的承载基板的单面层依次制备打底层、第一过渡膜层、第一金属层和第二过渡膜层,再进行湿法刻蚀;

34.3)、再制备绝缘层,再进行干法刻蚀;

35.4)、再制作第一感光保护层,再曝光、显影;

36.5)、再制作第三过渡膜层和第二金属层,然后湿法蚀刻;

37.6)、再制备绝缘保护层,进行干法刻蚀;

38.7)、再制备第二感光保护层,曝光、显影,形成完整的集成电路结构。

39.步骤1)所述表面处理包括清洗和plasma电浆清洗,整体的清洗时间为5s-10s;

40.步骤2)中,承载基板的打底层制备采用真空磁控溅射的方法,镀膜功率为6~9kw、镀膜压强为300~600千帕、镀膜时间为1~2分钟、加热温度为200~300℃。

41.步骤2)中所述第一过渡膜层、第一金属层、第二过渡膜层制备工艺为真空磁控溅射或电镀;

42.采用真空磁控溅射时,镀膜功率为13~20kw、镀膜压强为300~500千帕、镀膜时间为3~5分钟。

43.优选的,步骤2)中,在真空磁控溅射制备第一金属层时,腔室加热可以关闭;在真空磁控溅射制备第一过渡膜层、第二过渡膜层时,加热温度为200~300℃;

44.采用电镀制备时,电镀时间为6~10分钟、电流密度为1~1.5a/dm2;

45.步骤2)中,第一过渡膜层、第一金属层和第二过渡膜层制备后,进行湿法蚀刻,采用市售刻蚀液,蚀刻参数为:刻蚀时间为8~15分钟、温度为25~30℃,冲洗速度为80~100ml/s;

46.步骤3)中绝缘层的制备工艺为化学气相沉积法,沉积时间110~120分钟、温度为450℃;

47.步骤3)中绝缘层制备完成后,进行干法刻蚀,温度为30℃~85℃,压强为200千帕~450千帕,时间为8~15分钟;绝缘层主要作用通过干法刻蚀打孔把第一金属层和第二金属层以及通过电路设计形成电性连接;

48.步骤4)中,第一感光保护层的制备工艺为涂布、曝光、显影;涂布感光保护层材料,涂布方式为狭缝涂布,涂布时间为10s~20s、涂布表干温度70~100℃,曝光能量为100~150j、曝光时间为3~10分钟;显影时间为2~3分钟、显影速度为2.5m/分钟。

49.步骤5)中,所述第三过渡膜层、第二金属层的工艺为真空磁控溅射或电镀;

50.采用真空磁控溅射制备时,镀膜功率为13~20kw、镀膜压强为300~500千帕、镀膜时间为3~5分钟。

51.步骤5)中,在真空磁控溅射制备第二金属层时,腔室加热温度可以关闭。制备第三过渡膜层时,加热温度为200~300℃。

52.步骤5)中,采用电镀制备时,工艺参数:时间为6~10分钟、电流密度为1~1.5a/dm2;

53.步骤5)中,制备第三过渡膜层、第二金属层的后,进行湿法蚀刻,蚀刻液为市售刻蚀液,刻蚀参数为:时间为3~5分钟、温度为25~30℃。

54.步骤6)中,绝缘保护层的制备工艺为化学气相沉积法,沉积时间110~120分钟、温度为450℃;制备后,采用干法刻蚀,温度为30℃~85℃,压强为200千帕~450千帕,时间为8~15分钟;绝缘层主要作用通过干法刻蚀打孔把正负电极露出。

55.步骤7)中,第二感光保护层的制备工艺为涂布、曝光、显影,涂布感光保护层材料,涂布方式为狭缝涂布、涂布时间为10s~20s、涂布表干温度70~100℃;曝光能量为100~150j、曝光时间为3~10分钟;显影时间为2~3分钟、显影速度为2.5m/分钟。第二感光保护层主要作用通过曝光、显影把正负电极露出。

56.本发明将现有的镀厚金属层结构改善,使过渡膜层和金属层相结合,过渡膜层具有金属键结合和扩散的优势,确定了膜层与金属层之间高附着力,并具有良好的结构稳定性,且金属层与过渡膜层相结合进一步改善厚金属层的厚度和效率问题。本发明有效解决了厚金属层附着力的问题和厚金属层更高厚度的需求,且工艺结构简单,膜层结构的可量产性较高。

57.本发明对mini led cog线路结构改进,不仅没有增加较高的生产成本和生产难度,而且工艺结构简单,产品的量产性较高。

附图说明

58.图1为本发明mini led cog线路结构示意图。

具体实施方式

59.本发明提供一种mini led cog线路结构,包括承载基板,所述承载基板上依次设置:打底层、第一过渡膜层、第一金属层、第二过渡膜层、绝缘层、第一感光保护层、第三过渡膜层、第二金属层、绝缘保护层和第二感光保护层。

60.所述承载基板的厚度为0.1~10mm;

61.所述承载基板材料选择但不限于铝硅玻璃、钠钙玻璃、硼硅玻璃或石英玻璃。

62.所述打底层的厚度为0.01~10μm。

63.所述打底层的材料选择但不限于氮化硅、二氧化硅、钼、钛或镍中的一种或多种,采用以上材料,不仅具有打底保护的作用,而且能增加附着力、完善结构。

64.所述第一过渡膜层的厚度为0.01~10μm。

65.所述第一过渡膜层的材料包括但不限于钼铌合金、钼铜合金、钛铜合金、镍铜合金中的一种或多种。

66.所述第一金属层的厚度为0.1~100μm;

67.所述第一金属层的材料包括但不限于银、金、铜、钼铌合金、钼铜合金、钛铜合金、镍铜合金的一种或多种。

68.所述第二过渡膜层的厚度为0.1~10μm。

69.所述第二过渡膜层的材料包括但不限于钼铌合金、钼铜合金、钛铜合金、镍铜合金中的一种或多种;

70.所述绝缘层的厚度为0.1~5μm;

71.所述绝缘层的材料包括但不限于氮化硅、二氧化硅中的一种或多种。

72.所述第一感光保护层的厚度为5~30μm。

73.所述第一感光保护层包括但不限于半导体光刻胶、oc胶、紫外光刻胶、负性光刻胶中的一种或多种。

74.所述第三过渡层厚度为0.1~10μm。

75.所述第三过渡层的材料包括但不限于银、金、铜、钼铌、钼铜、钛铜、镍铜合金中的一种或多种。

76.所述第二金属层的厚度为0.1~10μm。

77.所述第二金属层的材料包括但不限于银、金、铜中的一种或多种。

78.所述绝缘保护层的厚度为0.1~5μm;

79.所述绝缘保护层的材料包括但不限于氮化硅、二氧化硅中的一种或多种。

80.所述第二感光保护层的厚度为5~15μm。

81.所述第二感光保护层的材料包括但不限于氮化硅、二氧化硅、半导体光刻胶、oc胶、紫外光刻胶、负性光刻胶中的一种或多种。

82.mini led cog线路结构的制作方法,包括以下步骤:

83.1)、对承载基板表面处理:包括清洗和plasma电浆清洗,整体的清洗时间为5s-10s;

84.2)、在步骤1)得到的承载基板的单面层依次制备打底层、第一过渡膜层、第一金属层和第二过渡膜层,再进行湿法刻蚀,具体为:

85.承载基板的打底层制备采用真空磁控溅射的方法,镀膜功率为6~9kw、镀膜压强

为300~600千帕、镀膜时间为1~2分钟、加热温度为200~300℃。再制备第一过渡膜层、第一金属层、第二过渡膜层,制备工艺为真空磁控溅射或电镀;采用真空磁控溅射时,镀膜功率为13~20kw、镀膜压强为300~500千帕、镀膜时间为3~5分钟。在真空磁控溅射制备第一金属层时,腔室加热可以关闭;在真空磁控溅射制备第一过渡膜层、第二过渡膜层时,加热温度为200~300℃;采用电镀制备时,电镀时间为6~10分钟、电流密度为1~1.5a/dm2;第一过渡膜层、第一金属层和第二过渡膜层制备后,进行湿法蚀刻,采用市售刻蚀液,蚀刻参数为:刻蚀时间为8~15分钟、温度为25~30℃,冲洗速度为80~100ml/s。

86.3)、再制备绝缘层,再进行干法刻蚀,具体为:采用化学气相沉积法制备绝缘层,沉积时间110~120分钟、温度为450℃;绝缘层制备完成后,进行干法刻蚀,温度为30℃~85℃,压强为200千帕~450千帕,时间为8~15分钟;绝缘层主要作用通过干法刻蚀打孔把第一金属层和第二金属层以及通过电路设计形成电性连接;

87.4)、再制作第一感光保护层,第一感光保护层的制备工艺为涂布、曝光、显影;涂布感光保护层材料,涂布方式为狭缝涂布,涂布时间为10s~20s、涂布表干温度70~100℃,曝光能量为100~150j、曝光时间为3~10分钟;显影时间为2~3分钟、显影速度为2.5m/分钟。

88.5)、再制作第三过渡膜层和第二金属层,然后湿法蚀刻;第三过渡膜层、第二金属层的工艺为真空磁控溅射或电镀;采用真空磁控溅射制备时,镀膜功率为13~20kw、镀膜压强为300~500千帕、镀膜时间为3~5分钟;在真空磁控溅射制备第二金属层时,腔室加热温度可以关闭。制备第三过渡膜层时,加热温度为200~300℃;采用电镀制备时,工艺参数:时间为6~10分钟、电流密度为1~1.5a/dm2;制备第三过渡膜层、第二金属层的后,进行湿法蚀刻,蚀刻液为市售刻蚀液,刻蚀参数为:时间为3~5分钟、温度为25~30℃。

89.6)、再制备绝缘保护层,进行干法刻蚀;绝缘保护层的制备工艺为化学气相沉积法,沉积时间110~120分钟、温度为450℃;制备后,采用干法刻蚀,温度为30℃~85℃,压强为200千帕~450千帕,时间为8~15分钟;绝缘层主要作用通过干法刻蚀打孔把正负电极露出。

90.7)、再制备第二感光保护层,曝光、显影,形成完整的集成电路结构;具体为:第二感光保护层的制备工艺为涂布、曝光、显影,涂布感光保护层材料。涂布方式为狭缝涂布、涂布时间为10s~20s、涂布表干温度70~100℃;曝光能量为100~150j、曝光时间为3~10分钟;显影时间为2~3分钟、显影速度为2.5m/分钟。第二感光保护层主要作用通过曝光、显影把正负电极露出。

91.以下为本发明几个优选的实施例:

92.实施例1

93.一种mini led cog线路结构,包括承载基板,所述承载基板上依次设置:打底层、第一过渡膜层、第一金属层、第二过渡膜层、绝缘层、第一感光保护层、第三过渡膜层、第二金属层、绝缘保护层和第二感光保护层。

94.所述承载基板的厚度为5mm,选择硼硅玻璃。

95.所述打底层的厚度为0.2μm,材料选择氮化硅。

96.所述第一过渡膜层的厚度为1.8μm,材料为钼铜合金;

97.所述第一金属层的厚度为1.8μm,材料为铜。

98.所述第二过渡膜层的厚度为1.8μm,材料为钼铜合金;

99.所述绝缘层的厚度为0.2μm,材料为氮化硅;

100.所述第一感光保护层的厚度为10μm,材料为半导体光刻胶;

101.所述第三过渡层厚度为0.3μm,材料为铜;

102.所述第二金属层的厚度为0.3μm,材料为银;

103.所述绝缘保护层的厚度为0.2μm,材料氮化硅;

104.所述第二感光保护层的厚度为10μm,材料为半导体光刻胶。

105.实施例1的mini led cog线路结构的制作方法,包括以下步骤:

106.1)、对承载基板表面处理;所述工艺包括清洗和plasma电浆清洗,整体的清洗时间为8s;

107.2)、在步骤1)得到的承载基板的单面层制作打底层、第一过渡膜层、第一金属层、第二过渡膜层;所述打底层制备工艺采用真空磁控溅射,镀膜功率为9kw、镀膜压强为500千帕、镀膜时间为1分钟、加热温度为260℃;第一过渡膜层、第一金属层、第二过渡膜层制备工艺为电镀,制备第一过渡膜层时,电镀时间为6分钟、电流密度为1.5a/m2;制备第一金属层时,电镀时间为7分钟、电流密度为1a/m2;制备第二过渡膜层时,电镀时间为8分钟、电流密度为1a/m2;制备第一金属层时,加热温度关闭。第一过渡膜层、第一金属层和第二过渡膜层制备后,进行湿法蚀刻,采用市售刻蚀液,蚀刻液为参数为时间为9分钟、温度为25℃、冲洗速度为90ml/s。

108.3)再制备绝缘层,制备工艺为化学气相沉积法沉积,时间为110分钟、温度为450℃,后续制程为干法刻蚀,温度为45℃,压强为350千帕,时间为10分钟。

109.4)、在承载基板的绝缘层上制作第一感光保护层后曝光显影;所述第一感光保护层的制备工艺为涂布、曝光、显影,涂布方式为狭缝涂布、涂布时间为12s、涂布表干温度80℃,曝光能量为120j、曝光时间为6分钟、显影时间为2分钟、显影速度为2.5m/分钟。

110.5)、在承载基板的第一感光保护层上制作第三过渡膜层、第二金属层,进行湿法刻蚀;所述第三过渡膜层、第二金属层的工艺为真空磁控溅射,制备第三过渡膜层时,真空磁控溅射镀膜功率为18kw、镀膜压强为400千帕、镀膜时间为3分钟;制备第二金属层时真空磁控溅射镀膜功率为15kw、镀膜压强为410千帕、镀膜时间为3.5分钟;制备第三过渡膜层时,加热温度为280℃。在第二金属层时腔室加热温度关闭。再进行湿法蚀刻,蚀刻液为市售刻蚀液,刻蚀参数为时间为4分钟、温度为25℃;

111.6)再制备绝缘层,绝缘保护层的制备工艺为化学气相沉积法,沉积时间115分钟、温度为450℃;后续制程为干法刻蚀,温度为55℃,压强为330千帕,时间为12分钟。

112.7)、最后制作第二感光保护层形成完整的集成电路结构:所述第二感光保护层的制备工艺为涂布、曝光、显影,涂布方式为狭缝涂布、涂布时间为12s、涂布表干温度80℃,曝光能量为140j、曝光时间为7分钟、显影时间为3分钟、显影速度为2.5m/分钟。第二感光保护层主要作用通过曝光、显影把正负电极露出。

113.实施例2

114.一种mini led cog线路结构,包括承载基板,所述承载基板上依次设置:打底层、第一过渡膜层、第一金属层、第二过渡膜层、绝缘层、第一感光保护层、第三过渡膜层、第二金属层、绝缘保护层和第二感光保护层。

115.所述承载基板的厚度为3mm,材料石英玻璃;

116.所述打底层的厚度为0.3μm,材料选择钼;

117.所述第一过渡膜层的厚度为0.4μm,材料为镍铜合金;

118.所述第一金属层的厚度为50μm,材料为金;

119.所述第二过渡膜层的厚度为5μm,材料为钛铜合金;

120.所述绝缘层的厚度为1μm;材料选择二氧化硅;

121.所述第一感光保护层的厚度为10μm,材料为紫外光刻胶;

122.所述第三过渡层厚度为5μm,材料为铜;

123.所述第二金属层的厚度为3μm,材料为金;

124.所述绝缘保护层的厚度为2μm,材料为二氧化硅;

125.所述第二感光保护层的厚度为10μm;材料为紫外光刻胶。

126.实施例2的mini led cog线路结构的制作方法,包括以下步骤:

127.1)、对承载基板表面处理:包括清洗和plasma电浆清洗,整体的清洗时间为6s;

128.2)、在步骤1)得到的承载基板的单面层上制作打底层、第一过渡膜层、第一金属层和第二过渡膜层;所述打底层制备工艺为电镀,镀膜功率为6kw、镀膜压强为400千帕、镀膜时间为1.5分钟、加热温度为230℃;第一过渡膜层、第一金属层、第二过渡膜层制备工艺为真空磁控溅射,第一过渡膜层制备时,真空磁控溅射镀膜功率为15kw、镀膜压强为430千帕、镀膜时间为3.5分钟;第一金属层制备时,真空磁控溅射镀膜功率为13kw、镀膜压强为400千帕、镀膜时间为3分钟;第二过渡膜层制备时,真空磁控溅射镀膜功率为16kw、镀膜压强为360千帕、镀膜时间为3.5分钟;制备第一过渡膜层、第二过渡膜层加热温度分别为230℃、250℃;制备第一金属层时,加热温度关闭。第一过渡膜层、第一金属层和第二过渡膜层制备后,进行湿法蚀刻,采用市售刻蚀液,蚀刻液为参数为时间为8分钟、温度为27℃、冲洗速度为85ml/s。

129.3)再制备绝缘层,制备工艺为化学气相沉积法沉积,时间为115分钟、温度为450℃,后续制程为干法刻蚀,温度为55℃,压强为300千帕,时间为11分钟。

130.4)、在承载基板的绝缘层上制作第一感光保护层后曝光显影;所述第一感光保护层的制备工艺为涂布、曝光、显影,涂布方式为狭缝涂布、涂布时间为16s、涂布表干温度89℃,曝光能量为145j、曝光时间为5分钟、显影时间为2分钟、显影速度为2.5m/分钟。

131.5)、在承载基板的第一感光保护层上制作第三过渡膜层、第二金属层,进行湿法刻蚀;所述第三过渡膜层、第二金属层的工艺为真空磁控溅射,制备第三过渡膜层时,真空磁控溅射镀膜功率为14kw、镀膜压强为500千帕、镀膜时间为3.5分钟;制备第二金属层时真空磁控溅射镀膜功率为17kw、镀膜压强为400千帕、镀膜时间为3.5分钟;制备第三过渡膜层时,加热温度为240℃。在第二金属层时腔室加热温度关闭。再进行湿法蚀刻,蚀刻液为市售刻蚀液,刻蚀参数为时间为3分钟、温度为30℃;

132.6)再制备绝缘层,绝缘保护层的制备工艺为化学气相沉积法,沉积时间1,8分钟,温度为450℃;后续制程为干法刻蚀,温度为65℃,压强为300千帕,时间为13分钟。

133.7)、最后制作第二感光保护层形成完整的集成电路结构:所述第二感光保护层的制备工艺为涂布、曝光、显影,涂布方式为狭缝涂布、涂布时间为12s、涂布表干温度90℃,曝光能量为120j、曝光时间为7分钟、显影时间为3分钟、显影速度为2.5m/分钟。

134.对比例1

135.一种mini led cog线路结构,包括承载基板,所述承载基板上依次设置:打底层、第一金属层、绝缘层、第一感光保护层、第二金属层、绝缘保护层和第二感光保护层。

136.所述承载基板的厚度为1.1mm,选择硼硅玻璃。

137.所述打底层的厚度为1μm,材料选择氮化硅。

138.所述第一金属层的厚度为2.5μm,材料为铜。

139.所述绝缘层的厚度为0.2μm,材料为氮化硅;

140.所述第一感光保护层的厚度为9μm,材料为半导体光刻胶;

141.所述第二金属层的厚度为2.5μm,材料为银;

142.所述绝缘保护层的厚度为0.2μm,材料氮化硅;

143.所述第二感光保护层的厚度为10μm,材料为半导体光刻胶。

144.对比例1的mini led cog线路结构的制作方法,包括以下步骤:

145.1)、对承载基板表面处理;所述工艺包括清洗和plasma电浆清洗,整体的清洗时间为8s;

146.2)、在步骤1)得到的承载基板的单面层制作打底层、第一金属层;所述打底层制备工艺采用真空磁控溅射,镀膜功率为9kw、镀膜压强为500千帕、镀膜时间为1分钟、加热温度为200℃;第一金属层制备工艺为真空磁控溅射,镀膜功率为11kw、镀膜压强为600千帕、镀膜时间为1分钟;制备第一金属层时,加热温度关闭。第一金属层进行湿法蚀刻,采用市售刻蚀液,蚀刻液为参数为时间为15分钟、温度为25℃、冲洗速度为90ml/s。

147.3)、再制备绝缘层,制备工艺为化学气相沉积法沉积,时间为110分钟、温度为450℃,后续制程为干法刻蚀,温度为45℃,压强为350千帕,时间为10分钟。

148.4)、在承载基板的绝缘层上制作第一感光保护层后曝光显影;所述第一感光保护层的制备工艺为涂布、曝光、显影,涂布方式为狭缝涂布、涂布时间为12s、涂布表干温度80℃,曝光能量为120j、曝光时间为6分钟、显影时间为2分钟、显影速度为2.5m/分钟。

149.5)、在承载基板的第一感光保护层上制作第二金属层,进行湿法刻蚀;所述第二金属层的工艺为真空磁控溅射,制备第二金属层时真空磁控溅射镀膜功率为15kw、镀膜压强为410千帕、镀膜时间为10分钟;在第二金属层时腔室加热温度关闭。再进行湿法蚀刻,蚀刻液为市售刻蚀液,刻蚀参数为时间为10分钟、温度为25℃;

150.6)、再制备绝缘层,绝缘保护层的制备工艺为化学气相沉积法,沉积时间115分钟、温度为450℃;后续制程为干法刻蚀,温度为55℃,压强为330千帕,时间为12分钟。

151.7)、最后制作第二感光保护层形成完整的集成电路结构:所述第二感光保护层的制备工艺为涂布、曝光、显影,涂布方式为狭缝涂布、涂布时间为12s、涂布表干温度80℃,曝光能量为140j、曝光时间为7分钟、显影时间为3分钟、显影速度为2.5m/分钟。第二感光保护层主要作用通过曝光、显影把正负电极露出。

152.对实施例1、2和对比例1的mini led cog线路结构进行测试,测试方法:x射线衍射法应力测定的基本原理是:当一束波长为λ的射线照射到多晶体上时,会在一定的角度上接收到反射的x射线强度极大值(即衍射峰)。其中,x射线的波长、衍射晶面间距d和衍射角2θ之间遵从布拉格定律:2dsinθ=nλ(n=1,2,3

……

)当应力引起晶格间距d发生变化时,衍射角2θ随之变化。所以要求晶面间距d的变化,只要测得衍射角2θ的变化即可。利用衍射角的变化,根据弹性力学相关方程,可求出材料某一方向的应力大小。

153.测试结果:实施例1、2的应力值测试为178.72、165.59。实施例1、2的状态是附着力无问题,对比例1的应力值测试为228.07,出现了膜层脱离附着力差的状态。

154.结果分析:正常的膜层整体应力值约200,过渡膜层在附着力上是实际测试参数为178.72、165.59,附着力是优于正常结构的。

155.显然本发明具体实现并不受上述方式的限制,只要采用了本发明的方法构思和技术方案进行的各种非实质性的改进,均在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。