1.本公开涉及半导体领域,尤其涉及半导体器件结构及形成方法。

背景技术:

2.集成芯片制造工业经常使用缩放来开发新产品(例如新的芯片)。缩放是减小集成芯片上的最小特征尺寸或使其制作得更小的工艺。通过减小集成芯片上的最小特征尺寸,可以改进集成芯片上的各个器件的性能(例如,功耗、速度等)。

技术实现要素:

3.根据本公开的第一方面,提供了一种集成芯片结构,包括:第一小芯片,所述第一小芯片占主导性地包括耦合到在第一衬底之上的第一多个互连的第一多个集成芯片器件,所述第一多个集成芯片器件是第一类型集成芯片器件;第二小芯片,所述第二小芯片占主导性地包括耦合到在第二衬底之上的第二多个互连的第二多个集成芯片器件,所述第二多个集成芯片器件是与所述第一类型集成芯片器件不同的第二类型集成芯片器件;一个或多个小芯片间连接器,所述一个或多个小芯片间连接器设置在所述第一小芯片和所述第二小芯片之间,并且被配置为电耦合所述第一小芯片和所述第二小芯片;并且其中,所述第一多个互连具有第一最小宽度,所述第一最小宽度与所述第二多个互连的第二最小宽度不同。

4.根据本公开的第二方面,提供了一种集成芯片结构,包括:第一小芯片,所述第一小芯片占主导性地包括设置在第一衬底上或之内的nmos晶体管,其中,所述nmos晶体管包括具有第一栅极长度的第一栅极结构,所述第一栅极结构设置在具有第一掺杂类型的第一源极/漏极区之间;第二小芯片,所述第二小芯片占主导性地包括设置在第二衬底上或之内的pmos晶体管,其中,所述pmos晶体管包括具有与所述第一栅极长度不同的第二栅极长度的第二栅极结构,所述第二栅极结构设置在具有与所述第一掺杂类型不同的第二掺杂类型的第二源极/漏极区之间;以及一个或多个小芯片间连接器,所述一个或多个小芯片间连接器布置在所述第一小芯片和所述第二小芯片之间,其中,所述一个或多个小芯片间连接器被配置为电耦合所述nmos晶体管和所述pmos晶体管。

5.根据本公开的第三方面,提供了一种形成集成芯片结构的方法,包括:根据第一制造工艺对第一衬底进行处理,以形成占主导性地具有第一多个器件的第一小芯片,其中,所述第一多个器件是第一类型集成芯片器件;根据第二制造工艺对第二衬底进行处理,以形成占主导性地具有第二多个器件的第二小芯片,其中,所述第二多个器件是与所述第一类型集成芯片器件不同的第二类型集成芯片器件;以及通过一个或多个层间连接器将所述第一小芯片内的第一多个器件电耦合到所述第二小芯片内的第二多个器件。

附图说明

6.当结合附图阅读时,从下面的具体实施方式中最好地理解本公开的各方面。应注意,根据工业中的标准惯例,各种特征未按比例绘制。实际上,为了讨论的清楚起见,各种特

征的尺寸可能被任意增加或减小。

7.图1示出了包括一个或多个小芯片(chiplet)的集成芯片结构的一些实施例的三维视图,这些小芯片各自占主导性地具有单一类型集成芯片器件。

8.图2示出了集成芯片结构的一些实施例的截面图,该集成芯片结构包括各自占主导性地具有单一类型集成芯片器件的多个小芯片。

9.图3示出了包括多个小芯片的集成芯片结构的一些附加实施例的截面图,这些小芯片各自占主导性地具有包括单一类型的接触蚀刻停止层应变的单一类型器件。

10.图4示出了包括多个小芯片的集成芯片结构的一些附加实施例的截面图,这些小芯片各自占主导性地具有包括单一类型的侧壁间隔件应变的单一类型器件。

11.图5示出了包括多个小芯片的集成芯片结构的一些附加实施例的截面图,这些小芯片各自占主导性地具有包括单一类型源极/漏极材料的单一类型器件。

12.图6示出了包括多个小芯片的集成芯片结构的一些附加实施例的截面图,这些小芯片各自占主导性地具有包括单一类型晶体管结构的单一类型器件。

13.图7示出了包括多个小芯片的集成芯片结构的一些附加实施例的截面图,这些小芯片各自占主导性地具有包括单一沟道方向的单一类型器件。

14.图8示出了包括多个小芯片的集成芯片结构的一些实施例的截面图,这些小芯片各自占主导性地具有单个类型的晶体管器件和一个或多个无源器件。

15.图9a-9b示出了具有与不同小芯片相关联的不同组件的功率管理电路的一些实施例。

16.图10a-10b示出了具有与不同小芯片相关联的不同组件的功率管理电路的一些替换实施例。

17.图11示出了包括多个小芯片的封装集成芯片结构的一些实施例的截面图,该封装集成芯片结构包括各自占主导性地具有单一类型集成芯片器件。

18.图12a-16c示出了形成包括多个小芯片的集成芯片结构的方法的一些实施例的截面图,这些小芯片各自占主导性地具有单一类型集成芯片器件。

19.图17示出了形成包括多个小芯片的集成芯片结构的方法的一些实施例的流程图,这些小芯片各自占主导性地具有单一类型集成芯片器件。

具体实施方式

20.下面的公开内容提供了用于实现所提供的主题的不同特征的许多不同的实施例或示例。下文描述了组件和布置的具体示例以简化本公开。当然,这些仅是示例而不意在进行限制。例如,下面的说明中,在第二特征之上或在第二特征上形成第一特征可以包括以直接接触的方式形成第一特征和第二特征的实施例,并且还可以包括可以在第一特征和第二特征之间形成附加特征使得第一特征和第二特征不直接接触的实施例。此外,本公开在各个示例中可以重复附图标记和/或字母。这种重复是为了简单和清楚的目的,并且其本身不表示所讨论的各个实施例和/或配置之间的关系。

21.此外,本文可能使用了空间相关术语(例如,“之下”、“下方”、“下”、“上方”、“上”等),以易于描述附图中所示的一个要素或特征与另外(一个或多个)要素或(一个或多个)特征的关系。这些空间相关术语意在涵盖使用中或工作中的器件处于除了附图中所示朝向

之外的不同朝向。装置可能以其他方式定向(旋转90度或处于其他朝向),并且本文使用的空间相关描述符可类似地进行相应解释。

22.数十年来,半导体工业已通过减小ic上的特征的尺寸(例如,栅极长度、互连宽度等),而使集成电路(ic)更快且更有功率效率。减小ic上的特征的尺寸通常被称为半导体缩放。在工业中,使用不同的制造工艺(例如技术节点或工艺节点)来生成包括具有不同最小特征尺寸的器件的集成芯片。例如,28纳米(nm)技术节点中的晶体管栅极长度通常小于45nm技术节点中的晶体管栅极长度。通常,较小的技术节点具有较小的晶体管,这既更快又更省电。

23.近年来,随着缩放变得更加困难,也已使用其他制造工艺(例如,使用集成芯片上的不同应变和/或材料)来增强器件性能。因为不是所有的器件类型都同等地受益于缩放和/或其他制造工艺增强,所以通常通过试图平衡制造工艺以满足多个不同器件类型(例如,nmos晶体管、pmos晶体管、无源器件等)的需要来优化ic的整体性能。然而,因为不同的器件类型通过不同的制造工艺来优化,所以所得到的ic可能具有总体次优(sub-optimal)的性能。例如,在单个芯片上形成nmos晶体管及pmos晶体管的制造工艺可以优化一种类型的器件(例如,nmos晶体管)的操作,而不优化另一类型的器件(例如,pmos晶体管)的性能。因此,这种制造工艺平衡牺牲了集成芯片内的一种或多种器件类型的最优性能。

24.在一些实施例中,本公开涉及被配置为优化集成芯片结构内的不同器件类型的性能的集成芯片结构。集成芯片结构包括通过不同制造工艺形成的多个小芯片。多个小芯片通过一个或多个小芯片间互连耦合在一起。多个小芯片中的相应小芯片占主导性地包括单一类型器件,该单一类型器件与其余小芯片的单一类型器件不同。例如,集成芯片结构可以包括第一小芯片和第二小芯片,第一小芯片占主导性地包括通过第一制造工艺(例如,65nm技术节点工艺)形成的pmos晶体管,第二小芯片占主导性地包括通过第二制造工艺(例如,45nm技术节点工艺)形成的nmos晶体管。通过使用不同制造工艺形成不同类型的器件,能够分别使用优化每种类型的器件的性能的制造工艺来形成不同类型的器件,从而减轻不同器件类型之间的制造工艺平衡的负面影响(例如,使集成芯片性能劣化)。

25.图1示出了集成芯片结构100的一些实施例的三维视图,集成芯片结构100包括多个小芯片,这些小芯片各自占主导性地具有单一类型集成芯片器件。

26.集成芯片结构100包括多个小芯片102-108。在一些实施例中,多个小芯片102-108可以包括第一小芯片102、第二小芯片104、第三小芯片106和第四小芯片108。多个小芯片102-108中的一个或多个占主导性地包括单一类型集成芯片器件(例如,包括多于80%的单一类型集成芯片器件;包括多于90%的单一类型集成芯片器件;包括多于95%的单一类型集成芯片器件;包括多于99%的单一类型集成芯片器件;包括约100%的单一类型集成芯片器件;仅包括单一类型集成芯片器件)。在一些实施例中,单一类型集成芯片器件可以是单一类型晶体管器件。在其他实施例中,单一类型集成芯片器件可以是无源器件(例如,电容器、电阻器、或电感器等)或栅极驱动器电路等。

27.例如,在一些实施例中,第一小芯片102可以占主导性地包括作为第一类型集成芯片器件(例如nmos晶体管)的第一多个集成芯片器件,并且第二小芯片104可以占主导性地包括作为第二类型集成芯片器件(例如pmos晶体管)的第二多个集成芯片器件。在一些实施例中,第一小芯片102可以占主导性地包括第一类型集成芯片器件,并且没有第二类型的器

件。在一些实施例中,第一小芯片102可以仅包括第一类型集成芯片器件。

28.在一些实施例中,多个小芯片102-108可以分别包括单一类型集成芯片器件,其中在多个小芯片102-108的每一个上的单一类型集成芯片器件是通过不同的制造工艺形成的。例如,在一些实施例中,第一小芯片102可以占主导性地包括由第一制造工艺(其优化nmos器件的性能)形成的nmos器件,第二小芯片104可以占主导性地包括由第二制造工艺(其优化pmos器件的性能)形成的pmos器件,第三小芯片106可以占主导性地包括由第三制造工艺(其优化无源器件性能)形成的无源器件(例如电感器、电容器、或电阻器等),并且第四小芯片108可以占主导性地包括限定由第四制造工艺(其优化一个或多个栅极驱动器电路的性能)形成的一个或多个栅极驱动器电路的晶体管器件。在一些实施例中,不同的制造工艺可以是不同的技术节点工艺。例如,在一些实施例中,第一制造工艺可以包括第一技术节点工艺(例如,7nm技术节点工艺),第二制造工艺可以包括第二技术节点工艺(例如,14nm技术节点工艺),第三制造工艺可以包括第三技术节点工艺(例如,65nm技术节点工艺),并且第四制造工艺可以包括第四技术节点工艺(例如,45nm技术节点工艺)。在一些替代实施例中,第一技术节点工艺可以与第二技术节点工艺相同。在一些替代实施例中,第三技术节点工艺可以与第四技术节点工艺相同。在另外的实施例中,不同的制造工艺可以为多个小芯片102-108中的每一个内的ic器件提供不同的材料、不同的应变或不同的沟道方向等。

29.多个小芯片102-108内的不同类型的集成芯片器件通过一个或多个小芯片间连接器110耦合在一起。一个或多个小芯片间连接器110被配置为允许不同类型的集成芯片器件一起操作以执行功能。在一些实施例中,一个或多个小芯片间连接器110可以包括以下项中的一个或多个:再分布层(rdl)、铜柱、导电凸块(例如微凸块)、焊料接头、铜到铜接头、铜到铝铜接头、铝铜到铝铜接头、或穿衬底过孔(through-substrate-via,tsv)接头等。在一些实施例中,多个小芯片102-108可以以多维芯片结构(例如,三维集成芯片(3d ic)结构)彼此堆叠。例如,在一些实施例中,第二小芯片104、第三小芯片106和第四小芯片108可以堆叠到第一小芯片102的上表面上。在这样的实施例中,第一小芯片102可以具有比第二小芯片104、第三小芯片106和第四小芯片108更大的面积。

30.通过使多个小芯片102-108分别且占主导性地包括单一类型集成芯片器件,可以使用优化每种类型的集成芯片器件的性能的制造工艺来形成不同类型的集成芯片器件。通过使用优化每一类型的集成芯片器件的性能的制造工艺来形成不同类型的集成芯片器件,能够避免由于制造工艺平衡而导致的器件劣化并且能够改进集成芯片结构的整体性能。

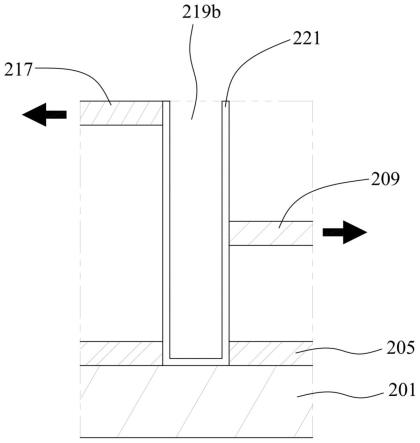

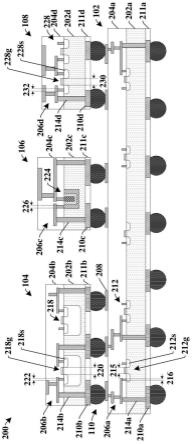

31.图2示出了包括多个小芯片的集成芯片结构200的一些附加实施例的截面图,这些小芯片各自占主导性地具有单一类型集成芯片器件。

32.集成芯片结构200包括通过小芯片间连接器110彼此耦合的多个小芯片102-108。在一些实施例中,多个小芯片102-108可以包括第一小芯片102、第二小芯片104、第三小芯片106和第四小芯片108。多个小芯片102-108分别占主导性地包括不同类型的集成芯片器件。

33.例如,在一些实施例中,第一小芯片102可以占主导性地包括作为第一类型的晶体管器件的第一多个晶体管器件212。在一些附加实施例中,第一小芯片102可以仅包括第一类型的晶体管器件。第一多个晶体管器件212分别包括设置在第一源极/漏极区212s之间的第一栅极结构212g。在一些实施例中,第一类型的晶体管器件是nmos晶体管,使得第一多个

晶体管器件212是nmos晶体管。在这样的实施例中,第一源极/漏极区212s可以包括第一掺杂类型(例如,n型掺杂),而在第一栅极结构212g之下并且在第一源极/漏极区212s之间延伸的沟道区可以包括第二掺杂类型(例如,p型掺杂)。在一些实施例中,第一栅极结构212g可以具有第一栅极长度215。

34.在一些实施例中,第一小芯片102还可以包括第一多个互连206a,第一多个互连206a设置在第一衬底202a之上的第一层间电介质(ild)结构204a内。在一些实施例中,第一多个互连206a可以包括导电接触件、互连线、和/或互连过孔。在一些实施例中,第一多个互连206a可以包括第一导电接触件,该第一导电接触件设置在第一多个晶体管器件212之一上并具有第一接触件宽度216。在一些实施例中,第一多个互连206a可以耦合到设置在第一ild结构204a之上的一个或多个前侧键合结构208。在各种实施例中,一个或多个前侧接合结构208可以包括再分布层、接合衬垫、或凸块下冶金(ubm)结构等。在一些附加实施例中,第一多个互连206a还可以通过第一穿衬底过孔(tsv)214a耦合到一个或多个第一背侧键合结构210a。一个或多个第一背侧键合结构210a与第一ild结构204a被第一衬底202a隔开。在各种实施例中,第一背侧键合结构210a可以包括再分布层、键合衬垫、或ubm结构等。在一些实施例中,一个或多个第一背侧键合结构210a可以设置在第一钝化结构211a上或之内,该第一钝化结构211a设置在第一衬底202a上。

35.在一些实施例中,第二小芯片104可以包括第二多个晶体管器件218,第二多个晶体管器件218是不同于第一类型晶体管器件的第二类型晶体管器件。在一些附加实施例中,第二小芯片104可以仅包括第二类型晶体管器件。第二多个晶体管器件218各自包括第二栅极结构218g,第二栅极结构218g设置在第二衬底202b内的第二源极/漏极区218s之间。在一些实施例中,第二类型晶体管器件是pmos晶体管,因此第二多个晶体管器件218是pmos晶体管。在这样的实施例中,第二源极/漏极区218s可以包括第二掺杂类型(例如,p型掺杂),而在第二栅极结构218g之下并且在第二源极/漏极区218s之间延伸的沟道区可以包括第一掺杂类型(例如,n型掺杂)。在一些实施例中,第二栅极结构218g可以包括不同于(例如大于)第一栅极长度215的第二栅极长度220。在一些实施例中,第二多个互连206b设置在第二衬底202b之上的第二ild结构204b内。在一些实施例中,第二多个互连206b可以包括设置在第二多个晶体管器件218之一上并具有第二接触件宽度222的导电接触件。在一些实施例中,第一多个互连206a具有第一最小宽度(例如第一接触件宽度216),该第一最小宽度与第二多个互连206b的第二最小宽度(例如第二接触件宽度222)不同。例如,在一些实施例中,第二接触件宽度222大于第一接触件宽度216。在一些实施例中,第二多个互连206b可以通过第二tsv 214b耦合到一个或多个第二背侧键合结构210b,这些第二背侧键合结构210b设置在第二衬底202b的背侧上的第二钝化结构211b上和/或内。

36.在一些实施例中,第三小芯片106可以占主导性地包括在第三衬底202c上和/或之内的无源器件224(例如,电容器、电感器、或电阻器等)。在一些实施例中,第三小芯片106可以没有晶体管器件。例如,第三小芯片106可以没有nmos晶体管器件和pmos晶体管器件。在一些附加实施例中,第三小芯片106可以仅包括无源器件224。在一些实施例中,无源器件224可以包括具有第一电极的电容器,该第一电极与第二电极被电容器电介质结构隔开。在其他实施例中,无源器件224可以包括电感器。在其他实施例中,无源器件224可以包括电阻器。在一些实施例中,第三多个互连206c设置在第三衬底202c之上的第三ild结构204c内。

第三多个互连件206c可以包括导电接触件,该导电接触件设置在无源器件224之一上并且具有第三接触件宽度226,该第三接触件宽度226不同于(例如大于)第一接触件宽度216和/或第二接触件宽度222。在一些实施例中,第三多个互连206c可以耦合到一个或多个第三背侧键合结构210c,这些第三背侧键合结构210c位于设置在第三衬底202c的背侧上的第三钝化结构211c上和/或之内。

37.在一些实施例中,第四小芯片108可以占主导性地包括限定一个或多个栅极驱动器电路的第三多个晶体管器件228。在一些附加实施例中,第四小芯片108可以仅包括限定一个或多个栅极驱动器电路的晶体管器件。在一些实施例中,第三多个晶体管器件228可以包括第三栅极结构228g,第三栅极结构228g在第四衬底202d内的第三源极/漏极区228s之间。在一些实施例中,第三栅极结构228g可以包括第三栅极长度230,该第三栅极长度230不同于(例如大于)第一栅极长度214和/或第二栅极长度220。在一些实施例中,第四多个互连206d设置在第四衬底202d之上的第四ild结构204d内。在一些实施例中,第四多个互连206d可以耦合到一个或多个第四背侧键合结构210d,这些第四背侧键合结构210d位于设置在第四衬底202d的背侧上的第四钝化结构211d上和/或之内。第四多个互连206d可以包括导电接触件,该导电接触件设置在第三多个晶体管器件228之一上并具有第四接触件宽度232,该第四接触件宽度232不同于(例如大于)第一接触件宽度216、第二接触件宽度222和/或第三接触件宽度226。

38.虽然图2示出了包括不同小芯片的集成芯片结构200,这些小芯片分别占主导性地具有不同类型的集成芯片器件(例如,nmos器件、pmos器件等),但是应当理解,在附加实施例中,各个小芯片内的不同类型的集成芯片器件可以占主导性地具有其他特征和/或附加特征。例如,同一小芯片内的不同集成芯片器件可以占主导性地具有相同的应变、栅极取向、和/或材料等。图3-7示出了包括多个小芯片的集成芯片结构的一些附加实施例的截面图,这些小芯片各自占主导性地具有包含相同特征的单一类型集成芯片器件。

39.图3示出了包括多个小芯片的集成芯片结构300的一些实施例的截面图,这些小芯片各自占主导性地具有包含单一类型接触蚀刻停止层应变的单一类型器件。

40.集成芯片结构300包括多个小芯片102-108。在一些实施例中,多个小芯片102-108可以包括第一小芯片102、第二小芯片104、第三小芯片106和第四小芯片108。在一些实施例中,第一小芯片102可以占主导性地包括第一多个晶体管器件212(例如nmos晶体管),第二小芯片104可以占主导性地包括第二多个晶体管器件218(例如pmos晶体管),第三小芯片106可以占主导性地包括一个或多个无源器件224,并且第四小芯片108可以占主导性地包括被配置为作为一个或多个栅极驱动器电路进行操作的第三多个晶体管器件228。

41.第一多个晶体管器件212可以包括设置在第一衬底202a内的第一阱区302a之上的第一栅极结构212g。在一些实施例中,第一阱区302a可以设置在一个或多个第一隔离结构304a之间,这些第一隔离结构304a各自包括设置在第一衬底202a中的沟槽内的一个或多个电介质材料。第一栅极结构212g设置在第一衬底202a之上并且在第一源极/漏极区212s之间。一个或多个第一侧壁间隔件306a沿着第一栅极结构212g的相反侧布置。第一接触蚀刻停止层(cesl)308a设置在第一衬底202a之上并且沿着第一栅极结构212g的侧面。第一多个互连206a设置在第一cesl 308a之上的第一ild结构204a内。在一些实施例中,第一cesl 308a包括第一类型应变。在一些实施例中,第一类型应变可以是拉伸应变。

42.第二小芯片104可以是设置在第二阱区302b之上的第二栅极结构218g,该第二阱区302b设置在第二衬底202b内。第二栅极结构218g设置在第二衬底202b之上并且在第二源极/漏极区218s之间。一个或多个第二侧壁间隔件306b沿着第二栅极结构218g的相反侧布置。第二cesl 308b设置在第二衬底202b之上并且沿着第二栅极结构218g的侧面。第二多个互连206b设置在第二衬底202b之上的第二ild结构204b内。在一些实施例中,第二cesl 308b包括与第一类型应变不同的第二类型应变。在一些实施例中,第二类型应变可以包括压缩应变。

43.虽然nmos晶体管和pmos晶体管通常通过针对nmos晶体管和pmos晶体管使用同一cesl的制造工艺来形成,但是应当理解,应变cesl对不同类型的晶体管的影响不同。例如,具有拉伸应变的cesl可以增强nmos晶体管性能,而具有压缩应变的cesl可以增强pmos晶体管性能。因此,通过在第一多个晶体管器件212之上形成第一cesl308a并且在第二多个晶体管器件218之上形成第二cesl 308b,能够针对同一集成芯片结构内的nmos晶体管和pmos晶体管两者优化器件性能。

44.图4示出了包括多个小芯片的集成芯片结构400的一些实施例的截面图,多个小芯片各自占主导性地具有包括单一类型侧壁间隔件应变的单一类型器件。

45.集成芯片结构400包括多个小芯片102-108。在一些实施例中,多个小芯片102-108可以包括第一小芯片102和第二小芯片104,第一小芯片102占主导性地包括第一多个晶体管器件212,第二小芯片104占主导性地包括第二多个晶体管器件218。

46.第一多个晶体管器件212可以包括设置在第一衬底202a上的第一栅极结构212g。一个或多个第一侧壁间隔件306a沿着第一栅极结构212g的相反侧布置。在一些实施例中,一个或多个第一侧壁间隔件306a包括第一类型应变。在一些实施例中,第一类型应变可以包括拉伸应变。第二多个晶体管器件218可以包括设置在第二衬底202b上的第二栅极结构218g。一个或多个第二侧壁间隔件306b沿着第二栅极结构218g的相反侧布置。在一些实施例中,一个或多个第二侧壁间隔件306b包括与第一类型应变不同的第二类型应变。在一些实施例中,第二类型应变可以包括压缩应变。

47.虽然nmos晶体管和pmos通常通过针对nmos晶体管和pmos使用同一侧壁间隔件应变的制造工艺来形成,但是已经认识到,应变侧壁间隔件对不同类型的晶体管的影响不同。例如,具有拉伸应变的侧壁间隔件可以增强nmos晶体管性能,而具有压缩应变的侧壁间隔件可以增强pmos晶体管性能。因此,通过在第一多个晶体管器件212周围形成一个或多个第一侧壁间隔件306a和在第二多个晶体管器件218周围形成一个或多个第二侧壁间隔件306b,能够在同一集成芯片结构内针对nmos晶体管和pmos晶体管两者优化器件性能。

48.图5示出了包括多个小芯片的集成芯片结构500的一些实施例的截面图,这些小芯片各自占主导性地具有包括单一类型源极/漏极应变的单一类型器件。

49.集成芯片结构500包括多个小芯片102-108。在一些实施例中,多个小芯片102-108可以包括第一小芯片102和第二小芯片104,第一小芯片102占主导性地包括第一多个晶体管器件212,第二小芯片104占主导性地包括第二多个晶体管器件218。

50.第一多个晶体管器件212可以包括第一栅极结构212g,该第一栅极结构212g设置在第一衬底202a之上并且在第一源极/漏极区212s之间。在一些实施例中,第一源极/漏极区212s可以包括第一类型半导体材料。例如,第一源极/漏极区212s可以包括碳化硅。第二

多个晶体管器件218可以包括第二栅极结构218g,该第二栅极结构218g设置在第二衬底202b之上并且在第二源极/漏极区218s之间。在一些实施例中,第二源极/漏极区218s可以包括与第一类型半导体材料不同的第二类型半导体材料。例如,第二源极/漏极区218s可以包括硅锗。

51.图6示出了包括多个小芯片的集成芯片结构600的一些实施例的截面图,这些小芯片各自占主导性地具有包括单一类型晶体管结构的单一类型器件。

52.集成芯片结构600包括多个小芯片102-108。在一些实施例中,多个小芯片102-108可以包括第一小芯片102和第二小芯片104,第一小芯片102占主导性地包括第一多个晶体管器件212,第二小芯片104占主导性地包括第二多个晶体管器件218。

53.第一多个晶体管器件212可以具有第一晶体管结构。在一些实施例中,第一晶体管结构可以包括finfet结构。在这样的实施例中,第一衬底202a包括半导体材料的一个或多个鳍202f,这些鳍202f从第一衬底202a的上表面向外延伸。沿半导体材料的一个或多个鳍202f的相反侧布置隔离结构602。第一栅极结构212g包绕半导体材料的一个或多个鳍。源极/漏极区(未示出)设置在半导体材料的鳍202f的相反侧,使得多个finfet器件的沟道区延伸到页面内或页面外。在其他实施例中,第一类型晶体管结构可以包括栅极全环绕(gaa)晶体管结构、纳米片晶体管结构、或平面fet结构等。

54.第二多个晶体管器件218可以具有与第一晶体管结构不同的第二晶体管结构。在一些实施例中,第二晶体管结构可以包括平面fet结构。在这样的实施例中,多个平面晶体管器件各自包括第二栅极结构218g,该第二栅极结构218g设置在第二衬底202b的上表面之上并且在第二衬底202b的上表面内的第二源极/漏极区218s之间。在其他实施例中,第二类型晶体管结构可以包括finfet晶体管结构、栅极全环绕(gaa)晶体管结构、或纳米片晶体管结构等。

55.图7示出了包括多个小芯片的集成芯片结构700的一些实施例的截面图,这些小芯片各自占主导性地具有包括单一沟道方向的单一类型器件。

56.集成芯片结构700包括多个小芯片102-108。在一些实施例中,多个小芯片102-108可以包括小芯片102和第二小芯片104,第一小芯片102占主导性地包括第一多个晶体管器件212,第二小芯片104占主导性地包括第二多个晶体管器件218。

57.第一多个晶体管器件212可以包括设置在第一衬底202a之上的第一栅极结构212g。第一栅极结构212g位于第一源极/漏极区212s之间。第一沟道区212c设置在第一栅极结构212g下方并且在第一源极/漏极区212s之间。在一些实施例中,第一衬底202a的上表面可以面向第一方向702(即,垂直于第一衬底202a的上表面的线可以在第一方向702上延伸),并且第一沟道区212c可以沿第二方向704延伸。例如,在一些实施例中,第一方向702可以是[100]方向(例如,垂直于(100)晶面的方向),并且第二方向704可以沿着(110)晶面。

[0058]

第二多个晶体管器件218可以包括设置在第二衬底202b之上的第二栅极结构218g。第二栅极结构218g位于第二源极/漏极区218s之间。第二沟道区218c设置在第二栅极结构218g下方并且在第二源极/漏极区218s之间。在一些实施例中,第二衬底202b的上表面可以面向第三方向706(即,垂直于第二衬底202b的上表面的线可以在第三方向706上延伸),并且第二沟道区218c可以沿第四方向708延伸。例如,在一些实施例中,第三方向706可以是[110]方向(例如,垂直于(110)晶面的方向),并且第四方向708可以沿着(110)晶面。

[0059]

通常,nmos器件和pmos器件制作在同一晶圆上。然而,已认识到,nmos器件和pmos器件的多数电荷载流子不同,并且不同的多数电荷载流子在不同方向上具有不同的迁移率。例如,电子在{100}族晶面中具有最大的迁移率,而空穴在{110}族晶面中具有最大的迁移率。因此,通过将第一多个晶体管器件212形成为具有沿第一晶面(例如,沿(100)晶面)的第一沟道区212c,以及将第二多个晶体管器件218形成为具有沿第二晶面(例如,沿(110)晶面)的第二沟道区218c,能够针对nmos晶体管和pmos晶体管两者来优化晶体管器件性能。

[0060]

图8示出了具有一个或多个小芯片的集成芯片结构800的替代实施例,这些小芯片占主导性地包括单一类型晶体管器件。

[0061]

集成芯片结构800包括第一小芯片102、第二小芯片104和第三小芯片106。第一小芯片102包括第一多个晶体管器件212(其占主导性地是nmos器件)。第二小芯片104包括第二多个晶体管器件218(其占主导性地是pmos器件)。第三小芯片106包括第三多个晶体管器件228(其占主导性地限定一个或多个栅极驱动器电路)。

[0062]

在一些实施例中,第一小芯片102、第二小芯片104和第三小芯片106中的一个或多个还可以包括一个或多个无源器件。例如,在一些实施例中,第一小芯片102可以占主导性地包括第一多个晶体管器件212和一个或多个第一无源器件224a(例如,一个或多个电容器、电感器等)。在一些附加实施例中,第二小芯片104可以占主导性地包括第二多个晶体管器件218和一个或多个第二无源器件224b(例如,一个或多个电感器、电容器等)。在一些附加实施例中,第三小芯片106可以占主导性地包括第三多个晶体管器件228和一个或多个第三无源器件224c(例如,一个或多个电阻器、电感器等)。由于无源器件可以不受一些制造工艺增强(例如不同的应变和/或材料)的影响,所以无源器件可以能够集成到具有单一类型晶体管器件的小芯片中,而不会对无源器件的性能产生大的影响。

[0063]

图9a示出了功率管理电路900的示例性示意图的一些实施例,功率管理电路900具有与不同小芯片相关联的不同组件。

[0064]

功率管理电路900包括具有栅极驱动器电路902的降压转换器,栅极驱动器电路902耦合到高侧驱动器904的第一栅极g1和低侧驱动器906的第二栅极g2。在一些实施例中,高侧驱动器904包括具有耦合到输入电压(v

in

)的第一源极s1的pmos晶体管,且低侧驱动器906可以包括具有耦合到接地(gnd)的第二源极s2的nmos晶体管。高侧驱动器904的第一漏极d1还在共享节点处耦合到低侧驱动器906的第二漏极d2。该共享节点还耦合到被配置被输出输出电压(v

out

)的谐振电路。谐振电路包括电感器908和电容器910。在操作期间,栅极驱动器电路902被配置为切换高侧驱动器904和低侧驱动器906。谐振电路被配置为存储能量然后耗散能量以生成输出电压(v

out

),该输出电压(v

out

)具有相对于输入电压(v

in

)减小的电压值,从而用作dc-dc转换器。

[0065]

在一些实施例中,栅极驱动器电路902可以设置在第四小芯片108上,高侧驱动器904可以设置在第二小芯片104上,低侧驱动器906可以设置在第一小芯片102上,并且谐振电路可以设置在第三小芯片106上。图9b示出了包括小芯片的集成芯片结构的一些实施例的截面图912,这些小芯片各自包括图9a的降压转换器电路的组件。

[0066]

降压转换器通常使用同一工艺和相同材料形成在单个衬底上。然而,通过在不同的小芯片上形成每个降压转换器电路组件,可以通过优化每个转换器组件内的器件来改进降压转换器电路的性能。例如,在一些实施例中,降压转换器电路可以被设置在智能电话的

功率管理集成电路(pmic)内,并且被配置为从电池接收输入电压v

in

(具有在约3.7v(伏特)与约5v之间的范围内的值),并且将输出电压(v

out

)(具有在约3.7v与约5v之间的范围内的值)输出到应用处理器(ap)。在一些这样的实施例中,降压转换器电路可以被配置为在约100khz(千赫)和约10mhz(兆赫)之间的频率下操作,并且输出在约0.5a(安培)与约3a之间的范围内的电流。

[0067]

在其他实施例中,降压转换器电路可以设置在服务器的pmic内,并且被配置为从主板接收输入电压v

in

(具有在约5v与约12v之间的范围内的值),并且将输出电压(v

out

)(具有在约0.6v与约1.2v之间的范围内的值)输出到中央处理单元(cpu)。在一些这样的实施例中,降压转换器电路可以被配置为在约100khz与约10mhz之间的频率下操作,并且输出在约20a与约100a之间的范围内的电流。

[0068]

在又一些实施例中,降压转换器电路可以设置在智能电话无线充电系统内,并且被配置成从无线充电板接收端接收输入电压v

in

(具有在约12v与约20v之间的范围内的值),并且将输出电压(v

out

)(具有在约3.7v与约5v之间的范围内的值)输出到电池。在一些这样的实施例中,降压转换器电路可以被配置为在约205khz或约6.78mhz之间的频率下操作,并且输出在约0.5a与约3a之间的范围内的电流。

[0069]

在其他实施例中,其他类型的电路也可以由设置在不同小芯片上的组件形成。例如,在一些附加实施例中,功率管理电路可以包括具有设置在不同小芯片上的组件的升压转换器电路。通过将升压转换器的组件设置在不同的小芯片上,升压转换器能够实现良好的性能。例如,在一些实施例中,所公开的升压转换器电路可以设置在智能电话的pmic内,并且被配置为从电池接收输入电压v

in

(具有在约3.7v(伏特)与约5v之间的范围内的值),并且将输出电压(v

out

)(具有在约6v与约32v之间的范围内的值)输出到显示电路。在一些这样的实施例中,升压转换器可以被配置为在约10khz与约100khz之间的频率下操作。

[0070]

图10a示出了功率管理电路1000的示例性示意图的一些替代实施例,功率管理电路1000具有与不同小芯片相关联的不同组件。

[0071]

功率管理电路1000包括降压转换器,该降压转换器包括栅极驱动器电路902,该栅极驱动器电路902耦合到高侧驱动器904的第一栅极g1和低侧驱动器906的第二栅极g2。谐振电路耦合到高侧驱动器904的第一漏极d1和低侧驱动器906的第二漏极d2。谐振电路包括电感器908和电容器910。

[0072]

在一些实施例中,栅极驱动器电路902可以设置在第四小芯片108上,高侧驱动器904可以设置在第二小芯片104上,低侧驱动器906可以设置在第一小芯片102上,并且电感器908和电容器910可以设置在第一小芯片102、第二小芯片104和第三小芯片106之一上。例如,图10b示出了集成芯片结构的一些实施例的截面图1002,该集成芯片结构包括具有高侧驱动器904的nmos晶体管和谐振电路的电感器908的第一小芯片、具有低侧驱动器的pmos晶体管和谐振电路的电容器910的第二小芯片、以及具有栅极驱动器电路902的第三小芯片106。

[0073]

应了解,所公开的集成芯片结构可以以多种封装类型来封装。图11示出了集成芯片结构1100的一些实施例的截面图,该集成芯片结构1100包括以cowos(衬底上晶圆上芯片)封装来封装的多个小芯片。

[0074]

封装的集成芯片结构1100包括设置在承载衬底1102(例如,内插器衬底)之上的多

个小芯片102-108。多个小芯片102-108各自占主导性地具有单一类型集成芯片器件。在一些实施例中,模制化合物1104也设置在承载衬底1102之上并围绕多个小芯片102-108。

[0075]

多个小芯片102-108通过多个微凸块1108电耦合到承载衬底1102。多个穿衬底过孔(tsv)1110延伸穿过承载衬底1102并且将多个微凸块1108电耦合到多个焊料凸块1114。在一些实施例中,可以沿承载衬底1102的顶部和/或底部布置一个或多个再分布层1112a和/或1112b,以提供tsv 1110与多个微凸块1108和/或多个焊料凸块1114之间的横向布线。

[0076]

图12a-16c示出了形成集成芯片结构的方法的一些实施例的截面图1200-1604,该集成芯片结构包括各自占主导性地具有单一类型集成芯片器件的多个小芯片。虽然关于方法描述了图12a-16c,但是应当理解,图12a-16c中公开的结构不限于这种方法,而是可以独立为独立于该方法的结构。

[0077]

如图12a的截面图1200所示,提供了第一衬底202a。在各种实施例中,第一衬底202a可以是任何类型的半导体主体(例如,硅、sige、soi等),例如半导体晶圆和/或晶圆上的一个或多个管芯,以及任何其他类型的半导体和/或与之相关联的外延层。

[0078]

如图12b的截面图1202所示,第一多个晶体管器件212形成在第一衬底202a内。第一衬底202a内的大部分器件是第一多个晶体管器件212。在一些实施例中,可以通过在第一衬底202a之上形成第一栅极结构212g来分别形成第一多个晶体管器件212。在一些实施例中,可以通过在第一衬底202a之上沉积第一栅极电介质膜和第一栅极电极膜来形成第一栅极结构212g。随后图案化第一栅极电介质膜和第一栅极电极膜以形成第一栅极电介质212d和第一栅极电极212e。在一些实施例中,第一栅极结构212g可以形成为具有第一栅极长度214。沿着第一栅极结构212g的相反侧形成第一源极/漏极区212s。在一些实施例中,可以沿着第一栅极结构212g的相反侧形成一个或多个第一侧壁间隔件306a。在一些实施例中,一个或多个第一侧壁间隔件306a可以形成为具有第一类型应变(例如拉伸应变)。

[0079]

在一些实施例中,第一多个晶体管器件212可以包括nmos晶体管。在一些这样的实施例中,可以在第一衬底202a之上形成第一栅极结构212g之前将第一阱区302a植入到第一衬底202a中。在一些实施例中,可以通过将具有第二掺杂类型(例如p型)的掺杂剂(例如,硼、铝等)植入到第一衬底202a中的第一植入工艺来形成第一阱区302a。在一些实施例中,可以随后执行第二注入工艺以将具有第一掺杂类型(例如n型)的掺杂剂(例如,磷、砷、锑等)注入到第一阱区302a中。在一些替代实施例中,第一多个晶体管器件212可以包括具有形成在第一衬底202a内的第一半导体材料的外延源极/漏极区。在一些实施例中,第一半导体材料可以包括碳化硅。

[0080]

如图12c的截面图1204所示,第一cesl 308a形成在第一衬底202a上和第一多个晶体管器件212之上。第一cesl 308a可以包括氮化物(例如氮化硅)或碳化物(例如碳化硅)等。在一些实施例中,第一cesl308a可以具有第一类型应变(例如拉伸应变)。第一多个互连206a可以形成在第一ild结构204a内,第一ild结构204a形成在第一cesl 308a上。在一些实施例中,第一多个互连206a可以各自使用镶嵌工艺(例如,单镶嵌工艺或双镶嵌工艺)来形成。通过在第一衬底202a上形成ild层,蚀刻ild层以形成过孔空穴和/或沟槽,以及用导电材料填充过孔空穴和/或沟槽,来执行镶嵌工艺。在一些实施例中,可以通过沉积工艺(例如,物理气相沉积(pvd)工艺、化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pe-cvd)工艺、原子层沉积(ald)工艺等)来沉积ild层,并且可以使用沉积工艺和/或电镀工艺

(例如,电电镀、无电电镀等)来形成导电材料(例如,钨、铜、铝等)。

[0081]

如图12d的截面图1206所示,第一衬底202a可以被减薄以减小第一衬底202a的厚度。在各种实施例中,可以通过蚀刻和/或机械磨削第一衬底202a的背侧来减薄第一衬底202a,以将第一衬底202a的厚度从第一厚度t1减小到第二厚度t2。在一些实施例中,第一厚度t1可以在约700μm与约800μm之间的范围内。在一些实施例中,第二厚度t2可以在约20μm与约80μm之间的范围内。

[0082]

如图12e的截面图1208所示,第一tsv 214a形成为延伸穿过第一衬底202a。在一些实施例中,可以通过执行第一蚀刻工艺以图案化第一衬底202a并形成延伸穿过第一衬底202a且界定第一tsv开口的第一衬底202a的侧壁,来形成第一tsv 214a。在一些实施例中,第一tsv开口延伸穿过第一cesl 308a和第一ild结构204a,以暴露第一多个互连件206a之一。在tsv开口内形成导电材料。导电材料可以通过沉积工艺和/或电镀工艺(例如电电镀、无电电镀等)形成。在各种实施例中,导电材料可以包括铜或铝等。在tsv开口内形成导电材料之后,可以执行平坦化工艺以去除过量的导电材料并且限定延伸穿过第一衬底202a的第一tsv 214a。

[0083]

沿着第一衬底202a的背侧形成第一背侧键合结构210a。可以在沿着第一衬底202a的背侧形成的第一钝化结构211a上和/或之内形成第一背侧接合结构210a。

[0084]

如图12f的截面图1210所示,第一衬底202a被分割(singulate)以形成多个第一小芯片102a-102b。在一些实施例中,第一衬底202a可以通过将第一衬底202a安装到一片切割胶带(dicing tape)1212的粘性表面上的切割工艺来分割。然后,晶圆锯沿着划片线1214切割第一衬底202a,以将第一衬底202a分离成多个第一小芯片102-102b。

[0085]

如图13a的截面图1300所示,提供了第二衬底202b。在各种实施例中,第二衬底202b可以是任何类型的半导体主体(例如,硅、sige、soi等),例如半导体晶圆和/或晶圆上的一个或多个管芯,以及任何其他类型的半导体和/或与之相关联的外延层。

[0086]

如图13b的截面图1302所示,在第二衬底202b内形成第二多个晶体管器件218。第二多个晶体管器件218可以包括第二衬底202b内的大部分器件。在一些实施例中,可以通过在第二衬底202b之上形成第二栅极结构218g来分别形成第二多个晶体管器件218。在一些实施例中,可以通过在第二衬底202b之上沉积第二栅极电介质膜和第二栅极电极膜,来形成第二栅极结构218g。随后图案化第二栅极电介质膜和第二栅极电极膜以形成第二栅极电介质218d和第二栅极电极218e。在一些实施例中,第二栅极结构218g可以形成为具有不同于(例如大于)第一栅极长度214的第二栅极长度220。第二源极/漏极区218s沿着第二栅极结构218g的相反侧形成。在一些实施例中,第二源极/漏极区218s可以包括具有形成在第二衬底202b内的第二半导体材料的外延源极/漏极区。在一些实施例中,第二半导体材料可以包括硅锗。在一些实施例中,可以沿着第二栅极结构218g的相反侧形成一个或多个第二侧壁间隔件306b。在一些实施例中,一个或多个第二侧壁间隔件306b可以形成为具有与一个或多个第一侧壁间隔件(图12b的306a)的第一类型应变不同的第二类型应变(例如压缩应变)。

[0087]

在一些实施例中,第一多个晶体管器件212可以包括pmos晶体管。在一些这样的实施例中,在第二衬底202b之上形成第二栅极结构218g之前,可以将第二阱区302b植入到一个或多个第二隔离结构304b之间的第二衬底202b中。在一些实施例中,第二阱区302b可以

通过第一注入工艺形成,该第一注入工艺将具有第一掺杂类型(例如n型)的掺杂剂(例如,磷、砷、锑等)注入到第二衬底202b中。在一些实施例中,可以随后执行第二注入工艺,以将具有第二掺杂类型(例如p型)的掺杂剂(例如,硼、铝等)注入到第二阱区302b中。在一些替代实施例中,第二多个晶体管器件218可以包括具有形成在第二衬底202b内的第二半导体材料的外延源极/漏极区。在一些实施例中,第二半导体材料可以包括硅锗。

[0088]

已认识到,在第一衬底(例如,图12b的202a)上形成nmos器件并且在第二衬底202b上形成pmos器件可以改进nmos器件和pmos器件的功率消耗及/或性能。此外,由于用于形成nmos器件和pmos器件的制造工艺可以是流水线化(streamlined),因此也可以改进制造工艺的成本和循环时间。例如,在同一衬底上形成nmos器件和pmos器件可能需要使用比在单独的衬底上形成nmos器件和pmos器件更多的掩模。

[0089]

如图13c的截面图1304所示,第二cesl 308b形成在第二衬底202b上和第二多个晶体管器件218之上。第二接触蚀刻停止层308b可以包括氮化物(例如氮化硅)或碳化物(例如碳化硅)等。在一些实施例中,第二cesl 308b可以具有与第一cesl(图12c的308a)的第一类型应变不同的第二类型应变(例如压缩应变)。第二多个互连206b可以形成在第二ild结构204b内,第二ild结构204b形成在第二cesl 308b上。

[0090]

如图13d的截面图1306所示,第二衬底202b可以被减薄以减小第二衬底202b的厚度。在各种实施例中,可以通过蚀刻和/或机械磨削第二衬底202b的背侧来减薄第二衬底202b以减小第二衬底202b的厚度(例如,从在约700μm与约800μm之间的范围内的第一厚度t1减小到在约20μm与约80μm之间的范围内的第二厚度t2)。

[0091]

如图13e的截面图1308所示,第二tsv 214b形成为延伸穿过第二衬底202b。沿第二衬底202b的背侧形成第二背侧键合结构210b。可以在沿着第二衬底202b的背侧形成的第二钝化结构211b上和/或之内形成第二背侧接合结构210b。

[0092]

如图13f的截面图1310所示,第二衬底202b被分隔以形成多个第二小芯片104a-104b。在一些实施例中,第二衬底202b可以通过将第二衬底202b安装到一片切割胶带1212的粘性表面上的切割工艺来分割。然后,晶圆锯沿着划片线1312切割第二衬底202b,以将第二衬底202b分离成多个第二小芯片104a-104b。

[0093]

如图14a的截面图1400所示,提供了第三衬底202c。在各种实施例中,第三衬底202c可以是任何类型的半导体主体(例如,硅、sige、soi等),例如半导体晶圆和/或晶圆上的一个或多个管芯,以及任何其他类型的半导体和/或与之相关联的外延层。

[0094]

如图14b的截面图1402所示,在第三衬底202c上和/或之内形成多个无源器件224。在一些实施例中,多个无源器件224可以包括具有第一导电层225a的电容器,该第一导电层225a与第二导电层225c被电容器电介质层225b分离。在其他实施例中,多个无源器件224可以包括电感器或电阻器等。

[0095]

如图14c的截面图1404所示,第三cesl 308c形成在第三衬底202c上。可以在第三ild结构204c内形成第三多个互连206c,第三ild结构204c形成在第三cesl 308c上。

[0096]

如图14d的截面图1406所示,第三衬底202c可以被减薄以减小第三衬底202c的厚度。在各种实施例中,可以通过蚀刻和/或机械磨削第三衬底202c的背侧来减薄第三衬底202c以减小第三衬底202c的厚度(例如,从在约700μm与约800μm之间的范围内的第一厚度t1减小到在约20μm与约80μm之间的范围内的第二厚度t2)。

[0097]

如图14e的截面图1408所示,第三tsv 214c形成为延伸穿过第三衬底202c。沿着第三衬底202c的背侧形成第三背侧键合结构210c。可以在沿着第三衬底202c的背侧形成的第三钝化结构211c上和/或之内形成第三背侧接合结构210c。

[0098]

如图14f的截面图1410所示,第三衬底202c被切割以形成多个第三小芯片106a-106b。在一些实施例中,第三衬底202c可以通过将第三衬底202c安装到一片切割胶带1212的粘性表面上的切割工艺来分割。然后,晶圆锯沿着划片线1412切割第三衬底202c,以将第三衬底202c分离成多个第三小芯片106a-106b。

[0099]

如图15a的截面图1500所示,提供了第四衬底202d。在各种实施例中,第四衬底202d可以是任何类型的半导体主体(例如,硅、sige、soi等),例如半导体晶圆和/或晶圆上的一个或多个管芯,以及任何其他类型的半导体和/或与之相关联的外延层。

[0100]

如图15b的截面图1502所示,第三多个晶体管器件228形成在第四衬底202d上和/或之内。第三多个晶体管器件228可以包括第四衬底202d内的大部分器件。在一些实施例中,第三多个晶体管器件228可以限定一个或多个栅极驱动器电路。在一些实施例中,第三多个晶体管器件228可以形成为具有第三栅极结构,该第三栅极结构具有不同于(例如大于)第一栅极长度214和/或第二栅极长度220的第三栅极长度230。在一些实施例中,第三栅极结构228g可以包括第三栅极电极228e,第三栅极电极228e与第四衬底202d被第三栅极电介质228d分离。在一些实施例中,可以在一个或多个第三隔离结构304d之间的第三阱区302d之上形成第三栅极结构228g。

[0101]

如图15c的截面图1504所示,在第四衬底202d上并且在第三多个晶体管器件228之上形成第四cesl 308d。第四cesl 308d可以包括氮化物(例如氮化硅)或碳化物(例如碳化硅)等。第四多个互连206d可以形成在第四ild结构204d内,第四ild结构204d形成在第四cesl 308d上。

[0102]

如图15d的截面图1506所示,第四衬底202d可以被减薄以减小第四衬底202d的厚度。在各种实施例中,可以通过蚀刻及/或机械磨削第四衬底202d的背侧来减薄第四衬底202d以减小第四衬底202d的厚度(例如,从在约700μm与约800μm之间的范围内的第一厚度减小到在约20μm与约80μm之间的范围内的第二厚度)。

[0103]

如图15e的截面图1508所示,第四tsv 214d形成为延伸穿过第四衬底202d。沿着第四衬底202d的背侧形成第四背侧键合结构210d。可以在沿着第四衬底202d的背侧形成的第四钝化结构211d上和/或之内形成第四背侧接合结构210d。

[0104]

如图15f的截面图1510所示,第四衬底202d被切割以形成多个第四小芯片108a-108b。在一些实施例中,可以通过将第四衬底202d安装到一片切割胶带1212的粘性表面上的切割工艺来分割第四衬底202d。然后,晶圆锯沿着划片线1512切割第四衬底202d,以将第四衬底202d分离成多个第四小芯片108a-108b。

[0105]

如图16a的截面图1600所示,多个第一小芯片102a-102b中的第一小芯片102a耦合到多个第二小芯片104a-104b中的第二小芯片104a。在一些实施例中,第一小芯片102a可以通过第一多个小芯片间连接器110a耦合到第二小芯片104a。在一些实施例中,第一多个小芯片间连接器110a可以包括焊料凸块、铜柱、微凸块(具有在约5μm到约30μm范围内的宽度)、或其他适用凸块结构。

[0106]

如图16b的截面图1602所示,多个第三小芯片106a-106b中的第三小芯片106a耦合

到第一小芯片102a。在一些实施例中,第三小芯片106a可以通过第二多个小芯片间连接器110b耦合到第一小芯片102a。在一些实施例中,第二多个小芯片间连接器110b可以包括焊料凸块、铜柱、微凸块(具有在约5μm到约30μm范围内的宽度)、或其他适用凸块结构。

[0107]

如图16c的截面图1604所示,多个第四小芯片108a-108b中的第四小芯片108a耦合到第一小芯片102a。在一些实施例中,第四小芯片108a可以通过第三多个小芯片间连接器110c耦合到第一小芯片102a。在一些实施例中,第三多个小芯片间连接器110c可以包括焊料凸块、铜柱、微凸块(具有在从约5μm至约30μm的范围内的宽度)、或其他可应用的凸块结构。

[0108]

图17示出了形成包括多个小芯片的集成芯片结构的方法1700的一些实施例的流程图,这些小芯片各自占主导性地具有单一类型集成芯片器件。

[0109]

虽然所公开的方法1700在本文中被示出和描述为一系列动作或事件,但应了解,这些动作或事件的所示出次序不应被解释为具有限制意义。例如,一些动作可以以不同的顺序发生和/或与除本文中所示出和/或描述的那些之外的其他动作或事件同时发生。另外,并非需要全部所示出的动作来实现本文描述的一个或多个方面或实施例。此外,本文所描绘的动作中的一个或多个可以在一个或多个单独的动作和/或阶段中执行。

[0110]

在动作1702处,可以根据第一制造工艺来对第一衬底进行处理,以形成占主导性地具有第一多个器件的第一小芯片,其中第一多个器件是第一类型集成芯片器件。在一些实施例中,第一类型集成芯片器件可以是nmos晶体管。在一些实施例中,第一制造工艺可以是与第一技术节点(例如7nm技术节点)相关联的制造工艺。在一些实施例中,可以根据动作1704-1706来执行第一制造工艺。

[0111]

在动作1704处,可以根据第一制造工艺来对第一半导体晶圆进行处理,以形成第一多个器件。图12a-12e示出了对应于动作1704的一些实施例的截面图1200-1208。

[0112]

在动作1706处,可以将第一半导体晶圆分离成包括第一小芯片的第一多个小芯片。图12f示出了对应于动作1706的一些实施例的截面图1210。

[0113]

在动作1708处,可以根据第二制造工艺对第二衬底进行处理,以形成占主导性地具有第二多个器件的第二小芯片,其中第二多个器件是第二类型集成芯片器件。在一些实施例中,第二类型集成芯片器件可以是pmos晶体管。在一些实施例中,第二制造工艺可以是与第二技术节点(例如,14nm技术节点)相关联的制造工艺。图13a-13f示出了对应于动作1708的一些实施例的截面图1300-1310。

[0114]

在动作1710处,在一些实施例中,可以根据第三制造工艺来对第三衬底进行处理,以形成占主导性地具有第三多个器件的第三小芯片,其中第三多个器件是第三类型集成芯片器件。在一些实施例中,第三类型集成芯片器件可以是无源器件(例如,电容器、电感器或电阻器等)。在一些实施例中,第三制造工艺可以是与第三技术节点(例如,45nm技术节点)相关联的制造工艺。图14a-14f示出了对应于动作1710的一些实施例的截面图1400-1410。

[0115]

在动作1712,在一些实施例中,可以根据第四制造工艺来对第四衬底进行处理,以形成占主导性地具有第四多个器件的第四小芯片,其中第四多个器件是第四类型集成芯片器件。在一些实施例中,第四类型集成芯片器件可以是栅极驱动器电路。在一些实施例中,第四制造工艺可以是与第四技术节点(例如,32nm技术节点)相关联的制造工艺。图15a-15f示出了对应于动作1712的一些实施例的截面图1500-1510。

[0116]

在动作1714,将第一小芯片、第二小芯片、第三小芯片和第四小芯片通过一个或多个小芯片间连接器耦合在一起,以形成集成芯片结构。图16a-16c示出了对应于动作1714的一些实施例的截面图1600-1604。

[0117]

因此,在一些实施例中,本公开涉及包括多个小芯片的集成芯片结构,这些小芯片各自地且占主导性地包括不同类型的集成芯片器件。

[0118]

在一些实施例中,本公开涉及集成芯片结构。该集成芯片结构包括:第一小芯片,所述第一小芯片占主导性地包括耦合到在第一衬底之上的第一多个互连的第一多个集成芯片器件,所述第一多个集成芯片器件是第一类型集成芯片器件;第二小芯片,所述第二小芯片占主导性地包括耦合到在第二衬底之上的第二多个互连的第二多个集成芯片器件,所述第二多个集成芯片器件是与所述第一类型集成芯片器件不同的第二类型集成芯片器件;一个或多个小芯片间连接器,所述一个或多个小芯片间连接器设置在所述第一小芯片和所述第二小芯片之间,并且被配置为电耦合所述第一小芯片和所述第二小芯片;并且其中,所述第一多个互连具有第一最小宽度,所述第一最小宽度与所述第二多个互连的第二最小宽度不同。在一些实施例中,所述第一小芯片仅包括所述第一类型集成芯片器件。在一些实施例中,所述第一小芯片没有所述第二类型集成芯片器件。在一些实施例中,所述第一类型集成芯片器件是nmos晶体管,并且所述第二类型集成芯片器件是pmos晶体管。在一些实施例中,所述nmos晶体管包括具有第一栅极长度的第一栅极结构,并且所述pmos晶体管包括具有与所述第一栅极长度不同的第二栅极长度的第二栅极结构。在一些实施例中,所述第一多个互连包括具有所述第一最小宽度的第一导电接触件,并且所述第二多个互连包括具有与所述第一最小宽度不同的所述第二最小宽度的第二导电接触件。在一些实施例中,该集成芯片结构还包括:第三小芯片,所述第三小芯片占主导性地包括第三多个集成芯片器件,所述第三多个集成芯片器件是与所述第一类型集成芯片器件和所述第二类型集成芯片器件不同的第三类型集成芯片器件;以及第四小芯片,所述第四小芯片占主导性地包括第四多个集成芯片器件,所述第四多个集成芯片器件是与所述第一类型集成芯片器件、所述第二类型集成芯片器件和所述第三类型集成芯片器件不同的第四类型集成芯片器件。在一些实施例中,所述第三小芯片没有晶体管器件。在一些实施例中,所述第三类型集成芯片器件是无源器件,并且所述第四类型集成芯片器件是栅极驱动器电路。

[0119]

在其他实施例中,本公开涉及一种集成芯片结构。该芯片集成结构包括:第一小芯片,所述第一小芯片占主导性地包括设置在第一衬底上或之内的nmos晶体管,其中,所述nmos晶体管包括具有第一栅极长度的第一栅极结构,所述第一栅极结构设置在具有第一掺杂类型的第一源极/漏极区之间;第二小芯片,所述第二小芯片占主导性地包括设置在第二衬底上或之内的pmos晶体管,所述pmos晶体管包括具有与所述第一栅极长度不同的第二栅极长度的第二栅极结构,所述第二栅极结构设置在具有与所述第一掺杂类型不同的第二掺杂类型的第二源极/漏极区之间;以及一个或多个小芯片间连接器,所述一个或多个小芯片间连接器布置在所述第一小芯片和所述第二小芯片之间,其中,所述一个或多个小芯片间连接器被配置为电耦合所述nmos晶体管和所述pmos晶体管。在一些实施例中,该集成芯片结构还包括:第一多个导电接触件,所述第一多个导电接触件与所述nmos晶体管实体接触并且具有第一宽度的底表面;以及第二多个导电接触件,所述第二多个导电接触件与所述pmos晶体管实体接触并且具有第二宽度的底表面,所述第二宽度与所述第一宽度不同。在

一些实施例中,所述第二栅极长度大于所述第一栅极长度。在一些实施例中,该集成芯片结构还包括:第三小芯片,所述第三小芯片占主导性地包括设置在第三衬底上或之内的无源器件;以及第四小芯片,所述第四小芯片占主导性地包括设置在第四衬底上或之内的一个或多个栅极驱动器电路。在一些实施例中,所述第一小芯片大于所述第二小芯片、所述第三小芯片和所述第四小芯片。在一些实施例中,所述第二小芯片、所述第三小芯片和所述第四小芯片设置在所述第一小芯片的上表面上。在一些实施例中,该集成芯片结构还包括:第一接触蚀刻停止层,所述第一接触蚀刻停止层设置在所述第一衬底上并且具有第一类型应变;以及第二接触蚀刻停止层,所述第二接触蚀刻停止层设置在所述第二衬底上并且具有与所述第一类型应变不同的第二类型应变。在一些实施例中,该集成芯片结构还包括:第一侧壁间隔件,所述第一侧壁间隔件沿着所述第一栅极结构的相反侧设置并且具有第一类型应变;以及第二侧壁间隔件,所述第二侧壁间隔件沿着所述第二栅极结构的相反侧设置并且具有与所述第一类型应变不同的第二类型应变。在一些实施例中,在所述第一栅极结构下方延伸的第一沟道区在第一方向上沿第一晶面延伸;并且在所述第一栅极结构下方延伸的第二沟道区在第二方向上沿第二晶面延伸,所述第二方向与所述第一方向不同。

[0120]

在其他实施例中,本公开涉及用于形成集成芯片结构的方法。该方法包括:根据第一制造工艺对第一衬底进行处理,以形成占主导性地具有第一多个器件的第一小芯片,其中,所述第一多个器件是第一类型集成芯片器件;根据第二制造工艺对第二衬底进行处理,以形成占主导性地具有第二多个器件的第二小芯片,其中,所述第二多个器件是与所述第一类型集成芯片器件不同的第二类型集成芯片器件;以及通过一个或多个层间连接器将所述第一小芯片内的第一多个器件电耦合到所述第二小芯片内的第二多个器件。在一些实施例中,所述第一类型集成芯片器件是nmos晶体管;并且所述第二类型集成芯片器件是pmos晶体管。

[0121]

前述概述了若干实施例的特征,使得本领域技术人员可以更好地理解本公开的各方面。本领域技术人员应当理解,他们可以容易地使用本公开作为设计或修改其他工艺和结构的基础,以实现与本文介绍的实施例相同的目的和/或实现与本文介绍的实施例相同的优点。本领域技术人员还应当认识到,这样的等效构造不脱离本公开的精神和范围,并且他们可以在不脱离本公开的精神和范围的情况下在此进行各种改变、替换和变更。

[0122]

示例

[0123]

示例1.一种集成芯片结构,包括:第一小芯片,所述第一小芯片占主导性地包括耦合到在第一衬底之上的第一多个互连的第一多个集成芯片器件,所述第一多个集成芯片器件是第一类型集成芯片器件;第二小芯片,所述第二小芯片占主导性地包括耦合到在第二衬底之上的第二多个互连的第二多个集成芯片器件,所述第二多个集成芯片器件是与所述第一类型集成芯片器件不同的第二类型集成芯片器件;一个或多个小芯片间连接器,所述一个或多个小芯片间连接器设置在所述第一小芯片和所述第二小芯片之间,并且被配置为电耦合所述第一小芯片和所述第二小芯片;并且其中,所述第一多个互连具有第一最小宽度,所述第一最小宽度与所述第二多个互连的第二最小宽度不同。

[0124]

示例2.根据示例1所述的集成芯片结构,其中,所述第一小芯片仅包括所述第一类型集成芯片器件。

[0125]

示例3.根据示例1所述的集成芯片结构,其中,所述第一小芯片没有所述第二类型

集成芯片器件。

[0126]

示例4.根据示例1所述的集成芯片结构,其中,所述第一类型集成芯片器件是nmos晶体管;并且其中,所述第二类型集成芯片器件是pmos晶体管。

[0127]

示例5.根据示例4所述的集成芯片结构,其中,所述nmos晶体管包括具有第一栅极长度的第一栅极结构,并且所述pmos晶体管包括具有与所述第一栅极长度不同的第二栅极长度的第二栅极结构。

[0128]

示例6.根据示例1所述的集成芯片结构,其中,所述第一多个互连包括具有所述第一最小宽度的第一导电接触件,并且所述第二多个互连包括具有与所述第一最小宽度不同的所述第二最小宽度的第二导电接触件。

[0129]

示例7.根据示例1所述的集成芯片结构,还包括:第三小芯片,所述第三小芯片占主导性地包括第三多个集成芯片器件,所述第三多个集成芯片器件是与所述第一类型集成芯片器件和所述第二类型集成芯片器件不同的第三类型集成芯片器件;以及第四小芯片,所述第四小芯片占主导性地包括第四多个集成芯片器件,所述第四多个集成芯片器件是与所述第一类型集成芯片器件、所述第二类型集成芯片器件和所述第三类型集成芯片器件不同的第四类型集成芯片器件。

[0130]

示例8.根据示例7所述的集成芯片结构,其中,所述第三小芯片没有晶体管器件。

[0131]

示例9.根据示例8所述的集成芯片结构,其中,所述第三类型集成芯片器件是无源器件;并且其中,所述第四类型集成芯片器件是栅极驱动器电路。

[0132]

示例10.一种集成芯片结构,包括:第一小芯片,所述第一小芯片占主导性地包括设置在第一衬底上或之内的nmos晶体管,其中,所述nmos晶体管包括具有第一栅极长度的第一栅极结构,所述第一栅极结构设置在具有第一掺杂类型的第一源极/漏极区之间;第二小芯片,所述第二小芯片占主导性地包括设置在第二衬底上或之内的pmos晶体管,其中,所述pmos晶体管包括具有与所述第一栅极长度不同的第二栅极长度的第二栅极结构,所述第二栅极结构设置在具有与所述第一掺杂类型不同的第二掺杂类型的第二源极/漏极区之间;以及一个或多个小芯片间连接器,所述一个或多个小芯片间连接器布置在所述第一小芯片和所述第二小芯片之间,其中,所述一个或多个小芯片间连接器被配置为电耦合所述nmos晶体管和所述pmos晶体管。

[0133]

示例11.根据示例10所述的集成芯片结构,还包括:第一多个导电接触件,所述第一多个导电接触件与所述nmos晶体管实体接触并且具有第一宽度的底表面;以及第二多个导电接触件,所述第二多个导电接触件与所述pmos晶体管实体接触并且具有第二宽度的底表面,所述第二宽度与所述第一宽度不同。

[0134]

示例12.根据示例10所述的集成芯片结构,其中,所述第二栅极长度大于所述第一栅极长度。

[0135]

示例13.根据示例10所述的集成芯片结构,还包括:第三小芯片,所述第三小芯片占主导性地包括设置在第三衬底上或之内的无源器件;以及第四小芯片,所述第四小芯片占主导性地包括设置在第四衬底上或之内的一个或多个栅极驱动器电路。

[0136]

示例14.根据示例13所述的集成芯片结构,其中,所述第一小芯片大于所述第二小芯片、所述第三小芯片和所述第四小芯片。

[0137]

示例15.根据示例13所述的集成芯片结构,其中,所述第二小芯片、所述第三小芯

片和所述第四小芯片设置在所述第一小芯片的上表面上。

[0138]

示例16.根据示例10所述的集成芯片结构,还包括:第一接触蚀刻停止层,所述第一接触蚀刻停止层设置在所述第一衬底上并且具有第一类型应变;以及第二接触蚀刻停止层,所述第二接触蚀刻停止层设置在所述第二衬底上并且具有与所述第一类型应变不同的第二类型应变。

[0139]

示例17.根据示例10所述的集成芯片结构,还包括:第一侧壁间隔件,所述第一侧壁间隔件沿着所述第一栅极结构的相反侧设置并且具有第一类型应变;以及第二侧壁间隔件,所述第二侧壁间隔件沿着所述第二栅极结构的相反侧设置并且具有与所述第一类型应变不同的第二类型应变。

[0140]

示例18.根据示例10所述的集成芯片结构,其中,在所述第一栅极结构下方延伸的第一沟道区在第一方向上沿第一晶面延伸;并且其中,在所述第一栅极结构下方延伸的第二沟道区在第二方向上沿第二晶面延伸,所述第二方向与所述第一方向不同。

[0141]

示例19.一种形成集成芯片结构的方法,包括:根据第一制造工艺对第一衬底进行处理,以形成占主导性地具有第一多个器件的第一小芯片,其中,所述第一多个器件是第一类型集成芯片器件;根据第二制造工艺对第二衬底进行处理,以形成占主导性地具有第二多个器件的第二小芯片,其中,所述第二多个器件是与所述第一类型集成芯片器件不同的第二类型集成芯片器件;以及通过一个或多个层间连接器将所述第一小芯片内的第一多个器件电耦合到所述第二小芯片内的第二多个器件。

[0142]

示例20.根据示例19所述的方法,其中所述第一类型集成芯片器件是nmos晶体管;并且其中所述第二类型集成芯片器件是pmos晶体管。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。