1.本公开的实施例涉及一种锁相环,并且具体地涉及一种包括振荡器的锁相环。

背景技术:

2.已知提供了一种包括压控振荡器的锁相环,其中压控振荡器包括并联连接的电感器和电容器,还包括与其并联连接的负电阻结构。还已知提供了与负电阻结构并联的可调谐电容,使得压控振荡器的输出频率以及因此锁相环的振荡频率可以由控制输入信号来调谐。

3.提供基于电容器的调谐的一种方式是通过使用一个或多个变容二极管,其中控制信号可以施加到变容二极管。虽然变容二极管能够实现非常精细的频率分辨率,但是变容二极管的品质因数(与放入谐振电路时每个振荡周期的信号损失有关的度量)随着频率的增加而降低,这使得振荡器的相位噪声劣化。

技术实现要素:

4.根据第一方面,提供了一种锁相环,包括压控振荡器。该压控振荡器包括:并联连接的电感器和电容器;以及与电感器和电容器并联连接的负电阻结构。负电阻结构的第一端子连接到电感器和电容器的相应第一端子,并且负电阻结构的第二端子连接到电感器和电容器的相应第二端子。负电阻结构呈现出可调谐电容,使得压控振荡器的输出频率可以由控制输入信号来调谐,并且该控制输入信号在锁相环中生成。负电阻结构包括第一晶体管和第二晶体管,并且第一晶体管和第二晶体管中的每个晶体管在其第一端子和第二端子之间具有相应的晶体管传导路径,并且每个晶体管具有控制端子。第一晶体管的第一端子与第二晶体管的控制端子之间存在第一传导路径,第一晶体管的控制端子与第二晶体管的第一端子之间存在第二传导路径,并且第一晶体管和第二晶体管中的至少一个晶体管的控制端子由控制输入信号来偏置;使得第一晶体管和第二晶体管中的所述至少一个晶体管的寄生电容能够由所述控制输入信号来调谐,以便调谐压控振荡器的输出频率,从而调谐锁相环的振荡频率。

5.负电阻结构可以包括多个第一晶体管和第二晶体管,并且第一晶体管和第二晶体管中的至少一个晶体管中的每一个晶体管的控制端子可以由控制输入信号偏置。

6.第一晶体管和第二晶体管包括cmos器件。

7.更具体地,第一晶体管和第二晶体管可以包括nmos器件,或者可以包括pmos器件。

8.第一晶体管和第二晶体管中的一个晶体管可以包括pmos器件,而第一晶体管和第二晶体管中的另一个晶体管包括nmos器件。

9.第一晶体管和第二晶体管的控制端子可以包括栅极端子。

10.第一晶体管和第二晶体管的第一端子可以包括漏极端子。

11.第一晶体管和第二晶体管两者的控制端子可以由控制输入信号偏置,而所述第一晶体管和所述第二晶体管两者的第一端子由电源电压偏置。

12.第一晶体管和第二晶体管两者的第一端子可以由所述电源电压通过阻抗偏置。第一晶体管和第二晶体管两者的第一端子可以由电源电压通过电感器偏置。

13.第一晶体管和第二晶体管的第二端子可以接地,或者可以连接到电流源,或者可以连接到调谐阻抗。

14.第一晶体管和第二晶体管中仅一个晶体管的控制端子可以由控制输入信号偏置,而第一晶体管和第二晶体管中的所述一个晶体管的第二端子由电源电压偏置。

15.可以将从所述压控振荡器的输出导出的信号的相位可以利用参考信号进行控制,并且将得到的相位误差信号传递到滤波器以导出振荡器的控制输入信号。

16.从所述压控振荡器的输出导出的信号可以是所述压控振荡器的输出。

17.从所述压控振荡器的输出导出的信号可以是所述压控振荡器的输出的分频或倍频版本。

18.这样做的好处是,有源器件的固有电容用于通过周期性地调制这些电容来实现频率调谐。这不需要在调谐振荡(tank)网络中引入额外的有损组件,因此有助于提高振荡器的品质因数和相位噪声性能,尤其是在诸如毫米波和太赫兹频段之类的较高频率下。这也有助于通过减少振荡网络中频率相关组件的数量来降低电源和温度敏感性。

附图说明

19.为了更好地理解本公开的示例以及为了更清楚地示出可以如何有效地实施示例,现在将仅通过举例说明参考附图,在附图中:

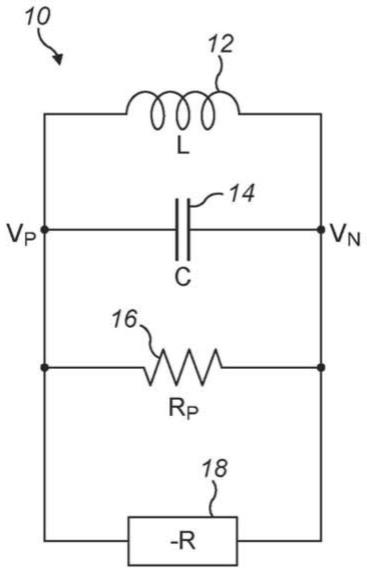

20.图1示出了振荡器的一般形式。

21.图2示出了根据一个实施例的包括受控振荡器的锁相环。

22.图3示出了替代形式的受控振荡器。

23.图4示出了另一种替代形式的受控振荡器。

24.图5示出了根据另一实施例的包括另一种替代形式的受控振荡器的锁相环。

25.图6示出了另一种替代形式的受控振荡器。

26.图7示出了另一种替代形式的受控振荡器。

27.图8图示了本文说明的受控振荡器的操作。

具体实施方式

28.图1示出了振荡器10的一般形式。

29.电感器(l)12和电容器(c)14并联连接以形成调谐振荡(tank)网络,其中在电感器12和电容器14各自的第一端子处具有电压v

p

并且在电感器12和电容器14各自的第二端子处具有电压vn。电感值l和电容值c共同决定振荡器10的大致振荡频率。

30.调谐振荡网络中的损耗由电阻器(r

p

)16表示。

31.负电阻(-r)结构18用于补偿调谐振荡网络中的损耗,以维持电路中的振荡。因此,负电阻结构18与电感器12和电容器14并联连接。

32.负电阻可以采用各种电路配置中的有源器件的形式。例如,有源器件可以用cmos技术中的晶体管实现(其可以是(i)仅pmos、(ii)仅nmos、或(iii)pmos和nmos器件的混合)。可以使用的其他技术包括双极技术和hemt(基于所谓的iii-v族材料的高电子迁移率晶体

管)。不用说,振荡器可以以广泛的集成电子电路技术来实现。

33.如下文更详细描述的,在本文公开的实施例中,调谐lc振荡器利用这些有源器件的固有电容、通过从上述电容值c修改电路的总电容来实现频率调谐。更具体地,这是通过周期性地调制有源器件的电容来实现的。

34.图2示出了根据一个实施例的锁相环30形式。

35.锁相环30包括受控振荡器32,其在该实施例中采用压控振荡器(vco)的形式。

36.振荡器32具有输出端子34,并且振荡器32在输出端子34的输出用作锁相环的输出信号源。在该实施例中,振荡器32在输出端子34处的输出被传递到第一分频器36,第一分频器36将输出的频率除以整数或小数值m,以便在输出38上生成锁相环的输出信号。

37.原则上,这种一般形式的锁相环可用于生成任何所需频率的输出信号。然而,振荡器32的形式在用于生成高频的输出信号时特别有利,例如在毫米波频带(在30ghz-300ghz范围内)或甚至在太赫兹频带(例如在300ghz-3thz或更高范围内),因为它避免了需要使用变容二极管,变容二极管的品质因数通常会在较高频率下降低。

38.从压控振荡器的输出导出的信号也被传递到相位检测器(pd)或相位频率检测器(pfd)40的第一输入。在这个图示的实施例中,压控振荡器32的输出被传递到第二分频器41,第二分频器41将输出的频率除以n,以便生成从压控振荡器的输出导出的信号。在另一实施例中,没有分频,并且从压控振荡器的输出导出的信号是压控振荡器的输出,该输出可以在其施加到相位检测器(pd)或者相位频率检测器(pfd)40之前被缓冲。

39.参考信号(ref)被传递到相位或相位频率检测器40的第二输入,检测器40生成表示参考信号与从压控振荡器32的输出导出的信号之间的相位或频率误差的输出信号。

40.在这个实施例中,相位或频率误差信号被传递到环路滤波器(lf)42,并且滤波后的相位或频率误差信号被传递到受控振荡器32的控制输入46以充当振荡器的控制输入信号。

41.具体地,振荡器32的控制输入信号被传递到电压控制(vc)块44。图2(a)和图2(b)示出了电压控制块44的更多细节。

42.在图2(a)所示的实施例中,锁相环30中的环路滤波器42为数字滤波器,该数字滤波器提供数字输出信号,该数字输出信号由数模转换器44a转换为模拟信号以生成用于压控振荡器32中的控制电压输出。

43.在图2(b)所示的实施例中,锁相环30中的环路滤波器42是模拟滤波器,它提供模拟控制输入信号。在这种情况下,电压控制块44是放大器44b,其将控制输入电压或电流信号转换为用于压控振荡器32中的控制电压输出。在又一些实施例中,锁相环是混合锁相环,为振荡器导出数字控制信号和模拟控制信号两者。

44.图2还示出了该实施例中的压控振荡器32形式。

45.具体地,振荡器32包括并联连接的电感器50和电容器52。还有与电感器50和电容器52并联连接的负电阻结构54,使得负电阻结构54的和电感器50和电容器52各自的第一端子在点56处连接在一起(在该点处具有电压v

p

),并且负电阻结构54的和电感器50和电容器52各自的第二端子

46.在点58处连接在一起(在该点处具有电压vn)。

47.电源电压v

dd

通过电感器50的中心抽头提供。

48.如下文更详细解释的,负电阻结构54呈现出可调谐电容,使得压控振荡器的输出频率可以由控制输入信号46(v

调谐

)来调谐。

49.在本实施例中,负电阻结构包括采用cmos技术实现的第一晶体管60和第二晶体管62,并且第一晶体管60和第二晶体管62交叉耦合。

50.也就是说,第一晶体管60的漏极连接到点56,并且第二晶体管62的漏极连接到点58。第一晶体管60的漏极还通过电容器64连接到第二晶体管62的栅极,并且第二晶体管62的漏极还通过电容器66连接到第一晶体管60的栅极。第一晶体管60和第二晶体管62的源极一起连接到节点vs。

51.因此,晶体管的栅极端子的偏置点与漏极端子隔离,并以不同的电压而被偏置。

52.在控制输入端子46处接收的控制输入信号(v

调谐

)通过相应的阻抗(此阻抗在该图示实施例中为电阻器68)连接到第一晶体管60的栅极,并且通过相应的阻抗(此阻抗在该图示实施例中为电阻器70)连接到第二晶体管62的栅极。

53.因此,在该实施例中,两个晶体管的栅极均由控制输入信号来偏置。然后,可以通过改变器件的偏置点来调制晶体管中的电容,从而对振荡器电路32的振荡频率进行调谐。

54.这意味着无需将任何有损组件引入振荡器的lc振荡回路即可实现频率调谐,这意味着品质因数不会降低。类似地,无需将额外的频率相关组件引入振荡器中即可实现频率调谐,从而降低电源和温度敏感性。此外,这能够产生非常精细的频率调谐步骤,因为可以实现器件电容的非常精细的调制。

55.图3更详细地示出了图2所示的压控振荡器32的形式。图3所示的压控振荡器32的组件由与图2所示的压控振荡器32的组件相同的附图标记指示。

56.图3还示出了晶体管60、62的栅极处的电压vg和晶体管60、62的源极处的电压vs。

57.图3还示出了分别存在于晶体管60、62的栅极和漏极之间以及栅极和源极之间的固有器件电容c

gd

和c

gs

。

58.响应于控制输入端子46上的控制输入信号v

调谐

,由晶体管60、62的栅极处的电压v

g,60

和v

g,62

来调制电容c

gd

和c

gs

,以便调整电路的总电容,从而调整振荡器32的振荡频率。

59.虽然图3示出了振荡器电路的一个特定示例,但应理解,相同的技术可扩展到其他lc振荡器结构,例如pmos类型、互补mos(pmos和nmos)类型和电流重用类型等。尽管图2和图3示出了晶体管60、62的源极连接在一起,但有些振荡器电路并非如此,例如分离调谐振荡器和gm增强型振荡器、和具有周期性尾偏置的振荡器、以及变压器偏置c类振荡器。负电阻也可以以双极技术以及cmos技术来实现。

60.振荡器32也可用于各种vco工作模式,例如13类、c类、双导等。

61.图4示出了压控振荡器82的略微修改形式。图4所示的压控振荡器82的组件由与图3所示的压控振荡器32的组件相同的附图标记指示。

62.图3示出了一实施例,其中为了偏置电容c

gd

和c

gs

而施加的控制信号v

调谐

是在控制输入端子46上从外部模拟源接收的模拟电压。在模拟pll的情况下,这可以是环路滤波器输出电压。在具有数字环路滤波器的数字或混合pll的情况下,数字环路滤波器的输出可应用于数模转换器,例如图2所示的数模转换器44,以便生成在振荡器32的控制输入端子46上接收的模拟电压。

63.相比之下,图4示出了一实施例,其中在振荡器82的控制输入端子46上接收的输入

是数字控制字,其例如可以直接从数字或混合pll中的数字环路滤波器接收。

64.该数字控制字被施加到数模转换器84,以便生成模拟控制信号v

调谐

,该模拟控制信号v

调谐

被施加到晶体管60、62的栅极端子,以便偏置电容c

gd

和c

gs

。

65.图5示出的锁相环包括另一种替代形式的压控振荡器,其中通过将所需的总负电阻分成更小的单元来实现不同的调谐范围。同样,该原理也可以应用于其他振荡器结构,例如推挽(cmos)振荡器、pmos振荡器、c类振荡器、b类振荡器和ab类振荡器等。

66.具体地,图5示出了锁相环90,包括压控振荡器100。如参考图2一般描述的,振荡器100的输出被施加到分频器(1/n)92,其中分频器92的输出、和参考信号被施加到相位检测器(pd)或相位/频率检测器(pfd)94的输入。在该实施例中,pfd 94生成可以被认为包括多个部分的误差信号error

粗略

,...,error

精细

。例如,在数字信号的情况下,这些可以是信号的不同位。

67.例如,最高有效位可以表示粗略误差,而最低有效位表示精细误差等。

68.误差信号被传递到环路滤波器96,该环路滤波器96又可以生成可被认为包括多个部分control

粗略

,...,control

精细

的控制信号。例如,在数字信号的情况下,这些可以是信号的不同位。

69.例如,最高有效位可用于粗略频率控制,而最低有效位可用于精细频率控制等。

70.然而,控制信号可以是模拟的,或者它们可以是数字的,或者它们可以是模拟和数字的组合。例如,control

粗略

和control

精细

可以都是数字的,或者可以都是模拟的,或者control

粗略

可以是数字的,而control

粗略

是模拟的等。

71.如参考图2所述,控制信号被传递到电压控制块98。

72.振荡器100包括并联连接的电感器102和电容器104。与电感器102和电容器104并联连接的还有负电阻结构106,使得负电阻结构106的以及电感器102和电容器104各自的第一端子在点108处连接在一起(在该点处具有电压v

p

),并且负电阻结构106的以及电感器102和电容器104各自的第二端子在点110处连接在一起(在该点处具有电压vn)。

73.电源电压v

dd

通过电感器102的中心抽头提供。

74.如在较早的实施例中,负电阻结构106呈现出可调谐电容,使得压控振荡器的输出频率可以由控制输入信号来调谐。

75.在该实施例中,负电阻结构包括多对晶体管,其中第一对晶体管包括第一晶体管112.0和第二晶体管114.0。

76.这些晶体管112.0、114.0是交叉耦合的。也就是说,第一晶体管112.0的漏极连接到点108,并且第二晶体管114.0的漏极连接到点110。第一晶体管112.0的漏极还连接到第二晶体管114.0的栅极,并且第二晶体管114.0的漏极还连接到第一晶体管112.0的栅极。第一晶体管112.0和第二晶体管114.0的源极一起连接到节点vs。节点vs可以替代地接地(例如通过阻抗),或者连接到恒流源。

77.负电阻结构106的第二对晶体管为第一调谐对,其包括第一晶体管112.1和第二晶体管114.1。

78.第一调谐对112.1的第一晶体管的漏极连接到点108,并且第一调谐对114.1的第二晶体管的漏极连接到点110。第一调谐对112.1的第一晶体管的漏极还通过电容器116.1连接到第一调谐对114.1的第二晶体管的栅极,并且第一调谐对114.1的第二晶体管的漏极

也通过电容器118.1连接到第一调谐对112.1的第一晶体管的栅极。第一调谐对112.1、114.1的第一晶体管和第二晶体管的源极也连接到节点v

cc

。

79.类似地,负电阻结构106的第n对调谐晶体管包括第一晶体管112.n和第二晶体管114.n。

80.该第n调谐对112.n的第一晶体管的漏极连接到点108,并且第n调谐对114.n的第二晶体管的漏极连接到点110。第n调谐对112.n的第一晶体管的漏极还通过电容器116连接到第n调谐对114.n的第二晶体管的栅极,并且第n调谐对114.n的第二晶体管的漏极还通过电容器118.n连接到第n调谐对112.n的第一晶体管的栅极。第n调谐对112.n、114.n的第一晶体管和第二晶体管的源极也连接到节点v

cc

。

81.在该实施例中,包括多对晶体管的负电阻结构提供了确保振荡器电路中持续振荡所需的总负电阻,并且电容的各部分可以被单独调制。

82.各个晶体管的尺寸使得能够以各种步长进行频率调谐。因此,图5示出了具有尺寸为m

cc1

=α1m

cc

的第一调谐对112.1、114.1的晶体管。类似地,第二调谐对112.2、114.2的晶体管具有尺寸m

cc2

=α2m

cc

,依此类推,直到第n调谐对112.n、114.n的晶体管具有尺寸m

ccn

=α

nmcc

,使得存在于晶体管的栅极和漏极之间以及栅极和源极之间的电容分别由c

gdn

和c

gsn

给出。

83.同样,可以调制用作负电阻的有源器件的这些器件电容,以便调谐振荡器100。

84.具体来说,控制输入被划分为多个部分,其中控制输入的第一部分v

调谐,1

通过相应的电阻器120.1、122.1等被施加到第一调谐对的晶体管112.1、114.1的栅极,直到控制输入的最后(第n)部分v

调谐,n

通过相应的电阻器120.n、122.n被施加到第n调谐对的晶体管112.n、114.n的栅极。

85.因此,控制输入信号可以被划分为多部分,其中每个部分偏置不同的晶体管对并对总电容产生单独的影响,从而对振荡频率产生单独的影响。这些效果被组合起来以便产生总的调谐效果。

86.因此,例如可以使用分段的pd/pfd 94,其中不同大小的相位误差的控制信号被分离。对于较大的相位误差,生成vbiasl,这导致控制输入的第一部分v

调谐,1

被施加到第一调谐对的晶体管112.1、114.1的栅极,因此充当粗略频率调谐。对于中等相位误差,vbias2由pd/pfd94和环路滤波器94生成。这导致控制输入被施加到中间晶体管对的晶体管的栅极。对于小的相位误差,pd/pfd 94和环路滤波器96生成vbias3,这导致控制输入的第n部分v

调谐,n

被施加于第n调谐对的晶体管112.n、114.n的栅极,因此提供了对电容的精细调谐,从而对振荡器的频率进行精细调谐。这可以扩展以实现广泛的频率分辨率。

87.图6示出了另一种替代形式的压控振荡器。具体而言,尽管先前的实施例使用了pmos晶体管对,并且尽管等同实施例使用了nmos晶体管对,但图6示出了电流重用压控振荡器。在这样的结构中,可以控制两个晶体管。然而,图6示出的示例中,晶体管中的仅一个晶体管被控制输入偏置。

88.振荡器140包括并联连接的电感器142和电容器144。与电感器142和电容器144并联连接的还有负电阻结构150,使得负电阻结构150的以及电感器142和电容器144各自的第一端子在点146处连接在一起(在该点处具有电压v

p

),并且负电阻结构150的以及电感器142和电容器144各自的第二端子在点148处连接在一起(在该点处具有电压vn)。

89.如前所述,负电阻结构150呈现出可调谐电容,使得压控振荡器的输出频率可以由控制输入信号来调谐。

90.在本实施例中,负电阻结构150包括作为nmos晶体管的第一晶体管152以及作为pmos晶体管的第二晶体管154。

91.第一晶体管和第二晶体管152、154交叉耦合。也就是说,第一晶体管152的漏极连接到点146,并且第二晶体管154的漏极连接到点148。第一晶体管152的漏极还通过电容器156连接到第二晶体管154的栅极,并且第二晶体管154的漏极还连接到第一晶体152的栅极。

92.第一晶体管152的源极连接到节点v

cc

,而第二晶体管154的源极连接到电源电压v

dd

。

93.因此,晶体管154的栅极端子的偏置点与晶体管152的漏极端子隔离,并且以不同的电压被偏置。

94.在控制输入端子158处接收的控制输入信号(v

调谐

)通过电阻器160连接到第二晶体管154的栅极。

95.因此,在该实施例中,晶体管中的仅一个晶体管(即pmos晶体管154)的栅极由控制输入信号偏置。然后,可以通过改变器件的偏置点来调制晶体管154中的电容,从而对振荡器电路140的振荡频率进行调谐。具体来说,图6示出了分别存在于晶体管154的栅极和漏极之间、以及栅极和源极之间的电容c

gd

和c

gs

。

96.响应于控制输入端子158上的控制输入信号v

调谐

,由晶体管154的栅极处的电压vg对电容c

gd

和c

gs

进行调制,以便调整电路的总电容,从而调整振荡器140的振荡频率。

97.图7示出了另一种替代形式的压控振荡器。具体而言,图7示出了电流重用压控振荡器180的替代形式。与图6所示的振荡器140的特征对应的振荡器180的特征

98.由相同的附图标记指示。

99.因此,振荡器180包括并联连接的电感器142和电容器144。与电感器142和电容器144并联连接的还有负电阻结构182,使得负电阻结构182的以及电感器142和电容器144各自的第一端子在点184处连接在一起(在该点处具有电压v

p

),并且负电阻结构182的以及电感器142和电容器144各自的第二端子在点186处连接在一起(在该点处具有电压vn)。

100.如前所述,负电阻结构182呈现出可调谐电容,使得压控振荡器的输出频率可以由控制输入信号来调谐。

101.在本实施例中,负电阻结构182包括作为nmos晶体管的第一晶体管152以及作为pmos晶体管的第二晶体管154。

102.第一晶体管和第二晶体管152、154交叉耦合。也就是说,第一晶体管152的漏极连接到点184,并且第二晶体管154的漏极连接到点186。第一晶体管152的漏极还连接到第二晶体管154的栅极,并且第二晶体管154的漏极还通过电容器188连接到第一晶体管152的栅极。

103.第一晶体管152的源极连接到电压v

cc

,而第二晶体管154的源极连接到电源电压v

dd

。

104.因此,晶体管152的栅极端子的偏置点与漏极端子隔离,并且以不同的电压被偏置。

105.在控制输入端子158处接收的控制输入信号(v

调谐

)通过电阻器190连接到第一晶体管152的栅极。

106.因此,在该实施例中,晶体管中的仅一个晶体管(在该实施例中即nmos晶体管152)的栅极由控制输入信号偏置。然后,可以通过改变器件的偏置点来调制晶体管152中的电容,从而对振荡器电路180的振荡频率进行调谐。

107.具体来说,图7示出了分别存在于晶体管152的栅极和漏极之间、以及栅极和源极之间的电容c

gd

和c

gs

。

108.响应于控制输入端子158上的控制输入信号v

调谐

,由晶体管152的栅极处的电压vg对电容c

gd

和c

gs

进行调制,以便调整电路的总电容,从而调整振荡器180的振荡频率。

109.图8是提供对本文描述的实施例背后的物理过程给出定性解释的图。

110.因此,图8示出了有源器件(例如前述振荡器中使用的晶体管)的寄生电容c

gd

和c

gs

如何呈现出非线性特性。

111.具体来说,图8示出了通过栅极端子和漏极端子的隔离偏置来调制器件电容的效果。在振荡器中,如前图所示,漏极端子和栅极端子处的相应电压可以写为:

[0112]vd

=v

dd

a

t

cos(φ),并且

[0113]vg

=v

调谐,n-a

t

cos(φ),

[0114]

其中,v

dd

是电源电压,v

调谐

是调谐电压,f是振荡相位,并且a

t

为振荡幅度。a

t

由振荡器电流和振荡(tank)阻抗设定,并在nmos/pmos型振荡器的情况下具有2v

dd

的上限(如图2、3、4和5所示)或在使用互补型mos,即pmos和nmos两者的推挽型振荡器的情况下具有v

dd

的上限(如图6和图7所示)。

[0115]

图8(a)示出了寄生电容c

gd

和c

gs

如何随栅极电压电平而变化。线200、202还示出了晶体管之一的栅极和漏极电压电平在一次振荡过程期间如何随时间变化。

[0116]

由于振荡器遵循大信号操作,因此从图8可以看出,在其工作期间,振荡器中的晶体管穿过不同的工作区域,即截止、饱和以及三极管区域。调谐振荡回路看到的有效电容是积分电容与电压特性的加权平均值,由它在其振荡的一个周期内呈现。

[0117]

因此,可以通过改变器件在每个区域花费的时间量来改变所看到的有效电容。

[0118]

图8(a)示出了栅极和漏极以同一电位被偏置的情况,即vg=vd。晶体管穿过所有工作区域,从而生成等效电容c1。

[0119]

图8(b)示出了栅极被偏置到比漏极高的电位的情况。在这种情况下,线204、206示出了栅极和漏极电压电平在其一个振荡周期的过程中如何随时间变化。

[0120]

在这种情况下,与图8(a)相比,图8(b)示出了晶体管在三极管区域中花费每个振荡周期的比例更大,从而导致电容c2略高,其中c2-c1=δc1。

[0121]

图8(c)示出了栅极被偏置到比漏极低的电位的情况。在这种情况下,线208、210示出了在一次振荡过程中栅极和漏极电压电平如何随时间变化。

[0122]

在这种情况下,与图8(a)相比,图8(c)示出了晶体管在截止区域中花费每个振荡周期的比例更大,从而导致电容c3略低,其中c1-c3=δc2。

[0123]

因此描述了一种锁相环,它允许在不需要使用有损或频率相关组件的情况下对振荡器生成的输出频率进行精细调谐。

[0124]

本领域的普通技术人员在实践请求保护的本发明时,可以根据对附图、说明书和

所附权利要求的研究,理解和实现对上述公开的实施例进行的改变。在权利要求中,词语“包括”不排除其他元件或步骤,并且不定冠词“一”或“一种”不排除复数。单独的处理器或其他单元可以实现权利要求中引用的几个条目的功能。唯一的事实在于,在相互不同的从属权利要求中叙述的一些措施并不表示这些措施的组合不能被有利地使用。计算机程序可以存储/分布于合适的介质上,如,与其他硬件一起或作为其他硬件的一部分提供的光学存储介质或固态介质,但是也可以以其他形式分布,如,经由互联网或其他有线或无线通讯系统。权利要求中的任何附图标记不应被解释为限制范围。

[0125]

应当注意,上述实施例说明而非限制本发明,并且本领域技术人员将能够设计很多备选实施例而不脱离所附权利要求的范围。词语“包括”不排除存在除了权利要求中所列出的元素或步骤之外的元素或步骤,“一”或“一个”不排除多个,并且单个特征或其它单元可以完成权利要求中记载的若干单元的功能。权利要求中的任何附图标记不应理解为对其范围的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。