1.本发明涉及半导体技术领域,具体而言,涉及一种单结晶体管结构及其 制造方法。

背景技术:

2.传统单结晶体管有稳定和不稳定两个区:稳定区,发射极pn结关闭, 两个基极之间的电流缓慢增加,主要为少子的注入;不稳定区,发射极pn 结开启,非稳态载流子注入,并漂移向一个基极电极,发射极和基极电极之 间的电阻降低,导致pn结正偏电压增大,形成正反馈。单结晶体管可用于 与电阻和电容构建成弛豫振荡器,可广泛应用于磁场、温度、光、压力和射 线等的测量。传统的体硅单结晶体管由两个欧姆基极接触和一个发射极pn 结构成,由于体硅工艺的单结晶体管的结构限制,导致调控手段单一,无法 很好的优化电路性能。

技术实现要素:

3.有鉴于此,本发明实施例的目的在于提供一种单结晶体管结构及其制 造方法,单结晶体管结构可实现对自身器件性能进行灵活调整。

4.第一方面,本技术通过一实施例提供如下技术方案:

5.一种单结晶体管结构,包括:衬底,在所述衬底上依次设置有第一氧化 层、配置层和第二氧化层,在所述第二氧化层上设置有第一高掺杂区、沟道 区以及第二高掺杂区;所述沟道区位于所述第一高掺杂区和所述第二高掺 杂区之间,所述沟道区分别与所述第一高掺杂区和所述第二高掺杂区欧姆 接触,所述配置层用于接入偏置电压。

6.可选的,所述配置层连接有引出部,所述引出部从所述第一高掺杂区和 /或所述第二高掺杂区远离所述沟道区的一侧引出。

7.可选的,所述引出部与所述第一高掺杂区和/或所述第二高掺杂区之间 设置有隔离区。

8.可选的,所述隔离区的材料为si3n4。

9.可选的,所述第一高掺杂区和所述第二高掺杂区为n型高掺杂。

10.可选的,所述沟道区为n型低掺杂。

11.可选的,所述配置层的材料为si。

12.可选的,还包括第三高掺杂区;所述第三高掺杂区位于所述沟道区上方, 并与所述沟道区形成发射结。

13.可选的,所述第三高掺杂区为p型高掺杂区。

14.第二方面,基于同一发明构思,本技术通过一实施例提供如下技术方案:

15.一种单结晶体管结构制造方法,包括:

16.提供衬底;在所述衬底上方依次形成所述第一氧化层、所述配置层、所 述第二氧化层以及顶层硅膜;对所述顶层硅膜的第一区域、第二区域和第三 区域分别进行掺杂,形

成第一高掺杂区、沟道区以及第二高掺杂区;在所述 配置层上方形成与所述配置层连接的引出部;其中,所述引出部从所述第一 高掺杂区和/或所述第二高掺杂区远离所述沟道区的位置延伸出;在所述引 出部与所述第一高掺杂区和/或所述第二高掺杂区之间形成隔离区。

17.本发明实施例提供的一种单结晶体管结构,包括:衬底、第一氧化层、 配置层、第二氧化层、第一高掺杂区、沟道区以及第二高掺杂区。第一氧化 层形成在衬底上;配置层形成在第一氧化层上;第二氧化层形成在配置层上, 第一高掺杂区、沟道区以及第二高掺杂区均形成在第二氧化层上,沟道区位 于第一高掺杂区和第二高掺杂区之间并欧姆接触。该单结晶体管结构具有 独立的配置层形成的背栅结构,并且该配置层位于第一氧化层和第二氧化 层之间可有效的屏蔽外界干扰,在配置层接入偏置电压之后,可实现大范围 的电压调节,实现对单结晶体管结构的器件性能进行灵活调整,以应用于不 同应用环境。

18.为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施 例,并配合所附附图,作详细说明如下。

附图说明

19.为了更清楚地说明本发明实施例的技术方案,下面将对实施例中所需 要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实 施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在 不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

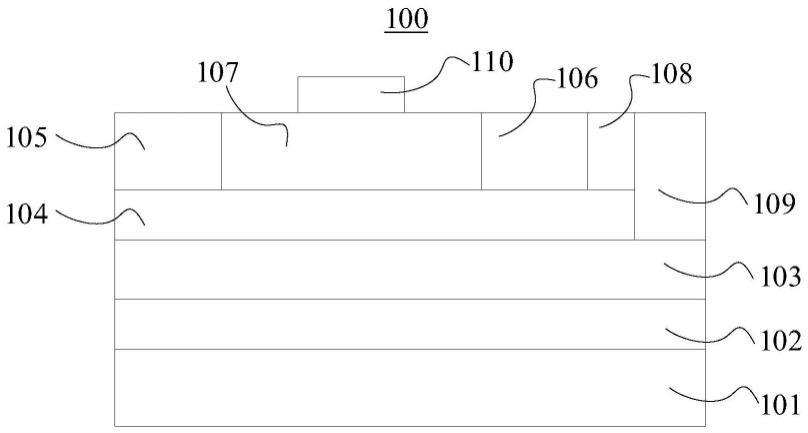

20.图1示出了本发明较佳实施例提供的一种单结晶体管结构的结构示意 图;

21.图2示出了本发明较佳实施例中单结晶体管结构进行仿真验证中的不 同漏极电压时,漏极电流与栅极电压的变化关系示意图;

22.图3示出了本发明较佳实施例中单结晶体管结构进行仿真验证中的不 同硅膜厚度下,栅极电流和栅极电压的变化关系示意图;

23.图4示出了本发明较佳实施例中单结晶体管结构进行仿真验证中的不 同背栅电压下,栅极电流与栅极电压的变化关系示意图;

24.图5示出了本发明较佳实施例中单结晶体管结构进行仿真验证中的不 同背栅电压下,漏极电流与栅极电压的变化关系示意图。

25.图标:100-单结晶体管结构;101-衬底;102-第一氧化层;103-配置层; 104-第二氧化层;105-第一高掺杂区;106-第二高掺杂区;107-沟道区;108

‑ꢀ

隔离区;109-引出部;110-第三高掺杂区。

具体实施方式

26.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只 是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对 公知结构和技术的描述,以避免不必要地混淆本公开的概念。

27.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是 按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略 了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、 位置关系仅是示例性的,实际中可能由

(technology computer aided design,半导体工艺以及器件模拟工具)仿真 软件对本实施例的单结晶体管进行仿真,仿真结果如图2-5所示。

36.图2示出了不同漏极电压vd时,漏极电流与栅极电压(i

d-vg)的变化 关系示意图,其中,tsi表示顶层硅膜的厚度;symbols表示进行0-3v漏 极电压扫描时,图示中得到的符号结果;lines表示进行3-0v漏极电压扫 描时,图示中得到的线性结果,其他图示相同不再赘述。结果显示,随着vd的升高,迟滞效应沿vg正向移动。

37.图3示出了不同硅膜厚度下,栅极电流和栅极电压(i

g-vg)的变化关 系示意图。结果显示,随着硅膜厚度的降低,迟滞效应沿vg正向移动。

38.图4示出了不同背栅电压(v

bg

)下,栅极电流与栅极电压(i

d-vg)的 变化关系示意图;图5示出了不同背栅电压(v

bg

)下,漏极电流与栅极电 压(i

d-vg)的变化关系示意图。结果显示,随着正向背偏电压的升高,迟 滞效应沿vg正向移动。

39.从上述的仿真结果可以看出,采用本实施例中的单结晶体管结构100, 在独立背栅上施加背栅电压能够有效的对器件性能进行改变,并且具有大 范围的调整空间。

40.本实施例的一种单结晶体管结构100,包括:衬底101、第一氧化层102、 配置层103、第二氧化层104、第一高掺杂区105、沟道区107以及第二高 掺杂区106。第一氧化层102形成在衬底101上;配置层103形成在第一氧 化层102上;第二氧化层104形成在配置层103上,第一高掺杂区105、沟 道区107以及第二高掺杂区106均形成在第二氧化层104上,沟道区107 位于第一高掺杂区105和第二高掺杂区106之间并欧姆接触。该单结晶体 管结构100具有独立的配置层103形成的背栅结构,并且该配置层103位 于第一氧化层102和第二氧化层104之间可有效的屏蔽外界干扰,在配置 层103接入偏置电压之后,可实现大范围的电压调节,实现对单结晶体管 结构100的器件性能进行灵活调整,以应用于不同应用环境。

41.进一步的,针对上述的单结晶体管结构,本实施例还提供了一种单结 晶体管结构的制造方法,所述方法包括:

42.步骤s10:提供衬底;

43.步骤s20:在所述衬底上方依次形成所述第一氧化层、所述配置层、所 述第二氧化层以及顶层硅膜;

44.步骤s30:对所述顶层硅膜的第一区域、第二区域和第三区域分别进行 掺杂,形成第一高掺杂区、沟道区以及第二高掺杂区;

45.步骤s40:在所述配置层上方形成与所述配置层连接的引出部;其中, 所述引出部从所述第一高掺杂区和/或所述第二高掺杂区远离所述沟道区的 位置延伸出;

46.步骤s50:在所述引出部与所述第一高掺杂区和/或所述第二高掺杂区 之间形成隔离区。

47.通过上述步骤s10-s50可以制造出单结晶体管结构,其中的引出部可 用于进行对配置层施加偏置电压,实现对单结晶体管结构性能的调节。需 要说明的是,该方法中每个步骤的实现过程可采用现有的半导体工艺进行, 本实施例中不再赘述。

48.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于 本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精 神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明 的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。