半导体构造及制作方法

1.[相关申请]

[0002]

本技术主张优先于在2021年3月19日提出申请且名称为“半导体构造及制造方法(semiconductor arrangement and method of manufacture)”的美国临时申请63/163,494,所述美国临时申请并入本技术供参考。

技术领域

[0003]

本公开涉及一种半导体构造及其制作方法。

背景技术:

[0004]

随着半导体行业在追求更高的装置密度、更高的性能及更低的成本方面已进展到纳米技术工艺节点,来自制造问题及设计问题二者的挑战已促成三维设计(例如垂直晶体管)的发展。

技术实现要素:

[0005]

根据一些实施例,一种半导体构造包括形成在半导体层之上的第一源极垫。第一纳米片材与所述第一源极垫接触。栅极垫与所述第一纳米片材相邻。第一漏极垫位于所述栅极垫之上且与所述第一纳米片材接触。后侧内连线位于所述栅极垫及所述第一源极垫下方。

[0006]

根据一些实施例,一种形成半导体构造的方法包括在半导体层之上形成第一源极垫。形成与所述第一源极垫接触的第一纳米片材。形成与所述第一纳米片材相邻的栅极垫。形成位于所述栅极垫之上且与所述第一纳米片材接触的第一漏极垫。在所述栅极垫及所述第一源极垫下方形成后侧内连线。形成与所述后侧内连线、所述第一源极垫或所述栅极垫中的至少一者接触的第一后侧接触件。

[0007]

根据一些实施例,一种半导体构造包括第一单位胞元及第二单位胞元。所述第一单位胞元包括:第一垂直n型晶体管,具有第一n型源极垫;第一垂直p型晶体管,具有第一p型源极垫;以及第一后侧接触件,与所述第一p型源极垫接触。所述第二单位胞元包括:第二垂直n型晶体管,具有第二n型源极垫;以及第二垂直p型晶体管,具有第二p型源极垫。第一后侧导电线与所述第一后侧接触件接触。后侧内连线位于所述第一单位胞元及所述第二单位胞元下方。

附图说明

[0008]

结合附图阅读以下详细说明,会理解本公开的各个方面。应理解,图式所示元件和/或结构未必按比例绘制。因此,为使论述清晰起见,可任意增大和/或减小各种特征的尺寸。

[0009]

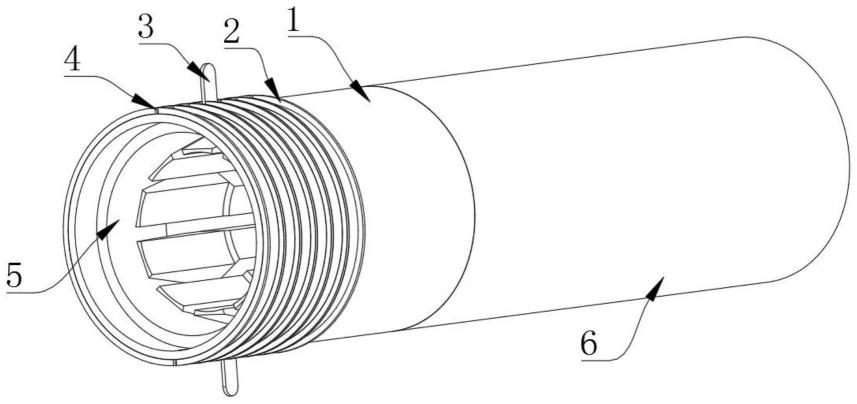

图1是根据一些实施例的半导体构造的剖视图。

[0010]

图2是根据一些实施例的半导体构造的俯视图。

definition,od)区。有源区的一些部分可各自用作相应晶体管的源极结构或漏极结构,且有源区的一些部分可各自用作相应晶体管的导电沟道。

[0021]

在使用不同的后侧连接方案的情况下,可使用相同的基本垂直装置构造来实施不同的装置,例如反相器、与非装置、与或反相器、与装置或其他合适的装置。

[0022]

参照图1及图2,分别提供根据一些实施例的包括单位胞元105的半导体构造100的剖视图及俯视图。为易于例示,在图2中并未示出单位胞元105的所有特征。在一些实施例中,单位胞元105包括形成在半导体层115之上的第一晶体管110n及第二晶体管110p。在一些实施例中,半导体层115是衬底的一部分,所述衬底包括外延层、单晶半导体材料(例如但不限于si、ge、sige、ingaas、gaas、insb、gap、gasb、inalas、gasbp、gaassb或inp中的至少一者)、绝缘体上硅(silicon-on-insulator,soi)结构、晶片或由晶片形成的管芯中的至少一者。在一些实施例中,半导体层115包括结晶硅或其他合适的材料中的至少一者。半导体层115的其他结构和/或配置也处于本公开的范围内。

[0023]

在一些实施例中,第一晶体管110n包括n型晶体管,所述n型晶体管包括源极垫120n、漏极垫125n及在源极垫120n与漏极垫125n之间延伸的纳米片材130n。在一些实施例中,源极垫120n及漏极垫125n经n型杂质(例如磷、砷、锑或一些其他合适的n型掺杂剂)掺杂。在一些实施例中,纳米片材130n未经掺杂或经p型杂质(例如硼、三氟化硼、镓、铟或一些其他合适的p型掺杂剂)掺杂。

[0024]

在一些实施例中,第二晶体管110p包括p型晶体管,所述p型晶体管包括源极垫120p、漏极垫125p及在源极垫120p与漏极垫125p之间延伸的纳米片材130p。在一些实施例中,源极垫120p及漏极垫125p经p型杂质掺杂。在一些实施例中,纳米片材130p未经掺杂或经n型杂质掺杂。

[0025]

在一些实施例中,通过对半导体层115进行刻蚀以界定源极垫120n、120p来形成源极垫120n、120p。在一些实施例中,在半导体层115之上沉积或生长半导体材料层且将所述半导体材料层图案化以界定源极垫120n、120p。在一些实施例中,根据适当的导电类型实行一个或多个掩模植入工艺以将杂质植入到源极垫120n、120p中。

[0026]

在一些实施例中,浅沟槽隔离(shallow trench isolation,sti)结构135位于源极垫120n、120p之间。在一些实施例中,通过在半导体层之上形成至少一个掩模层来形成sti结构135,以形成源极垫120n、120p(其可与半导体层115相同或可为不同的半导体层,例如形成在半导体层115之上的第二半导体层)。在一些实施例中,掩模层包括氧化物材料层及位于氧化物材料层之上的氮化物材料层和/或一个或多个其他合适的层。移除所述至少一个掩模层中的至少一些掩模层,以对用作模板的刻蚀掩模进行界定,以对用于形成源极垫120n、120p的半导体层进行刻蚀,从而形成沟槽。在沟槽中形成介电材料以界定sti结构135。在一些实施例中,sti结构135包括多个层,例如氧化物衬垫、形成在氧化物衬垫之上的氮化物衬垫、形成在氮化物衬垫之上的氧化物填充材料和/或其他合适的材料。

[0027]

在一些实施例中,使用高密度等离子体(high density plasma,hdp)工艺形成填充材料(例如氧化物填充材料)。hdp工艺使用包括硅烷(sih4)、氧气、氩气或其他合适气体中的至少一者的前驱气体。hdp工艺包括沉积组件及溅镀组件,所述沉积组件在界定沟槽的表面上形成材料,所述溅镀组件移除或重新定位所沉积的材料。沉积对溅镀比率取决于沉积组件期间所采用的气体比率。根据一些实施例,氩气及氧气充当溅镀源且气体比率的特

定值是基于沟槽的高宽比(aspect ratio)来确定。在形成填充材料之后,实行退火工艺以将填充材料致密化。在一些实施例中,sti结构135产生压缩应力。sti结构135的其他结构和/或配置也处于本公开的范围内。

[0028]

在一些实施例中,通过在源极垫120n、120p之上形成半导体材料层并实行图案化刻蚀工艺以形成纳米片材130n、130p来形成纳米片材130n、130p。在一些实施例中,在图案化刻蚀工艺之前根据适当的导电类型实行一个或多个掩模植入工艺,以将杂质植入到用于形成纳米片材130n、130p的半导体层中。在一些实施例中,纳米片材130n、130p具有矩形的垂直横截面及水平横截面。在一些实施例中,纳米片材130n、130p是具有椭圆形的水平横截面的支柱。如本文中所使用的用语纳米片材旨在囊括具有矩形的水平横截面或椭圆形的水平横截面的结构。

[0029]

在一些实施例中,在纳米片材130n、130p周围形成有栅极垫140。根据一些实施例,通过以下方式形成栅极垫140:在源极垫120n、120p及sti结构135之上形成底部介电层145并在底部介电层145之上单独或组合地形成包括牺牲栅极介电层、牺牲层(例如多晶硅)及硬掩模层(例如氮化硅、二氧化硅或一些其他合适的硬掩模材料)的牺牲栅极结构。在一些实施例中,对应于将形成的栅极垫140的图案实行图案化工艺以将硬掩模层图案化,且使用经图案化的硬掩模层实行刻蚀工艺以对牺牲层及牺牲栅极介电层进行刻蚀,从而界定栅极垫140。在一些实施例中,硬掩模层的剩余部分在刻蚀工艺之后剩余的牺牲层的一些部分之上形成顶盖层。

[0030]

在一些实施例中,栅极垫140是通过使用替换栅极介电层及替换栅极电极(未单独示出)替换在开始时形成的牺牲栅极电极层及牺牲栅极电极而形成的替换栅极结构。在一些实施例中,在替换牺牲材料之前,在栅极垫140之上形成介电层150。在一些实施例中,介电层150包括一层或多层低介电常数(low-k)介电材料。低介电常数介电材料具有低于约3.9的介电常数值(介电常数)。一些低介电常数介电材料具有低于约3.5的介电常数值且可具有低于约2.5的介电常数值。在一些实施例中,低介电常数层被进一步表征或分类为超低介电常数(ultra low-k,ulk)、特低介电常数(extra low-k,elk)或极低介电常数(extreme low-k,xlk),其中所述分类一般是基于介电常数值。举例来说,ulk一般是指具有介于约2.7到约2.4之间的介电常数值的材料,elk一般是指具有介于约2.3到约2.0之间的介电常数值的材料,且xlk一般是指具有小于约2.0的介电常数值的材料。在一些实施例中,介电层150包括二氧化硅和/或其他合适的材料。在一些实施例中,用于介电层150的材料包括si、o、c或h中的至少一者,例如sicoh、sioc、经氧掺杂sic(oxygen-doped sic,odc)、经氮掺杂sic(nitrogen-doped sic,ndc)、等离子体增强型氧化物(plasma-enhanced oxide,peox)和/或其他合适的材料。可对介电层150使用例如聚合物等有机材料。在一些实施例中,介电层150包括一层或多层含碳材料、有机硅酸盐玻璃、含成孔剂材料和/或其他合适的材料。在一些实施例中,介电层150包括氮。在一些实施例中,通过使用例如以下技术中的至少一者形成介电层150:原子层沉积(atomic layer deposition,ald)、化学气相沉积(chemical vapor deposition,cvd)、低压化学气相沉积(low pressure cvd,lpcvd)、原子层化学气相沉积(atomic layer chemical vapor deposition,alcvd)、超高真空化学气相沉积(ultrahigh vacuum cvd,uhvcvd)、减压化学气相沉积(reduced pressure cvd,rpcvd)、等离子体增强型化学气相沉积(plasma enhanced cvd,pecvd)或其他合适的技术。在一些实

施例中,介电层150包括一个或多个层,所述一个或多个层中的至少一些层可具有相同的材料成分。在一些实施例中,存在介电层150的一个或多个层,所述一个或多个层中的至少一些层可具有相同的材料成分。介电层150的其他结构和/或配置也处于本公开的范围内。

[0031]

在栅极垫140是替换栅极结构的一些实施例中,替换栅极介电层包括高介电常数介电材料。如本文中所使用的用语“高介电常数介电质”是指具有大于或等于约3.9的介电常数k的材料,3.9是sio2的介电常数值。高介电常数介电层的材料可包括任何合适的材料。高介电常数介电层的材料的实例包括但不限于al2o3、hfo2、zro2、la2o3、tio2、srtio3、laalo3、y2o3、al2o

x

ny、hfo

x

ny、zro

x

ny、la2o

x

ny、tio

x

ny、srtio

x

ny、laalo

x

ny、y2o

x

ny、sion、sin

x

、其硅酸盐、其合金和/或其他合适的材料。x的每一值独立地从0.5到3,且y的每一值独立地从0到2。在一些实施例中,栅极介电层包括通过在工艺流程中的不同阶段处将半导体构造100暴露到氧气而形成的原生氧化物层,从而使得在被暴露出的表面上形成二氧化硅。在一些实施例中,在原生氧化物之上形成由介电材料(例如包括二氧化硅)、高介电常数介电材料和/或其他合适的材料形成的附加层,以形成栅极介电层。

[0032]

在其中栅极垫140是替换栅极结构的一些实施例中,替换栅极电极包括阻挡层、一个或多个功函数材料层、晶种层、金属填充层和/或其他合适的层。在一些实施例中,金属填充层包括钨、铝、铜、钴和/或其他合适的材料。在一些实施例中,通过ald、物理气相沉积(physical vapor deposition,pvd)、cvd、lpcvd、alcvd、uhvcvd、rpcvd、分子束外延(molecular beam epitaxy,mbe)或其他合适的技术中的至少一者形成栅极介电层和/或包括栅极电极的所述一个或多个层。在一些实施例中,使替换栅电极凹陷且在栅极垫140之上形成顶部介电层155。

[0033]

在一些实施例中,通过以下方式形成漏极垫125n、125p:在栅极垫140及介电层150之上形成半导体材料层并将所述半导体材料层图案化以界定漏极垫125n、125p。在一些实施例中,根据适当的导电类型实行一个或多个掩模植入工艺以将杂质植入在漏极垫125n、125p中。在一些实施例中,在用于界定漏极垫125n、125p的图案化工艺期间,使栅极垫140的中心部分140ct相对于端部部分140e凹陷。在一些实施例中,在介电层150、漏极垫125n、125p以及栅极垫140的中心部分140ct之上形成有介电层160。在一些实施例中,介电层160的材料与介电层150的材料相同。

[0034]

在一些实施例中,在介电层160中形成有漏极接触件165n、165p及栅极接触件170。以任意数目的方式(例如通过单镶嵌工艺、双镶嵌工艺、沟槽硅化物工艺和/或其他合适的技术)形成漏极接触件165n、165p及栅极接触件170。在一些实施例中,漏极接触件165n、165p及栅极接触件170包括阻挡层、晶种层、金属填充层和/或其他合适的层。在一些实施例中,金属填充层包括钨、铝、铜、钴和/或其他合适的材料。漏极接触件165n、165p及栅极接触件170的其他结构和/或配置也处于本公开的范围内。

[0035]

在一些实施例中,在介电层160、漏极接触件165n、165p及栅极接触件170之上形成有介电层180,且在介电层180中形成有导电线185a、185b、185c、185d、185e。在一些实施例中,介电层180及导电线185a、185b、185c、185d、185e界定半导体构造100的第一金属化层(m0)。在一些实施例中,介电层180包括与介电层150或介电层160相同的材料。在一些实施例中,在介电层180及导电线185a、185b、185c、185d、185e上方形成有附加的金属化层,以在单位胞元105与形成在半导体构造100中的其他装置之间形成各种内连。举例来说,如图2中

所示,在后续金属化层中的导电线185a、185b、185c、185d、185e之上形成有位于第二金属化层(m1)中的导电线187a、187b。在一些实施例中,导电线185a、185b、185c、185d、185e中的所选择的导电线包括用于向单位胞元105提供供应电压v

dd

和/或参考电压v

ss

的电力轨(power rail)。

[0036]

在一些实施例中,通过后侧接触件190a、190b、后侧导电线195a、195b及后侧内连线200来实现对单位胞元105的后侧连接。在一些实施例中,侧壁间隔件205a、205b位于后侧导电线195a、195b与半导体层115之间。在一些实施例中,在半导体层115下方形成有介电层210,且在介电层210中形成的沟槽中形成有后侧导电线195a、195b。在一些实施例中,介电层210及后侧导电线195a、195b界定第一后侧金属化层(backside m0)。在一些实施例中,间隔件层215位于后侧内连线200与源极垫120p、120n之间。在一些实施例中,顶盖层220a、220b位于后侧接触件190a、190b与后侧导电线195a、195b之间。在一些实施例中,顶盖层225位于后侧内连线200与后侧导电线195a、195b之间。在一些实施例中,顶盖层220a、220b、225包括介电材料(包括例如硅、氮、碳、氧等材料)或其他合适的材料。顶盖层220a、220b的材料不同于顶盖层225的材料。

[0037]

图1中所示的单位胞元105可被配置或与其他单位胞元105组合来实现不同的逻辑装置。可基于正在被实施的特定逻辑装置提供后侧内连的不同配置。举例来说,在一些实施例中,后侧导电线195a、195b包括用于向单位胞元105提供供应电压v

dd

和/或参考电压v

ss

的电力轨。可省略顶盖层220a、220b中的一者或两者,以将后侧导电线195a、195b连接到相应的后侧接触件190a、190b。可省略后侧接触件190a、190b中的一者或多者。可局部地移除侧壁间隔件205a、205b中的一者或多者,以将后侧接触件190a、190b中的一者或两者连接到后侧内连线200。在一些实施例中,提供后侧栅极接触件230以将后侧内连线200连接到栅极垫140。

[0038]

参照图1,在一些实施例中,纳米片材130n、130p的垂直高度为约12.5nm到60nm,被称为纳米片材高度(nanosheet height,nsh)。漏极接触件165n、165p的垂直高度为nsh的约0.5到2.5倍。漏极垫125n、125p的垂直高度为nsh的约1到3倍。源极垫120n、120p的垂直高度为nsh的约1到2倍。栅极接触件170的垂直高度为约为漏极接触件165n、165p的高度、漏极垫125n、125p的高度以及0.7到1倍的nsh的总和。

[0039]

参照图2,在一些实施例中,m0导电线185a、185b、185c、185d、185e的节距为约20nm。m1导电线187a、187b的节距为约26nm。单位胞元105的高度h为m0节距的约5倍或100nm,且单位胞元105的宽度w为m1节距的约2倍或52nm。

[0040]

图3a到图3i是根据一些实施例的半导体构造在各种制造阶段的剖视图。图3a到图3i示出上面倒置形成有半导体构造100,以使得能够形成后侧内连的半导体晶片。

[0041]

参照图3a,根据一些实施例,在半导体层115中形成接触开口300a、300b,且在半导体层115之上及接触开口300a、300b中形成介电层305。在一些实施例中,通过在半导体层115之上形成至少一个掩模层来形成接触开口300a、300b。在一些实施例中,掩模层包括位于半导体层115之上的氧化物材料层及位于氧化物材料层之上的氮化物材料层和/或一个或多个其他合适的层。移除掩模层中的至少一些以界定用作模板的刻蚀掩模,以对半导体层115进行刻蚀来形成接触开口300a、300b。在一些实施例中,介电层305包括二氧化硅、低介电常数材料和/或其他合适的材料。在一些实施例中,用于介电层305的材料包括si、o、c

或h中的至少一者,例如sicoh、sioc、odc、ndc、peox和/或其他合适的材料。可对介电层305使用例如聚合物等有机材料。在一些实施例中,介电层305包括一层或多层含碳材料、有机硅酸盐玻璃、含成孔剂材料和/或其他合适的材料。在一些实施例中,介电层305包括氮。在一些实施例中,通过使用例如cvd、pecvd、lpcvd、alcvd、旋转涂布(spin-on technology)技术或其他合适的技术中的至少一者来形成介电层305。在一些实施例中,介电层305包括一个或多个层,所述一个或多个层中的至少一些层可具有相同的材料成分。在一些实施例中,存在介电层305的一个或多个层,所述一个或多个层中的至少一些层可具有相同的材料成分。介电层305的其他结构和/或配置也处于本公开的范围内。

[0042]

参照图3b,根据一些实施例,使介电层305凹陷且在接触开口300a、300b的顶部部分中形成顶盖层310。在一些实施例中,实行平坦化工艺以移除介电层305的位于半导体层115之上的部分,且实行刻蚀工艺以使介电层305凹陷。在一些实施例中,顶盖层310包括介电材料(包括例如硅、氮、碳、氧等材料)或其他合适的材料。在一些实施例中,通过在半导体层115之上及凹槽中沉积材料层并实行平坦化工艺以移除材料层的位于凹槽外部的部分来形成顶盖层310。介电层305的剩余部分界定虚设接触件315a、315b。

[0043]

参照图3c,根据一些实施例,移除半导体层115且在顶盖层310及介电层150之上形成间隔件层320。在一些实施例中,实行刻蚀工艺以移除半导体层115。在一些实施例中,通过cvd、pecvd、lpcvd、alcvd、旋转涂布技术或其他合适的技术中的至少一者来形成间隔件层320。在一些实施例中,间隔件层320包括介电材料(包括例如硅、氮、碳、氧等材料)或其他合适的材料。在一些实施例中,间隔件层320的材料成分不同于顶盖层310的材料成分,以便于选择性地移除间隔件层320而不移除顶盖层310。

[0044]

参照图3d,根据一些实施例,在间隔件层320之上形成掩模325,且移除间隔件层320的被掩模325暴露出的部分。掩模325包括开口330,开口330暴露出虚设接触件315b的一部分。在一些实施例中,掩模325包括光刻胶或一些其他合适的掩模材料。在一些实施例中,使用掩模325作为刻蚀模板来实行刻蚀工艺,以移除间隔件层320的一部分并暴露出虚设接触件315b的一部分。在一些实施例中,实行斜角刻蚀工艺(angled etch process)以在将间隔件层320的下部部分留在源极垫120p之上的适当位置的同时移除间隔件层320的上部部分,以提供电隔离。在一些实施例中,使用被称为倒角(chamfering)的工艺在开口330的底部中提供牺牲材料以在刻蚀工艺期间保护间隔件层320的底部部分,且随后移除牺牲材料。

[0045]

参照图3e,根据一些实施例,移除掩模325且在虚设接触件315a、315b之间形成后侧内连线200。后侧内连线335a、335b与相邻的单位胞元105(未在图1中示出)相关联。在一些实施例中,后侧内连线200、335a、335b包括钨、铝、铜、钴和/或其他合适的材料。在一些实施例中,通过在虚设接触件315a、315b之上沉积导电材料并将导电材料平坦化以移除导电材料的位于顶盖层310之上的部分来形成后侧内连线200、335a、335b。在一些实施例中,平坦化工艺还移除间隔件层320的位于顶盖层310之上的部分。

[0046]

参照图3f,根据一些实施例,在后侧内连线200、335a、335b之上形成掩模340,且移除虚设接触件315b之上的顶盖层310。掩模340包括开口345,开口345暴露出顶盖层310及虚设接触件315b。在一些实施例中,掩模340包括光刻胶或一些其他合适的掩模材料。在一些实施例中,使用掩模340作为刻蚀模板来实行刻蚀工艺,以移除顶盖层310及虚设接触件315b,从而界定凹槽350。

[0047]

参照图3g,根据一些实施例,移除掩模340且在凹槽350中形成后侧接触件190b。在一些实施例中,后侧接触件190b包括钨、铝、铜、钴和/或其他合适的材料。在一些实施例中,通过在凹槽350中沉积导电材料并将所述导电材料平坦化以移除导电材料的位于凹槽350外部的部分来形成后侧接触件190b。

[0048]

参照图3h,根据一些实施例,使后侧接触件190b及后侧内连线200、335a、335b凹陷以界定凹槽,且在凹槽中形成顶盖层355。在一些实施例中,实行刻蚀工艺以使后侧接触件190b及后侧内连线200、335a、335b凹陷。在一些实施例中,顶盖层355包括与顶盖层310相同的材料。在一些实施例中,通过在后侧接触件190b及后侧内连线200、335a、335b之上沉积材料层并实行平坦化工艺以移除材料层的位于后侧接触件190b及后侧内连线200、335a、335b中的凹槽外部的部分来形成顶盖层355。

[0049]

参照图3i,根据一些实施例,形成介电层210及后侧导电线195a、195b。在一些实施例中,后侧导电线195b通过顶盖层355而与后侧接触件190b及后侧内连线200、335a、335b隔离。后侧接触件190b与后侧内连线200接触。

[0050]

在一些实施例中,由于在由单位胞元105创建的逻辑装置中未形成后侧接触件,因此虚设接触件315a保持在原处。在一些实施例中,使用图3d到图3i所示步骤来替换虚设接触件315a、315b二者,使得后侧内连线200与后侧接触件190b以及通过移除间隔件层320的一部分并替换虚设接触件315a而形成的后侧接触件(未示出)接触。

[0051]

图4a到图4e是根据一些实施例的半导体构造在各种制造阶段的剖视图。图4a到图4e示出上面倒置形成有半导体构造100以使得能够形成后侧内连的半导体晶片。图4a到图4e所示处理从图3c中所示的半导体构造100开始。

[0052]

参照图4a,根据一些实施例,形成与虚设接触件315a、315b相邻的后侧内连线200、335a、335b。在一些实施例中,后侧内连线200、335a、335b包括钨、铝、铜、钴和/或其他合适的材料。在一些实施例中,通过在虚设接触件315a、315b之上沉积导电材料并将所述导电材料平坦化以移除导电材料的位于顶盖层310之上的部分来形成后侧内连线200、335a、335b。在一些实施例中,平坦化工艺还移除间隔件层320的位于顶盖层310之上的部分。

[0053]

参照图4b,根据一些实施例,移除虚设接触件315a、315b。在一些实施例中,实行刻蚀工艺以移除顶盖层310及虚设接触件315a、315b,从而界定凹槽350a、350b。

[0054]

参照图4c,根据一些实施例,在凹槽350a、350b中形成后侧接触件190a、190b。在一些实施例中,后侧接触件190a、190b包括钨、铝、铜、钴和/或其他合适的材料。在一些实施例中,通过在凹槽350a、350b中沉积导电材料并将所述导电材料平坦化以移除导电材料的位于凹槽350a、350b外部的部分来形成后侧接触件190a、190b。

[0055]

参照图4d,根据一些实施例,使后侧接触件190a、190b及后侧内连线200、335a、335b凹陷且形成顶盖层355。在一些实施例中,实行刻蚀工艺以使后侧接触件190a、190b及后侧内连线200、335a、335b凹陷。在一些实施例中,顶盖层355包括与顶盖层310相同的材料。在一些实施例中,通过在后侧接触件190a、190b及后侧内连线200、335a、335b之上沉积材料层并实行平坦化工艺以移除材料层的位于后侧接触件190a、190b及后侧内连线200、335a、335b中的凹槽外部的部分来形成顶盖层355。

[0056]

参照图4e,根据一些实施例,形成介电层210及后侧导电线195a、195b。在一些实施例中,后侧接触件190a、190b与后侧导电线195a、195b及源极垫120n、120p接触,且后侧内连

线200通过间隔件层320而与后侧接触件190a、190b隔离。

[0057]

图5a到图5d是根据一些实施例的半导体构造在各种制造阶段的剖视图。图5a到图5d示出上面倒置形成有半导体构造100以使得能够形成后侧内连的半导体晶片。图5a到图5d所示处理从图3c中所示的半导体构造100开始。

[0058]

参照图5a,根据一些实施例,在间隔件层320及虚设接触件315a、315b之上形成掩模360,且移除间隔件层320的一些部分、sti结构135的一些部分及底部介电层145的一些部分。在一些实施例中,掩模360包括位于sti结构135之上的开口365。在一些实施例中,掩模360包括光刻胶或一些其他合适的掩模材料。在一些实施例中,使用掩模360作为刻蚀模板来实行刻蚀工艺,以移除间隔件层320的所述一些部分、sti结构135的所述一些部分及底部介电层145的所述一些部分,从而界定栅极接触开口370。

[0059]

参照图5b,根据一些实施例,移除掩模340,在栅极接触开口370中形成后侧栅极接触件230,且形成与虚设接触件315a、315b相邻的后侧内连线200、335a、335b。在一些实施例中,后侧栅极接触件230及后侧内连线200、335a、335b包括钨、铝、铜、钴和/或其他合适的材料。在一些实施例中,通过在栅极接触开口370中且与虚设接触件315a、315b相邻地沉积导电材料并将所述导电材料平坦化以移除导电材料的位于虚设接触件315a、315b之上的部分来形成后侧栅极接触件230及后侧内连线200、335a、335b。在一些实施例中,平坦化工艺还移除间隔件层320的位于顶盖层310之上的部分。

[0060]

参照图5c,根据一些实施例,使后侧内连线200、335a、335b凹陷且形成顶盖层355。在一些实施例中,实行刻蚀工艺以使后侧内连线200、335a、335b凹陷。在一些实施例中,顶盖层355包括与顶盖层310相同的材料。在一些实施例中,通过在后侧内连线200、335a、335b之上沉积材料层并实行平坦化工艺以移除材料层的位于后侧内连线200、335a、335b中的凹槽外部的部分来形成顶盖层355。在一些实施例中,由于在由单位胞元105创建的逻辑装置中未形成后侧接触件,因此虚设接触件315a、315b保持在原处。

[0061]

参照图5d,根据一些实施例,形成介电层210及后侧导电线195a、195b。在一些实施例中,后侧内连线200通过顶盖层355而与后侧导电线195a、195b隔离。在一些实施例中,后侧栅极接触件230与后侧内连线200接触。

[0062]

可采用图3a到图3i、图4a到图4e及图5a到图5d所示工艺提供不同的后侧内连,以支持各种逻辑装置配置。

[0063]

参照图6a及图6b,根据一些实施例,提供反相器600的电路图及简化等轴视图。在一些实施例中,使用一个单位胞元105来实施反相器600。为易于例示而简化图6b中所示的单位胞元105。根据图4a到图4e中所示的处理,后侧接触件190a、190b连接到后侧导电线195a、195b,且分别经由后侧导电线195a、195b向单位胞元105提供参考电压v

ss

及供应电压v

dd

。导电线185a、185d在上覆的金属化层中连接到彼此。经由导电线185c接收反相器600的输入in,且反相器600的输出out存在于内连的导电线185a、185d上。

[0064]

参照图7a及图7b,根据一些实施例,提供双输入(two-input)与非闸700的电路图及简化等轴视图。在一些实施例中,使用两个单位胞元105a、105b来实施双输入与非闸700。为易于例示而简化图7b中所示的单位胞元105a、105b。单位胞元105a、105b具有共享源极垫120n及共享漏极垫125p。根据图4a到图4e中所示的处理,单位胞元105b的后侧接触件190b2及单位胞元105a的后侧接触件(不可见)连接到后侧导电线195b,且经由后侧导电线195b向

单位胞元105a、105b提供供应电压v

dd

。导电线185a1经由漏极接触件165n向单位胞元105a的漏极垫125n1提供参考电压v

ss

。导电线185b2经由漏极接触件165n2耦合到第二单位胞元105b的漏极垫125n2。导电线185d2经由漏极接触件165p2耦合到漏极垫125p。导电线185b2、185d2在上覆的金属化层中连接到彼此。导电线185c1经由栅极接触件170a连接到单位胞元105a的栅极垫140a。导电线185c2经由栅极接触件170b连接到单位胞元105b的栅极垫140b。经由导电线185c1、185c2接收双输入与非闸700的输入in1、in2,且在内连的导电线185b2、185d2上提供双输入与非闸700的输出out。

[0065]

参照图8a及图8b,根据一些实施例,提供双输入与或反相器800的电路图及简化等轴视图。在一些实施例中,使用四个单位胞元105a、105b、105c、105d来实施与或反相器800。为易于例示而简化图8b中所示的单位胞元105a、105b、105c、105d。单位胞元105a、105b具有共享源极垫120n1,且单位胞元105b、105c具有共享源极垫120n3。单位胞元105a、105b、105c、105d具有共享源极垫120p1。单位胞元105b、105c具有共享漏极垫125n2。单位胞元105c、105d具有共享漏极垫125p3。导电线185a1经由漏极接触件165n1向单位胞元105a的漏极垫125n1提供参考电压v

ss

。导电线185e1经由漏极接触件165p1、165p2向单位胞元105a、105b的漏极垫125p1、125p2提供供应电压v

dd

。导电线185a4经由漏极接触件165n4向单位胞元105d的漏极垫125n4提供参考电压v

ss

。导电线185b3经由漏极接触件165n3连接到漏极垫125n2。导电线185d3经由漏极接触件165p连接到漏极垫125p3。导电线185b3、185d3在上覆的金属化层中内连。导电线185c1经由栅极接触件170a连接到单位胞元105a的栅极垫140a。导电线185c2经由栅极接触件170b连接到单位胞元105b的栅极垫140b。导电线185c3经由栅极接触件170c连接到单位胞元105c的栅极垫140c。导电线185c4经由栅极接触件170d连接到单位胞元105d的栅极垫140d。经由导电线185c1、185c2接收与或反相器800的输入in1、in2,且与或反相器800的输出out存在于内连的导电线185b3、185d3上。

[0066]

参照图9a及图9b,根据一些实施例,提供双输入与闸900的电路图及简化等轴视图。在一些实施例中,使用三个单位胞元105a、105b、105c来实施与闸900。为易于例示而简化图8b中所示的单位胞元105a、105b、105c。单位胞元105a、105b具有共享源极垫120p1。单位胞元105a、105b具有共享漏极垫125n1。根据图4a到图4e中所示的处理,单位胞元105a、105c的后侧接触件190a1、190a3连接到后侧导电线195a,且经由后侧导电线195a向单位胞元105a、105c的源极垫120n1、120n3提供参考电压v

ss

。根据图4a到图4e中所示的处理,单位胞元105c的后侧接触件190b3连接到后侧导电线195b,且经由后侧导电线195b向单位胞元105c的源极垫120p3提供供应电压v

dd

。导电线185e1经由漏极接触件165p1、165p2向单位胞元105a、105b的漏极垫125p1、125p2提供供应电压v

dd

。根据图3a到图3i所示处理,单位胞元105b的后侧接触件190a2及后侧接触件190b(不可见)连接到后侧内连线200。根据图5a到图5d所示处理,单位胞元105c的栅极垫140c经由后侧栅极接触件230c连接到后侧内连线200。导电线185b3、185d3分别经由漏极接触件165n3、165p3连接到漏极垫125n3、125p3。导电线185b3、185d3在上覆的金属化层中连接到彼此。导电线185c1经由栅极接触件170a连接到单位胞元105a的栅极垫140a。导电线185c2经由栅极接触件170b连接到单位胞元105b的栅极垫140b。经由导电线185c1、185c2接收与闸900的输入in1、in2,且在内连的导电线185b3、185d3上提供与闸900的输出out。

[0067]

图10是示出根据一些实施例的形成半导体构造100的方法1000的流程图。在操作

1002处,在半导体层115之上形成第一源极垫120n、120p。在操作1004处,形成与第一源极垫120n、120p接触的第一纳米片材130n、130p。在操作1006处,形成与第一纳米片材130n、130p相邻的栅极垫140。在操作1008处,形成位于栅极垫140之上且与第一纳米片材130n、130p接触的第一漏极垫125n、125p。在操作1010处,在栅极垫140及第一源极垫120n、120p下方形成后侧内连线200。在操作1012处,形成与后侧内连线200、第一源极垫120n、120p或栅极垫140中的至少一者接触的第一后侧接触件190a、190b。

[0068]

又一实施例涉及一种包括处理器可执行指令的计算机可读介质,所述处理器可执行指令被配置成实施本文中所呈现的技术中的一种或多种。示例性计算机可读介质在图11中示出,其中实施例1100包括上面编码有计算机可读数据1104的计算机可读介质1102(例如,可记录光盘(compact disk-recordable,cd-r)、可记录数字视频光盘(digital video disk-recordable,dvd-r)、闪存驱动机、硬盘驱动机的盘片等)。此计算机可读数据1104又包括被配置成根据本文中所述的原理中的一者或多者而运作的一组处理器可执行计算机指令1106。在一些实施例1100中,处理器可执行计算机指令1106被配置成实行方法1108,例如前述方法中的至少一些。在一些实施例中,处理器可执行计算机指令1106被配置成实施系统,例如前述系统中的至少一些。所属领域中的普通技术人员可设计出被配置成根据本文中所呈现的技术而运作的许多此种计算机可读介质。

[0069]

图12及以下论述提供对适合于实施本文中所述规定中的一者或多者的实施例的计算环境的简要大体说明。图12所示操作环境仅为合适的操作环境的一个实例,且并不旨在对操作环境的使用范围或功能提出任何限制。示例性计算装置包括但不限于个人计算机、服务器计算机、手持式或膝上型装置、移动装置(例如移动电话、个人数字助理(personal digital assistant,pda)、介质播放器等)、多处理器系统、消费型电子产品、小型计算机、大型计算机、包括上述系统或装置中任一者的分布式计算环境等。

[0070]

尽管不是必需的,然而实施例是在由一个或多个计算装置执行“计算机可读指令”的一般上下文中阐述的。计算机可读指令可通过计算机可读介质(以下论述)被分布。计算机可读指令可被实施为实行特定任务或实施特定抽象数据类型的程序模块,例如函数、对象、应用编程接口(application programming interface,api)、数据结构等。通常,可根据需要在各种环境中组合或分布计算机可读指令的功能。

[0071]

图12绘示出包括用于实施本文中所提供的一些实施例的计算装置1202的系统1200的实例。在一些配置中,计算装置1202包括至少一个处理单元1204及存储器1206。视计算装置的确切配置及类型而定,存储器1206可为易失性的(例如(举例来说)随机存取存储器(random access-memory,ram))、非易失性的(例如(举例来说)惟读存储器(read-only memory,rom)、闪存等)或两者的一些组合。此种配置在图12中由虚线1208示出。

[0072]

在一些实施例中,计算装置1202可包括附加特征和/或功能。举例来说,计算装置1202还可包括附加存储装置(例如,可装卸和/或不可装卸的),包括但不限于磁性存储装置、光学存储装置等。此种附加存储装置在图12中由存储装置1210示出。在一些实施例中,实施本文中所提供的一个或多个实施例的计算机可读指令可位于存储装置1210中。存储装置1210还可存储实施操作系统、应用程序等的其他计算机可读指令。举例来说,计算机可读指令可被加载到存储器1206中,以便由处理单元1204执行。

[0073]

本文中所使用的用语“计算机可读介质”包括计算机存储介质。计算机存储介质包

括以任何方法或技术实施以用于存储例如计算机可读指令或其他数据等信息的易失性及非易失性、可装卸及不可装卸的介质。存储器1206及存储装置1210是计算机存储介质的实例。计算机存储介质包括但不限于ram、rom、电可擦除可编程惟读存储器(electrically erasable programmable read only memory,eeprom)、闪存或其他存储器技术、光盘惟读存储器(compact disc-read only memory,cd-rom)、数字多用光盘(digital versatile disk,dvd)或其他光学存储装置、盒式磁带、磁带、磁盘存储装置或其他磁性存储装置、或者可用于存储所期望信息并可由计算装置1202存取的任何其他介质。任何此种计算机存储介质均可为计算装置1202的一部分。

[0074]

在一些实施例中,计算装置1202包括使得计算装置1202能够与其他装置进行通信的通信界面1212或多个通信界面。通信界面1212可包括但不限于调制解调器、网络界面卡(network interface card,nic)、集成网络界面、射频发射器/接收器、红外端口、通用串行总线(universal serial bus,usb)连接或用于将计算装置1202连接到其他计算装置的其他界面。通信界面1212可包括有线连接或无线连接。通信界面1212可传送和/或接收通信介质。

[0075]

用语“计算机可读介质”可包括通信介质。通信介质通常以例如载波或其他传输机制等“经调制数据信号”来实施计算机可读指令或其他数据,且包括任何信息递送介质。用语“经调制数据信号”可包括如下信号:其特性中的一者或多者已以使得在信号中编码信息的方式被设定或改变。

[0076]

计算装置1202可包括输入装置1214,例如键盘、鼠标、笔、话音输入装置、触摸输入装置、红外照相机、视频输入装置和/或任何其他合适的输入装置。在计算装置1202中也可包括输出装置1216,例如一个或多个显示器、扬声器、打印机和/或任何其他合适的输出装置。输入装置1214及输出装置1216可经由有线连接、无线连接或其任意组合连接到计算装置1202。在一些实施例中,来自另一计算装置的输入装置或输出装置可用作计算装置1202的输入装置1214或输出装置1216。

[0077]

计算装置[1202的各组件可通过例如总线等各种内连件来连接。此类内连件可包括外围组件互连(peripheral component interconnect,pci)(例如快速pci(pci express))、usb、火线(firewire)(ieee 1394)、光学总线结构等。在一些实施例中,计算装置1202的各组件可通过网络进行内连。举例来说,存储器1206可由位于通过网络内连的不同物理位置中的多个物理存储器单元构成。

[0078]

所属领域中的技术人员将认识到,用于存储计算机可读指令的存储装置可跨网络而分布。举例来说,可经由网络1220存取的计算装置1218可存储实施本文中所提供的一个或多个实施例的计算机可读指令。计算装置1202可存取计算装置1218并下载计算机可读指令的一部分或全部以供执行。作为另一选择,计算装置1202可视需要下载多条计算机可读指令,或者一些指令可在计算装置1202处执行,而一些指令可在计算装置1218处执行。

[0079]

在一些实施例中,采用纳米片材130n、130p及后侧内连的单位胞元105的垂直架构使得能够提供顶侧或后侧接触件以向单位胞元105施加电源电压或栅极电压。单位胞元105下方的后侧内连线200使得能够实现对单位胞元105进行内连的灵活性。后侧内连线200可在单位胞元105中连接到晶体管110n、110p的源极垫120n或栅极垫140。与finfet装置相比,单位胞元中的垂直纳米线装置提供减小的电容。在使用不同的后侧连接方案的情况下,可

使用相同的基本垂直装置构造来实施不同的装置,例如反相器、与非装置、与或反相器、与装置或其他合适的装置。

[0080]

根据一些实施例,一种半导体构造包括形成在半导体层之上的第一源极垫。第一纳米片材与所述第一源极垫接触。栅极垫与所述第一纳米片材相邻。第一漏极垫位于所述栅极垫之上且与所述第一纳米片材接触。后侧内连线位于所述栅极垫及所述第一源极垫下方。

[0081]

在一些实施例中,半导体构造还包括:第一后侧接触件,与所述第一源极垫接触。在一些实施例中,所述第一后侧接触件与所述第一源极垫及所述后侧内连线接触。在一些实施例中,半导体构造还包括:第一后侧导电线,与所述第一后侧接触件接触;以及介电材料,位于所述第一后侧接触件与所述后侧内连线之间。在一些实施例中,半导体构造还包括:后侧栅极接触件,与所述后侧内连线及所述栅极垫接触。在一些实施例中,半导体构造还包括:第二源极垫,形成在所述半导体层之上;第二纳米片材,与所述第二源极垫接触;以及第二漏极垫,位于所述栅极垫之上且与所述第二纳米片材接触,其中:所述栅极垫与所述第二纳米片材相邻。在一些实施例中,半导体构造还包括:第一后侧接触件,与所述第一源极垫接触;以及第二后侧接触件,与所述第二源极垫接触。在一些实施例中,所述第一后侧接触件及所述第二后侧接触件与所述后侧内连线接触。在一些实施例中,半导体构造还包括:后侧栅极接触件,与所述后侧内连线及所述栅极垫接触。在一些实施例中,半导体构造还包括:后侧栅极接触件,与所述后侧内连线及所述栅极垫接触。

[0082]

根据一些实施例,一种形成半导体构造的方法包括在半导体层之上形成第一源极垫。形成与所述第一源极垫接触的第一纳米片材。形成与所述第一纳米片材相邻的栅极垫。形成位于所述栅极垫之上且与所述第一纳米片材接触的第一漏极垫。在所述栅极垫及所述第一源极垫下方形成后侧内连线。形成与所述后侧内连线、所述第一源极垫或所述栅极垫中的至少一者接触的第一后侧接触件。

[0083]

在一些实施例中,形成半导体构造的方法还包括:在所述第一后侧接触件下方形成第一后侧导电线。在一些实施例中,形成半导体构造的方法还包括:在所述第一后侧导电线与所述第一后侧接触件之间形成顶盖层,其中:所述第一后侧接触件与所述后侧内连线接触。在一些实施例中,形成半导体构造的方法还包括:在所述第一后侧接触件与所述后侧内连线之间形成间隔件层,其中:所述第一后侧接触件与所述第一后侧导电线接触。在一些实施例中,形成所述第一后侧接触件包括:形成将所述后侧内连线连接到所述栅极垫的所述第一后侧接触件。

[0084]

根据一些实施例,一种半导体构造包括第一单位胞元及第二单位胞元。所述第一单位胞元包括:第一垂直n型晶体管,具有第一n型源极垫;第一垂直p型晶体管,具有第一p型源极垫;以及第一后侧接触件,与所述第一p型源极垫接触。所述第二单位胞元包括:第二垂直n型晶体管,具有第二n型源极垫;以及第二垂直p型晶体管,具有第二p型源极垫。第一后侧导电线与所述第一后侧接触件接触。后侧内连线位于所述第一单位胞元及所述第二单位胞元下方。

[0085]

在一些实施例中,半导体构造还包括:共享p型漏极垫,位于所述第一垂直p型晶体管及所述第二垂直p型晶体管中;以及共享n型漏极垫,位于所述第一垂直n型晶体管及所述第二垂直n型晶体管中。在一些实施例中,半导体构造还包括:第三单位胞元,包括:第三垂

直n型晶体管,具有第三n型源极垫;第三垂直p型晶体管,具有第三p型源极垫;以及第二后侧接触件,与所述第三p型源极垫接触;以及第二后侧导电线,与所述第二后侧接触件接触,其中:所述第一单位胞元包括与所述第一n型源极垫及所述第二后侧导电线接触的第三后侧接触件。在一些实施例中,所述第一单位胞元包括:第一n型漏极垫,位于所述第一垂直n型晶体管中;第一p型漏极垫,位于所述第一垂直p型晶体管中;栅极垫,位于所述第一n型源极垫与所述第一n型漏极垫之间以及所述第一p型源极垫与所述第一p型漏极垫之间;以及后侧栅极接触件,使所述后侧内连线与所述栅极垫接触,且所述第二单位胞元包括与所述第二n型源极垫及所述后侧内连线接触的第四后侧接触件。在一些实施例中,所述第二单位胞元包括:第一n型漏极垫,位于所述第二垂直n型晶体管中;第一p型漏极垫,位于所述第二垂直p型晶体管中;栅极垫,位于所述第二n型源极垫与所述第一n型漏极垫之间以及所述第二p型源极垫与所述第一p型漏极垫之间;以及栅极接触件,位于所述栅极垫之上且连接到输入端子。

[0086]

以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,他们可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下对其作出各种改变、替代及变更。

[0087]

尽管已采用结构特征或方法动作专用的语言阐述了本主题,然而应理解,所附权利要求书的主题未必仅限于上述具体特征或动作。确切来说,上述具体特征及动作是作为实施权利要求中的至少一些权利要求的示例性形式而公开的。

[0088]

本文中提供实施例的各种操作。阐述一些或所有所述操作时的次序不应被理解为暗示这些操作必须依照次序进行。应理解,替代次序也具有本说明的益处。此外,应理解,并非所有操作均必须存在于本文中所提供的每一实施例中。另外,应理解,在一些实施例中,并非所有操作均是必要的。

[0089]

应理解,在一些实施例中,例如出于简明及易于理解的目的,本文中所绘示的层、特征、元件等是以相对于彼此的特定尺寸(例如,结构尺寸或取向)进行示出,且所述层、特征、元件等的实际尺寸实质上不同于本文中所示出的尺寸。另外,存在用于形成本文中所述层、区、特征、元件等的各种技术,例如刻蚀技术、平坦化技术、植入技术、掺杂技术、旋转涂布技术、溅镀技术、生长技术或沉积技术(例如化学气相沉积(cvd))中的至少一者。

[0090]

另外,本文中使用“示例性”来指充当实例、例子、示例等,而未必指为有利的。本技术中所使用的“或”旨在意指包括性“或”而不是指排他性“或”。另外,除非另有指明或从上下文中清楚地表明指单数形式,否则本技术及所附权利要求书中使用的“一(a及an)”一般被视为意指“一个或多个”。另外,a及b中的至少一者和/或类似表述一般意指a或b、或a与b两者。此外,就使用“包括(includes)”、“具有(having、has)”、“带有(with)”或其变型而言,此种用语旨在以相似于用语“包括(comprising)”的方式表示包括性。另外,除非另有指明,否则“第一(first)”、“第二(second)”等并不旨在暗示时间方面、空间方面、次序等。确切来说,此种用语仅用作特征、元件、物项等的识别符、名称等。举例来说,第一元件及第二元件一般对应于元件a及元件b、或两个不同元件、或两个相同元件、或同一元件。

[0091]

另外,尽管已针对一种或多种实施方案示出并阐述了本公开,然而所属领域中的普通技术人员在阅读及理解本说明书及附图后将想到等效更改及修改形式。本公开包括所有此种修改及更改形式,且仅受限于以上权利要求书的范围。特别对于由上述组件实行的各种功能而言,用于阐述此种组件的用语旨在对应于实行所述组件的指定功能的任何组件(例如,功能上等效)(除非另有指示),即使所述组件在结构上不与所公开的结构等效。另外,尽管可能仅相对于若干实施方案中的一种实施方案公开了本公开的特定特征,然而在对于任何给定或特定应用而言可能为期望的及有利的时,此种特征可与其他实施方案的一种或多种其他特征进行组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。