1.本公开涉及半导体光元件及其制造方法。

背景技术:

2.已知有将由化合物半导体形成且具有光学增益的半导体元件接合于形成导波路的soi(silicon on insulator,绝缘体上硅芯片)衬底(硅光子)等衬底的技术(例如非专利文献1)。

3.现有技术文献

4.非专利文献

5.非专利文献1:amin abbasi et al.“43gb/s nrz-ook direct modulation of aheterogeneously integrated inp/si dfb laser”journal of lightwave technology,vol.35,no.6.march 15,2017

技术实现要素:

6.发明所要解决的问题

7.通过在衬底上形成导波路以及衍射光栅等,将具有光学增益的半导体元件接合于衍射光栅之上,从而形成分布反馈型(dfb:distributed feedback)激光元件。

8.若在衬底与半导体元件之间设置树脂等中间层,则热阻上升。伴随着动作而温度容易上升,特性劣化。另一方面,若不设置中间层而将衬底与半导体元件直接接合,则由于在衬底设置有槽,因此衬底与半导体元件的接触面积变小,接合强度降低。另外,由于衬底的槽被空气充满,因此热阻变高。因此,本公开的目的在于提供一种能够降低热阻并且提高接合强度的半导体光元件及其制造方法。

9.用于解决问题的方法

10.本公开所涉及的半导体光元件具备:衬底,其包含硅且在当俯视时各自不同的区域具有平台、导波路以及衍射光栅;以及半导体元件,其接合于所述衍射光栅以及所述平台之上,所述半导体元件与所述衬底的上表面接触,由iii-v族化合物半导体形成,并具有光学增益,所述导波路在所述导波路的延伸方向上与所述衍射光栅光耦合,所述平台在与所述导波路的延伸方向交叉的方向上位于所述导波路以及所述衍射光栅的两侧,所述衬底在所述平台与所述导波路之间具有槽,所述衍射光栅在与所述导波路的延伸方向交叉的方向上与所述平台连续。

11.本公开涉及的半导体光元件的制造方法具备:准备包含硅且在当俯视时各自不同的区域形成有平台、导波路以及衍射光栅的衬底的准备工序;以及将由iii-v族化合物半导体形成且具有光学增益的半导体元件接合于所述衬底中的所述衍射光栅以及所述平台之上的接合工序,在所述接合工序中,所述半导体元件与所述衬底的上表面接触,所述导波路在所述导波路的延伸方向上与所述衍射光栅光耦合,所述平台在与所述导波路的延伸方向交叉的方向上位于所述导波路以及所述衍射光栅的两侧,所述衬底在所述平台与所述导波

路之间具有槽,所述衍射光栅在与所述导波路的延伸方向交叉的方向上与所述平台连续。

12.发明效果

13.根据本公开,能够实现热阻的降低以及接合强度的提高。

附图说明

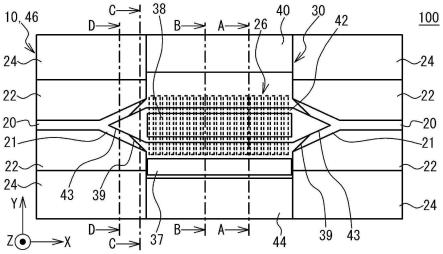

14.图1a是对实施方式所涉及的半导体光元件进行示例的俯视图。

15.图1b是沿图1a的线a-a的剖视图。

16.图1c是沿图1a的线b-b的剖视图。

17.图1d是沿图1a的线c-c的剖视图。

18.图1e是沿图1a的线d-d的剖视图。

19.图2是对衬底进行示例的俯视图。

20.图3a是对光的强度进行示例的图。

21.图3b是对光的强度进行示例的图。

22.图4a是对光的强度进行示例的图。

23.图4b是对光的强度进行示例的图。

24.图5是对半导体元件的制造方法进行示例的剖视图。

25.图6a是对半导体光元件的制造方法进行示例的俯视图。

26.图6b是沿图6a的线a-a的剖视图。

27.图6c是沿图6a的线b-b的剖视图。

28.图6d是沿图6a的线c-c的剖视图。

29.图6e是沿图6a的线d-d的剖视图。

30.图7a是对半导体光元件的制造方法进行示例的俯视图。

31.图7b是沿图7a的线a-a的剖视图。

32.图7c是沿图7a的线b-b的剖视图。

33.图7d是沿图7a的线c-c的剖视图。

34.图7e是沿图7a的线d-d的剖视图。

35.图8a是对半导体光元件的制造方法进行示例的俯视图。

36.图8b是沿图8a的线a-a的剖视图。

37.图8c是沿图8a的线b-b的剖视图。

38.图8d是沿图8a的线c-c的剖视图。

39.图8e是沿图8a的线d-d的剖视图。

40.图9a是对半导体光元件的制造方法进行示例的俯视图。

41.图9b是沿图9a的线a-a的剖视图。

42.图9c是沿图9a的线b-b的剖视图。

43.图9d是沿图9a的线c-c的剖视图。

44.图9e是沿图9a的线d-d的剖视图。

45.图10a是对比较例所涉及的半导体光学元件进行示例的俯视图。

46.图10b是沿图10a的线a-a的剖视图。

47.图10c是沿图10a的线b-b的剖视图。

48.图10d是沿图10a的线c-c的剖视图。

49.图10e是沿图10a的线d-d的剖视图。

50.图11是对衬底进行示例的俯视图。

51.附图标记说明

52.10、10r、12、50:衬底;14:sio2层;16:si层;20:导波路;21、39、43:锥部;22:槽;24:平台;24a:突出部;26:衍射光栅;26a:凹部;26b:凸部;30:半导体元件;32、35;包覆层;34:有源层;36:接触层;37、38:电极;40、42、44:台面;46:绝缘膜;100、100r:半导体光元件。

具体实施方式

53.[本公开的实施方式的说明]

[0054]

首先,罗列本公开的实施方式的内容来进行说明。

[0055]

本公开的一个方式为,(1)半导体光元件具备:衬底,其包含硅且在当俯视时各自不同的区域具有平台、导波路以及衍射光栅;以及半导体元件,其接合于所述衍射光栅以及所述平台之上,所述半导体元件与所述衬底的上表面接触,由iii-v族化合物半导体形成,并具有光学增益,所述导波路在所述导波路的延伸方向上与所述衍射光栅光耦合,所述平台在与所述导波路的延伸方向交叉的方向上位于所述导波路以及所述衍射光栅的两侧,所述衬底在所述平台与所述导波路之间具有槽,所述衍射光栅在与所述导波路的延伸方向交叉的方向上与所述平台连续。通过增大半导体元件与衬底的接触面积,接合强度得以提高,并且热阻得以降低。

[0056]

(2)可以是,所述衬底具有硅层,所述平台、所述导波路以及所述衍射光栅设置于所述硅层,所述衍射光栅包含沿所述导波路的延伸方向周期性地配置于所述硅层的凹部和凸部,所述平台的上表面与所述衍射光栅的凸部的上表面形成平面。由于半导体元件与平台以及凸部接触,因此接合强度得以提高,并且热阻得以降低。

[0057]

(3)可以是,所述半导体元件具有从所述衬底侧起依次层叠的第一包覆层、有源层以及第二包覆层,并且在所述衍射光栅之上具有从所述衬底侧向与所述衬底相反的一侧突出的第一台面,所述第一台面包含第二包覆层。由于半导体元件具有第一台面,因此向半导体元件的光限制变强,向衬底的光的泄漏被抑制,能够进行光的模式控制。

[0058]

(4)可以是,所述衍射光栅在与所述导波路的延伸方向交叉的方向上的宽度比所述第一台面的宽度大。由于平台与第一台面分离,因此向半导体元件的光限制变强,向衬底的光的泄漏被抑制。

[0059]

(5)可以是,所述半导体元件在所述衬底的所述平台之上具有从所述衬底侧向与所述衬底相反的一侧突出的第二台面,所述第二台面包含第二包覆层,并且从所述第一台面分离,所述半导体元件具备:第一电极,其与所述第一包覆层电连接;以及第二电极,其与所述第一台面的所述第二包覆层电连接。向位于第一台面的下部的有源层的光限制变强,向衬底的光的泄漏被抑制,能够进行光的模式控制。

[0060]

(6)可以是,所述平台具有朝向所述衍射光栅突出的突出部,所述衍射光栅与所述突出部连接。由于半导体元件与衬底的接触面积增加,因此接合强度得以提高,热阻得以降低。

[0061]

(7)可以是,所述导波路具有从所述衍射光栅侧朝向与所述衍射光栅相反的一侧

为尖头的第一锥部。能够抑制光的损失。

[0062]

(8)可以是,所述半导体元件具有从所述衍射光栅侧朝向所述导波路侧为尖头的第二锥部。半导体元件与衬底的光耦合变强,能够抑制光的损失。

[0063]

(9)半导体光元件的制造方法具备:准备包含硅且在当俯视时各自不同的区域形成有平台、导波路以及衍射光栅的衬底的准备工序;以及将由iii-v族化合物半导体形成且具有光学增益的半导体元件接合于所述衬底中的所述衍射光栅以及所述平台之上的接合工序,在所述接合工序中,所述半导体元件与所述衬底的上表面接触,所述导波路在所述导波路的延伸方向上与所述衍射光栅光耦合,所述平台在与所述导波路的延伸方向交叉的方向上位于所述导波路以及所述衍射光栅的两侧,所述衬底在所述平台与所述导波路之间具有槽,所述衍射光栅在与所述导波路的延伸方向交叉的方向上与所述平台连续。通过增大半导体元件与衬底的接触面积,接合强度得以提高,并且热阻得以降低。

[0064]

[本公开的实施方式的详细内容]

[0065]

对本公开的实施方式所涉及的半导体光元件及其制造方法的具体例,在以下一边参照附图一边进行说明。此外,本公开不限于这些示例,而由权利要求书进行表示,以期包含在与权利要求书等同的意思以及范围内的全部的变更。

[0066]

图1a是对实施方式所涉及的半导体光元件100进行示例的俯视图。图1b是沿图1a的线a-a的剖视图。图1c是沿图1a的线b-b的剖视图。图1d是沿图1a的线c-c的剖视图。图1e是沿图1a的线d-d的剖视图。图2是对衬底10进行示例的俯视图。如图1a至图1e所示,半导体光元件100是具有衬底10以及半导体元件30的混合型的dfb激光元件。衬底10以及半导体元件30的表面用绝缘膜46覆盖,但在图1a中对绝缘膜46进行透视。

[0067]

(衬底)

[0068]

如图1b至图1e所示,衬底10是具有依次层叠了的硅(si)的衬底12、氧化硅(sio2)层14、以及si层16而成的soi衬底。衬底10的端面施加了涂布以防止光的反射。衬底10具有沿x轴方向延伸的边以及沿y轴方向延伸的边。将衬底12、sio2层14以及si层16的层叠方向设为z轴方向。x轴方向、y轴方向以及z轴方向相互正交。

[0069]

如图1a以及图2所示,在衬底10的si层16设置有导波路20、槽22、平台24以及衍射光栅26。从衬底10的x轴方向的一端侧到另一端侧,导波路20、衍射光栅26以及导波路20依次排列。导波路20沿x轴方向延伸,与衍射光栅26光耦合,并在与衍射光栅26的连接部分具有锥部21。锥部21在衍射光栅26侧宽度较宽,沿x轴方向朝向与衍射光栅26相反的一侧为尖头。

[0070]

在si层16中的被两个锥部21夹着的部分,沿x轴方向设置有周期性的凹凸。凹部26a内的空气与si层的凸部26b具有折射率差,多个凹凸作为衍射光栅26而发挥功能。换言之,衍射光栅26包含多个凹部26a以及多个凸部26b。在衍射光栅26上接合有半导体元件30。

[0071]

在导波路20以及锥部21的y轴方向的两侧设置有槽22。在槽22的外侧设置有平台24。导波路20的上表面、锥部21的上表面、平台24的上表面以及凸部26b的上表面在z轴方向上位于同一高度,形成同一平面。

[0072]

槽22以及凹部26a在z轴方向上延伸至si层16的中途。槽22以及凹部26a的底面由si层16形成,在z轴方向上位于同一高度,位于比平台24以及凸部26b的上表面靠下的位置。如图1d以及图1e所示,槽22的内侧被绝缘膜46覆盖。凹部26a的内侧为空洞。

[0073]

如图1a以及图2所示,在衍射光栅26与平台24之间未设置槽22。衍射光栅26在y轴方向上到达平台24,与平台24连续。详细而言,平台24在y轴方向上与衍射光栅26对置的位置具有突出部24a。突出部24a向y轴方向突出,与衍射光栅26连接。衍射光栅26的凸部26b延伸至平台24的突出部24a,与突出部24a一起形成衬底10的上表面。衍射光栅26的凹部26a的y轴方向的两端到达突出部24a。

[0074]

图1c以及图2所示的衍射光栅26在y轴方向上的宽度w1例如为5μm。衍射光栅26的宽度w1是指凹部26a以及凸部26b的宽度。图2所示的导波路20的宽度w2例如为0.5μm。槽22的宽度w3例如为5μm。

[0075]

(半导体元件)

[0076]

图1a所示的半导体元件30是由iii-v族化合物半导体形成的具有脊形台面(ridge mesa)结构的发光元件。如图1b至图1e所示,半导体元件30具有从衬底10侧起依次在z轴方向上层叠的包覆层32(第一包覆层)、有源层34、包覆层35(第二包覆层)以及接触层36。

[0077]

包覆层32例如由n型磷化铟(n-inp)形成。包覆层35例如由p-inp形成。接触层36例如由p型的铟镓砷(p-ingaas)等形成。有源层34包含例如由非掺杂的镓铟砷磷(i-gainasp)形成的多个阱层和势垒层,且具有多量子阱结构(mqw:multi quantum well)。也可以在有源层34与包覆层32之间、以及有源层34与包覆层35之间设置间隔层。半导体元件30可以在包覆层32之上包含未图示的n型接触层,也可以由上述以外的半导体形成。

[0078]

半导体元件30具有三个台面40、42以及44。台面40、42以及44在y轴方向上依次排列,并彼此分离。台面40以及台面44(第二台面)位于平台24之上。台面42(第一台面)位于衍射光栅26之上。如图1b以及图1c所示,台面40、42以及44由包覆层35以及接触层36形成,以半导体元件30的下表面(包覆层32)为基准,向与衬底10相反的方向(z轴方向上侧)突出。包覆层32以及有源层34从台面40延伸到台面44。

[0079]

图1c所示的台面42的宽度w4比衍射光栅26的宽度w1小,例如为2.5μm。如图1a所示,台面40以及44的x轴方向的长度例如与衍射光栅26的长度同程度。台面42的x轴方向的长度比衍射光栅26、台面40以及44的长度大。台面42具有两个锥部43。锥部43在x轴方向上比衍射光栅26突出,朝向与衍射光栅26相反的一侧为尖头。

[0080]

如图1a、图1d以及图1e所示,包覆层32以及有源层34具有两个锥部39。锥部39位于衬底10的锥部21之上,在x轴方向上比衍射光栅26突出,朝向与衍射光栅26相反的一侧为尖头。如图1d至图1e所示,锥部43位于锥部39之上。如图1e所示,在尖头的前端侧,锥部43与锥部39合流。锥部39以及43的x轴方向的长度比衬底10的锥部21的长度小。

[0081]

如图1b至图1e所示,绝缘膜46覆盖台面40、42以及44的上表面及侧面,覆盖台面间的有源层34的上表面,覆盖衬底10的上表面。绝缘膜46例如由氧化硅(sio2)等形成。绝缘膜46的折射率低于si层16的折射率以及台面42的折射率。因此,绝缘膜46作为将光限制在台面42以及导波路20中的包覆层而发挥功能。电极37是n型电极。如图1b所示,电极37设置在台面42与台面44之间,通过绝缘膜46的开口部与包覆层32电连接。电极37具有由金、锗以及ni的合金(augeni)形成的欧姆电极层、以及由au形成的配线层。电极38是p型电极。电极38设置于台面42的上表面,通过绝缘膜46的开口部与接触层36以及包覆层35电连接。电极38具有由钛、铂以及金的层叠体(ti/pt/au)形成的欧姆电极层、以及由au形成的配线层。

[0082]

半导体元件30具有光学增益。通过对电极37和38施加电压,电流流过台面42,载流

子被注入有源层34。由此台面42的下部的有源层34发光。半导体元件30的有源层34与衬底10的衍射光栅26进行倏逝(evanescent)光耦合。由半导体元件30生成的光在衍射光栅26、锥部21以及导波路20中传输,从衬底10的端面朝向半导体光元件100的外部射出。

[0083]

由于在导波路20的两侧设置有槽22,因此通过由si层构成的导波路20与槽22内的绝缘膜46(或空气)的折射率差,能够将光强力地限制于导波路20。另一方面,在衍射光栅26的两侧未设置槽22,衍射光栅26与平台24的突出部24a连接。半导体元件30具有在衍射光栅26上具有台面42的脊形台面结构。通过脊形台面结构,光被较强地限制在位于台面42的下部的有源层34的区域,难以泄漏到衬底10的si层16。由此,能够得到所希望的光的模式分布。

[0084]

图3a至图4b是对光的强度进行示例的图。图3a以及图3b表示如图1b那样半导体元件30与衍射光栅26的凸部26b排列的截面中的光的强度。图4a以及图4b表示如图1c那样半导体元件30与衍射光栅26的凹部26a排列的截面中的光的强度。图3a至图4b的纵轴表示光的强度。

[0085]

图3a以及图4a的横轴表示y轴方向上的位置。即,图3a以及图4a表示y轴方向的光的分布。y轴方向的5μm的位置与台面42中的宽度方向的中央对应。如图3a以及图4a所示,光分布在4~6μm的范围内,在该范围内存在光的强度的峰值。光集中于y轴方向的中央,即集中于台面42。衍射光栅26的宽度优选大于图3a以及图4a所示的y轴方向的光的分布的范围。具体而言,衍射光栅26的宽度为台面42的宽度的2倍以上。

[0086]

图3b以及图4b的横轴表示包含台面42的z轴方向上的位置。即,图3b以及图4b表示z轴方向的光的分布。如图3b所示,在包含凸部26b的截面中,光具有两个峰值p1以及p2。峰值p1出现在衬底10的si层16。峰值p2比峰值p1大,出现在台面42的有源层34。如图4b所示,在包含凹部26a的截面中,光仅在有源层34显示峰值。

[0087]

在包含凸部26b的截面中,向有源层34的光限制系数为3.74%。光主要分布于有源层34,但如图3b所示,光也向si层16泄漏。在包含凹部26a的截面中,光限制系数为5.77%。如图4a以及图4b所示,与包含凸部26b的截面相比,在包含凹部26a的截面中光被有源层34较强地限制。通过在衍射光栅26上交替地配置多个凹部26a以及凸部26b并对脊形台面结构的半导体元件30进行接合,接合部分整体的光限制系数为4%以上。在此,整体的光限制系数是指,使用包含凹部26a的截面中的光限制系数和包含凸部26b的截面中的光限制系数,考虑凹部26a和凸部26b的x轴方向的长度的分配(衍射光栅的占空比)而计算出的平均的光限制系数。

[0088]

(制造方法)

[0089]

在半导体光元件100的制造中,例如使用两个晶圆。两个晶圆是指:用于制造soi衬底的晶圆(衬底10)以及用于制造半导体元件30的iii-v族化合物半导体的晶圆。

[0090]

晶圆状态的soi衬底具有多个供半导体光元件100形成的区域。在soi衬底的该区域分别形成图2所示的导波路20、锥部21、槽22、平台24以及衍射光栅26。通过电子束绘制等形成抗蚀剂图案,用抗蚀剂覆盖成为导波路20、锥部21、平台24以及衍射光栅26的凸部26b的部分。对si层16中的从抗蚀剂露出的部分进行干法蚀刻,从而形成槽22以及凹部26a。在由抗蚀剂保护的部分形成导波路20、锥部21、平台24以及凸部26b(参照图2)。

[0091]

图5是对半导体元件30的制造方法进行示例的剖视图。例如通过有机金属气相生

长法(omvpe:organo metallic vapor phase epitaxy)等,在inp的衬底50上依次外延生长接触层36、包覆层35、有源层34以及包覆层32。对晶圆进行切割,形成多个半导体元件30。在切割的时刻,在半导体元件30未形成台面40、42以及44、电极、锥部43。

[0092]

图6a、图7a、图8a以及图9a是对半导体光元件100的制造方法进行示例的俯视图,表示半导体元件30向衬底10的接合以后的工序。图6b、图7b、图8b以及图9b分别图示了沿对应的俯视图的线a-a的截面。图6c、图7c、图8c以及图9c分别图示沿对应的俯视图的线b-b的截面。图6d、图7d、图8d以及图9d分别图示了沿对应的俯视图的线c-c的截面。图6e、图7e、图8e以及图9e分别图示了沿对应的俯视图的线d-d的截面。

[0093]

例如通过等离子体照射等使半导体元件30的包覆层32的表面以及衬底10的si层16的表面活化。如图6a至图6e所示,使半导体元件30与si层16接触,将半导体元件30接合于衬底10的上表面。在半导体元件30的面与衬底10的上表面之间不设置粘接剂等而使表面彼此接触。接合后,通过湿法蚀刻除去半导体元件30的衬底50,使接触层36的表面露出。湿法蚀刻的蚀刻剂流入衬底10的槽22,但被衍射光栅26的凸部26b以及平台24阻挡。半导体元件30的下表面(包覆层32)的蚀刻得以抑制。

[0094]

如图7a至图7e所示,在半导体元件30形成台面40、42以及44。在半导体元件30的表面形成掩模用的绝缘膜,在绝缘膜之上形成抗蚀剂图案。通过使用抗蚀剂图案对绝缘膜进行干法蚀刻,形成具有开口的绝缘膜掩模(未图示)。除去抗蚀剂图案。接触层36的一部分从绝缘膜掩模的开口露出。对半导体元件30中的露出的部分进行干法蚀刻,形成台面40、42以及44。用绝缘膜掩模覆盖的部分未被蚀刻。在蚀刻之后除去绝缘膜掩模。

[0095]

如图8a至图8e所示,在半导体元件30形成锥部39。在半导体元件30形成掩模用的绝缘膜,在绝缘膜之上形成抗蚀剂图案。通过使用抗蚀剂图案对绝缘膜进行干法蚀刻,形成绝缘膜掩模(未图示)。除去抗蚀剂图案。有源层34的一部分从绝缘膜掩模露出。通过对半导体元件30中的从绝缘膜掩模露出的部分进行干法蚀刻,形成锥部39。如图8b以及图8c所示,台面40、42以及44、台面间的部分未被蚀刻。如图8d以及图8e所示,衬底10的上表面的一部分露出。除去绝缘膜掩模。

[0096]

如图9a至图9e所示,例如通过化学气相生长法(cvd:chemical vapor deposition)等,在衬底10以及半导体元件30的表面形成绝缘膜46。在台面42上以及台面42与台面44之间的绝缘膜46设置开口部,例如通过真空蒸镀等设置图1a等所示的电极38以及37。通过以上的工序,形成图1a~图1e所示的半导体光元件100。

[0097]

(比较例)

[0098]

图10a是对比较例所涉及的半导体光元件100r进行示例的俯视图。图10b至图10e分别是沿图10a的线a-a、线b-b、线c-c、线d-d的剖视图。图11是对衬底10r进行示例的俯视图。半导体光元件100r具有衬底10r来代替衬底10。

[0099]

如图10a至图11所示,在衬底10r的衍射光栅26的两侧设置有槽22。平台24不具有突出部24a,而从衍射光栅26分离。为了增强向半导体元件30的有源层34的光的限制,优选扩大槽22。但是,由于在衍射光栅26与平台24之间存在槽22,因此半导体元件30与衬底10r的接触面积变小,接合强度降低。

[0100]

在比较例中,从半导体元件30露出的槽22的内侧由绝缘膜46覆盖。另一方面,位于半导体元件30之下的槽22的内侧由空气填满。空气的热传导率比衬底10r的热传导率低,因

此热阻上升。由于伴随着动作的温度上升,半导体光元件100r的特性劣化。在对半导体元件30的衬底进行湿法蚀刻时,蚀刻剂侵入槽22,有时从下侧对半导体元件30进行蚀刻。通过蚀刻,半导体元件30容易剥离。

[0101]

根据本实施方式,衬底10具有平台24、衍射光栅26以及导波路20。如图2所示,通过在导波路20的两侧具有槽22,能够将光较强地限制在导波路20中。另一方面,在衍射光栅26的两侧未设置槽22。衍射光栅26在y轴方向上延伸至平台24,与平台24连接。半导体元件30接合于平台24及衍射光栅26之上,与衬底10的表面接触。与比较例相比,半导体元件30与衬底10的接触面积变大,因此接合强度变高。

[0102]

如图1b至图1e所示,在半导体元件30与衬底10之间不存在粘接剂等,半导体元件30的下表面与衬底10的上表面接触。与使用树脂等粘接剂的情况相比,热阻得以降低。另外,由于在衍射光栅26的两侧未设置槽22,因此半导体元件30与衬底10之间的空气的量与比较例相比减少,半导体元件30与衬底10的接触面积变大。热阻降低,动作时的热有效地释放到衬底10。半导体元件30的温度上升被抑制,特性稳定。由于在衍射光栅26的两侧未设置槽22,因此例如在对图5所示的衬底50进行湿法蚀刻时,蚀刻剂难以侵入到半导体元件30之下。半导体元件30的蚀刻被抑制,变得难以剥离。

[0103]

在衬底10的si层16形成导波路20、平台24以及衍射光栅26。如图2所示,衍射光栅26包含凹部26a和凸部26b。如图1b所示,凸部26b、平台24在z轴方向上位于同一高度,形成衬底10的上表面。半导体元件30与凸部26b以及平台24接触。由于衬底10与si层16的接触面积变大,因此接合强度提高,散热性也变高。凹部26a的底面优选为si层16。热在si层16中传递并释放。

[0104]

衍射光栅26包含周期性配置的多个凹部26a和多个凸部26b。通过凹部26a以及凸部26b的周期排列能够对光的波长进行调整。如图2所示,多个凹部26a和多个凸部26b也可以一样地排列。衍射光栅26例如具有多个部分衍射光栅,可以作为sg-dbr(sampled grating-distributed bragg reflector,采样光栅分布式布拉格反射器)而发挥功能。

[0105]

图2所示的平台24的突出部24a朝向衍射光栅26在y轴方向上突出。通过突出部24a与半导体元件30接触,接合强度变高,散热性得以提高。由于突出部24a阻挡侵入槽22的蚀刻剂,因此抑制了从半导体元件30的下侧的蚀刻。

[0106]

半导体元件30是在衍射光栅26之上具有台面42、在平台24之上具有台面40以及44的脊形台面结构。电极38设置在台面42之上。对电极37以及38施加电压,从台面42下的有源层34射出光。能够通过台面42来规定光的模式的形状,模式的控制性得以提高。图1c所示的包含凹部26a的截面中的光限制系数为3.74%。图1b所示的包含凸部26b的截面中的光限制系数为5.77%。在半导体元件30的接合部分整体,能够得到4%以上的光限制系数。因此,能够抑制特性的劣化。为了提高光限制,半导体元件30只要在衍射光栅26之上具有台面42即可,也可以不具有台面40以及44。

[0107]

平台24的突出部24a越长,接触面积就越大,能够提高接合强度。另一方面,若突出部24a较长,衍射光栅26的宽度w1较小,则向半导体元件30的光的限制变弱,光会泄漏到衬底10。衍射光栅26的宽度w1例如优选大于半导体元件30的台面42的宽度。作为一个例子,衍射光栅26的宽度w1优选为台面42的宽度的2倍以上。台面42与平台24分离,因此向半导体元件30的光限制变强,能够抑制光向衬底10的泄漏并控制模式的形状。在衍射光栅26的宽度

w1大到堵塞槽22的程度的情况下,也可以不在平台24设置突出部24a。

[0108]

如图1a以及图2所示,衬底10的si层16具有锥部21。锥部21从衍射光栅26侧朝向与衍射光栅26相反的一侧为尖头。通过锥部21,能够在衍射光栅26与导波路20之间抑制光的反射并抑制光的损失。

[0109]

如图1a所示,半导体元件30具有从衍射光栅26侧朝向导波路20侧为尖头的锥部43。通过锥部43,能够增强半导体元件30与导波路20的光耦合并抑制光的损失。

[0110]

以上,对本公开的实施方式进行了详述,但本公开不限于特定的实施方式,可以在权利要求书所记载的本公开的主旨的范围内进行各种的变形、变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。