1.本发明涉及芯片封装技术领域,尤其涉及一种有源面板级扇出型封装结构及其制备方法。

背景技术:

2.随着集成电路封装技术的发展,芯片封装的作用开始不仅仅局限于对硅基芯片裸片的固定连接和引出引脚,功能化的封装逐渐受到人们的关注,越来越多的元件被希望封装在单个的封装体内以实现封装的集成化和紧凑化。扇出型面板级封装技术(fanout panel level package,foplp)利用面板技术中的多层互连线层对芯片的i/o进行重分配和扩展,但现有foplp技术仅实现了将无源元件集成在封装单元内,这对于利用单个封装体实现完整电子系统还存在不少距离。

3.因此,如何对封装结构进行改进,以扩展封装结构的功能,从而进一步提高封装结构的集成度,是当前亟待解决的技术问题。

技术实现要素:

4.本发明提供一种有源面板级扇出型封装(active fanout panel level package,afoplp)结构及其制备方法,用以解决现有的封装结构无法实现有源器件在封装单元内部的集成的问题,以扩展封装结构的功能,提高封装结构的集成度。本发明提供的封装结构除了利用面板技术的多层互连线实现对硅基芯片i/o的扩展,还利用面板技术中的有源薄膜晶体管构建功能电路,以对硅基芯片功能进行扩展,并且传感器、天线等外设也可以集成在面板上以实现对硅基芯片裸片的高度集成化功能性封装。

5.为了解决上述问题,本发明提供了一种有源面板级扇出型封装结构,包括:

6.衬底;

7.有源薄膜晶体管接口电路层,位于所述衬底上,包括有源薄膜晶体管接口电路,所述有源薄膜晶体管接口电路包括多个有源薄膜晶体管;

8.互连层,位于所述有源薄膜晶体管接口电路层背离所述衬底的一侧表面,所述互连层与所述有源薄膜晶体管接口电路电连接;

9.顶层外设器件,位于所述互连层背离所述有源薄膜晶体管接口电路层的一侧,所述顶层外设器件电连接所述互连层;

10.顶层芯片晶粒,位于所述互连层背离所述有源薄膜晶体管接口电路层的一侧,所述顶层芯片晶粒电连接所述互连层,所述顶层芯片晶粒为未经封装的硅基集成电路芯片;

11.底层外设器件,位于所述衬底背离所述有源薄膜晶体管接口电路层的一侧,所述底层外设器件电连接所述互连层;

12.底层芯片晶粒,位于所述衬底背离所述有源薄膜晶体管接口电路层的一侧,所述底层芯片晶粒电连接所述互连层,所述底层芯片晶粒为未经封装的硅基集成电路芯片。

13.可选的,所述顶层外设器件为传感器或者天线,所述底层外设器件为传感器或者

天线。

14.可选的,所述顶层芯片晶粒为数字集成电路芯片、模拟集成电路芯片或混合信号电路芯片,所述底层芯片晶粒为数字集成电路芯片、模拟集成电路芯片或混合信号电路芯片。

15.可选的,还包括:

16.顶层连接层,位于所述顶层芯片晶粒与所述互连层之间、以及所述顶层外设器件与所述互连层之间,用于固定连接所述顶层芯片晶粒与所述互连层、以及所述顶层外设器件与所述互连层;

17.底层连接层,位于所述底层芯片晶粒与所述衬底之间、以及所述底层外设器件与所述衬底之间,用于固定连接所述底层芯片晶粒与所述衬底、以及所述底层外设器件与所述衬底。

18.可选的,还包括:

19.第一连接结构,至少贯穿所述衬底和所述有源薄膜晶体管接口电路层,所述第一连接结构的一端电连接所述互连层中的第一子互连结构、另一端电连接所述底层外设器件,所述第一子互连结构电连接所述顶层芯片晶粒和所述有源薄膜晶体管接口电路;

20.第二连接结构,至少贯穿所述衬底和所述有源薄膜晶体管接口电路层,所述第二连接结构的一端电连接所述互连层中的第二子互连结构、另一端电连接所述底层芯片晶粒,所述第二子互连结构电连接所述顶层外设器件和所述有源薄膜晶体管接口电路。

21.可选的,所述有源薄膜晶体管接口电路层包括模拟电路、数字电路、或者模拟-数字混合电路。

22.可选的,所述有源薄膜晶体管包括半导体层,所述半导体层的材料为有机小分子半导体材料、聚合物半导体材料、小分子半导体材料-聚合物绝缘了混合体系材料、硅基半导体材料、或者氧化物半导体材料。

23.可选的,所述顶层芯片晶粒的数量为多个,且多个所述顶层芯片晶粒沿平行于所述互连层的顶面的方向平行排布,所述互连层的顶面是指所述互连层背离所述衬底的表面;

24.所述顶层外设器件的数量为多个,且多个所述顶层外设器件沿平行于所述互连层的顶面的方向平行排布。

25.可选的,所述底层外设器件的数量为多个,且多个所述底层外设器件沿平行于所述衬底的底面的方向平行排布,所述衬底的底面是指所述衬底背离所述有源薄膜晶体管接口电路层的表面;

26.所述底层芯片晶粒的数量为多个,且多个所述底层芯片晶粒沿平行于所述衬底的底面的方向平行排布。

27.为了解决上述问题,本发明还提供了一种如上所述的有源面板级扇出型封装结构的制备方法,包括如下步骤:

28.形成顶层芯片晶粒、顶层外设器件、底层外设器件和底层芯片晶粒,所述顶层芯片晶粒为未经封装的硅基集成电路芯,所述底层芯片晶粒为未经封装的硅基集成电路芯片;

29.形成有源面板,所述有源面板包括衬底、位于所述衬底上的有源薄膜晶体管接口电路层、位于所述有源薄膜晶体管接口电路层上的互连层,所述有源薄膜晶体管接口电路

层包括有源薄膜晶体管接口电路,所述有源薄膜晶体管接口电路包括多个有源薄膜晶体管,所述互连层电连接所述有源薄膜晶体管接口电路;

30.固定连接所述顶层芯片晶粒和所述顶层外设器件于所述互连层背离所述有源薄膜晶体管接口电路层的一侧、并固定连接所述底层芯片晶粒和所述底层外设器件于所述衬底背离所述有源薄膜晶体管接口电路层的一侧,所述顶层芯片晶粒、所述顶层外设器件、所述底层芯片晶粒和所述底层外设器件均电连接所述互连层。

31.本发明提供的有源面板级扇出型封装结构及其制备方法,通过设置包括衬底、互连层和有源薄膜晶体管接口电路层的有源面板,并在所述有源面板的相对两侧均形成芯片晶粒和外设器件,所述互连层和所述有源薄膜晶体管接口电路层的形成可以均由面板工艺实现,相比于现有的面板级扇出型封装结构,本发明不仅利用面板工艺中的多层互连层实现对待封装的硅基芯片的引脚的重分配,还利用面板工艺中的薄膜晶体管构建有源接口电路,对待封装硅基芯片进行功能扩展,并且本发明的封装对象不局限于硅基芯片,还可以包括外设器件等功能模块,最终实现完整的高度集成化电子系统。

附图说明

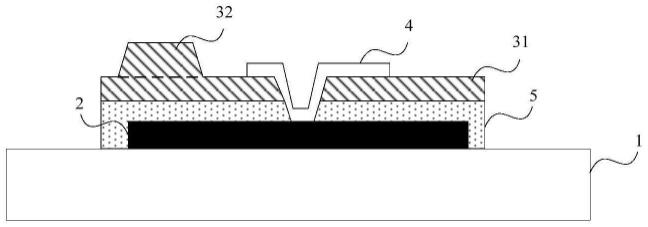

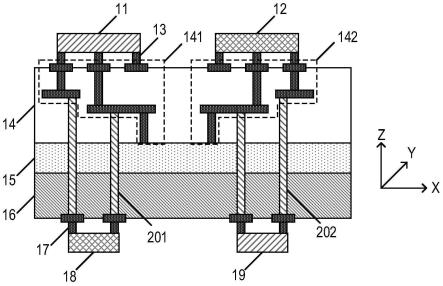

32.附图1是本发明具体实施方式中有源面板级扇出型封装结构的截面示意图;

33.附图2是本发明具体实施方式中有源面板级扇出型封装结构的俯视示意图;

34.附图3是本发明具体实施方式中有源薄膜晶体管接口电路的一示意图;

35.附图4是本发明具体实施方式中有源面板级扇出型封装结构的制备方法流程图;

36.附图5a-5b是本发明具体实施方式在制备有源面板级扇出型封装结构的过程中主要的工艺示意图。

具体实施方式

37.下面结合附图对本发明提供的有源面板级扇出型封装结构及其制备方法的具体实施方式做详细说明。

38.本具体实施方式提供了一种有源面板级扇出型封装结构,附图1是本发明具体实施方式中有源面板级扇出型封装结构的截面示意图。如图1所示,所述有源面板级扇出型封装结构,包括:

39.衬底16;

40.有源薄膜晶体管接口电路层15,位于所述衬底16上,包括有源薄膜晶体管接口电路,所述有源薄膜晶体管接口电路包括多个有源薄膜晶体管;

41.互连层14,位于所述有源薄膜晶体管接口电路层15背离所述衬底16的一侧表面,所述互连层14与所述有源薄膜晶体管接口电路电连接;

42.顶层外设器件12,位于所述互连层14背离所述有源薄膜晶体管接口电路层15的一侧,所述顶层外设器件12电连接所述互连层14;

43.顶层芯片晶粒11,位于所述互连层14背离所述有源薄膜晶体管接口电路层15的一侧,所述顶层芯片晶粒11电连接所述互连层14,所述顶层芯片晶粒11为未经封装的硅基集成电路芯片;

44.底层外设器件18,位于所述衬底16背离所述有源薄膜晶体管接口电路层15的一

侧,所述底层外设器件18电连接所述互连层14;

45.底层芯片晶粒19,位于所述衬底16背离所述有源薄膜晶体管接口电路层15的一侧,所述底层芯片晶粒19电连接所述互连层14,所述底层芯片晶粒19为未经封装的硅基集成电路芯片。

46.具体来说,在沿垂直于所述衬底16的顶面的方向(例如图1中的z轴方向)上,所述衬底16、所述有源薄膜晶体管接口电路层15和所述互连层14依次叠置,形成包括所述衬底16、所述有源薄膜晶体管接口电路层15和所述互连层14的有源面板。所述互连层14包括沿垂直于所述衬底16的顶面的方向平行排布的多层金属互连线、以及用于连接相邻两层所述金属互连线的金属连接插塞。本具体实施方式的所述互连层14中的不同层的所述金属互连线之间可以形成电容结构,以进一步扩展所述互连层14的功能。所述互连层14可以通过面板工艺实现,从而满足复杂的互连需求、以及实现高密度的互连。所述顶层芯片晶粒11和所述顶层外设器件12固定于所述互连层14的顶面(即所述互连层14背离所述有源薄膜晶体管接口电路层15的表面)。本具体实施方式可以通过所述互连层14电连接所述顶层芯片晶粒11和所述有源薄膜晶体管接口电路、以及通过所述互连层14电连接所述顶层外设器件12和所述有源薄膜晶体管接口电路。

47.所述有源薄膜晶体管接口电路层15所述有源薄膜晶体管电路,所述有源薄膜晶体管电路包括多个有源薄膜晶体管,即由多个所述有源薄膜晶体管电连接形成所述有源薄膜晶体管接口电路。所述有源薄膜晶体管接口电路用于扩展和增强所述顶层芯片晶粒11和/或所述底层芯片晶粒19的功能和应用场景。所述底层芯片晶粒19和所述底层外设器件18可以通过沿垂直于所述衬底16顶面的方向贯穿所述衬底16的通孔连接结构与所述互连层14电连接之后,再由所述互连层14电连接至所述有源波按摩晶体管接口电路。所述顶层芯片晶粒11和所述底层芯片晶粒19可以为硅基cmos工艺的芯片。

48.在一实施例中,所述有源薄膜晶体管接口电路中的多个所述有源薄膜晶体管均为分立的有源薄膜晶体管,多个分立的所述有源薄膜晶体管通过所述有源薄膜晶体管接口电路层中的导电互连线实现电连接。在另一实施例中,所述有源薄膜晶体管接口电路中的多个所述有源薄膜晶体管均为分立的有源薄膜晶体管,多个分立的所述有源薄膜晶体管通过所述互连层中的金属互连线实现电连接,从而可以提高多个所述有源薄膜晶体管连接的灵活性。

49.本具体实施方式中所述的外设器件用于接收自于所述有源面板级扇出型封装结构外部的信号或者向所述有源面板级扇出型封装结构外部传输信号,并将所述外部信号传输至所述互连层14。其中,所述外部信号是指来自于所述有源面板级扇出型封装结构外部的信号。所述外部信号可以是电信号、光信号、或者压力信号等。所述外设器件可以是但不限于传感器或者天线,其中,所述传感器可以为光传感器或者压力传感器。

50.所述有源薄膜晶体管的结构可以为底栅底接触结构、底栅顶接触结构、顶栅底接触结构、或者顶栅顶接触结构。

51.可选的,所述有源薄膜晶体管包括半导体层,所述半导体层的材料为有机小分子半导体材料、聚合物半导体材料、小分子半导体材料-聚合物绝缘了混合体系材料、硅基半导体材料、或者氧化物半导体材料。

52.所述衬底16可以为刚性衬底、柔性衬底或者弹性衬底。所述刚性衬底的材料可以

为玻璃。所述柔性衬底的材料可以为聚对苯二甲酸乙二醇酯(pet)、聚萘二甲酸乙二醇酯(pen)、聚酰亚胺(pi)、热固化的胶水、或者紫外固化的胶水。所述弹性衬底的材料可以为聚二甲基硅氧烷(pdms)、聚氨酯(pu)、或者铂催化硅胶(ecoflex)。

53.可选的,所述顶层外设器件12为传感器或者天线,所述底层外设器件18为传感器或者天线。其中,所述传感器可以是光传感器或者压力传感器。

54.可选的,所述顶层芯片晶粒11为数字集成电路芯片、模拟集成电路芯片或混合信号电路芯片,所述底层芯片晶粒为数字集成电路芯片、模拟集成电路芯片或混合信号电路芯片。

55.可选的,所述有源面板级扇出型封装结构还包括:

56.顶层连接层13,位于所述顶层芯片晶粒11与所述互连层14之间、以及所述顶层外设器件12与所述互连层14之间,用于固定连接所述顶层芯片晶粒11与所述互连层14、以及所述顶层外设器件与所述互连层;

57.底层连接层17,位于所述底层芯片晶粒19与所述衬底16之间、以及所述底层外设器件18与所述衬底16之间,用于固定连接所述底层芯片晶粒19与所述衬底16、以及所述底层外设器件18与所述衬底16。

58.具体来说,所述顶层芯片晶粒11的所有引脚电极均引出至所述顶层芯片晶粒11的下表面(即所述顶层芯片晶粒11朝向所述互连层14的表面),从而使得所述顶层芯片晶粒11的所有引脚电极均能够通过所述顶层连接层13与所述互连层14固定并电连接。所述顶层外设器件12的所有引脚电极也均引出至所述顶层外设器件12的下表面(即所述顶层外设器件12朝向所述互连层14的表面),从而使得所述顶层外设器件12的所有引脚电极均能够通过所述顶层连接层13与所述互连层14固定并电连接。所述底层芯片晶粒19的所有引脚电极均引出至所述底层芯片晶粒19的上表面(即所述底层芯片晶粒19朝向所述衬底16的表面),从而使得所述底层芯片晶粒19的所有引脚电极均能够通过所述底层连接层17固定于所述衬底16的下表面。所述底层外设器件18的所有引脚电极均引出至所述底层外设器件18的上表面(即所述底层外设器件18朝向所述衬底16的表面),从而使得所述底层外设器件18的所有引脚电极均能够通过所述底层连接层17固定于所述衬底16的下表面。

59.所述顶层连接层13和所述底层连接层17的材料可以相同,也可以不同。所述顶层连接层13和所述底层连接层17的材料可以均为导电胶、焊锡、双面粘性胶带、热固化的粘结胶水、紫外固化的粘结胶水或者烧结料等。相应的,所述顶层外设器件12和所述顶层芯片晶粒11可以与所述互连层14通过导电胶贴装、焊料焊接或者烧结等方式固定并电连接;所述底层外设器件18和所述底层芯片晶粒19可以与所述衬底16通过导电胶贴装、焊料焊接或者烧结等方式固定并电连接。

60.可选的,所述有源面板级扇出型封装结构还包括:

61.第一连接结构201,至少贯穿所述衬底16和所述有源薄膜晶体管接口电路层15,所述第一连接结构201的一端电连接所述互连层14中的第一子互连结构141、另一端电连接所述底层外设器件18,所述第一子互连结构141电连接所述顶层芯片晶粒11和所述有源薄膜晶体管接口电路;

62.第二连接结构202,至少贯穿所述衬底16和所述有源薄膜晶体管接口电路层15,所述第二连接结构202的一端电连接所述互连层14中的第二子互连结构142、另一端电连接所

述底层芯片晶粒19,所述第二子互连结构142电连接所述顶层外设器件12和所述有源薄膜晶体管接口电路。

63.具体来说,所述第一连接结构201贯穿所述有源薄膜晶体管接口电路层15是指,所述第一连接结构201贯穿所述有源薄膜晶体管接口电路外部的所述有源薄膜晶体管接口电路层15。所述第二连接结构202贯穿所述有源薄膜晶体管接口电路层15是指,所述第二连接结构202贯穿所述有源薄膜晶体管接口电路外部的所述有源薄膜晶体管接口电路层15。

64.所述第一连接结构201沿垂直于所述衬底16的顶面的方向(例如图1中的z轴方向)贯穿所述衬底16和所述有源薄膜晶体管接口电路层15、并延伸至所述互连层14内部,并与所述互连层14内部的所述第一子互连结构141与电连接。所述第一子互连结构141与所述顶层芯片晶粒11和所述有源薄膜晶体管接口电路均电连接。因此,一方面,所述底层外设器件18可以依次通过所述底层连接层17、所述第一连接结构201、所述第一子互连结构141、所述顶层连接层13与所述顶层芯片晶粒11电连接;另一方面,所述底层外设器件18还可以依次通过所述底层连接层17、所述第一连接结构201和所述第一子互连结构141与所述有源薄膜晶体管接口电路电连接。所述第二连接结构202沿垂直于所述衬底16的顶面的方向贯穿所述衬底16和所述有源薄膜晶体管接口电路层15、并延伸至所述互连层14内部,并与所述互连层14内部的所述第二子互连结构142电连接。因此,一方面,所述底层芯片晶粒19可以依次通过所述底层连接层17、所述第二连接结构201、所述第二子互连结构142、所述顶层连接层13与所述顶层外设器件12电连接;另一方面,所述底层芯片晶粒19还可以依次通过所述底层连接层17、所述第二连接结构201和所述第二子互连结构142与所述有源薄膜晶体管接口电路电连接。所述第一连接结构201和所述第二连接结构202的设置,提高了所述有源面板级扇出型封装结构内部连接、控制的灵活性,从而进一步提高了所述有源面板级扇出型封装结构的功能。

65.所述第一连接结构201、所述第二连接结构202、以及所述互连层14中的所述第一子互连结构141和所述第二子互连结构142的材料可以为导电聚合物、金属及碳基的导电浆料、导电聚合物、碳基导电物、金属氧化物、金属纳米线、金属、金属氧化物纳米颗粒掺杂的导电弹性材料中的一种或者两种以上的组合,其中,所述导电聚合物为ph值酸性或中性的聚(3,4-亚乙二氧基噻吩)-聚(苯乙烯磺酸)、聚苯乙烯磺酸、聚苯胺、聚噻吩或聚吡咯,所述碳基导电物为单层或多层石墨烯、石墨、炭黑、单壁或多壁碳纳米管,所述金属为金、银、铜、铝或镍,所述金属氧化物为氧化铟锡或氟掺杂锡氧化物。

66.可选的,所述有源薄膜晶体管接口电路层15包括模拟电路、数字电路、或者模拟-数字混合电路。

67.附图3是本发明具体实施方式中有源薄膜晶体管接口电路的一示意图。如图3所示,所述有源薄膜晶体管接口电路的输入端可以连接所述顶层外设器件12,输出端连接所述底层芯片晶粒19或者位于所述有源面板级扇出型封装结构外部的外部电路结构;和/或,所述有源薄膜晶体管接口电路的输入端连接所述底层外设器件18,输出端连接所述顶层芯片晶粒11或者位于所述有源面板级扇出型封装结构外部的外部电路结构。采用如图3所示的有源薄膜晶体管接口电路层电路结构,能够实现低功耗的电平转换功能,同时所述电路结构也可以实现对从所述底层外设器件18或者所述顶层外设器件12中获取的微弱信号进行放大的功能。

68.可选的,所述顶层芯片晶粒11的数量为多个,且多个所述顶层芯片晶粒11沿平行于所述互连层14的顶面的方向平行排布,所述互连层14的顶面是指所述互连层14背离所述衬底16的表面;

69.所述顶层外设器件12的数量为多个,且多个所述顶层外设器件12沿平行于所述互连层14的顶面的方向平行排布。

70.可选的,所述底层外设器件18的数量为多个,且多个所述底层外设器件18沿平行于所述衬底16的底面的方向平行排布,所述衬底16的底面是指所述衬底16背离所述有源薄膜晶体管接口电路层15的表面;

71.所述底层芯片晶粒19的数量为多个,且多个所述底层芯片晶粒19沿平行于所述衬底16的底面的方向平行排布。

72.附图2是本发明具体实施方式中有源面板级扇出型封装结构的俯视示意图。具体来说,多个所述顶层芯片晶粒11在图1和图2中的xy平面内平行排布,多个所述顶层外设器件12也在图1和图2中的xy平面内平行排布。相应的,多个所述底层芯片晶粒19在图1和图2中所示的xy平面内平行排布,多个所述底层外设器件18也在图1和图2中的xy平面内平行排布。

73.本领域技术人员还可以根据实际需要调整所述顶层芯片晶粒11、所述顶层外设器件12、所述底层芯片晶粒19和所述底层外设器件18的数量和尺寸规模,并相应调整所述有源面板(包括所述衬底16、所述有源薄膜晶体管接口电路层15和所述互连层14)的尺寸、以及所述有源薄膜晶体管接口电路层15的功能。所述有源薄膜晶体管接口电路层15的功能可以通过调整多个所述有源薄膜晶体管的类型以及电连接结构实现。

74.不仅如此,本具体实施方式还提供了一种如上所述的有源面板级扇出型封装结构的制备方法。附图4是本发明具体实施方式中有源面板级扇出型封装结构的制备方法流程图,附图5a-5b是本发明具体实施方式在制备有源面板级扇出型封装结构的过程中主要的工艺示意图。本具体实施方式制备的有源面板级扇出型封装结构的示意图可以参见图1-图3。如图1-图4、图5a和图5b所示,所述有源面板级扇出型封装结构的制备方法,包括如下步骤:

75.步骤s41,形成顶层芯片晶粒11、顶层外设器件12、底层外设器件18和底层芯片晶粒19,所述顶层芯片晶粒11为未经封装的硅基集成电路芯,所述底层芯片晶粒19为未经封装的硅基集成电路芯片,如图5a所示;

76.步骤s42,形成有源面板,所述有源面板包括衬底16、位于所述衬底16上的有源薄膜晶体管接口电路层15、位于所述有源薄膜晶体管接口电路层15上的互连层14,所述有源薄膜晶体管接口电路层15包括有源薄膜晶体管接口电路,所述有源薄膜晶体管接口电路包括多个有源薄膜晶体管,所述互连层14电连接所述有源薄膜晶体管接口电路,如图5a所示;

77.步骤s43,固定连接所述顶层芯片晶粒11和所述顶层外设器件12于所述互连层14背离所述有源薄膜晶体管接口电路层15的一侧、并固定连接所述底层芯片晶粒19和所述底层外设器件18于所述衬底背离所述有源薄膜晶体管接口电路层15的一侧,所述顶层芯片晶粒11、所述顶层外设器件12、所述底层芯片晶粒19和所述底层外设器件18均电连接所述互连层14,如图1、图2和图5b所示。

78.本具体实施方式提供的有源面板级扇出型封装结构及其制备方法,通过设置包括

衬底、互连层和有源薄膜晶体管接口电路层的有源面板,并在所述有源面板的相对两侧均形成芯片晶粒和外设器件,所述互连层和所述有源薄膜晶体管接口电路层的形成可以均由面板工艺实现,相比于现有的面板级扇出型封装结构,本发明不仅利用面板工艺中的多层互连层实现对待封装的硅基芯片的引脚的重分配,还利用面板工艺中的薄膜晶体管构建有源接口电路,对待封装硅基芯片进行功能扩展,并且本发明的封装对象不局限于硅基芯片,还可以包括外设器件等功能模块,最终实现完整的高度集成化电子系统。

79.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。