技术特征:

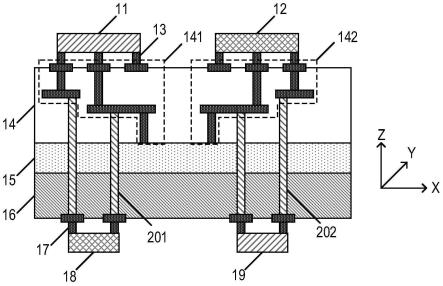

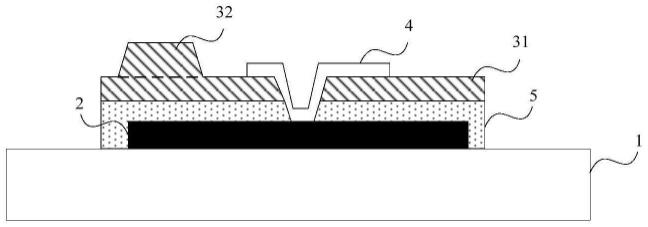

1.一种有源面板级扇出型封装结构,其特征在于,包括:衬底;有源薄膜晶体管接口电路层,位于所述衬底上,包括有源薄膜晶体管接口电路,所述有源薄膜晶体管接口电路包括多个有源薄膜晶体管;互连层,位于所述有源薄膜晶体管接口电路层背离所述衬底的一侧表面,所述互连层与所述有源薄膜晶体管接口电路电连接;顶层外设器件,位于所述互连层背离所述有源薄膜晶体管接口电路层的一侧,所述顶层外设器件电连接所述互连层;顶层芯片晶粒,位于所述互连层背离所述有源薄膜晶体管接口电路层的一侧,所述顶层芯片晶粒电连接所述互连层,所述顶层芯片晶粒为未经封装的硅基集成电路芯片;底层外设器件,位于所述衬底背离所述有源薄膜晶体管接口电路层的一侧,所述底层外设器件电连接所述互连层;底层芯片晶粒,位于所述衬底背离所述有源薄膜晶体管接口电路层的一侧,所述底层芯片晶粒电连接所述互连层,所述底层芯片晶粒为未经封装的硅基集成电路芯片。2.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,所述顶层外设器件为传感器或者天线,所述底层外设器件为传感器或者天线。3.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,所述顶层芯片晶粒为数字集成电路芯片、模拟集成电路芯片或混合信号电路芯片,所述底层芯片晶粒为数字集成电路芯片、模拟集成电路芯片或混合信号电路芯片。4.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,还包括:顶层连接层,位于所述顶层芯片晶粒与所述互连层之间、以及所述顶层外设器件与所述互连层之间,用于固定连接所述顶层芯片晶粒与所述互连层、以及所述顶层外设器件与所述互连层;底层连接层,位于所述底层芯片晶粒与所述衬底之间、以及所述底层外设器件与所述衬底之间,用于固定连接所述底层芯片晶粒与所述衬底、以及所述底层外设器件与所述衬底。5.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,还包括:第一连接结构,至少贯穿所述衬底和所述有源薄膜晶体管接口电路层,所述第一连接结构的一端电连接所述互连层中的第一子互连结构、另一端电连接所述底层外设器件,所述第一子互连结构电连接所述顶层芯片晶粒和所述有源薄膜晶体管接口电路;第二连接结构,至少贯穿所述衬底和所述有源薄膜晶体管接口电路层,所述第二连接结构的一端电连接所述互连层中的第二子互连结构、另一端电连接所述底层芯片晶粒,所述第二子互连结构电连接所述顶层外设器件和所述有源薄膜晶体管接口电路。6.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,所述有源薄膜晶体管接口电路包括模拟电路、数字电路、或者模拟-数字混合电路。7.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,所述有源薄膜晶体管包括半导体层,所述半导体层的材料为有机小分子半导体材料、聚合物半导体材料、小分子半导体材料-聚合物绝缘了混合体系材料、硅基半导体材料、或者氧化物半导体材料。8.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,所述顶层芯片晶粒

的数量为多个,且多个所述顶层芯片晶粒沿平行于所述互连层的顶面的方向平行排布,所述互连层的顶面是指所述互连层背离所述衬底的表面;所述顶层外设器件的数量为多个,且多个所述顶层外设器件沿平行于所述互连层的顶面的方向平行排布。9.根据权利要求1所述的有源面板级扇出型封装结构,其特征在于,所述底层外设器件的数量为多个,且多个所述底层外设器件沿平行于所述衬底的底面的方向平行排布,所述衬底的底面是指所述衬底背离所述有源薄膜晶体管接口电路层的表面;所述底层芯片晶粒的数量为多个,且多个所述底层芯片晶粒沿平行于所述衬底的底面的方向平行排布。10.一种如权利要求1所述的有源面板级扇出型封装结构的制备方法,其特征在于,包括如下步骤:形成顶层芯片晶粒、顶层外设器件、底层外设器件和底层芯片晶粒,所述顶层芯片晶粒为未经封装的硅基集成电路芯,所述底层芯片晶粒为未经封装的硅基集成电路芯片;形成有源面板,所述有源面板包括衬底、位于所述衬底上的有源薄膜晶体管接口电路层、位于所述有源薄膜晶体管接口电路层上的互连层,所述有源薄膜晶体管接口电路层包括有源薄膜晶体管接口电路,所述有源薄膜晶体管接口电路包括多个有源薄膜晶体管,所述互连层电连接所述有源薄膜晶体管接口电路;固定连接所述顶层芯片晶粒和所述顶层外设器件于所述互连层背离所述有源薄膜晶体管接口电路层的一侧、并固定连接所述底层芯片晶粒和所述底层外设器件于所述衬底背离所述有源薄膜晶体管接口电路层的一侧,所述顶层芯片晶粒、所述顶层外设器件、所述底层芯片晶粒和所述底层外设器件均电连接所述互连层。

技术总结

本发明提供的有源面板级扇出型封装结构包括:衬底;有源薄膜晶体管接口电路层,位于所述衬底顶面,包括有源薄膜晶体管接口电路;互连层,位于所述有源薄膜晶体管接口电路层上且电连接所述有源薄膜晶体管接口电路;顶层外设器件,位于所述互连层上且电连接所述互连层;顶层芯片晶粒,位于所述互连层上且电连接所述互连层,所述顶层芯片晶粒为未经封装的硅基集成电路芯片;底层外设器件,位于所述衬底底面且电连接所述互连层;底层芯片晶粒,位于所述衬底底面且电连接所述互连层,所述底层芯片晶粒为未经封装的硅基集成电路芯片。本发明实现了对待封装硅基芯片进行功能扩展。了对待封装硅基芯片进行功能扩展。了对待封装硅基芯片进行功能扩展。

技术研发人员:郭小军 邓立昂 尹晓宽 韩磊 欧阳邦 李骏

受保护的技术使用者:上海交通大学

技术研发日:2022.02.24

技术公布日:2022/6/10

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。