1.本发明涉及集成领域,并且更特别地,涉及电子产品、相关半导体产品及其制造方法。

背景技术:

2.在关于高性能片上集成储能解决方案的研究中,通过使用三维(3d)构造(例如,介孔(mesoporous)、纳米孔、纳米柱或纳米线型构造)来增加电容结构的比表面积已被证明是在允许减少芯片表面的同时显著增加电容密度的极好的方法。例如,由murata integrated passive solutions开发的pics技术允许将高密度电容元件集成到硅基板中。根据该技术,可以有效地将数十甚至数百个无源元件集成到一个硅片中。

3.增加电容的另一种方法涉及减小电介质的厚度。然而,随着3d构造的几何形状缩小,这种方法对常规电介质来说难度大大增加。替选的解决方案提出使用固态电解质代替常规的电介质。在该方法中,经由通过静电反应和/或氧化还原反应在电解质/电极界面处积累移动电荷(例如,离子,如li 、na 等)来存储能量。通过将电解质的厚度适当地配置成防止随着频率增加的电容急剧下降,通过这种方法可以获得成百上千倍的电容值,原因在于如下事实:可以实现在两个界面处的更大的电荷密度。

4.图1示出了示例3d固态电解质电容器100的截面图。如图1中所示,电容器100包括形成在基板102上方的3d结构104。3d结构104包括嵌入堆叠结构的多孔阳极氧化铝(paa)区域106。堆叠结构包括第一电极层108、固态电解质层110和第二电极层112。

5.为了增加电容器100的功率密度和频率响应,必须将固态电解质层110的厚度缩小至几纳米。为此目的,固态电解质层110的沉积通常使用原子层沉积(ald)来完成以确保固态电解质层110与paa区域106的形状的共形性。

6.然而,对于具有高长径比(例如,》100)的ppa区域106,实现固态电解质层110的共形性是非常有挑战性的任务,原因是前体(在电解质的ald期间所使用的)的暴露通常沿着paa区域106的孔不均匀。例如,在实验中,本发明的发明人观察到:对于具有80nm孔径的paa区域,在锂磷氧氮(lipon)ald沉积的情况下,在孔高度超过约5微米处开始出现共形性问题。这导致如图2中所示的电解质的不均匀沉积,图2示出lipon层沉积到孔高度为12微米且孔径为80纳米的paa区域中。具体来说,图2通过都沿着孔对p元素进行扫描来对lipon层进行能量色散x射线(edx)分析获得并且示出了如edx信号中p元素的强度降低(p元素强度从孔表面处的322降低至孔中部处的37和孔底部处的21)所反映的lipon层随着其延伸更深入paa孔而变得越来越不连续。

7.如图3中所示,电解质层110到paa区域106的孔中的不均匀沉积通常导致成分不均匀的区域(横截面(a))(即,化学计量不均衡的区域)和厚度不均匀的区域(横截面(b))。这些区域通常会导致易受击穿和电子泄漏的弱点。更严重地,不均匀的沉积可能会在电解质中造成不连续,从而导致电容器的短路(横截面(c))。

8.可以通过降低3d结构的长径比、增加电解质层的厚度和/或调整ald参数(例如,执

行更多ald循环、提高前体的停留时间或使用更小分子的前体)来减少这些缺陷。然而,这些解决方案的代价是显著增加了工艺成本/时间,并且阻碍了使电容密度最大化的最终目标。

技术实现要素:

9.本发明提出一种制造低缺陷高电容薄固态电解质电容器的方法。在实施方式中,该方法包括:

10.在基板上方形成三维结构,该三维结构包括具有从远离基板的三维结构的顶表面朝向基板延伸的细长孔或离开基板朝向远离基板的三维结构的顶表面延伸的细长柱的区域;

11.在三维结构的所述区域的表面上方形成第一电极层,该第一电极层与所述区域的所述表面共形;

12.在第一电极层上方形成中间层;以及

13.在中间层上方形成第二电极层,第二电极层与中间层共形,

14.其中,形成中间层包括:

15.形成与第一电极层部分地共形的固态电解质层;以及

16.形成与第一电极层共形的电介质层。

17.以相对于第一电极层仅部分地共形的方式形成固态电解质层提供了有利于所提出的方法的若干优点。

18.在一方面,制造时间减少。在固态电解质层与第一电极层仅部分地共形的情况下,电解质的形成时间(其通常使用原子层沉积(ald)来执行)变得更短。具体而言,可以使用更短的前体沉积和清除周期。

19.在另一方面,由于需要更少的材料因此制造工艺的成本降低。具体而言,减少了使用的固态电解质前体(一种昂贵的材料)的量。

20.在另一方面,通过要求固态电解质层与第一电极层仅部分地共形,可以使固态电解质层更薄并且被沉积到具有更大长径比的三维结构中。这导致电容器的增加的电容。

21.非限制性地,固态电解质层可以由锂磷氧氮(lipon)、li3po4、lialf4、lisipon、li2sio3或任何无机锂离子导体制成。

22.在实施方式中,固态电解质的厚度范围在5纳米与15纳米之间。

23.在又一方面,通过要求固态电解质层与第一电极层仅部分地共形,可以不考虑通常使用的验证固态电解质层的共形性的工艺步骤。因此,在实施方式中,制造方法不包括验证固态电解质层的共形性。

24.在实施方式中,形成与第一电极层部分地共形的固态电解质层包括选择用于固态电解质层的目标共形性水平和配置用于沉积电解质以实现所选择的目标共形性水平的ald工艺。在实施方式中,基于三维结构的几何形状和电解质材料选择目标共形性水平。

25.以相对于第一电极层共形的方式形成电介质层减轻了可能由允许固态电解质层与第一电极层仅部分地共形和/或更薄而引起的缺陷。在一方面,电介质层减少了可能由电解质层的成分不均匀的区域和厚度不均匀的区域引起的缺陷。在另一方面,电介质层减轻了可能由电解质层中的不连续引起的短路。

26.如本文中使用的,当层沿着下面的层(或表面)的形状延伸时其共形性大于或等于

80%的时候,该层与(直接地或间接地)下层(或表面)“共形”,并且当该层沿着下面的层(或表面)的形状延伸时其共形性小于80%但大于50%的时候,该层与下面的层(或表面)“部分地共形”。当层沿着下层(或表面)的形状延伸时其共形性小于50%的时候,该层被认为与下面的层(或表面)“不共形”。根据实施方式,该层和下面的层(或表面)根据具有细长孔或细长柱的3d结构而成形。该层相对于下面的层(或表面)的共形性被确定为在下面的层(或表面)的底表面(即,在3d结构的孔或柱间沟槽的底部处的下面的层或表面的表面)处测量的层的厚度与在下面的层(或表面)的顶表面(即,叠加在3d结构的顶表面上的下面的层或表面的表面)处测量的层的厚度之间的比率。可以通过在给定深度的选定数目的点处执行测量并对测量值进行平均来确定在给定深度(例如,孔底部或在顶表面处)的层的厚度。

27.在实施方式中,电介质层优选地由顺电体材料制成。作为顺电体,电介质层的特征在于在高频(例如》1khz,1khz是lipon的典型截止频率)下基本上恒定的介电常数,这确保了高频下的电容稳定性。此外,作为顺电体,电介质层与铁电材料相比呈现更大的介电强度,例如这在电介质层的一个作用是防止击穿和电子泄漏的情况下是有利的。

28.在实施方式中,电介质层由氧化铝、氧化硅或氧化铪制成。

29.认识到即使对于极端的长径比(例如,高达1000),电介质到狭窄结构中的沉积现在也受到良好控制(在厚度控制和共形性两个方面),根据实施方式电介质层可以被制成超薄的。在实施方式中,电介质层的厚度为5纳米或更小,与其它层的组合厚度(例如,大约30纳米)相比,电介质层的厚度可以忽略不计。因此,电介质层对结构的轮廓的影响可以忽略不计。

30.第一电极层/第二电极层可以各自包括一层或更多层的导电材料。在实施方式中,导电材料是适于ald沉积的材料。非限制性地,导电材料可以是铂、钌、钼、钴、钛、氮化钛、氮化钽、ruo2、co3o4、v2o5、tio

x

(x=0.5至2)或wo

x

(x=0.5至3)。

31.取决于存储机制的类型,在电容器中固态电解质层和电介质层的位置可以互换。

32.在实施方式中,该方法包括:

33.在第一电极层上方形成固态电解质层;以及

34.在固态电解质层上方形成电介质层。

35.根据该实施方式,第一电极层可以被形成为包括导电层和适于离子扩散/嵌入的氧化物层的双层。氧化物层还可以被选择为适于在氧化物层与导电层之间的界面处发生的吸附。导电层可以由铂、钌、钼、钴、钛、氮化钛、氮化钽制成。氧化物层可以由ruo2、co3o4、v2o5、tio

x

(x=0.5至2)或wo

x

(x=0.5至3)制成。氧化物层提升了第一电极层与固态电解质之间的界面处的离子电荷的存在,从而增加了电容密度。在实施方式中,可以通过使导电层氧化或通过ald来形成氧化物层。

36.在实施方式中,形成中间层包括在电介质层上方形成另一固态电解质层。由于额外的固态电解质层,可以实现特别是在较低频率下的电容密度的提升。根据该实施方式,第一电极层和第二电极层可以各自被形成为包括导电层和适于离子扩散/嵌入的氧化物层的双层。氧化物层还可以被选择为适于在氧化物层与导电层之间的界面处发生的吸附。氧化物层增强了在电极/电解质界面处的感应电流反应(即金属元素例如li被氧化以得到金属离子例如li 的反应)并且导致界面处的电荷密度增加。

37.在另一实施方式中,该方法包括:

38.在第一电极层上方形成电介质层;以及

39.在电介质层上方形成固态电解质层。

40.根据该实施方式,第二电极层可以被形成为包括导电层和适于离子扩散/嵌入的氧化物层的双层。氧化物层还可以被选择为适于在氧化物层与导电层之间的界面处发生的吸附。导电层可以由铂、钌、钼、钴、钛、氮化钛、氮化钽制成。氧化物层可以由ruo2、co3o4、v2o5、tio

x

(x=0.5至2)或wo

x

(x=0.5至3)制成。氧化物层提升了在第二电极层与固态电解质之间的界面处的离子电荷的存在,从而增加了电容密度。在实施方式中,可以通过使导电层氧化或通过ald来形成氧化物层。

41.如上文提到的,三维结构可以包括细长孔或细长柱。非限制性地,细长孔可以是多孔阳极氧化铝(paa)的孔。细长柱可以是纳米柱或纳米线。

42.在另一方面,本发明提供一种电容器,包括:

43.基板;

44.设置在基板上方的三维结构,该三维结构包括具有从远离基板的三维结构的顶表面朝向基板延伸的细长孔或离开基板朝向远离基板的三维结构的顶表面延伸的细长柱的区域;

45.设置在三维结构的所述区域的表面上方的第一电极层,第一电极层与所述区域的所述表面共形;

46.设置在第一电极层上方的中间层,中间层与第一电极层共形;以及

47.设置在中间层上方的第二电极层,第二电极层与中间层共形,

48.其中,中间层包括:

49.与第一电极层部分地共形的固态电解质层;以及

50.与第一电极层共形的电介质层。

附图说明

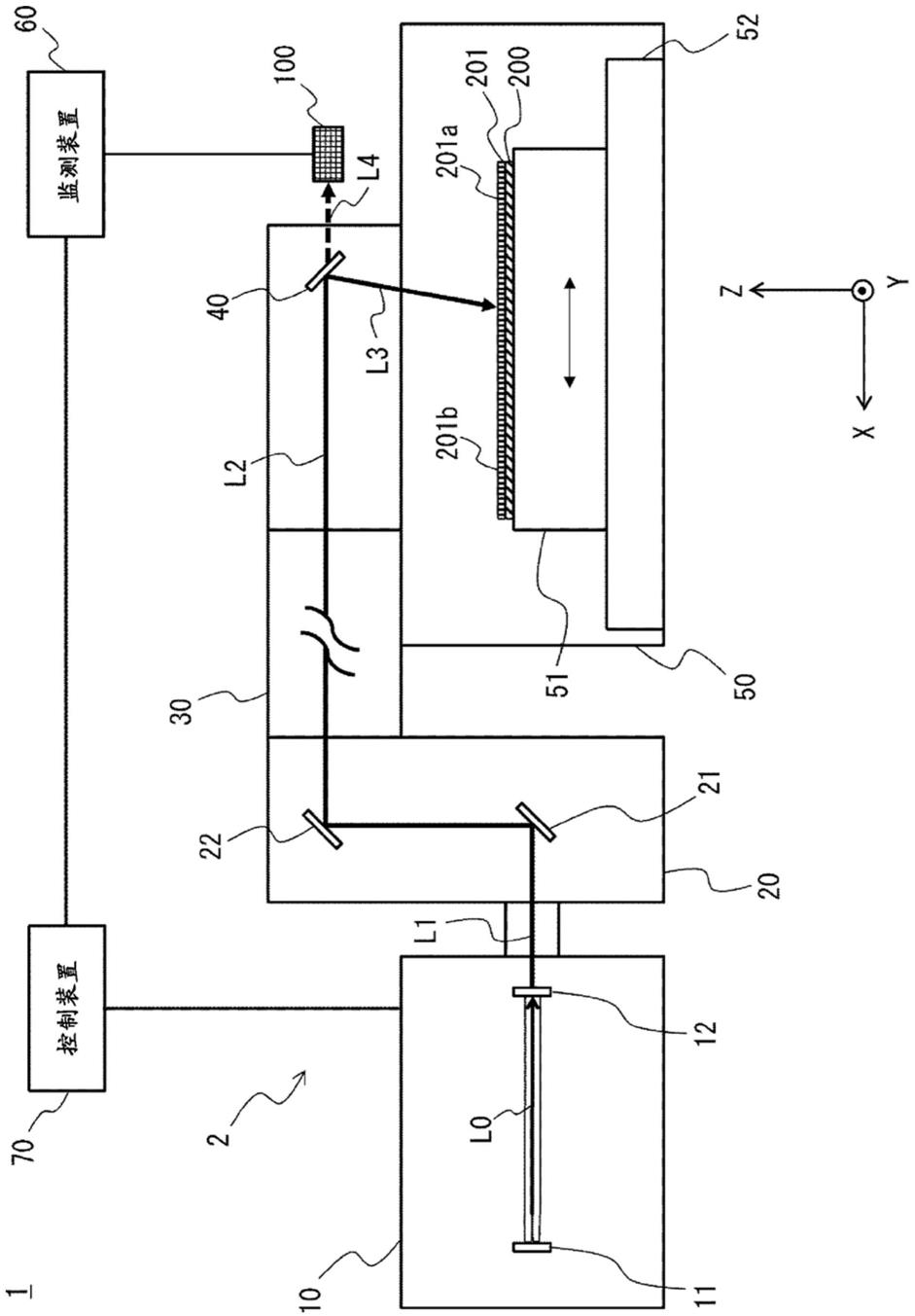

51.根据参照附图仅通过说明而非限制的方式给出的对本发明的某些实施方式的以下描述,本发明的其它特征和优点将变得明显,在附图中:

52.图1示出了示例3d固态电解质电容器的截面图。

53.图2示出了示出固态电解质沉积到高长径比3d结构中的扫描电子显微镜(sem)图像。

54.图3示出了与固态电解质沉积到高长径比3d结构中相关联的问题。

55.图4a至图4f示出了根据实施方式的制造3d固态电解质电容器的过程。

56.图5示出了示出电介质层沉积到高长径比3d结构中的透射电子显微镜(tem)图像。

57.图6示意性地示出了根据本发明的实施方式制造的示例3d固态电解质电容器的截面图。

58.图7示出了电介质层的厚度对根据实施方式的3d固态电解质电容器的电容的影响。

59.图8示出了根据实施方式的3d固态电解质电容器的电容随频率的表现。

具体实施方式

60.本发明的实施方式通过提出一种用于制造低缺陷高电容薄固态电解质电容器的方法来解决现有技术的现有缺陷。

61.本发明的发明人认识到,现有沉积技术例如原子层沉积(atomic layer deposition,ald)在用于将薄(例如,小于30纳米)固态电解质材料沉积到狭窄结构例如高长径比(例如长径比》100)的三维(3d)结构中时具有共形性缺陷。如上所述,这些缺陷可能导致结构中的电子泄漏、击穿和/或短路。

62.虽然发明人意识到可以通过调整沉积工艺的参数(例如,增加暴露时间和/或工艺中的循环次数,调整前体/电解质类型),通过降低3d结构的长径比和/或通过增加电解质的目标厚度来减少这些缺陷,但是这些解决方案的代价是显著增加了工艺成本/时间并且阻碍了使电容密度最大化的最终目标。

63.相反,认识到:即使对于极端的长径比(例如,1000),电介质材料的沉积现在也高度完善(在厚度控制和共形性两个方面),发明人提出将具有电解质层的超薄电介质层(例如,小于5纳米)嵌入电容器的电极之间。如下文进一步描述的,该解决方案在不影响得到的电容器的性能的情况下以最小的工艺成本/复杂性有效地解决了上述问题。

64.根据该解决方案,本发明提出了一种根据实施方式的在图4a至图4f中示出的制造固态电解质电容器的方法。

65.如图4a和图4b中所示,所提出的方法开始于在基板402上方形成三维结构420。三维结构包括区域408,区域408具有从远离基板402的三维结构420的顶表面418朝向基板402延伸的细长孔。替选地或附加地,区域408可以包括离开基板402朝向远离基板402的三维结构420的顶表面418延伸的细长柱。非限制性地,细长孔可以是多孔阳极氧化铝(paa)的孔。细长柱可以是纳米柱或纳米线。

66.出于说明性的目的,并且非限制性地,在图4a和图4b示出将三维结构420形成为包括细长孔。

67.如图4a中所示,这包括在基板402上方形成金属层404,以及在金属层404上沉积硬掩模层406。金属层404可以由铝制成,然而也可以使用其它金属,例如钛或钨。优选地,用于金属层404的金属是被阳极氧化以提供有序多孔区域的金属。硬掩模层406在其敞开的地方限定了金属层404内的期望对金属层404进行阳极氧化的部分。

68.接下来,如图4b中所示,由硬掩模层406限定的金属层404的部分被阳极氧化以形成包括具有孔的阳极氧化物层的区域408。在实施方式中,金属层404的阳极氧化包括第一阳极氧化步骤、蚀刻步骤和第二阳极氧化步骤。第一阳极氧化步骤在金属层404的顶上形成具有浅孔的阳极氧化物层。然后形成的阳极氧化物层被蚀刻,导致金属层404的顶表面产生限定最终孔位置的纹理。第二阳极氧化步骤完成金属层404的阳极氧化以形成如图4b中所示的孔。

69.随后,如图4c中所示,所提出的方法包括在三维结构420的区域408的表面上方形成第一电极层410,第一电极层410与区域408的表面共形。

70.如本文中使用的,当层沿着下面的层(或表面)的形状延伸时其共形性大于或等于80%的时候,该层与(直接地或间接地)下面的层(或表面)“共形”,并且当该层沿着下面的层(或表面)的形状延伸时其共形性小于80%但大于50%的时候,该层与下面的层(或表面)“部分地共形”。当层沿着下面的层(或表面)的形状延伸时其共形性小于50%的时候,该层被认为与下面的层(或表面)“不共形”。根据实施方式,该层和下面的层(或表面)根据具有细长孔或细长柱的3d结构而成形。该层相对于下面对的层(或表面)的共形性被确定为在下面的层(或表面)的底表面(即,在3d结构的孔或柱间沟槽的底部处的下面的层或表面的表面)处测量的层的厚度与在下面的层(或表面)的顶表面(即,叠加在3d结构的顶表面上的下面的层或表面的表面)处测量的层的厚度之间的比率。可以通过在给定深度的选定数目的点处执行测量并对测量值进行平均来确定在给定深度处(例如,孔底部或在顶表面处)的层的厚度。

71.第一电极层410可以包括一层或更多层的导电材料。在实施方式中,导电材料是适于ald沉积的材料。非限制性地,导电材料可以是铂、钌、钼、钴、钛、氮化钛、氮化钽、ruo2、co3o4、v2o5、tio

x

(x=0.5至2)或wo

x

(x=0.5至3)。为了实现要求的共形性水平,可以使用具有增加的暴露时间的ald。

72.接下来,在第一电极层410上方形成中间层。在一个实施方式中,如图4d和图4e中所示,这包括形成与第一电极层410部分地共形的固态电解质层412;并且然后在固态电解质层412上方形成与第一电极层410共形的电介质层414。

73.在实施方式中,固态电解质层412的沉积使用被预先配置成实现固态电解质层412相对于第一电极层410的目标共形性水平的ald工艺来完成。可以基于3d结构的几何形状(例如,长径比、孔/柱高度、孔/柱直径)和所使用的电解质材料来选择固态电解质412的目标共形性水平。例如,对于长径比为100、孔高度为8微米和孔径为80纳米的纳米多孔3d结构,可以在0与80%之间选择由lipon制成的固态电解质的目标共形性。

74.如本领域技术人员基于本文中的教导将理解的,ald工艺包括影响其结果的各种参数。虽然这些参数中的一些参数可能更难以调整(例如,设备、基板),但是其它参数可能被容易地改变以影响沉积结果。根据实施方式,用于固态电解质层412的沉积的ald工艺被预先设计成实现被选择的目标共形性水平。这包括选择一个或更多个参数,以上一个或更多个参数包括沉积技术(表面受控与受控)、ald循环次数(每个循环由前体剂量半周期、暴露步骤、清除步骤、共反应物剂量半周期、暴露步骤和清除步骤组成)、每个ald循环中前体和共反应物的剂量水平、每个ald循环中的前体/共反应物半周期的长度、每个ald循环中清除步骤的长度等。使用模拟工具或通过实验,可以验证设计ald工艺在具体3d结构中的结果。特别地,可以测量沉积的固态电解质的共形性水平以验证其是否满足所选择的目标共形性水平。

75.在实施方式中,因为固态电解质层412的所选择的目标共形性水平要求其与第一电极层410仅部分地共形,所以在制造期间不验证固态电解质层412的共形性(即,该层是否共形)。因此可以消除在固态电解质电容器的制造期间通常使用的验证固态电解质层的共形性的工艺步骤。

76.非限制性地,固态电解质层可以由锂磷氧氮(lipon)、li3po4、lialf4、lisipon、li2sio3或任何无机锂离子导体制成。

77.在固态电解质层412上方形成电介质层414可以使用ald来完成。如前面提到的,即使对于极端的长径比(例如,1000),电介质到狭窄结构中的沉积现在也受到良好控制(在厚度控制和共形性两个方面)。为了说明性的目的,图5示出了sio/alo/sio三层到孔高度为12

微米且孔径为80纳米的3d paa结构中的沉积的透射电子显微镜(tem)图像。如所示出的,沉积的三层都沿着孔形状(靠近表面、靠近中部和靠近底部)与下面的tin层共形(对于sio共形性为100%并且对于alo共形性》80%)。

78.在实施方式中,电介质层414的厚度为5纳米或更小。因此,3d电容器的轮廓受电介质层414的添加的影响可以忽略不计。

79.在实施方式中,电介质层414优选地由顺电体材料制成。作为顺电体,电介质层414的特征在于在高频(例如,>1khz)下基本上恒定的介电常数,这确保了高频下的电容稳定性。此外,作为顺电体,电介质层与铁电材料相比呈现更大的介电强度,例如,这在电介质层的一个作用是防止击穿和电子泄漏的情况下是有利的。在实施方式中,电介质层由氧化铝、氧化硅或氧化铪制成。

80.最后,如图4f中所示,该工艺终止于在中间层上方形成与中间层共形的第二电极层416。第二电极层410可以包括一层或更多层的导电材料。在实施方式中,导电材料是适于ald沉积的材料。非限制性地,导电材料可以是铂、钌、钼、钴、钛、氮化钛、氮化钽、ruo2、co3o4、v2o5、tio

x

(x=0.5至2)或wo

x

(x=0.5至3)。为了实现要求的共形性水平,可以使用具有增加的暴露时间的ald。

81.根据该实施方式,第一电极层可以被形成为包括导电层和适于离子扩散/嵌入的氧化物层的双层。氧化物层还可以被选择为适于在氧化物层与导电层之间的界面处发生的吸附。导电层可以由铂、钌、钼、钴、钛、氮化钛、氮化钽制成。氧化物层可以由ruo2、co3o4、v2o5、tio

x

(x=0.5至2)或wo

x

(x=0.5至3)制成。氧化物层提升了在第一电极层与固态电解质之间的界面处的离子电荷的存在,增加了电容密度。

82.在另一实施方式中(图4a至图4f中未示出),形成中间层包括在电介质层414上方形成另一固态电解质层。根据该实施方式,第一电极层408和第二电极层416可以各自被形成为包括导电层和适于离子扩散/嵌入的氧化物层的双层。氧化物层还可以被选择为适于在氧化物层与导电层之间的界面处发生的吸附。氧化物层增强了在电极/电解质界面处的感应电流反应(即金属元素例如li被氧化以得到金属离子例如li 的反应)并且导致界面处的电荷密度增加。

83.在另一实施方式中,固态电解质层412和电介质层414的位置被互换。因此,形成中间层包括在第一电极层410上方形成电介质层414;以及在电介质层414上方形成固态电解质层412。

84.根据该实施方式,第二电极层可以被形成为包括导电层和适于离子扩散/嵌入的氧化物层的双层。氧化物层还可以被选择为适于在氧化物层与导电层之间的界面处发生的吸附。导电层可以由铂、钌、钼、钴、钛、氮化钛、氮化钽制成。氧化物层可以由ruo2、co3o4、v2o5、tio

x

(x=0.5至2)或wo

x

(x=0.5至3)制成。氧化物层提升了在第二电极层与固态电解质之间的界面处的离子电荷的存在,增加了电容密度。

85.已经通过实验示出所提出的制造方法显著地减少了与在狭窄结构中的固态电解质的沉积相关联的缺陷。图6示意性地示出了根据本发明的实施方式制造的示例3d固态电解质电容器的截面图。如所示出的,在一方面,3d固态电解质电容器结构中的电介质层602的嵌入减少了电解质的成分不均匀的区域(横截面(a))和厚度不均匀的区域的影响,这些区域如上所述导致结构中易受击穿和电子泄漏影响的弱点。在另一方面,确保电极之间的

分离的电介质层602显著地防止由电解质的不连续性(横截面(c))引起的结构中的可能的短路。

86.在电容性能方面,得到的结构提供了可与常规固态电解质电容器相比的性能。这将在下面参照图7和图8进一步讨论。

87.图7示出了电介质层的厚度对固态电解质电容器的电容的影响。具体来说,图7比较了常规固态电解质电容器(即,没有电介质层)的电容密度与根据本发明的(不同的电介质层厚度的)三个固态电解质电容器的电容密度。测试的固态电解质电容器具有包括由铂制成的电极层和由lipon制成的电解质层的二维平面配置。电极层各自的厚度为50纳米并且电解质层的厚度为100纳米。用于根据本发明的三个电容器的电介质层由氧化铝制成并且电介质层的厚度分别为2纳米、5纳米和10纳米。为了获得图7的曲线,在每个电容器上以100mv/s至100v/s的不同扫描速率执行循环伏安法。图7中示出的电容值通过对电压范围内的电流密度进行积分而从循环伏安图中提取。

88.如图7中所示,根据本发明的电容器的性能与常规固态电解质电容器(即,没有电介质层)的性能相当。实际上,在电介质的厚度为2纳米时(曲线704),常规电容器(曲线702)与所提出的电容器之间的电容密度的差异在扫描速率范围内非常小。厚度为2纳米与厚度为5纳米(曲线706)之间的差异在低扫描速率下可忽略不计而在较高速率下略有增加。事实上,即使在超高扫描速率下,具有5纳米电介质的电容器的电容密度仍然高于10μf/cm2,对于二维平面电容器来说是高的数字。对于较高的电介质厚度例如在10纳米下(曲线708),电容密度在低扫描速率下明显地降低并且随着扫描速率的增加而迅速降低。这意味着在电介质的厚度方面存在限度,在该限度处,即使在低速率下,固态电解质中的离子也不再足够快的移动以存储能量。

89.图8示出了根据实施方式的3d固态电解质电容器的电容随频率的表现。具体来说,图8示出了常规固态电解质电容器(曲线802)和具有5纳米的嵌入电介质层的固态电解质电容器(曲线804)的电容与频率的关系曲线。显著地,在较低频率下(例如,低于5000hz),即使有嵌入电介质层(其将充当离子屏障),所提出的电容器的性能虽然低于常规电容器的性能,但是仍然完全可以接受。这一点很重要,因为离子电容器在低频下最受关注,在低频下离子电容器的离子存储机制允许是电介质电容器的好几倍(例如,是200倍)的电容。在高频下,两种结构之间的性能差异可以忽略不计,原因是固态电解质表现为常规电介质并且固态电解质/电介质双层的表现由电解质和电介质材料的介电常数的叠加决定。

90.另外的变型

91.虽然以上已经参照某些具体实施方式描述了本发明,但是将理解,本发明不受具体实施方式的特殊性的限制。在所附权利要求的范围内,可以在上述实施方式中做出许多变化、修改和开发。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。