1.本公开涉及用于量子位的参量放大器。

背景技术:

2.量子计算是一种新的计算技术,它利用了量子力学现象,诸如两个量子态的叠加和属于不同实体的量子态之间的纠缠。与使用配置为处于两个双稳态(例如“0”和“1”)的“位”来存储和操纵信息的数字计算机相比,量子计算系统旨在使用配置为量子态的叠加(例如,a|0》 b|l》)的“量子位”来操纵信息。每个量子位的量子态可以彼此纠缠,使得一个量子位的测量结果与另一个量子位的测量结果强相关。在某些实施方式中,这些属性可以提供优于经典计算技术的优势。

技术实现要素:

3.行波参量放大器(twpa)包括基于由集总元件电感器和电容器制成的传输线的放大器。在某些类型的twpa(称为约瑟夫森结twpa(也称为约瑟夫森twpa))中,电感器由包含约瑟夫森结的传输线形成,其提供非线性电感。用大的泵浦音调制该电感可以用于将能量传输到通过装置传播的其他信号,从而实现参量放大。twpa可能是基于超导体的量子计算系统中的有用工具,因为参量放大可以提供具有接近量子限制噪声的超导量子位的高保真状态测量。

4.在一些实施方式中,twpa被设计成具有与twpa所连接到的负载的阻抗相匹配的阻抗,从而减少电磁反射。这种阻抗匹配可能需要修改twpa的电容。一般而言,在一些方面,本公开的主题涵盖其中电容可以结合在twpa内而无需引入否则可能吸收信号并向twpa操作添加噪声的有损电介质材料的技术和装置。

5.特别地,本公开的主题包括twpa,其包括:共面波导,具有中断共面波导的中心迹线的至少一个约瑟夫森结;以及至少一个并联电容器,由接地超导体迹线形成,该接地超导体迹线跨过共面波导的中心迹线并通过间隙与该中心迹线分开。因此,超导体迹线和共面波导形成并联电容器的板,它们分开间隙高度。由于板之间的空间由(例如,由空气或真空制成的)间隙而不是有损电介质固体形成,因此可以减少twpa内的信号吸收和噪声,尤其是当twpa在真空条件下运行时。

6.一种参量行波放大器装置包括:共面波导,其中共面波导包括中断共面波导的中心迹线的至少一个约瑟夫森结;以及联接到共面波导的至少一个并联电容器,其中所述至少一个并联电容器中的每个并联电容器包括在共面波导的中心迹线的上表面上方延伸的对应超导体迹线,其中间隙将超导体迹线与中心迹线的上表面分开,并且其中包括所述至少一个约瑟夫森结的共面波导和并联电容器为行波参量放大器建立预定义的总阻抗。

7.该装置的实现可以包括以下特征中的一个或更多个。行波参量放大器的阻抗是每个并联电容器的间隙的高度的函数。在该装置中,超导体迹线在中心迹线上方延伸而不在至少一个约瑟夫森结上方延伸。该装置中,超导体迹线在与中心迹线的伸长方向正交的方

向上伸长。该装置中,超导体迹线在中心迹线上方提供空气桥。该装置中,共面波导包括沿中心迹线的第一侧延伸的第一接地平面并且包括沿中心迹线的第二侧延伸的第二接地平面,其中空气桥的第一端被电连接到第一接地平面,并且空气桥的第二端被电连接到第二接地平面。该装置包括:第一基板;以及第二基板,接合到第一基板,其中共面波导布置在第一基板的上表面上,超导体迹线布置在第二基板上。该装置中,第一基板凸块接合到第二基板。该装置中,共面波导包括:第一接地面,沿中心迹线的第一侧延伸;和第二接地平面,沿着中心迹线的第二侧延伸,其中超导体迹线在第一端通过第一凸块接合电连接到第一接地平面,并且在第二端通过第二凸块接合电连接到第二接地平面。该装置包括第二部件,其中行波参量放大器的预定义的总阻抗与第二部件的阻抗匹配。该装置中,预定义的总阻抗约为50欧姆。

8.一个总体方面包括制造参量行波放大器的方法,该方法包括:提供第一基板;在第一基板上形成共面波导,共面波导包括中断共面波导的中心迹线的至少一个约瑟夫森结;将至少一个超导体迹线固定在共面波导之上以分别形成至少一个并联电容器,其中所述至少一个并联电容器的每个超导体迹线在共面波导的中心迹线的上表面上方延伸并且通过相应的间隙与上表面分开,并且其中包括至少一个约瑟夫森结的共面波导和所述至少一个并联电容器为行波参量放大器建立预定义的总阻抗。

9.实施方式可以包括以下特征中的一个或更多个。在方法中,对于每个超导体迹线,将所述至少一个超导体迹线固定在共面波导之上包括:在共面波导上方提供电介质材料的层;

10.图案化电介质材料的层以形成电介质材料的垫并露出共面波导的一部分;在电介质材料的垫上和在共面波导的所述部分上形成超导体层;图案化超导体层以形成超导体迹线;以及去除电介质材料的垫以形成间隙,其中超导体迹线在中心迹线上方提供空气桥。在该方法中,共面波导包括沿中心迹线的第一侧延伸的第一接地平面和沿中心迹线的第二侧延伸的第二接地平面,并且其中图案化超导体层以形成超导体迹线包括在超导体迹线的第一端和第一接地平面之间形成第一电接触并且在超导体迹线的第二端和第二接地平面之间形成第二电接触。在该方法中,对于所述至少一个超导迹线中的每个超导迹线,将超导体迹线固定在共面波导之上包括:提供包括超导体迹线的第二基板;将第二基板接合到第一基板,使得超导体迹线定位在中心迹线的上表面上方并且与该上表面分开相应的间隙。

11.在该方法中,共面波导包括沿中心迹线的第一侧延伸的第一接地平面和沿中心迹线的第二侧延伸的第二接地平面,并且其中接合包括:在超导体迹线的第一端和第一接地平面之间形成第一凸块接合;以及在超导体迹线的第二端和第二接地平面之间形成第二凸块接合。在该方法中,所述至少一个超导体迹线中的每个超导体迹线在与中心迹线的伸长方向正交的方向上伸长。在该方法中,所述至少一个超导体迹线中的每个超导体迹线在中心迹线上方延伸而不在所述至少一个约瑟夫森结上方延伸。该方法形成第二部件,其中预定义的总阻抗与第二部件的阻抗匹配。在该方法中,预定义的阻抗为大约50欧姆。

12.本文公开的主题的各种实施方式可以具有一个或更多个优点。例如,在某些实施方式中,

13.出于本公开的目的,超导体(或者,超导)材料可以理解为在超导临界温度或更低时表现出超导特性的材料。超导体材料的示例包括但不限于铝(例如1.2开尔文的超导临界

温度)、铌(例如9.3开尔文的超导临界温度)和钛氮化物(例如5.6开尔文的超导临界温度)。

14.在附图和以下描述中阐述了一种或更多种实施方式的细节。从描述、附图和权利要求中,其他特征和优点将是明显的。

附图说明

15.图1是示出示例性行波参量放大器的电路示意图的图。

16.图2a是示出示例性行波参量放大器的俯视图的示意图。

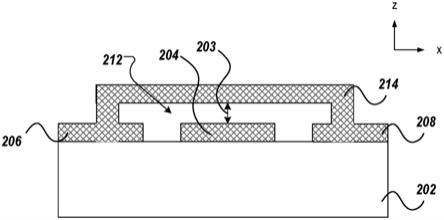

17.图2b是示出图2a的行波参量放大器沿线a-a的截面图的示意图。

18.图3a-3i是描绘图2a-2b的空气桥的制造过程的示意图。

19.图4a是示出示例性行波参量放大器的俯视图的示意图。

20.图4b是示出图4a的行波参量放大器沿线a-a的截面图的示意图。

21.图5a是示出示例性行波参量放大器的俯视图的示意图。

22.图5b是示出图5a的行波参量放大器沿线a-a的截面图的示意图。

23.图6a-6d是描绘用于图5a的twpa的制造过程的示意图。

具体实施方式

24.可以使用量子位和读出装置(例如,测量谐振器)之间的色散相互作用来完成量子位的读出。例如,可以生成探测音,用于对读出装置的频率进行采样以测量取决于量子位的状态/频率的相移。然而,在某些情况下,从读出装置获得的信号可能在输出线上衰减,从而降低信噪比并使测量更加困难。为了提高信噪比,可以在读出装置的输出端放置放大器。可用于增强输出信号的放大器的一示例是行波参量放大器(twpa)。twpa提供相对高的带宽、动态范围和饱和功率,因此可能允许频率复用,从而改进量子处理器的缩放。

25.图1是示出示例性twpa 100的电路示意图的图。twpa 100是基于包括集总元件电感器和电容器的传输线102的放大器。在某些实施方式中,传输线102可以包括例如共面波导,诸如超导共面波导。共面波导,包括超导共面波导,可以包括形成在基板上并在两侧由接地平面界定的中心导电迹线,其中接地平面与中心迹线间隔开。在超导共面波导的情况下,接地平面和中心迹线可以由诸如例如铝的超导体材料形成。

26.twpa 100的电感器包括约瑟夫森结104,其提供非线性电感。用大的泵浦音ω

p

调制该电感将把能量转移到通过该装置传播的其他信号(例如,从量子位测量谐振器获得的信号ωs),从而导致参量放大。特别地,泵浦音ω

p

调制twpa 100的与电流相关的电感,从而通过混频将泵浦音ω

p

耦合到空闲音ωi和来自测量谐振器的信号ωs,使得ωs ωi=2ω

p

。调整泵浦频率、信号频率和空闲频率之间的关系以满足能量守恒。twpa的增益、带宽和动态范围可以由耦合的非线性传输线的模式方程确定。有关twpa的操作和制造的更多详细信息,请参见“traveling wave parametric amplifier with josephson junctions using minimal resonator phase matching(具有使用最小谐振器相位匹配的约瑟夫森结的行波参量放大器)”,t.c.white等,应用物理快报,106卷,242601-1至242601-5(2015),其全部内容通过引用并入本文。

27.为了提高性能,结电感应该相当大。例如,结电感可以是共面波导的几何电感的大约10倍或更大。然而,为了避免不必要的反射,twpa 100的阻抗也应该与负载的阻抗相匹

配。在许多实施方式中,该阻抗设置为50欧姆。由于twpa 100的阻抗z随每单位长度的电感(l/l)除以每单位长度的电容(c/l)的平方根而变化,因此可以向twpa 100添加到地108的附加电容器106,也称为并联电容器,以将阻抗调节到接近所需阻抗。在一些实施方式中,额外电容大到足以使用平行板电容器设计来实现电容器106,其中平行板电容器的电介质由诸如例如sio2的沉积的绝缘体提供。在一些实施方式中,可以忽略由附加电容器增加的几何电感。

28.沉积的绝缘体通常在微波频率下是有损耗的,并且可以吸收放大器100内的信号以及增加放大器中的噪声。然而,当这种放大器用作放大的第一级时,这种损耗可能是有害的,因为在某些实施方式中,该信号损耗将等同于噪声的增加。

29.本公开的twpa可以形成为包括平行板电容器而不使用沉积的绝缘体。例如,本公开的平行板电容器可以使用空气或真空作为电介质来形成。通过消除沉积的绝缘体,在一些实施方式中,可以减少twpa内的信号吸收和噪声。

30.本公开的twpa可以以各种实施方式形成。例如,在一些实施方式中,用于形成平行板电容器的超导体迹线可以是在一端连接到地(例如,共面波导的一个接地平面)、跨过共面波导的中心迹线、并且在第二端连接到地(例如,共面波导的第二接地平面)的空气桥。在其他实施方式中,共面波导的中心迹线本身是在超导体迹线上方延伸的空气桥,该超导体迹线在一端连接到地(例如,共面波导的一个接地平面)并在第二端连接到地(例如,共面波导的第二接地平面)。在其他实施方式中,共面波导形成在第一基板上,并且超导体迹线形成在第二基板上,该第二基板(例如,通过凸块接合)接合到第一基板并与第一基板间隔开。在任何前述实施方式中,共面波导的中心迹线与超导体迹线之间的间隔可以用于调整并联电容器的阻抗。在任何前述实施方式中,中心迹线和超导体迹线沿其伸长的方向可以彼此正交。此外,超导体迹线可以与中心迹线重叠,而不在任何约瑟夫森结上方延伸。

31.图2a是示出根据本公开的示例性行波参量放大器200的俯视图的示意图。图2b是示出图2a的行波参量放大器200沿线a-a的截面图的示意图。图2a中所示的twpa 200是约瑟夫森twpa并且包括基板202和在基板202上形成的共面波导。在本示例中,基板202是电介质材料,诸如例如硅或蓝宝石,但也可以替代地使用其他电介质。

32.形成在基板上的共面波导包括中心迹线204。共面波导还包括分别沿着中心迹线204的第一侧和第二侧延伸的第一接地平面206和第二接地平面208。接地平面206、208和中心迹线由导电材料形成。在特定示例中,导电材料是超导体薄膜,诸如铝、铌或钛氮化物。接地平面206、208与中心迹线204间隔开距离201,该距离沿迹线204的长度可以是恒定的。

33.twpa 200还包括至少一个约瑟夫森结210,其中断共面波导的中心迹线204。图2a中的示例显示了串联连接的两个约瑟夫森结210。至少一个约瑟夫森结210提供了twpa 200的非线性电感部分。约瑟夫森结是由两个超导电极制成的量子力学装置,该两个超导电极由例如薄绝缘膜的阻挡物隔开。例如,在本示例中,至少一个约瑟夫森结210可以由al/al2o3/al薄膜的三层形成。

34.为了提供与共面波导的电感和约瑟夫森结的电感一起为twpa 200提供预定义的总阻抗的附加电容,twpa 200还包括至少一个并联电容器。在本示例中,所述至少一个并联电容器是平行板电容器,其中电容器的第一板由共面波导的中心迹线204提供,电容器的第二板由形成空气桥结构的导电迹线提供。特别地,导电迹线可以是超导体迹线214。在本示

例中,超导体迹线214跨过共面波导的中心迹线204的上表面。出于该示例的目的,上表面被理解为与迹线204的面向基板202的表面相反的迹线204的表面。超导体迹线214可以在与中心迹线204的伸长方向正交的方向上伸长。

35.如图2b所示,超导体迹线214的第一端与第一接地平面206物理接触并因此电连接到第一接地平面206。超导体迹线214的第二端与第二接地平面208物理接触并因此电连接到第二接地平面208。因此,超导体迹线214接地并形成并联电容器的接地板。同样如图2b所示,超导体迹线214跨过中心迹线204的上表面。在中心迹线204的上表面和由超导体迹线214形成的空气桥的下表面之间的空间212不包括电介质膜。也就是,在超导体迹线214和中心迹线204之间提供间隙212。该间隙可以包括空气。或者,包括twpa 200的装置可以在真空环境中使用,因此间隙212可以是真空。间隙的高度203(这里理解为直接跨过中心迹线204和超导体迹线214的相对面测量的距离)可以在例如大约30nm至约大10微米之间。并联电容器的电容与1/d成比例变化,其中d对应于间隙高度203。因此,通过调整间隙212的高度203,可以改变并联电容值。类似地,调整中心迹线204和超导体迹线214之间的重叠面积也可以用于改变并联电容值。特别地,超导迹线214的高度和/或重叠面积可以被预定义以实现相应的电容,该电容与中心迹线204的电感和至少一个约瑟夫森结的电感一起,为行波参量放大器200建立预定义的总阻抗。作为示例,对于超导迹线214和中心迹线204之间的约300nm的分离间隙,重叠面积可以为约100μm乘以约14μm。行波参量放大器的预定义的总阻抗可以被设置为紧密匹配芯片上的第二部件的阻抗。例如,twpa 200的预定义的总阻抗可以设置为大约50欧姆的阻抗(其可以对应于标准微波耦合器的阻抗),例如50欧姆阻抗的1欧姆以内、2欧姆以内、3欧姆以内、4欧姆以内、或5欧姆以内。这是因为twpa的大部分阻抗来源于中心迹线204中的至少一个约瑟夫森结的电感。当twpa装置被泵浦时,平均电感将增加,但与具有和不具有至少一个约瑟夫森结的共面波导的阻抗的差异相比,增加相对小(例如,大约10%)。因此,包括至少一个并联电容器的设计的twpa可以在没有施加泵浦信号时具有例如大约47-48欧姆的阻抗,然后当泵浦处于最佳功率时该阻抗增加到50欧姆。作为示例,总电感可以表示为

[0036][0037]

其中l

junction

为约瑟夫森结的电感,l

stray

为杂散电感,c

shunt

为并联电容,c

stray

为杂散电容。这假设所有值都是每单位长度的。

[0038]

超导体twpa 200可以使用与用于集成电路制造的相同或相似的处理技术(例如光刻、诸如溅射或化学气相沉积的材料沉积以及诸如蚀刻或剥离的材料去除)来制造。图3a-3i是描绘图2a-2b的twpa 200的超导体迹线214部分的示例性制造过程的示意图。特别地,图3a-3i是将处理步骤描绘为图2a的截面a-a处的截面图的示意图。在第一步骤中,如图3a所示,提供基板202。基板202是包括例如硅或蓝宝石的电介质材料。优选地,单晶硅或蓝宝石可以用于基板以降低基板202内的双级态(tls)的密度。

[0039]

随后,可以在基板202上方均匀地沉积例如第一导电层300,诸如超导体材料的层。层300可以包括例如铝、铌或钛氮化物,以及其他超导体材料。然后将导电层300图案化,如图3c所示。在该示例中,两个开口301形成在层300中并且延伸进出页面(例如,沿着y轴),使得基底基板202通过孔301暴露。孔301建立第一接地平面206、中心迹线204和第二接地平面

208。换句话说,孔302对应于两个沟槽,将接地平面206与中心迹线204分开,并将接地平面208与中心迹线204分开。可以通过沉积光致抗蚀剂层、uv曝光、显影光致抗蚀剂层以及对层300的暴露区域进行湿法或干法蚀刻来实现第一导电层300的图案化。或者,在一些实施方式中,使用剥离工艺以形成开口301。

[0040]

在对第一导电层300进行图案化之后,可以在基板202上方沉积电介质材料的层302,例如二氧化硅层,以覆盖层300和开口301,如图3d所示。层302对应于旨在用于支撑将要形成的导电桥结构的层间电介质。参照图3e,该装置可以通过化学机械抛光(cmp)而被平坦化。此步骤减小了由两个孔周围的凹坑导致的粗糙度,该凹坑可能影响后续层的厚度和均匀性。

[0041]

随后,可以图案化电介质材料的层302以形成支撑将要形成的导电桥的支撑结构305或垫区域,如图3f所示。特别地,电介质材料的层302可以被图案化,使得开口304形成在层302内以暴露第一接地平面206的部分并且暴露第二接地平面208的部分。可以使用例如干法或湿法蚀刻工艺形成开口。

[0042]

参照图3g,可以在电介质层302和开口304上方沉积第二导电层306,使得沉积的层306接触并形成在接地平面206、208的暴露部分上。层306的导电材料可以包括超导体材料,诸如铝、铌或钛氮化物等。随后,如图3h所示,可以图案化第二导电层306,使得仅第二导电层的对应于桥214的部分保留,而其余部分被去除。图案化可以包括例如湿法或干法蚀刻工艺。在对层306进行图案化以形成桥214之后,如图3i所示,去除桥214下方和桥214周围的剩余电介质材料304。例如,去除电介质材料304可以包括执行干蒸气蚀刻(dry-vapor etch)。特别地,如果电介质材料304是二氧化硅,则可以使用干蒸气hf(vhf)蚀刻选择性地去除二氧化硅。或者,在一些实施方式中,取决于用作电介质层304的具体材料,可以使用基于等离子体(例如用四氟甲烷蒸气、三氟化氮蒸气或二氟化氙产生的等离子体)的蚀刻工艺选择性地去除电介质304。因此电介质层304的去除留下“空气桥”结构,该结构跨过中心迹线204并且在一端由第一接地平面206支撑并且在另一端由第二接地平面208支撑。

[0043]

尽管图2a-2b的twpa 200将空气桥结构214描绘为用于联接两个接地平面,但在一些实施方式中,空气桥结构可以替代地形成为中心迹线204的一部分。例如,图4a是示出示例性行波参量放大器400的俯视图的示意图,其中中心迹线204跨过第一接地平面206和第二接地平面208之间的联接链路402。图4b是示出图4a的行波参量放大器沿线a-a的截面图的示意图。

[0044]

特别地,在示例性twpa 400中,联接链路402可以形成为形成第一接地平面206和第二接地平面208的导电材料的同一层的部分,因此可以在与第一接地平面206和第二接地平面208相同的处理步骤中被图案化。相比之下,中心迹线204的一部分404被构造为跨过联接部分204的空气桥。如图4a和图4b所示,中心迹线204的空气桥部分404以对应的间隙高度203定位在联接部分402之上。中心迹线204的其余部分可以形成在与第一接地平面206、第二接地平面208和联接部分402相同的层中。空气桥部分404可以在第一端401固定到中心迹线204的形成在与接地平面206、208相同的层中的部分,并且可以在第二端403固定到中心迹线204的形成在与接地平面206、208相同的层中的另一部分。与twpa200一样,可以调整间隙高度203以及空气桥和联接部分402之间的重叠面积以改变电容,这又可以用于将twpa 400的整体阻抗改变为预定义值。

[0045]

用作空气桥的部分404可以以与图2a的空气桥类似的方式制造。例如,制造部分404可以包括:形成并图案化第一导电层,该第一导电层包括下面的联接部分402、第一接地平面206和第二接地平面208以及中心迹线204的某些部分;在第一导电层上方沉积并图案化绝缘层;在图案化的绝缘层上沉积并图案化第二导电层以限定空气桥结构;以及去除绝缘层以形成空气桥结构。

[0046]

在一些实施方式中,可以使用堆叠结构而不是空气桥结构来形成并联电容器。图5a是示出使用堆叠结构形成的示例性行波参量放大器500的俯视图的示意图。图5b是示出图5a的行波参量放大器500沿线a-a的截面图的示意图。在图5a中,使用虚线描绘第一接地平面206、中心迹线204、第二接地平面208和跨过中心迹线204的超导迹线504以指示它们在twpa500中的相对位置。

[0047]

如图5b所示,超导体迹线504形成在第二基板502上并通过接合元件506堆叠到第一基板204。第二基板502可以包括例如电介质基板,诸如硅或蓝宝石。超导体迹线504可以在与中心迹线204的伸长方向正交的方向上伸长。接合元件506在超导体迹线504的第一端和第一接地平面206之间提供直接物理连接和电连接,以及在超导体迹线504的第二端和第二接地平面208之间提供直接物理连接和电连接。除了提供电连接之外,接合元件506还设置间隙高度203。接合元件506可以例如由超导体材料诸如铝、铌或钛氮化物等形成。在一些实施方式中,在接合元件506与接合元件506所连接到的接地平面和/或超导体迹线504之间提供扩散阻挡物。例如,在一些情况下,阻挡层可以由钛氮化物、铂或钨形成。

[0048]

使用凸块接合相对于使用空气桥结构来建立并联电容器的一个优点是,凸块接合允许在某些实施方式中基于逐个装置而不是基于逐个晶片来设置twpa的电容。例如,在一些实施方式中,可以制造堆叠的底部部分(即,twpa的包括接地平面和中心迹线的部分),之后可以将包括底部部分的晶片切割成单独的芯片。然后可以使用倒装芯片接合将堆叠的上部部分(即,包括旨在跨过中心迹线204的超导体迹线504的部分)接合到底部堆叠部分。然后可以通过改变间隙高度203在接合工艺期间原位调整并联电容器的电容,从而调整twpa的总阻抗。因此,可以避免在阻抗变化的情况下重新设计twpa结构的需要。如本文所解释的,可以预定义高度203和/或超导迹线504与中心迹线204的重叠面积以实现对应的电容,该电容与中心迹线204的电感和至少一个约瑟夫森结的电感一起为行波参量放大器500建立预定义的总阻抗。行波参量放大器的预定义的总阻抗可以被设置为紧密匹配芯片上的第二部件的阻抗。例如,twpa 500的预定义的总阻抗可以设置为大约50欧姆的阻抗(其可以对应于标准微波耦合器的阻抗),例如50欧姆阻抗的1欧姆以内、2欧姆以内、3欧姆以内、4欧姆以内或5欧姆以内。

[0049]

图6a-6d是描绘图5a的twpa的制造过程的示意图。在第一步骤中,如图6a所示,提供包括第一接地平面206、中心迹线204和第二接地平面208的第一基板202。接地平面可以通过对应的开口301与中心迹线分开。可以以与本文描述的图3a-3c相同的方式制造该基板。此外,如图6b所示,提供包括超导体迹线504的第二基板502。超导体迹线504可以通过首先在基板502上沉积超导体材料的层并图案化(例如,通过光刻和湿法或干法蚀刻工艺或通过剥离工艺)沉积的层以形成迹线504来制造。随后,如图6c所示,可以形成接合元件506。在一些实施方式中,接合元件506可以形成在接地平面206和208上。或者,接合元件506可以形成在超导体迹线504上。接合元件506可以通过诸如例如热蒸发的沉积工艺形成并且可以使

用光刻和湿法或干法蚀刻工艺或剥离工艺的组合来图案化。

[0050]

然后将基板接合在一起,如图6d所示。可以使用例如压力接合将两个基板彼此接合。可以在不施加热的情况下(例如,在室温下)执行压力接合。用于形成接合的压力的示例是对于6平方毫米芯片中的1000个凸块为25牛顿。在室温(例如,在大约18℃和大约30℃之间的范围内)执行接合的一个优点是可以减少在材料界面处形成小丘和空隙。

[0051]

可以设置接合元件106的厚度,使得间隙高度203间隔期望的量。例如,第一芯片的面向第二芯片的相对表面的表面之间的高度203可以被设置为在大约0.5μm至大约100μm之间(例如,在大约0.5μm至大约20μm之间,在大约0.5μm和大约15μm之间,在大约0.5μm和大约10μm之间,在大约0.5μm和大约5μm之间,或者在30大约0.5μm和大约2.5μm之间)。

[0052]

本说明书中描述的量子主题和量子操作的实施方式可以在合适的量子电路中,或更一般地,量子计算系统中实现,包括本说明书中公开的结构及其结构等价物,或者它们中的一个或更多个的组合。术语“量子计算系统”可以包括但不限于量子计算机、量子信息处理系统、量子密码系统、拓扑量子计算机或量子模拟器。

[0053]

术语量子信息和量子数据是指由量子系统携带、保存或存储的信息或数据,其中最小的非平凡系统是量子位,例如,定义量子信息的单位的系统。应当理解,术语“量子位”包括在相应上下文中可以适当地近似为两级系统的所有量子系统。这样的量子系统可以包括多级系统,例如,具有两个或更多个级。作为示例,这样的系统可以包括原子、电子、光子、离子或超导量子位。在一些实施方式中,计算基础态被识别为基态和第一激发态,然而应当理解,计算态被识别为更高级激发态的其他设置是可能的。应当理解,量子存储器是能够长时间、高保真、高效率地存储量子数据的装置,例如光用于传输的光-物质界面,以及用于存储和保存量子数据的量子特征诸如叠加或量子相干的物质。

[0054]

量子电路元件(也称为量子计算电路元件和量子信息处理装置)包括用于执行量子处理操作的电路元件。也就是,量子电路元件被配置为利用量子力学现象,诸如叠加和纠缠,以非确定性方式对数据执行操作。某些量子电路元件,诸如量子位,可以配置为同时表示和操作处于多于一个状态的信息。超导量子电路元件的示例包括电路元件,诸如量子lc振荡器、量子位(例如通量量子位、相位量子位或电荷量子位)和超导量子干涉装置(squid)(例如rf-squid或dc-squid)等。

[0055]

相比之下,经典电路元件通常以确定性方式处理数据。经典电路元件可以被配置为通过对数据执行基本算术、逻辑和/或输入/输出操作来共同执行计算机程序的指令,其中数据以模拟或数字形式表示。在一些实施方式中,经典电路元件可以用于通过电或电磁连接向量子电路元件传输数据和/或从量子电路元件接收数据。经典电路元件的示例包括基于cmos电路的电路元件、快速单通量量子(rsfq)装置、互易量子逻辑(rql)装置和ersfq装置(其是rsfq的不使用偏置电阻器的节能版本)。

[0056]

本文所述的量子电路元件和经典电路元件的制造可能需要沉积一种或更多种材料,诸如超导体、电介质和/或金属。根据所选择的材料,这些材料可以使用诸如化学气相沉积、物理气相沉积(例如蒸发或溅射)或外延技术等沉积工艺以及其他沉积工艺来沉积。在此描述的用于制造电路元件的工艺可能需要在制造期间从装置中去除一种或更多种材料。根据要去除的材料,去除工艺可以包括例如湿法蚀刻技术、干法蚀刻技术或剥离工艺。可以使用已知的光刻技术(例如,光刻或电子束光刻)对形成本文所述的电路元件的材料进行图

案化。

[0057]

在使用超导量子电路元件和/或超导经典电路元件(诸如本文描述的电路元件)的量子计算系统的操作期间,超导电路元件在低温恒温器内被冷却到允许超导体材料表现出超导特性的温度。超导体(或者超导)材料可以理解为在超导临界温度或更低时表现出超导特性的材料。超导材料的示例包括铝(1.2开尔文的超导临界温度)、铌(9.3开尔文的超导临界温度)和钛氮化物(5.6开尔文的超导临界温度)。

[0058]

虽然本说明书包含许多具体的实施细节,但这些不应被解释为对可能要求保护的范围的限制,而是对可能特定于特定实施方式的特征的描述。本说明书中在不同的实施方式的上下文中描述的某些特征也可以在单个实施方式中组合实现。相反,在单个实施方式的上下文中描述的各种特征也可以在多个实施方式中单独实现或以任何合适的子组合来实现。此外,尽管特征可以在上面描述为在某些组合中起作用并且甚至最初如此要求,但是在一些情况下来自要求的组合的一个或更多个特征可以从所述组合去除,并且要求的组合可以针对子组合或子组合的变体。

[0059]

类似地,虽然在附图中以特定次序描绘了操作,但这不应被理解为要求这些操作以所示的特定次序或按顺序次序执行,或者所有所示的操作都被执行以获得期望的结果。例如,权利要求中记载的动作可以以不同的次序执行,但仍能实现期望的结果。在某些情况下,多任务和并行处理可能是有利的。此外,上述实施方式中各种部件的分离不应理解为在所有实施方式中都需要这种分离。

[0060]

已经描述了许多实施例。然而,将理解,在不背离本发明的精神和范围的情况下可以进行各种修改。例如,在一些实施方式中,twpa是动态电感twpa,其可以至少部分地由在微波频率范围内(例如,在大约300mhz和300ghz之间)表现出高动态电感lk的材料形成。动态电感twpa通常在较高阻抗(例如,约200欧姆)下运行,因为使用本文公开的几何形状来设计电容可能是困难的。由于动态电感twpa表现出相对较弱的非线性,因此它们往往长得多,以实现所需的增益。

[0061]

因此,如本文所述,动态电感twpa可以从具有增加其每单位长度的电容的低损耗方式中获益更多。如本文所述的示例中所示,跨过中心迹线的超导体迹线这样做而不在至少一个约瑟夫森结上方延伸。然而,在一些实施方式中,超导体迹线可以在至少一个约瑟夫森结上方延伸,只要重叠被设计成预定义的几何形状以提供每单位长度的预设计的电容。因此,其他实施例在所附权利要求的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。