三维存储装置及其形成方法

1.相关申请的交叉引用

2.本技术要求于2021年8月23日提交的标题为“three-dimensional memory devices and methods for forming the same”的国际申请no.pct/cn2021/114050的优先权的权益,以引用方式将该国际申请的全部内容并入本文中。

背景技术:

3.本公开的实施例涉及三维(3d)存储装置及其制造方法。

4.通过改进工艺技术、电路设计、编程算法和制造工艺,将平面存储单元缩小到更小的尺寸。然而,随着存储单元的特征尺寸接近下限,平面工艺和制造技术变得具有挑战性且成本高。结果,平面存储单元的存储密度接近上限。随着3d存储层数量的不断增加,沟道轮廓的控制变得越来越困难。

技术实现要素:

5.本文公开了3d存储装置及其形成方法的实施例。

6.在一个方面,公开了一种3d存储装置。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。存储膜包括半导体沟道之上的隧穿层、隧穿层之上的存储层和存储层之上的阻挡层。阻挡层在沟道结构的底部处的第一厚度大于阻挡层在沟道结构的上部处的第二厚度。

7.在另一方面,公开了一种3d存储装置。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。半导体沟道包括有角结构,并且半导体沟道在有角结构下方的沟道结构的底部处的第一直径小于半导体沟道在有角结构上方的沟道结构的上部处的第二直径。

8.在又一方面,公开了一种系统。该系统包括被配置为存储数据的3d存储装置、以及耦合到3d存储装置并被配置为控制3d存储装置的操作的存储控制器。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。存储膜包括半导体沟道之上的隧穿层、隧穿层之上的存储层和存储层之上的阻挡层。阻挡层在沟道结构的底部处的第一厚度大于阻挡层在沟道结构的上部处的第二厚度。

9.在又一方面,公开了一种系统。该系统包括被配置为存储数据的3d存储装置、以及耦合到3d存储装置并被配置为控制3d存储装置的操作的存储控制器。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。半导体沟道包括有角结构,并且半导体沟道在有角结构下方的沟道结构

的底部处的第一直径小于半导体沟道在有角结构上方的沟道结构的上部处的第二直径。

10.在又一方面,公开了一种用于形成3d存储装置的方法。包括第一电介质层、第一多晶硅层、第二电介质层和第二多晶硅层的第一堆叠结构形成在衬底上。包括交替布置的多个第三电介质层和多个牺牲层的第二堆叠结构形成在第一堆叠结构上。形成沿第一方向穿透第二堆叠结构和第一堆叠结构的沟道孔。执行氧化操作以在由沟道孔的侧壁暴露的第一多晶硅层上形成第四电介质层。沟道结构形成在沟道孔中。去除衬底、第一电介质层、第一多晶硅层、第四电介质层和沟道结构的底部。第三多晶硅层形成在暴露的沟道结构之上。

11.在又一方面,公开了一种用于形成3d存储装置的方法。包括第一电介质层、第一多晶硅层、第二电介质层和第二多晶硅层的第一堆叠结构形成在衬底上。包括交替布置的多个第三电介质层和多个牺牲层的第二堆叠结构形成在第一堆叠结构上。形成沿第一方向穿透第二堆叠结构和第一堆叠结构的沟道孔。第四电介质层沿垂直于第一方向的第二方向形成在由沟道孔的侧壁暴露的第一多晶硅层上,以连接由沟道孔划分的第一多晶硅层。在第四电介质层上方的沟道孔中形成沟道结构。去除衬底、第一电介质层、第一多晶硅层、第四电介质层和沟道结构的底部。在暴露的沟道结构之上形成第三多晶硅层。

附图说明

12.并入本文并形成说明书一部分的附图示出了本公开的各方面,并且与描述一起进一步用于解释本公开并使相关领域的技术人员能够制作和使用本公开。

13.图1示出了根据本公开的一些方面的示例性3d存储装置的截面。

14.图2示出了根据本公开的一些方面的沟道结构的底部的截面。

15.图3示出了根据本公开的一些方面的沟道结构的底部的截面。

16.图4-20示出了根据本公开的一些方面的在制造工艺的不同阶段的示例性3d存储装置的截面。

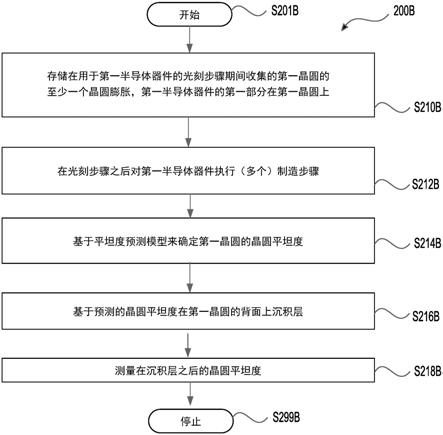

17.图21示出了根据本公开的一些方面的用于形成3d存储装置的示例性方法的流程图。

18.图22示出了根据本公开的一些方面的示例性3d存储装置的截面。

19.图23示出了根据本公开的一些方面的另一示例性3d存储装置的截面。

20.图24示出了根据本公开的一些方面的示例性3d存储装置的截面。

21.图25示出了根据本公开的一些方面的沟道结构的底部的截面。

22.图26示出了根据本公开的一些方面的沟道结构的底部的截面。

23.图27示出了根据本公开的一些方面的沟道结构的底部的截面。

24.图28示出了根据本公开的一些方面的沟道结构的底部的截面。

25.图29-40示出了根据本公开的一些方面的在制造工艺的不同阶段的示例性3d存储装置的截面。

26.图41示出了根据本公开的一些方面的用于形成3d存储装置的示例性方法的流程图。

27.图42示出了根据本公开的一些方面的示例性3d存储装置的截面。

28.图43示出了根据本公开的一些方面的沟道结构的底部的截面。

29.图44-52示出了根据本公开的一些方面的在制造工艺的不同阶段的示例性3d存储

装置的截面。

30.图53示出了根据本公开的一些方面的用于形成3d存储装置的示例性方法的流程图。

31.图54示出了根据本公开的一些方面的具有存储装置的示例性系统的框图。

32.图55a示出了根据本公开的一些方面的具有存储装置的示例性存储卡的示图。

33.图55b示出了根据本公开的一些方面的具有存储装置的示例性固态驱动器(ssd)的示图。

34.将参考附图描述本公开。

具体实施方式

35.尽管讨论了具体的构造和布置,但是应当理解,这样做仅出于说明的目的。这样,在不脱离本公开的范围的情况下,可以使用其他构造和布置。而且,本公开还可以用于多种其他应用中。如在本公开中描述的功能和结构特征可以以未在附图中具体描绘的方式彼此组合、调整和修改,使得这些组合、调整和修改在本公开的范围内。

36.通常,可以至少部分地根据上下文中的使用来理解术语。例如,至少部分地取决于上下文,本文所使用的术语“一个或多个”可以用于以单数意义描述任何特征、结构或特性,或者可以用于以复数意义描述特征、结构或特性的组合。类似地,至少部分地取决于上下文,诸如“一”或“所述”的术语可以同样被理解为传达单数用法或传达复数用法。另外,同样至少部分地取决于上下文,术语“基于”可以被理解为不一定旨在传达一组排他的因素,并且可以代替地允许存在不一定明确描述的附加因素。

37.应该容易理解,本公开中“上”、“上方”和“之上”的含义应该以最广义的方式解释,使得“上”不仅意味着直接在某物“上”,而且还包括在某物“上”并且其间具有中间特征或层的含义,并且“上方”或“之上”不仅意味着在某物“上方”或“之上”的含义,还可以包括在某物“上方”或“之上”并且其间没有中间特征或层(即,直接在某物上)的含义。

38.此外,为了便于描述,在本文中可以使用诸如“下面”、“下方”、“下部”、“上方”、“上部”等空间相对术语,以描述一个元件或特征相对于另一个(或多个)元件或特征的如图中所示的关系。除了在图中描述的取向之外,空间相对术语还旨在涵盖装置在使用或操作中的不同取向。设备可以以其他方式定向(旋转90度或以其他取向),并且本文中使用的空间相对描述语可以类似地被相应地解释。

39.如本文中使用的,术语“层”是指包括具有厚度的区域的材料部分。层可以在整个下层或上层结构之上延伸,或者可以具有小于下层或上层结构的范围的范围。此外,层可以是均质或非均质连续结构的区域,其厚度小于连续结构的厚度。例如,层可以位于连续结构的顶表面和底表面之间、或在连续结构的顶表面和底表面处的任何一对水平面之间。层可以水平、垂直和/或沿着锥形表面延伸。衬底可以是层,可以在其中包括一个或多个层,和/或可以在其上、上方和/或下方具有一个或多个层。层可以包括多层。例如,互连层可以包括一个或多个导体和接触层(在其中形成互连线和/或过孔触点)和一个或多个电介质层。

40.如本文所使用的,术语“衬底”是指在其上添加后续材料层的材料。衬底本身可以被图案化。添加到衬底顶部的材料可以被图案化或可以保持未图案化。此外,衬底可以包括各种各样的半导体材料,例如硅、锗、砷化镓、磷化铟等。替代地,衬底可以由诸如玻璃、塑

料、或蓝宝石晶圆的非导电材料制成。

41.如本文中所使用,术语“3d存储装置”是指在横向取向的衬底上具有垂直取向的存储单元晶体管串(在本文中被称为“存储串”,例如nand存储串),使得存储串相对于衬底在垂直方向上延伸的半导体装置。

42.3d半导体装置可以通过堆叠半导体晶圆或管芯并将它们垂直互连来形成,以使所得结构充当单个装置,从而以与常规平面工艺相比降低的功率和较小的占用面积来实现性能改进。然而,随着3d存储层数量的不断增加,沟道轮廓的控制变得越来越困难

43.图1示出了根据本公开的一些方面的示例性3d存储装置100的截面。如图1所示,3d存储装置100包括堆叠结构111和沿y方向延伸穿过堆叠结构111的沟道结构118。堆叠结构111可以包括交错的导电层105和电介质层107,并且堆叠的导电/电介质层对也被称为存储堆叠体。在一些实施方式中,电介质层107可以包括电介质材料,包括但不限于氧化硅、氮化硅、氮氧化硅或其任何组合。在一些实施方式中,导电层105可以形成字线并且可以包括导电材料,包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物、或其任何组合。

44.沟道结构118可以延伸穿过堆叠结构111,并且沟道结构118的底部可以接触3d存储装置100的源极。在一些实施方式中,沟道结构118可以包括半导体沟道132和形成在半导体沟道132之上的存储膜125。此处“之上”的含义,除了上述解释外,还应被解释为从顶侧或从横向侧在某物“之上”。在一些实施方式中,沟道结构118还可以包括位于沟道结构118中心的电介质芯129。在一些实施方式中,存储膜125可以包括在半导体沟道132之上的隧穿层130、在隧穿层130之上的存储层128、以及在存储层128之上的阻挡层126。

45.根据一些实施方式,电介质芯129、半导体沟道132、隧穿层130、存储层128和阻挡层126以该顺序从沟道结构118的中心向外表面沿径向布置。在一些实施方式中,隧穿层130可以包括氧化硅、氮氧化硅或其任何组合。在一些实施方式中,存储层128可以包括氮化硅、氮氧化硅、硅或其任何组合。在一些实施方式中,阻挡层126可以包括氧化硅、氮氧化硅、高介电常数(高k)电介质或其任何组合。在一个示例中,存储膜可以包括氧化硅/氮氧化硅(或氮化硅)/氧化硅(ono)的复合层。

46.如图1所示,虚设沟道结构124可以形成在沿y方向延伸的堆叠结构111中。在一些实施方式中,接触结构134可以形成在沿y方向延伸的堆叠结构111中。可以理解的是,在实际结构中,可能不会在同一截面中看到堆叠结构111和阶梯区域(包括虚设沟道结构124和/或接触结构134)。为了更好地描述本公开,在本公开的同一附图中示出堆叠结构111和阶梯区域的截面,并且在图1中标注x方向和z方向的坐标以示出堆叠结构111和阶梯区域的截面的垂直度。

47.图2示出根据本公开的一些方面的3d存储装置100的沟道结构118的底部的截面。如图2所示,沟道结构118的底部可以包括半导体沟道132、隧穿层130和存储层128的弯曲结构。在一些实施方式中,位于沟道结构118的底部的阻挡层126与位于沟道结构118的上部的阻挡层126相比,可以具有不同的厚度。在一些实施方式中,阻挡层126在沟道结构118的底部处可以具有厚度w1,阻挡层126在沟道结构118的上部处可以具有厚度w2,并且w1大于w2,如图2所示。

48.在一些实施方式中,阻挡层126可以包括通过形成沟道结构存储膜125所得的电介

质材料和形成第五电介质层116所得的电介质材料,这将在稍后描述。换言之,阻挡层126的厚度w1或阻挡层126的厚度w2可以包括沿x方向形成在存储层128和堆叠结构111的侧壁之间的电介质材料。

49.导电层136可以设置在堆叠结构111下方,如图1和图2所示。在一些实施方式中,导电层136可以是多晶硅层。在一些实施方式中,导电层136与半导体沟道132直接接触。在一些实施方式中,导电层136与半导体沟道132的底表面和半导体沟道132的侧表面的处于沟道结构118的底部的一部分直接接触。在一些实施方式中,包括阻挡层126、存储层128和隧穿层130的存储膜125的底表面处于半导体沟道132的底表面上方,如图2所示。

50.图3示出了根据本公开的一些方面的3d存储装置100的沟道结构118的底部的截面。在一些实施方式中,沟道结构118在3d存储装置100的平面图中是圆形结构。在一些实施方式中,电介质芯129、半导体沟道132、隧穿层130、存储层128和阻挡层126从沟道结构118的中心朝向外表面沿径向布置。如图3所示,与位于沟道结构118的上部的半导体沟道132相比,位于沟道结构118的底部的半导体沟道132可以具有不同的直径。在一些实施方式中,在3d存储装置100的平面图中,半导体沟道132在沟道结构118的底部处可以具有外径w3,半导体沟道132在沟道结构118的上部处可以具有外径w4,并且w3小于w4。在一些实施方式中,半导体沟道132可以在沟道结构118的底部的截面中形成为有角结构131。例如,如图3所示,半导体沟道132可以形成为两个直角结构。在一些实施方式中,半导体沟道132可以形成为钝角结构、锐角结构、直角结构、弧角结构或这些有角结构的任何组合。半导体沟道132在有角结构下方的沟道结构118的底部处的外径w3小于半导体沟道132在有角结构上方的沟道结构118的上部处的外径w4。

51.图4-20示出了根据本公开的一些方面的在制造工艺的不同阶段的3d存储装置100的截面。图21示出了根据本公开的一些方面的用于形成3d存储装置100的示例性方法2100的流程图。为了更好地描述本公开,将一起讨论图4-20中的3d存储装置100的截面和图21中的方法2100。可以理解,方法2100中所示的操作不是穷举的,并且也可以在任何所示操作之前、之后或之间执行其他操作。此外,一些操作可以同时执行,或者以不同于图4-20和图21所示的顺序执行。

52.如图4和图21中的操作2102所示,包括第一电介质层104、第一导电层106、第二电介质层108和第二导电层110的第一堆叠结构101形成在衬底102上。在一些实施方式中,衬底102可以是掺杂半导体层。在一些实施方式中,导电层106可以是多晶硅层,并且导电层110可以是多晶硅层。在一些实施方式中,第一电介质层104和/或第二电介质层108可以包括氧化硅层。在一些实施方式中,第一导电层106可以包括掺杂的多晶硅层。在一些实施方式中,第一导电层106可以包括p掺杂的多晶硅层。在一些实施方式中,第二导电层110可以包括未掺杂的多晶硅层。在一些实施方式中,可以通过一个或多个薄膜沉积工艺依次沉积第一电介质层104、第一导电层106、第二电介质层108和第二导电层110,所述沉积工艺包括但不限于化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其任何组合。在一些实施方式中,第一堆叠结构101可以仅包括一个多晶硅层,例如第一导电层106。

53.在一些实施方式中,在第一堆叠结构101的形成期间,可以对第一导电层106和第二导电层110执行氨(nh3)处理。在一些实施方式中,可以在第一导电层106和第二导电层110的顶表面上执行nh3处理。在一些实施方式中,在第一导电层106和第二导电层110的顶

表面上执行nh3处理可以防止在随后的氧化工艺中在第一导电层106和第二导电层110上沿x方向形成氧化物层。

54.如图5和图21中的操作2104所示,包括交替布置的多个第三电介质层107和多个牺牲层109的第二堆叠结构103形成在第一堆叠结构101上。电介质/牺牲层对可以包括沿x方向和垂直于y方向的平面延伸的交错的第三电介质层107和牺牲层109。在一些实施方式中,每个第三电介质层107可以包括氧化硅层,并且每个牺牲层109可以包括氮化硅层。第二堆叠结构103可以通过一种或多种薄膜沉积工艺形成,所述沉积工艺包括但不限于cvd、pvd、ald或其任何组合。

55.进一步参考图5和图21中的操作2106,在第二堆叠结构103和第一堆叠结构101中沿第一方向(y方向)形成沟道孔112。在一些实施方式中,沟道孔112可以穿透第二堆叠结构103并延伸到第一导电层106的顶表面。在一些实施方式中,沟道孔112可以延伸到第一导电层106的中间,如图20所示。在一些实施方式中,沟道孔112可以穿透第二堆叠结构103和第一导电层106并且暴露衬底,如图5所示。如图5所示,第一电介质层、第一导电层106、第二电介质层和第二导电层110被沟道孔112的侧壁暴露。在一些实施方式中,用于形成沟道孔112的制造工艺可以包括湿法蚀刻和/或干法蚀刻,例如深反应离子蚀刻(drie)。在一些实施方式中,沟道孔112可以进一步延伸到衬底的顶部中。

56.如图6和图21中的操作2108所示,执行氧化操作以在由沟道孔112的侧壁暴露的第一导电层106上形成第四电介质层114。在一些实施方式中,因为在第一堆叠结构的形成期间在第一导电层106和第二导电层110的顶表面上执行nh3处理,第四电介质层114可以沿x方向(其为垂直于y方向的平面)形成在被沟道孔112的侧壁暴露的第一导电层106上。

57.在3d存储装置100的平面图中,沟道孔112可以是圆形,并且暴露的侧壁是圆形的圆周。在一些实施方式中,第四电介质层114的形成从第一导电层106上的圆形的圆周开始,并且然后延伸到圆形的中心。

58.在一些实施方式中,基于第四电介质层114的形成速度,在沟道孔112中的第一导电层106的一侧上形成的第四电介质层114可以与在第一导电层106的另一侧上形成的第四电介质层114接触。在一些实施方式中,形成在沟道孔112中的第一导电层106的一侧上的第四电介质层114可以通过间隙与形成在第一导电层106的另一侧上的第四电介质层114分开。可以理解,这里描述的沟道孔112的一侧或另一侧是从截面图的视角来看。在实际结构中,从平面图来看,沟道孔112可以是孔,形成在第一导电层106上的第四电介质层114可以从周边向中心形成。在一些实施方式中,在平面图中,形成在第一导电层106上的第四电介质层114可以覆盖整个沟道孔112。在一些实施方式中,在平面图中,形成在第一导电层106上的第四电介质层114在沟道孔112的中心可以具有间隙(孔)。在一些实施方式中,间隙的宽度可以在形成操作期间进行控制,并且间隙的大小可以进一步带来在后续工艺中形成的存储膜的各种结构。在一些实施方式中,可以控制间隙的宽度以使部分存储膜或整个存储膜填充在间隙中。例如,可以形成阻挡层,以填充间隙。

59.在一些实施方式中,第五电介质层116可以形成在由沟道孔112的侧壁暴露的第二导电层110上。因为第一导电层106包括掺杂的多晶硅,并且第二导电层110包括未掺杂的多晶硅,所以第四电介质层114的形成速度可以高于第五电介质层116。因此,第四电介质层114的面积可以大于第五电介质层116的面积。可以理解,在图6的截面图中,第五电介质层

116从第二导电层110的两侧形成,然而,在该结构的平面图中,第五电介质层116从周边向中心形成在第二导电层110上。

60.如图7和图21中的操作2110所示,沟道结构118可以形成在沟道孔112中。沟道结构118可以包括存储膜125和半导体沟道132。在一些实施方式中,沟道结构118还可以包括在沟道结构118的中心的电介质芯129。在一些实施方式中,存储膜125是包括隧穿层130、存储层128(也称为“电荷陷阱层”)和阻挡层126的复合层。沟道结构118可以具有圆柱形状(例如,柱形状),并且圆柱形状的底部可以在具有形成在沟道孔112的侧壁上的第五电介质层116的部分处收缩。在一些实施方式中,沟道结构118可以是锥形形状,并且锥形形状的底部小于锥形形状的上部。在这种情况下,锥形形状的底部可以在具有形成在沟道孔112的侧壁上的第五电介质层116的部分处收缩。

61.根据一些实施方式,电介质芯129、半导体沟道132、隧穿层130、存储层128和阻挡层126以该顺序从柱的中心朝向外表面沿径向布置。在一些实施方式中,隧穿层130可以包括氧化硅、氮氧化硅或其任何组合。在一些实施方式中,存储层128可以包括氮化硅、氮氧化硅、硅或其任何组合。在一些实施方式中,阻挡层126可以包括氧化硅、氮氧化硅、高介电常数(高k)电介质或其任何组合。在一个示例中,存储膜125可以包括氧化硅/氮氧化硅(或氮化硅)/氧化硅(ono)的复合层。

62.如图7所示,还可以在第二堆叠结构103和第一堆叠结构101中沿y方向形成栅缝隙开口120。栅缝隙开口120可以通过执行干法蚀刻、湿法蚀刻或其他合适的工艺来形成。在一些实施方式中,栅缝隙开口120可以延伸到衬底102。

63.如图8所示,可以进一步在栅缝隙开口120中执行多晶硅氧化操作,以在第一导电层106上形成氧化物层121,在由栅缝隙开口120暴露的第二导电层110上形成氧化物层123。形成在第一导电层106和第二导电层110上的氧化物层121和123可以在字线替换操作的后续蚀刻工艺期间保护第一导电层106和第二导电层110。

64.如图9所示,执行字线替换操作,并且可以去除牺牲层109并用字线105替换牺牲层109,字线105是图1中的导电层105。例如,可以通过干法蚀刻、湿法蚀刻或其他合适的工艺去除牺牲层109以形成多个空腔。可以通过依次沉积由高k电介质材料制成的栅极电介质层、包括钛/氮化钛(ti/tin)或钽/氮化钽(ta/tan)的粘附层、以及由钨制成的栅极导体来在所述空腔中形成字线105。在字线替换操作之后,形成堆叠结构111,如图9所示。

65.如图10所示,可以执行去除工艺以清洁栅缝隙开口120。去除工艺可以从栅缝隙开口120去除先前工序的残留物。例如,可以从栅缝隙开口120中去除高k电介质材料。

66.如图11所示,栅缝隙133可以形成在栅缝隙开口120中。在一些实施方式中,栅缝隙133可以包括电介质层。在一些实施方式中,栅缝隙133还可以包括一个或多个导电层,例如多晶硅、钨(w)或多晶硅和w的组合。

67.如图12所示,虚设沟道结构124可以形成在沿y方向延伸的堆叠结构111中。在一些实施方式中,接触结构134可以形成在沿y方向延伸的堆叠结构111中。在一些实施方式中,接触结构134可以与第二导电层110接触。

68.在一些实施方式中,栅缝隙133可以在字线替换操作之前形成。在一些实施方式中,在衬底102上形成栅缝隙133、虚设沟道结构124和接触结构134之后,还可以在存储阵列上形成一个或多个互连层。此外,外围电路可以形成于另一衬底上,并在后续工艺中与存储

阵列键合。

69.如图13和图21中的操作2112所示,执行衬底去除操作。在一些实施方式中,可以通过湿法蚀刻、干法蚀刻或其他合适的工艺去除衬底102,直到被第一电介质层104停止为止。当使用湿法蚀刻去除衬底102时,沟道结构118的底表面高于栅缝隙133和虚设沟道结构124的底表面,因此在最终结构中,半导体沟道132的底表面高于栅缝隙133和虚设沟道结构124的底表面。在一些实施方式中,可以通过化学机械抛光(cmp)工艺去除衬底102,并且可以一起去除栅缝隙133和虚设沟道结构124的底部,如图22和图23所示。

70.在一些实施方式中,可以剥离衬底102。在其中衬底102包括硅并且停止层(第一电介质层104)包括例如氧化硅或氮化硅的电介质层的一些实施方式中,可以使用硅cmp来去除衬底102,当到达具有除硅以外的材料的停止层时,硅cmp可以自动停止,即,充当背面cmp停止层。在一些实施方式中,使用通过四甲基铵(tmah)进行的湿法蚀刻来去除衬底102,当到达具有除硅以外的材料的停止层时,湿法蚀刻自动停止,即,充当背面蚀刻停止层。

71.然后,如图14和图21中的操作2114所示,去除第一电介质层104和第四电介质层114。在一些实施方式中,第一电介质层104和第四电介质层114可以通过湿法蚀刻、干法蚀刻、cmp或其他合适的工艺来去除。在去除第一电介质层104和第四电介质层114之后,沟道结构118的底部被暴露。在一些实施方式中,栅缝隙133的电介质层的底部也被去除。在一些实施方式中,阻挡层126的一部分也可以与第四电介质层114一起被去除。

72.因为沟道结构118形成在第四电介质层114上,如图7所示,并且通过多晶硅氧化操作形成第四电介质层114,如图6所示,在去除第一电介质层104和第四电介质层114之前,沟道结构118的底部(其为阻挡层126的最底部位置)可以被控制为与第一导电层106的顶表面共面,或者略高于第一导电层106的顶表面。在随后的工艺中去除部分存储膜之后,半导体沟道132的底表面可以在第一导电层106上方,与第二导电层110的底表面共面,与第二导电层110的顶表面共面,在第二导电层110的底表面和顶表面之间,与第三电介质层107中的最底层的底表面共面,或在第三电介质层107中的最底层的底表面上方。因此,通过使用在第一导电层106上执行的多晶硅氧化操作,可以将沟道结构118的深度控制在预定范围内,并且沟道结构118的深度或底部轮廓不会受到沟道孔112中形成的残留物的影响。因此改善了沟道轮廓的控制。

73.然后,如图15和图21中的操作2112所示,去除第一导电层106。在一些实施方式中,可以通过湿法蚀刻、干法蚀刻、cmp或其他合适的工艺来去除第一导电层106。

74.如图16所示,去除第二电介质层108以暴露第二导电层110,并且去除存储膜的部分以暴露隧穿层130、存储层128和阻挡层126的部分。在一些实施方式中,通过一次蚀刻工艺去除存储膜的部分和第二电介质层108。在一些实施方式中,通过多次蚀刻工艺去除存储膜的部分和第二电介质层108。例如,可以首先去除第二电介质层108。使用利用合适的蚀刻剂(例如磷酸)的湿法蚀刻来选择性地去除包括氮化硅的存储层128,而不蚀刻第二导电层110。可以通过控制蚀刻时间和/或蚀刻速率来控制存储层128的蚀刻,使得蚀刻不会继续影响存储层128的被存储堆叠体包围的其余部分。然后,可以使用利用合适的蚀刻剂(例如氢氟酸)的湿法蚀刻来选择性地去除包括氧化硅的阻挡层126和隧穿层130,而不蚀刻包括多晶硅的第二导电层110和半导体沟道132。可以通过控制蚀刻时间和/或蚀刻速率来控制阻挡层126和隧穿层130的蚀刻,使得蚀刻不会继续影响阻挡层126和隧穿层130的被存储堆叠

体包围的其余部分。在一些实施方式中,在去除存储膜的部分之后,隧穿层130、存储层128和阻挡层126的暴露部分的底表面处于半导体沟道132的底表面上方。

75.在一些实施方式中,在操作2112中,第一电介质层104、第四电介质层114和第一导电层106的去除顺序可以不同。在一些实施方式中,在去除如图13所示的衬底102之后,可以单独去除第一电介质层104并且可以保留第四电介质层114。然后,去除第四电介质层114周围的第一导电层106。之后,可以在同一工艺中去除第四电介质层114和第二电介质层108。

76.因为在沟道结构118的形成期间,第五电介质层116在沟道孔112的侧壁上沿x方向形成突起,沟道结构118的圆柱形状的底部受到第五电介质层116影响并形成收缩结构或下陷,如图7所示。在去除存储膜的底部之后,在一些实施方式中,隧穿层130和存储层128的暴露部分可以具有小于位于沟道结构118的上部的隧穿层130和存储层128的临界尺寸(或从平面图看的直径),如图16所示。此外,在一些实施方式中,位于沟道结构118的底部的半导体沟道132的暴露部分也具有小于位于沟道结构118的上部的半导体沟道132的临界尺寸(或从平面图中看的直径),如图16所示。

77.在一些实施方式中,可以通过cmp工艺去除第二电介质层108,并且栅缝隙133的底表面和虚设沟道结构124的底表面可以与第二导电层110的底表面共面或基本共面,如图22或图23所示。

78.因为第五电介质层116通过多晶硅氧化操作形成在第二导电层110上,如图6所示,并且此后存储膜形成在第五电介质层116上,阻挡层126、存储层128和隧穿层130沿y方向可以不是平直结构。阻挡层126的底部的宽度w1可以大于阻挡层126的上部的宽度w2,如图16所示。此外,存储层128和隧穿层130可以在存储膜的底部形成有角结构。

79.如图17所示,第三导电层136形成在暴露的沟道结构118和第二导电层110之上。在一些实施方式中,第三导电层136可以是多晶硅层。在一些实施方式中,第三导电层136可以通过cvd、pvd、ald或其他合适的工艺形成。

80.如图18所示,形成穿硅触点(tsc)以暴露接触结构。如图19所示,形成与接触结构134接触或与第三导电层136接触的接触焊盘138。

81.图22示出了根据本公开的一些方面的另一示例性3d存储装置200的截面。图22中所示的3d存储装置200包括沟道结构118、栅缝隙133和虚设沟道结构124。栅缝隙133的底部和虚设沟道结构124的底部可以与第二导电层110的底表面共面或基本共面。在一些实施方式中,栅缝隙133的底部和虚设沟道结构124的底部可以与半导体沟道132的底表面共面或基本共面。例如,在一些实施方式中,在第一电介质层104、第一导电层106和/或第二电介质层108的去除操作期间,栅缝隙133的底部和虚设沟道结构124的底部可以与沟道结构118一起被去除。在一些实施方式中,栅缝隙133的底表面和虚设沟道结构124的底表面可以与第二导电层110的底表面共面或略高于第二导电层110的底表面,如图22所示。

82.图23示出了根据本公开的一些方面的又一示例性3d存储装置300的截面。沟道结构118的底表面,例如半导体沟道132的底表面,可以在第二导电层110的顶表面上方,如图23所示。在一些实施方式中,沟道结构118的底表面,例如半导体沟道132的底表面,可以与第二导电层110的顶表面共面。在一些实施方式中,沟道结构118的底表面,例如,半导体沟道132的底表面,可以在第二导电层110的顶表面下方,如图22所示。

83.通过在由沟道孔112的侧壁暴露的第一导电层106上形成第四电介质层114,沟道

孔112可以被第四电介质层114完全或部分地填充。因此,沟道结构118的底部可以由第四电介质层114和第一导电层106的位置限定。沟道结构118的底部不会受到沟道孔蚀刻挖槽的影响,并且因此沟道孔的形成的工艺窗口将大大增加。

84.图24示出了根据本公开的一些方面的示例性3d存储装置400的截面。如图24所示,3d存储装置400包括堆叠结构402和沿y方向延伸穿过堆叠结构402的沟道结构404。堆叠结构402可以包括交错的导电层和电介质层,其类似于3d存储装置100的堆叠结构111。在一些实施方式中,堆叠结构402的形成和材料可以类似于堆叠结构111的形成和材料。

85.图25示出了根据本公开的一些方面的3d存储装置400的沟道结构404的底部的截面。沟道结构404可以延伸穿过堆叠结构402,并且沟道结构404的底部可以接触3d存储装置400的源极。在一些实施方式中,沟道结构404可以包括半导体沟道132和形成在半导体沟道132之上的存储膜125,其类似于3d存储装置100的沟道结构118。然而,沟道结构404的底部的结构不同于沟道结构118。在一些实施方式中,沟道结构404还可以包括位于沟道结构404中心的电介质芯129。在一些实施方式中,存储膜125可以包括半导体沟道132之上的隧穿层130、隧穿层130之上的存储层128和存储层128之上的阻挡层126。

86.如图25所示,沟道结构404的底部412可以包括阻挡层126、隧穿层130和存储层128的弯曲结构。在一些实施方式中,在3d存储装置400的平面图中,沟道结构404的底部412可以具有外径w5,并且沟道结构404的上部414可以具有外径w6。在一些实施方式中,w5小于w6。在一些实施方式中,存储膜125可以包括有角结构422,并且存储膜125在有角结构422下方的底部处的外径w5小于存储膜125在有角结构422上方的上部处的外径w6。例如,如图25所示,存储膜125可以形成为两个直角结构。在一些实施方式中,存储膜125可以形成为钝角结构、锐角结构、直角结构、弧角结构或这些有角结构的任何组合。

87.在一些实施方式中,在3d存储装置400的平面图中,沟道结构404的底部412中的半导体沟道132可以具有外径w7,并且沟道结构404的上部414中的半导体沟道132可以具有外径w8。在一些实施方式中,w7小于w8。在一些实施方式中,半导体沟道132可以包括有角结构424,并且半导体沟道132在有角结构424下方的沟道结构404的底部处的外径w7小于半导体沟道132在有角结构424上方的沟道结构404的上部处的外径w8。例如,如图25所示,半导体沟道132可以形成为一个直角结构。在一些实施方式中,半导体沟道132可以形成为钝角结构、锐角结构、直角结构、弧角结构或这些有角结构的任何组合。

88.3d存储装置400可以进一步包括与堆叠结构402直接接触的导电层406,以及设置在导电层406下方的掺杂导电层408。在一些实施方式中,导电层406可以是多晶硅层,并且掺杂导电层408可以是掺杂的多晶硅层。在一些实施方式中,3d存储装置400可以进一步包括设置在导电层406与沟道结构404的底部412之间的电介质层410。在3d存储装置400的平面图中,电介质层410可以围绕沟道结构404的底部412,并且导电层406可以围绕电介质层410。掺杂导电层408设置在导电层406、电介质层410和沟道结构404下方。在一些实施方式中,掺杂导电层408可以与存储膜125和半导体沟道132的底表面直接接触。在一些实施方式中,电介质芯129仅形成在沟道结构404的上部414中。

89.图26示出了根据本公开的一些方面的3d存储装置500的另一沟道结构504的底部的截面。3d存储装置500的沟道结构504(包括上部514)类似于3d存储装置400的沟道结构404,但沟道结构504的底部512不同。如图26所示,掺杂导电层408的一部分延伸到导电层

406中。掺杂导电层408的延伸部分围绕沟道结构504的底部512。导电层406进一步围绕掺杂导电层408的延伸部分。在一些实施方式中,存储膜125的底表面与掺杂导电层408直接接触。在一些实施方式中,多晶硅层406的顶表面与掺杂多晶硅层408的顶表面和存储膜125的底表面共面。

90.图27示出了根据本公开的一些方面的3d存储装置600的沟道结构604的底部的截面。在一些实施方式中,3d存储装置600的沟道结构604可以类似于3d存储装置400的沟道结构404,但是3d存储装置600不包括导电层406下方的掺杂多晶硅层。在一些实施方式中,3d存储装置600的沟道结构604可以直接耦合到互连结构。例如,3d存储装置600的沟道结构604可以直接耦合到焊盘引出结构而不在沟道结构下方形成掺杂多晶硅层。

91.图28示出了根据本公开的一些方面的3d存储装置700的沟道结构704的底部的截面。在一些实施方式中,3d存储装置700的沟道结构704可以类似于3d存储装置500的沟道结构504,但是3d存储装置700的掺杂导电层408可以不形成在导电层406下方。如图28所示,3d存储装置700的掺杂导电层408可以围绕沟道结构704的底部512。导电层406进一步围绕掺杂导电层408。在一些实施方式中,3d存储装置700的沟道结构704可以直接耦合到互连结构。例如,3d存储装置700的沟道结构704可以直接耦合到焊盘引出结构而不在导电层406下方形成掺杂多晶硅层。

92.图29-40示出了根据本公开的一些方面的在制造工艺的不同阶段的3d存储装置400的截面。图41示出了根据本公开的一些方面的用于形成3d存储装置400的示例性方法4100的流程图。为了更好地描述本公开,将一起讨论图29-40中的3d存储装置400的截面和图41中的方法4100。可以理解,方法4100中所示的操作不是穷举的,并且也可以在任何所示操作之前、之后或之间执行其他操作。此外,一些操作可以同时执行,或者以与图29-40和图41所示不同的顺序执行。

93.如图29和图41中的操作4102所示,包括电介质层456和导电层406的堆叠结构452形成在衬底458上。在一些实施方式中,衬底458可以是掺杂半导体层。在一些实施方式中,电介质层456可以包括氧化硅或氮化硅层。在一些实施方式中,导电层406可以包括掺杂多晶硅层或未掺杂多晶硅层。在一些实施方式中,可以通过一种或多种薄膜沉积工艺依次沉积电介质层456和导电层406,所述如图14和图21中的操作2114所示包括但不限于cvd、pvd、ald或其任何组合。

94.然后,如图29和图41中的操作4104所示,包括交替布置的多个电介质层462和多个牺牲层460的堆叠结构454形成在堆叠结构452上。电介质/牺牲层对可以包括沿x方向和垂直于y方向的平面延伸的交错的电介质层462和牺牲层460。在一些实施方式中,每个电介质层462可以包括氧化硅层,并且每个牺牲层460可以包括氮化硅层。可以通过一种或多种薄膜沉积工艺形成堆叠结构454,所述沉积工艺包括但不限于cvd、pvd、ald或其任何组合。

95.如图30和图41中的操作4106所示,形成沿y方向穿透堆叠结构454和堆叠结构452的沟道孔464,并且衬底458被沟道孔464暴露。在一些实施方式中,用于形成沟道孔464的制造工艺可以包括湿法蚀刻和/或干法蚀刻,例如深反应离子蚀刻(drie)。

96.然后,如图30和图41中的操作4108所示,执行氧化操作以在由沟道孔464的侧壁暴露的导电层406上形成电介质层410。在一些实施方式中,电介质层410进一步形成在衬底458上的沟道孔464的底部上。在一些实施方式中,电介质层410进一步形成在电介质层456

上。在一些实施方式中,电介质层410沿x方向形成在导电层406上。如图30所示,在形成电介质层410之后,沟道孔464在具有形成于侧壁上的电介质层410的部分处具有宽度w9(或平面图中的直径),而在没有形成于侧壁上的电介质层410的部分处具有宽度w10。在一些实施方式中,宽度w9小于宽度w10。

97.如图31和图41中的操作4110所示,沟道结构404可以形成在沟道孔464中。沟道结构404可以包括存储膜125和半导体沟道132。在一些实施方式中,存储膜125是包括隧穿层130、存储层128(也称为“电荷陷阱层”)和阻挡层126的复合层,如图25所示。沟道结构404可以具有圆柱形状(例如,柱形状),并且圆柱形状的底部可以在具有形成在沟道孔464的侧壁上的电介质层410的部分处收缩。沟道结构404的形成可以包括在沟道孔464中共形地形成存储膜125,然后在存储膜125之上的沟道孔464中形成半导体沟道132,如图41中的操作4112所示。如图31所示,因为沟道孔464在具有形成在侧壁上的电介质层410的部分处具有较小的宽度w9,所以半导体沟道132可以在沟道孔的具有形成在侧壁上的电介质层410的部分处完全填充沟道孔464。

98.如图32所示,可以对薄半导体沟道132执行多晶硅回蚀刻操作,并且可以在沟道结构404的中心形成电介质芯129。根据一些实施方式,电介质芯129、半导体沟道132、隧穿层130、存储层128和阻挡层126以该顺序从柱的中心朝向外表面沿径向布置。因为半导体沟道132可以在沟道孔的具有形成在侧壁上的电介质层410的部分处完全填充沟道孔464,所以可以在半导体沟道132的完全填充部分上方形成电介质芯129。在一些实施方式中,隧穿层130可以包括氧化硅、氮氧化硅或其任何组合。在一些实施方式中,存储层128可以包括氮化硅、氮氧化硅、硅或其任何组合。在一些实施方式中,阻挡层126可以包括氧化硅、氮氧化硅、高介电常数(高k)电介质或其任何组合。在一个示例中,存储膜125可以包括氧化硅/氮氧化硅(或氮化硅)/氧化硅(ono)的复合层。

99.如图33所示,可以形成栅缝隙466。可以首先形成垂直延伸穿过堆叠结构454和堆叠结构452的开口缝隙。在一些实施例中,用于形成缝隙的制造工艺可以包括湿法蚀刻和/或干法蚀刻,例如drie。然后可以通过缝隙执行栅极替换工艺以用字线结构替换牺牲层460。绝缘结构可以完全或部分地填充在缝隙中(有或没有气隙),以使用一种或多种薄膜沉积工艺形成栅缝隙466,所述沉积工艺例如ald、cvd、pvd、任何其他合适的工艺或其任何组合。

100.在形成栅缝隙466之后,形成包括沟道局部触点468和字线局部触点470的局部触点以及外围触点472。可以通过使用一种或多种薄膜沉积工艺(例如cvd、pvd、ald或其任何组合)在堆叠结构402的顶部沉积诸如氧化硅或氮化硅的电介质材料而在堆叠结构402上形成局部电介质层。可以通过使用湿法蚀刻和/或干法蚀刻(例如,rie)穿过局部电介质层(和任何其他层间电介质(ild)层)蚀刻出接触开口,然后使用一种或多种薄膜沉积工艺(例如ald、cvd、pvd、任何其他合适的工艺或其任何组合)用导电材料填充接触开口来形成沟道局部触点468、字线局部触点470和外围触点472。

101.如图34所示,键合层474形成在沟道局部触点468、字线局部触点470和外围触点472上方。键合层474可以包括电连接到沟道局部触点468、字线局部触点470和外围触点472的键合触点。然后,如图35所示,存储堆叠体和外围电路476以面对面的方式键合。在一些实施例中,在键合之前将例如等离子体处理、湿法处理和/或热处理的处理工艺施加于键合表

面。

102.如图36和图41中的操作4114所示,去除衬底458以暴露电介质层456。在一些实施方式中,可以使用cmp、研磨、干法蚀刻和/或湿法蚀刻完全去除衬底458。在一些实施例中,衬底458被剥离。在衬底458包括硅的一些实施例中,电介质层456可以用作停止层,例如氮化硅,当使用硅cmp去除衬底458时,当到达具有除硅以外的材料的电介质层456时,硅cmp可以自动停止,即,充当背面cmp停止层。在一些实施例中,使用通过四甲基铵(tmah)进行的湿法蚀刻来去除衬底458(硅衬底),当到达具有除硅以外的材料的电介质层456时,湿法蚀刻自动停止,即,充当背面蚀刻停止层。电介质层456可以确保衬底458的完全去除,而无需担心减薄后的厚度均匀性。

103.如图37和图41中的操作4114所示,在一些实施方式中,在去除衬底458之后,可以进一步执行平坦化操作,例如cmp,以去除电介质层456、存储膜125的一部分和半导体沟道132的一部分。在一些实施方式中,在去除电介质层456之后,导电层406的上表面与电介质层410、存储膜125和半导体沟道132的顶表面共面。

104.如图38所示,可以在半导体沟道132上执行注入操作以掺杂半导体沟道132的多晶硅材料的顶部,然后可以在导电层406、电介质层410、存储膜125和半导体沟道132上形成掺杂导电层408。在一些实施方式中,可以在掺杂导电层408上进一步执行激活操作,例如激光激活操作。在一些实施方式中,掺杂导电层408与电介质层410、存储膜125和半导体沟道132直接接触。

105.如图39和图41中的操作4116所示,形成与半导体沟道132接触的互连结构。可以在掺杂导电层408上形成ild层480,然后可以在ild层480中形成源极接触开口。在源极接触开口中形成源极触点478。在一些实施方式中,形成延伸穿过ild层480并与外围触点接触的触点482。如图40所示,再分布层484形成在源极触点478和触点482之上。

106.图42示出了根据本公开的一些方面的示例性3d存储装置800的截面。如图42所示,3d存储装置800包括堆叠结构802和沿y方向延伸穿过堆叠结构802的沟道结构804。堆叠结构802可以包括交错的导电层和电介质层,其类似于3d存储装置100的堆叠结构111。在一些实施方式中,堆叠结构802的形成和材料可以类似于堆叠结构111的形成和材料。

107.图43示出了根据本公开的一些方面的3d存储装置800的沟道结构804的底部的截面。沟道结构804可以延伸穿过堆叠结构802,并且沟道结构804的底部可以接触3d存储装置800的源极。在一些实施方式中,沟道结构804可以包括半导体沟道132和形成在半导体沟道132之上的存储膜125,半导体沟道132类似于3d存储装置100的沟道结构118。然而,沟道结构804的底部的结构不同于沟道结构118。在一些实施方式中,沟道结构804还可以包括位于沟道结构804中心的电介质芯129。在一些实施方式中,存储膜125可以包括半导体沟道132之上的隧穿层130、隧穿层130之上的存储层128和存储层128之上的阻挡层126。

108.如图43所示,沟道结构804的底部812可以包括阻挡层126、隧穿层130和存储层128的弯曲结构。在一些实施方式中,在3d存储装置800的平面图中,沟道结构804的底部812可以具有直径w11,并且沟道结构804的上部814可以具有直径w12。在一些实施方式中,w11小于w12。在一些实施方式中,在3d存储装置800的平面图中,电介质芯129在沟道结构804的底部812中可以具有直径w13,并且电介质芯129在沟道结构804的上部814中可以具有直径w14。在一些实施方式中,w13小于w14。

109.3d存储装置800还可以包括与堆叠结构802直接接触的导电层806,以及设置在导电层806下方的掺杂导电层808。在一些实施方式中,导电层806可以是多晶硅层,并且掺杂导电层808可以是掺杂多晶硅层。在一些实施方式中,掺杂导电层808的一部分可以延伸到导电层806中。如图43所示,半导体沟道132的底部可以延伸到掺杂导电层808的延伸部分中,并且掺杂导电层808的延伸部分围绕半导体沟道132的底部812。导电层806进一步围绕掺杂导电层808的延伸部分。在一些实施方式中,存储膜125的底表面与掺杂导电层808直接接触。在一些实施方式中,导电层806的顶表面与掺杂导电层808的顶表面和存储膜125的底表面共面。

110.3d存储装置800的沟道结构804与3d存储装置400的沟道结构404之间的差异在于沟道结构的底部的结构。如图43所示,电介质芯129可以填充在沟道结构804的窄部(底部812)处的半导体沟道132之间;然而,电介质芯129可以形成在沟道结构404的窄部(底部412)处的半导体沟道132上方。差异可能是由存储膜125和半导体沟道132的形成工艺引起的。当半导体沟道132形成为完全填充沟道孔的窄部时,稍后形成的电介质芯129可以形成在半导体沟道132上方。当半导体沟道132形成为部分填充沟道孔的窄部时,稍后形成的电介质芯129可以填充在半导体沟道132之间。

111.通过在由沟道孔464的侧壁暴露的导电层406上形成电介质层410,沟道结构404的底部可以由电介质层410和导电层406的位置限定。沟道结构404的底部将不受沟道孔蚀刻挖槽的影响,因此沟道孔形成的工艺窗口将大大增加。

112.图44-52示出了根据本公开的一些方面的在制造工艺的不同阶段的3d存储装置800的截面。图53示出了根据本公开的一些方面的用于形成3d存储装置800的示例性方法5300的流程图。为了更好地描述本公开,将一起讨论图44-52中的3d存储装置800的截面和图53中的方法5300。可以理解,方法5300中所示的操作不是穷举的,并且也可以在任何所示操作之前、之后或之间执行其他操作。此外,一些操作可以同时执行,或者以不同于图44-52和图53所示的顺序执行。

113.如图44和图53中的操作5302所示,包括电介质层856和导电层806的堆叠结构852形成在衬底858上。在一些实施方式中,衬底858可以是掺杂半导体层。在一些实施方式中,电介质层856可以包括氧化硅或氮化硅层。在一些实施方式中,导电层806可以包括掺杂多晶硅层或未掺杂多晶硅层。在一些实施方式中,可以通过一种或多种薄膜沉积工艺依次沉积电介质层856和导电层806,所述沉积工艺包括但不限于cvd、pvd、ald或其任何组合。

114.然后,如图44和图53中的操作5304所示,包括交替布置的多个电介质层862和多个牺牲层860的堆叠结构854形成在堆叠结构852上。电介质/牺牲层对可以包括沿x方向和垂直于y方向的平面延伸的交错的电介质层862和牺牲层860。在一些实施方式中,每个电介质层862可以包括氧化硅层,并且每个牺牲层860可以包括氮化硅层。可以通过一种或多种薄膜沉积工艺形成堆叠结构854,所述沉积工艺包括但不限于cvd、pvd、ald或其任何组合。

115.如图44和图53中的操作5306所示,形成沿y方向穿透堆叠结构854和堆叠结构852的沟道孔864,并且衬底858被沟道孔864暴露。在一些实施方式中,用于形成沟道孔464的制造工艺可以包括湿法蚀刻和/或干法蚀刻,例如深反应离子蚀刻(drie)。

116.然后,如图44和图53中的操作5308所示,执行氧化操作以在由沟道孔864的侧壁暴露的导电层806上形成电介质层810。在一些实施方式中,电介质层810进一步形成在衬底

858上的沟道孔864的底部上。在一些实施方式中,电介质层810进一步形成在电介质层856上。在一些实施方式中,电介质层810沿x方向形成在导电层806上。如图44所示,在形成电介质层810之后,沟道孔864在具有形成于侧壁上的电介质层810的部分处具有宽度w15(或平面图中的直径),而在没有形成于侧壁上的电介质层810的另一部分处具有宽度w16。在一些实施方式中,宽度w15小于宽度w16。

117.如图45和图53中的操作5310所示,沟道结构804可以形成在沟道孔864中。沟道结构804可以包括存储膜125和半导体沟道132。在一些实施方式中,存储膜125是包括隧穿层130、存储层128(也称为“电荷陷阱层”)和阻挡层126的复合层,如图43所示。沟道结构804可以具有圆柱形状(例如,柱形状),并且圆柱形状的底部可以在具有形成在沟道孔864的侧壁上的电介质层810的部分处收缩。沟道结构804的形成可以包括在沟道孔864中共形地形成存储膜125,然后在存储膜125之上的沟道孔864中形成半导体沟道132,如图53中的操作5312所示。如图45所示,因为沟道孔864在具有形成在侧壁上的电介质层810的部分处具有较小的宽度w15,所以半导体沟道132可以在沟道孔的具有形成在侧壁上的电介质层810的部分处完全填充沟道孔864。

118.可以对薄半导体沟道132执行多晶硅回蚀刻操作,并且可以在沟道结构804的中心形成电介质芯129。因为半导体沟道132可以在沟道孔的具有形成在侧壁上的电介质层810的部分处完全填充沟道孔864,所以电介质芯129可以沟道孔的具有形成在侧壁上的电介质层810的部分处完全填充沟道结构804的中心,如图53中的操作5312所示。根据一些实施方式,电介质芯129、半导体沟道132、隧穿层130、存储层128和阻挡层126以该顺序从柱的中心朝向外表面沿径向布置。在一些实施方式中,隧穿层130可以包括氧化硅、氮氧化硅或其任何组合。在一些实施方式中,存储层128可以包括氮化硅、氮氧化硅、硅或其任何组合。在一些实施方式中,阻挡层126可以包括氧化硅、氮氧化硅、高介电常数(高k)电介质或其任何组合。在一个示例中,存储膜125可以包括氧化硅/氮氧化硅(或氮化硅)/氧化硅(ono)的复合层。

119.如图46所示,可以形成栅缝隙866,并且然后可以执行栅极替换以用字线结构替换牺牲层860。绝缘结构可以完全或部分地填充在缝隙中(有或没有气隙)以使用一种或多种薄膜沉积工艺(例如ald、cvd、pvd、任何其他合适的工艺或其任何组合)来形成栅缝隙866。

120.在形成栅缝隙866之后,形成包括沟道局部触点868和字线局部触点870的局部触点以及外围触点872。通过使用一种或多种薄膜沉积工艺(例如cvd、pvd、ald或其任何组合)在堆叠结构802的顶部沉积诸如氧化硅或氮化硅的电介质材料,可以在堆叠结构802上形成局部电介质层。可以通过使用湿法蚀刻和/或干法蚀刻(例如rie)穿过局部电介质层(和任何其他ild层)蚀刻出接触开口,接着使用一种或多种薄膜沉积工艺(例如ald、cvd、pvd、任何其他合适的工艺或其任何组合)用导电材料填充接触开口,来形成沟道局部触点868、字线局部触点870和外围触点872。

121.键合层874形成在沟道局部触点868、字线局部触点870和外围触点872上方。键合层874可以包括电连接到沟道局部触点868、字线局部触点870和外围触点872的键合触点。然后,如图47所示,存储堆叠体和外围电路876以面对面的方式键合。在一些实施例中,在键合之前将处理工艺(例如等离子体处理、湿法处理和/或热处理)施加于键合表面。

122.如图48和图53中的操作5314所示,去除衬底858以暴露电介质层856。在一些实施

方式中,可以使用cmp、研磨、干法蚀刻和/或湿法蚀刻完全去除衬底858。在一些实施例中,衬底858被剥离。在衬底858包括硅的一些实施例中,电介质层856可以用作停止层,例如氮化硅,当使用硅cmp去除衬底458时,当到达具有除硅以外的材料的电介质层856时,硅cmp可以自动停止,即,充当背面cmp停止层。在一些实施例中,使用通过tmah进行的湿法蚀刻来去除衬底858(硅衬底),当到达具有除硅以外的材料的电介质层856时,湿法蚀刻自动停止,即,充当背面蚀刻停止层。电介质层856可以确保衬底858的完全去除,而无需担心减薄后的厚度均匀性。

123.如图49和图53中的操作5314所示,在一些实施方式中,在去除衬底858之后,可以进一步执行平坦化操作,例如cmp,以去除电介质层856、存储膜125的一部分和半导体沟道132的一部分。在一些实施方式中,在去除电介质层856之后,导电层806的顶表面与电介质层810、存储膜125和半导体沟道132的顶表面共面。

124.然后,如图50所示,可以去除存储膜125的部分和电介质层810以形成暴露半导体沟道132的侧表面的凹陷。在一些实施方式中,可以通过干法蚀刻、湿法蚀刻或其他合适的工艺去除存储膜125(包括氧化硅/氮氧化硅(或氮化硅)/氧化硅(ono))的部分和电介质层810。可以在半导体沟道132上执行注入操作以掺杂半导体沟道132的多晶硅材料的顶部,然后掺杂导电层808可以形成在导电层806上并形成在凹陷中。在一些实施方式中,可以在掺杂导电层808上进一步执行激活操作,例如激光激活操作。在一些实施方式中,掺杂导电层808与存储膜125和半导体沟道132直接接触。

125.如图52和图53中的操作5316所示,形成与半导体沟道132接触的互连结构。可以在掺杂导电层808上形成ild层880,然后可以在ild层880中形成源极接触开口。在源极接触开口中形成源极触点878。在一些实施方式中,形成延伸穿过ild层880并与外围触点接触的触点882。如图52所示,可以在源极接触878和接触882之上形成再分布层884。

126.通过在由沟道孔864的侧壁暴露的导电层806上形成电介质层810,沟道结构804的底部可以由电介质层810和导电层806的位置限定。沟道结构804的底部将不受沟道孔蚀刻挖槽的影响,因此沟道孔形成的工艺窗口将大大增加。

127.图54示出了根据本公开的一些方面的具有存储装置的示例性系统900的框图。系统900可以是手机、台式计算机、膝上型计算机、平板电脑、车载计算机、游戏机、打印机、定位装置、可穿戴电子装置、智能传感器、虚拟现实(vr)装置、增强现实(ar)装置、或其中具有存储的任何其他合适的电子装置。如图54所示,系统900可以包括主机908和具有一个或多个存储装置904和存储控制器906的存储器系统902。主机908可以是电子装置的处理器(例如中央处理单元(cpu))或片上系统(soc)(例如应用处理器(ap))。主机908可以被配置为向存储装置904发送数据或从存储装置904接收数据。

128.存储装置904可以是本公开中公开的任何存储装置。如上文详细公开的,诸如nand闪存装置的存储装置904在对位线放电的放电操作中可以具有受控且预定义的放电电流。根据一些实施方式,存储控制器906耦合到存储装置904和主机908并且被配置为控制存储装置904。存储控制器906可以管理存储在存储装置904中的数据并且与主机908通信。例如,存储控制器906可以耦合到存储装置904,例如如上所述的3d存储装置100、200、300、400、500、600、700或800,并且存储控制器906可以被配置为通过外围装置控制沟道结构118、404、504、604、704或804的操作。通过在由沟道孔的侧壁暴露的多晶硅层上形成电介质层,

沟道结构的底部将不会受到沟道孔蚀刻挖槽的影响,并且因此形成3d存储装置100、200、300、400、500、600、700或800的工艺窗口将大大增加。

129.在一些实施方式中,存储控制器906被设计为用于在低占空比环境中操作,例如安全数字(sd)卡、紧凑型闪存(cf)卡、通用串行总线(usb)闪存驱动器、或其他用于电子装置(例如个人计算机、数码相机、移动电话等)中的介质。在一些实施方式中,存储控制器906被设计为用于在高占空比环境ssd或者被用作移动装置(例如智能手机、平板电脑、膝上型计算机等)和企业存储阵列的数据存储设备的嵌入式多媒体卡(emmc)中运行。存储控制器906可以被配置为控制存储装置904的操作,例如读取、擦除和编程操作。存储控制器906还可以被配置为针对已存储或将要存储在存储装置904中的数据来管理各种功能,包括但不限于坏块管理、垃圾收集、逻辑到物理地址转换、损耗均衡。在一些实施方式中,存储控制器906还被配置为针对从存储装置904读取或写入到存储装置904的数据来处理错误校正码(ecc)。存储控制器906也可以执行任何其他合适的功能,例如,对存储装置904进行格式化。存储控制器906可以根据特定的通信协议与外部装置(例如,主机908)进行通信。例如,存储控制器906可以通过各种接口协议中的至少一种与外部装置通信,所述各种接口协议例如是usb协议、mmc协议、外围部件互连(pci)协议、pci-快速(pci-e)协议、高级技术附件(ata)协议、串行ata协议、并行ata协议、小型计算机小型接口(scsi)协议、增强型小型磁盘接口(esdi)协议、集成驱动电子(ide)协议、firewire协议等。

130.存储控制器906和一个或多个存储装置904可以集成到各种类型的存储装置中,例如,被包括在同一封装中,例如通用闪存存储(ufs)封装或emmc封装。即,可以实施存储系统902并将其封装到不同类型的最终电子产品中。在如图55a所示的一个示例中,存储控制器906和单个存储装置904可以集成到存储卡1002中。存储卡1002可以包括pc卡(pcmcia,个人计算机存储卡国际协会)、cf卡、智能媒体(sm)卡、存储棒、多媒体卡(mmc、rs-mmc、mmcmicro)、sd卡(sd、minisd、microsd、sdhc)、ufs等。存储卡1002还可以包括将存储卡1002与主机(例如,图18中的主机908)耦合的存储卡连接器1004。在如图55b所示的另一示例中,存储控制器906和多个存储装置904可以集成到ssd 1006中。ssd 1006还可以包括将ssd 1006与主机(例如,图18中的主机908)耦合的ssd连接器1008。在一些实施方式中,ssd 1006的存储容量和/或操作速度大于存储卡1002的存储容量和/或操作速度。

131.根据本公开的一个方面,公开了一种3d存储装置。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部处与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。存储膜包括半导体沟道之上的隧穿层、隧穿层之上的存储层和存储层之上的阻挡层。阻挡层在沟道结构的底部处的第一厚度大于阻挡层在沟道结构的上部处的第二厚度。

132.在一些实施方式中,半导体沟道包括有角结构,并且半导体沟道在有角结构下方的沟道结构的底部处的第一直径小于半导体沟道在有角结构上方的沟道结构的上部处的第二直径。

133.在一些实施方式中,3d存储装置还包括设置在堆叠结构下方的多晶硅层,并且多晶硅层与半导体沟道直接接触。在一些实施方式中,多晶硅层与半导体沟道的底表面和半导体沟道的侧表面的位于沟道结构的底部处的一部分直接接触。在一些实施方式中,半导

体沟道的底表面在堆叠结构的底表面上方。在一些实施方式中,半导体沟道的底表面在堆叠结构的底表面下方。

134.在一些实施方式中,存储膜的底表面在半导体沟道的底表面上方。在一些实施方式中,存储膜包括位于沟道结构的底部处的弯曲部分。在一些实施方式中,半导体沟道包括位于沟道结构的底部处的弯曲部分。

135.根据本公开的另一方面,公开了一种3d存储装置。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部处与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。半导体沟道包括有角结构,并且半导体沟道在有角结构下方的沟道结构的底部处的第一直径小于半导体沟道在有角结构上方的沟道结构的上部处的第二直径。

136.在一些实施方式中,3d存储装置还包括设置在堆叠结构下方的多晶硅层,并且多晶硅层与半导体沟道直接接触。在一些实施方式中,多晶硅层与半导体沟道的底表面和半导体沟道的侧表面的位于沟道结构的底部处的一部分直接接触。在一些实施方式中,半导体沟道的底表面在堆叠结构的底表面上方。在一些实施方式中,半导体沟道的底表面在堆叠结构的底表面下方。

137.在一些实施方式中,半导体沟道包括位于沟道结构的底部处的弯曲部分。

138.根据本公开的又一方面,公开了一种系统。该系统包括被配置为存储数据的3d存储装置,以及耦合到3d存储装置并被配置为控制3d存储装置的操作的存储控制器。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部处与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。存储膜包括半导体沟道之上的隧穿层、隧穿层之上的存储层和存储层之上的阻挡层。阻挡层在沟道结构的底部处的第一厚度大于阻挡层在沟道结构的上部处的第二厚度。

139.根据本公开的又一方面,公开了一种系统。该系统包括被配置为存储数据的3d存储装置,以及耦合到3d存储装置并被配置为控制3d存储装置的操作的存储控制器。3d存储装置包括具有交错的导电层和电介质层的堆叠结构,以及沿第一方向延伸穿过堆叠结构的沟道结构。沟道结构在沟道结构的底部处与3d存储装置的源极接触。沟道结构包括半导体沟道和半导体沟道之上的存储膜。半导体沟道包括有角结构,并且半导体沟道在有角结构下方的沟道结构的底部处的第一直径小于半导体沟道在有角结构上方的沟道结构的上部处的第二直径。

140.根据本公开的又一方面,公开了一种用于形成3d存储装置的方法。在衬底上形成包括第一电介质层、第一多晶硅层、第二电介质层和第二多晶硅层的第一堆叠结构。在第一堆叠结构上形成包括交替布置的多个第三电介质层和多个牺牲层的第二堆叠结构。形成沿第一方向穿透第二堆叠结构和第一堆叠结构的沟道孔。执行氧化操作以在由沟道孔的侧壁暴露的第一多晶硅层上形成第四电介质层。在沟道孔中形成沟道结构。去除衬底、第一电介质层、第一多晶硅层、第四电介质层和沟道结构的底部。在暴露的沟道结构之上形成第三多晶硅层。

141.在一些实施方式中,在沿垂直于第一方向的第二方向由沟道孔的侧壁暴露的第一多晶硅层上形成第四电介质层。在一些实施方式中,在沿第二方向由沟道孔的侧壁暴露的

第二多晶硅层上形成第五电介质层。

142.在一些实施方式中,在3d存储装置的截面图中,第一多晶硅层被沟道孔划分成第一部分和第二部分,并且形成在第一多晶硅层的第一部分上的第四电介质层与形成在第一多晶硅层的第二部分上的第四电介质层接触。

143.在一些实施方式中,在3d存储装置的截面图中,第一多晶硅层被沟道孔划分成第一部分和第二部分,并且形成在第一多晶硅层的第一部分上的第四电介质层与形成在第一多晶硅层的第二部分上的第四电介质层隔开一间隙。

144.在一些实施方式中,形成沿第一方向穿透第二堆叠结构和第一堆叠结构的栅缝隙结构。在一些实施方式中,形成沿第一方向穿透第二堆叠结构和第一堆叠结构的虚设沟道结构。

145.在一些实施方式中,在沟道孔的侧壁之上形成存储膜,并且在存储膜之上形成半导体沟道。

146.在一些实施方式中,依次去除衬底和第一电介质层以暴露第一多晶硅层和第四电介质层。去除第一多晶硅层。去除第四电介质层和存储膜的底部以暴露半导体沟道的底表面和存储膜的底表面。

147.在一些实施方式中,依次去除衬底、第一电介质层和第四电介质层以暴露半导体沟道的底表面。去除第一多晶硅层。去除存储膜的底部以暴露存储膜的底表面。

148.在一些实施方式中,存储膜的底表面在半导体沟道的底表面上方。在一些实施方式中,形成与半导体沟道的底表面和存储膜的底表面直接接触的第三多晶硅层。在一些实施方式中,将多个牺牲层替换为多个字线。

149.在一些实施方式中,第一多晶硅层包括掺杂多晶硅层。在一些实施方式中,对第一多晶硅层和第二多晶硅层执行预处理操作。在一些实施方式中,预处理操作包括对第一多晶硅层和第二多晶硅层进行nh3处理。

150.根据本公开的又一方面,公开了一种用于形成3d存储装置的方法。在衬底上形成包括第一电介质层、第一多晶硅层、第二电介质层和第二多晶硅层的第一堆叠结构。在第一堆叠结构上形成包括交替布置的多个第三电介质层和多个牺牲层的第二堆叠结构。形成沿第一方向穿透第二堆叠结构和第一堆叠结构的沟道孔。在沿垂直于第一方向的第二方向由沟道孔的侧壁暴露的第一多晶硅层上形成第四电介质层,以连接由沟道孔划分的第一多晶硅层。在第四电介质层上方的沟道孔中形成沟道结构。去除衬底、第一电介质层、第一多晶硅层、第四电介质层和沟道结构的底部。在暴露的沟道结构之上形成第三多晶硅层。

151.在一些实施方式中,对由沟道孔的侧壁暴露的第一多晶硅层执行氧化操作。

152.在一些实施方式中,在3d存储装置的截面图中,第一多晶硅层被沟道孔划分成第一部分和第二部分,并且形成在第一多晶硅层的第一部分上的第四电介质层与形成在第一多晶硅层的第二部分上的第四电介质层接触。

153.在一些实施方式中,在沿第二方向由沟道孔的侧壁暴露的第二多晶硅层上形成第五电介质层。在一些实施方式中,第五电介质层沿第二方向在沟道孔的侧壁上形成突起。

154.在一些实施方式中,在沟道孔的侧壁之上形成存储膜。在存储膜之上形成半导体沟道。存储膜的底部和半导体沟道的底部包括形成在第五电介质层上的下陷。

155.在一些实施方式中,依次去除衬底和第一电介质层以暴露第一多晶硅层和第四电

介质层。去除第一多晶硅层。去除第四电介质层和存储膜的底部以暴露半导体沟道的底表面和存储膜的底表面。

156.在一些实施方式中,依次去除衬底、第一电介质层和第四电介质层以暴露半导体沟道的底表面。去除第一多晶硅层。去除存储膜的底部以暴露存储膜的底表面。

157.在一些实施方式中,存储膜的底表面在半导体沟道的底表面上方。在一些实施方式中,第三多晶硅层形成为与半导体沟道的底表面和存储膜的底表面直接接触。

158.特定实施方式的前述描述可以容易地被修改和/或改编以用于各种应用。因此,基于本文提出的教导和指导,这样的改编和修改旨在处于所公开的实施方式的等同物的含义和范围内。

159.本公开的广度和范围不应由任何上述示例性实施方式来限制,而应仅根据所附权利要求及其等同物来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。