1.本发明涉及集成电路制造技术领域,特别涉及一种半导体器件的制造方法。

背景技术:

2.在半导体制程中,光刻胶去除(photoresist remove )、膜层刻蚀(film etch)以及清洗(clean)等多道制程中均需要进行湿法刻蚀工艺,而湿法刻蚀主要通过酸蚀来实现制程目的。

3.然而,湿法刻蚀工艺中使用的混酸(包括spm和apm,其中,spm为硫酸和过氧化氢的混合溶液,apm为氨水和过氧化氢的混合溶液)有时会对部分膜层造成损伤。例如,在图1和图2所示的低压器件(lv device)中,衬底100上形成有栅极110,所述栅极110的侧壁上形成有侧墙120,且所述侧墙120为氧化层121和氮化硅层122堆叠而成的叠层结构。在对所述低压器件进行离子注入工艺之前,多道湿法刻蚀工艺中所使用的混酸会损伤所述氮化硅层122,破环侧墙结构,从而影响离子注入工艺的效果,并最终导致所述低压器件在晶圆测试(wafer test,wat)中出现电性漂移(shift)。

4.为了解决上述问题,现有技术通常会对湿法刻蚀的混酸中spm和apm的含量及配比进行调整,或通过控制湿法刻蚀的时间来减少氮化硅层的损伤,以减少低压器件的电性变化。然而,调整混酸的含量及配比的难度较大,且多道湿法刻蚀的叠加效应依旧会导致氮化硅层的损伤;控制湿法刻蚀的酸洗时间时,时间过短无法达到湿法刻蚀的预期效果,时间过长仍然会造成氮化硅层的损伤,进而对低压器件的电性产生影响。

5.鉴于此,需要一种方法减少或避免多次湿法刻蚀对半导体器件中的部分膜层造成损伤,从而确保半导体器件的电性稳定。

技术实现要素:

6.本发明的目的在于提供一种半导体器件的制造方法,通过形成覆盖氮化硅层的保护层,减少或避免了湿法刻蚀对氮化硅层造成损伤,从而确保半导体器件的电性稳定。

7.为了解决上述技术问题,本发明提供一种半导体器件的制造方法,包括:提供衬底,所述衬底上形成有栅极,所述栅极的侧壁上依次形成有第一氧化层和氮化硅层;在所述氮化硅层的表面形成保护层;进行离子注入工艺,以在所述栅极两侧的衬底内分别形成第一离子注入区和第二离子注入区;以及,在所述保护层的表面形成第二氧化层,所述第一氧化层、所述氮化硅层、所述保护层和所述第二氧化层构成所述栅极的侧墙。

8.可选的,形成所述第一离子注入区和所述第二离子注入区的过程包括:在所述衬底和所述栅极的表面形成图案化的第一光刻胶层,所述图案化的第一光刻胶层至少暴露所述栅极一侧的部分衬底;

以所述图案化的第一光刻胶层和所述氮化硅层为掩模进行第一次离子注入工艺,以形成所述第一离子注入区;去除所述图案化的第一光刻胶层,在所述衬底和所述栅极的表面形成图案化的第二光刻胶层,所述图案化的第二光刻胶层至少暴露所述栅极的异于所述第一离子注入区一侧的部分衬底;以所述图案化的第二光刻胶层和所述氮化硅层为掩模进行第二次离子注入工艺,以形成所述第二离子注入区;以及,去除所述图案化的第二光刻胶层。

9.可选的,采用湿法刻蚀工艺分别去除所述图案化的第一光刻胶层和所述图案化的第二光刻胶层,所述保护层在所述湿法刻蚀工艺中保护所述氮化硅层不受损伤。

10.可选的,所述湿法刻蚀工艺的刻蚀剂包括硫酸和过氧化氢的混合溶液,以及氨水和过氧化氢的混合溶液。

11.可选的,所述保护层为氧化层。

12.可选的,所述保护层的形成过程包括第一阶段、第二阶段、第三阶段和第四阶段,其中:所述第一阶段的工艺温度为200℃~350℃,腔室压力为200mt~680mt,工艺气体包括氧气,且氧气流量为1000sccm~1400sccm,工艺时间为40s~80s;所述第二阶段的工艺温度为200℃~350℃,腔室压力为2000mt~4600mt,工艺气体包括氧气、氢气和氮气,且氧气流量为5000sccm~7000sccm,氢气和氮气的流量均为1500sccm~2500sccm,工艺时间为40s~80s;所述第三阶段的工艺温度为200℃~350℃,腔室压力为2000mt~4600mt,工艺气体包括氧气、氢气和氮气,且氧气流量为5000sccm~7000sccm,氢气和氮气的流量均为1500sccm~2500sccm,工艺时间为50s~90s;所述第四阶段的工艺温度为200℃~350℃,腔室压力为500mt~2800mt,工艺气体包括氧气、氢气和氮气,且氧气流量为80sccm~150sccm,氢气和氮气的流量均为1500sccm~2500sccm,工艺时间为20s~40s。

13.可选的,所述第二氧化层的厚度大于所述保护层的厚度。

14.可选的,所述保护层的厚度范围为10

ꢀåꢀ

~30

å

。

15.可选的,所述保护层的材料与所述第二氧化层的材料相同。

16.可选的,所述第一氧化层和第二氧化层的材料均包括氧化硅。

17.综上所述,本发明提供一种半导体器件的制造方法,包括:提供衬底,所述衬底上形成有栅极,所述栅极的侧壁上依次形成有第一氧化层和氮化硅层;在所述氮化硅层的表面形成保护层;进行离子注入工艺,以在所述栅极两侧的衬底内分别形成第一离子注入区和第二离子注入区;以及,在所述保护层的表面形成第二氧化层,所述第一氧化层、所述氮化硅层、所述保护层和所述第二氧化层构成所述栅极的侧墙。本发明通过形成覆盖氮化硅层的保护层,减少或避免了多次湿法刻蚀对氮化硅层造成的损伤,从而确保半导体器件的电性稳定,提高了晶圆利用率。

附图说明

18.本领域的普通技术人员应当理解,提供的附图用于更好地理解本发明,而不对本发明的范围构成任何限定。

19.图1和图2为一低压器件的制造方法中部分步骤对应的结构示意图。

20.图3为一低压器件的制造方法中部分步骤对应结构的电性变化情况。

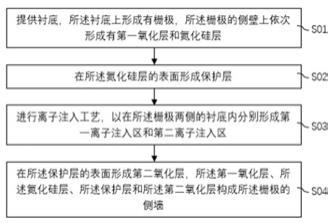

21.图4为本发明一实施例提供的半导体器件的制造方法的流程图。

22.图5-图8为本发明一实施例提供的半导体器件的制造方法中各个步骤对应的结构示意图。

23.图9为本发明一实施例提供的半导体器件的制造方法中各个步骤对应结构的电性变化情况。

24.其中,附图标记如下:100-衬底;110-栅极;120-侧墙;121-氧化层;122-氮化硅层;123-第二氧化层;200-衬底;210-栅极;220-侧墙;221-第一氧化层;222-氮化硅层;223-保护层;224-第二氧化层。

具体实施方式

25.为使本发明的目的、优点和特征更加清楚,以下结合附图和具体实施例对本发明作进一步详细说明。需说明的是,附图均采用非常简化的形式且未按比例绘制,仅用以方便、明晰地辅助说明本发明实施例的目的。此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。

26.如在本发明中所使用的,单数形式“一”、“一个”以及“该”包括复数对象,术语“或”通常是以包括“和/或”的含义而进行使用的,术语“若干”通常是以包括“至少一个”的含义而进行使用的,术语“至少两个”通常是以包括“两个或两个以上”的含义而进行使用的,此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”、“第三”的特征可以明示或者隐含地包括一个或者至少两个该特征,“一端”与“另一端”以及“近端”与“远端”通常是指相对应的两部分,其不仅包括端点,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。此外,如在本发明中所使用的,一元件设置于另一元件,通常仅表示两元件之间存在连接、耦合、配合或传动关系,且两元件之间可以是直接的或通过中间元件间接的连接、耦合、配合或传动,而不能理解为指示或暗示两元件之间的空间位置关系,即一元件可以在另一元件的内部、外部、上方、下方或一侧等任意方位,除非内容另外明确指出外。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

27.图1和图2为一低压器件的制造方法中部分步骤对应的结构示意图。所述低压器件的制造方法包括:首先,参阅图1,提供衬底100,所述衬底100的表面形成有栅极结110,在所述栅极110的侧壁依次形成第一氧化层121以及氮化硅层122。可选的,所述第一氧化层121的材料包括氧化硅,所述氮化硅层122的材料包括氮化硅。

28.随后,进行离子注入工艺,在所述栅极结构两侧的衬底100内分别形成第一离子注入区(图中未示出)和第二离子注入区(图中未示出)。具体的,形成第一离子注入区和第二离子注入区的过程包括:在所述衬底100和所述栅极110的表面形成图案化的第一光刻胶层(图中未示出),所述图案化的第一光刻胶层至少暴露所述栅极110一侧的部分衬底100;以所述图案化的第一光刻胶层和所述氮化硅层122为掩模进行第一次离子注入工艺,以形成所述第一离子注入区;去除所述图案化的第一光刻胶层,在所述衬底100和所述栅极110的表面形成图案化的第二光刻胶层(图中未示出),所述图案化的第二光刻胶层至少暴露所述栅极110的异于所述第一离子注入区一侧的部分衬底100;以所述图案化的第二光刻胶层和所述氮化硅层122为掩模进行第二次离子注入工艺,以形成所述第二离子注入区;以及,去除所述图案化的第二光刻胶层。可选的,采用湿法刻蚀工艺分别去除所述图案化的第一光刻胶层和所述图案化的第二光刻胶层。

29.接着,参阅图2,在所述氮化硅层122的表面形成第二氧化层123,所述第一氧化层121、所述氮化硅层122和所述第二氧化层123构成所述栅极110的侧墙120。即,所述栅极110的侧墙120为ono叠层结构(氧化硅层、氮化硅层和氧化硅层堆叠而成的叠层结构)。

30.此外,在形成所述氮化硅层122之后,进行所述离子注入工艺之前,所述低压器件的制造方法还包括形成其他半导体结构的工艺步骤,例如,光刻胶去除工艺(photoresist remove)、膜层刻蚀工艺(film etch)、清洗工艺(clean)等,上述工艺均需要进行湿法刻蚀。然而,湿法刻蚀工艺所采用的刻蚀剂通常包括spm和apm(spm为硫酸和过氧化氢的混合溶液,apm为氨水和过氧化氢的混合溶液),所述刻蚀剂会损伤所述氮化硅层122,破坏所述栅极100的侧墙120,从而影响所述离子注入工艺的工艺效果。图3为所述低压器件的制造方法中部分步骤对应结构的电性变化情况,参阅图3,随着工艺步骤的进行,湿法刻蚀次数的增加,所述低压器件的测试电压逐渐增大,可见,多次湿法刻蚀工艺破坏了所述栅极100的侧墙120,并导致所述低压器件出现电性漂移(shift)。

31.为了解决上述问题,现有技术通常会对所述刻蚀剂中spm和apm的含量及配比进行调整,或通过控制湿法刻蚀的时间来减少氮化硅层的损伤,以减少所述低压器件的电性漂移。然而,调整所述刻蚀剂中spm和apm的含量及配比的难度较大,且多道湿法刻蚀的叠加效应依旧会导致氮化硅层的损伤;控制湿法刻蚀的酸洗时间时,时间过短无法达到湿法刻蚀的预期效果,时间过长仍然会造成氮化硅层的损伤,进而对低压器件的电性产生影响。

32.鉴于此,本发明提供一种半导体器件的制造方法,减少或避免多次湿法刻蚀对半导体器件中的部分膜层造成损伤,从而确保半导体器件的电性稳定。图4为本发明一实施例提供的半导体器件的制造方法的流程图。参阅图4,本实施例所述的半导体器件的制造方法包括:步骤s01:提供衬底,所述衬底上形成有栅极,所述栅极的侧壁上依次形成有第一氧化层和氮化硅层;步骤s02:在所述氮化硅层的表面形成保护层;步骤s03:进行离子注入工艺,以在所述栅极两侧的衬底内分别形成第一离子注入区和第二离子注入区;以及,步骤s04:在所述保护层的表面形成第二氧化层,所述第一氧化层、所述氮化硅层、所述保护层和所述第二氧化层构成所述栅极的侧墙。

33.图5-图8为本发明一实施例提供的半导体器件的制造方法中各个步骤对应的结构示意图,下面结合图5-图8详细说明本实施例所述的半导体器件的制造方法。

34.首先,参阅图5,执行步骤s01,提供衬底200,所述衬底200上形成有栅极210,所述栅极210的侧壁上依次形成有第一氧化层221和氮化硅层222。本实施例中,所述衬底200为硅衬底,所述栅极210的材料为多晶硅,所述第一氧化层221的材料为氧化硅,在本发明的其他实施例中,所述衬底200的材料还可以是锗硅衬底、

ⅲ‑ⅴ

族元素化合物衬底、碳化硅衬底或其叠层结构,或绝缘体上硅结构,也可以是金刚石衬底或本领域技术人员公知的其他半导体材料衬底,所述第一氧化层221的材料也可以根据实际需要进行调整,本发明对此不作限制。

35.接着,参阅图6,执行步骤s02,在所述氮化硅层222的表面形成保护层223。本实施例中,所述保护层223为氧化层,且所述保护层223的厚度范围为10

ꢀåꢀ

~30

å

。具体的,所述保护层的形成过程包括第一阶段、第二阶段、第三阶段和第四阶段,其中:所述第一阶段的工艺温度为200℃~350℃,腔室压力为200mt~680mt,工艺气体包括氧气,且氧气流量为1000sccm~1400sccm,工艺时间为40s~80s;所述第二阶段的工艺温度为200℃~350℃,腔室压力为2000mt~4600mt,工艺气体包括氧气、氢气和氮气,且氧气流量为5000sccm~7000sccm,氢气和氮气的流量均为1500sccm~2500sccm,工艺时间为40s~80s,以形成稳定的反应环境;所述第三阶段的工艺温度为200℃~350℃,腔室压力为2000mt~4600mt,工艺气体包括氧气、氢气和氮气,且氧气流量为5000sccm~7000sccm,氢气和氮气的流量均为1500sccm~2500sccm,工艺时间为50s~90s,以形成所述保护层223;所述第四阶段的工艺温度为200℃~350℃,腔室压力为500mt~2800mt,工艺气体包括氧气、氢气和氮气,且氧气流量为80sccm~150sccm,氢气和氮气的流量均为1500sccm~2500sccm,工艺时间为20s~40s,以便停止反应。

36.需要说明的是,在本发明的其他实施例中,所述保护层223的形成过程及工艺参数可以根据实际需要进行调整,本发明对此不作限制。

37.随后,参阅图7,执行步骤s03,进行离子注入工艺,以在所述栅极210两侧的衬底200内分别形成第一离子注入区(图中未示出)和第二离子注入区(图中未示出)。

38.示例性的,形成所述第一离子注入区和所述第二离子注入区的过程包括:在所述衬底200和所述栅极210的表面形成图案化的第一光刻胶层(图中未示出),所述图案化的第一光刻胶层至少暴露所述栅极210一侧的部分衬底200;以所述图案化的第一光刻胶层和所述氮化硅层222为掩模进行第一次离子注入工艺,以形成所述第一离子注入区;去除所述图案化的第一光刻胶层,在所述衬底200和所述栅极210的表面形成图案化的第二光刻胶层(图中未示出),所述图案化的第二光刻胶层至少暴露所述栅极210的异于所述第一离子注入区一侧的部分衬底200;以所述图案化的第二光刻胶层和所述氮化硅层222为掩模进行第二次离子注入工艺,以形成所述第二离子注入区;以及,去除所述图案化的第二光刻胶层。

39.本实施例中,采用湿法刻蚀工艺分别去除所述图案化的第一光刻胶层和所述图案化的第二光刻胶层。可选的,所述湿法刻蚀工艺的刻蚀剂包括硫酸和过氧化氢的混合溶液(spm),以及氨水和过氧化氢的混合溶液(apm)。由于所述保护层223为氧化层,不会与所述刻蚀剂发生反应,因此,所述保护层223可以在所述湿法刻蚀工艺中保护所述氮化硅层222

不受损伤。

40.需要说明的是,在形成所述保护层223之后,进行所述离子注入工艺之前,所述半导体器件还包括清洗工艺(clean)、膜层刻蚀工艺(film etch)、光刻胶层的去除工艺(photoresist remove)等其他需要采用湿法刻蚀的工艺步骤,例如,若所述图案化的第一光刻胶层(或所述图案化的第二光刻胶层)发生偏移需要重做时,需要通过湿法刻蚀工艺去除所述图案化的第一光刻胶层,本实施例中所述保护层223可以在多次湿法刻蚀工艺中保护所述氮化硅层222始终不受损伤,确保后续离子注入工艺的正常进行。

41.接着,参阅图8,执行步骤s04,在所述保护层223的表面形成第二氧化层224,所述第一氧化层221、所述氮化硅层222、所述保护层223和所述第二氧化层224构成所述栅极210的侧墙220。本实施例中,所述第二氧化层224的厚度大于所述保护层223的厚度,所述保护层223的材料与所述第二氧化层224的材料相同,均包括氧化硅。因此,所述侧墙220为所述第一氧化层221、所述氮化硅层222、所述保护层223和所述第二氧化层224构成的onoo叠层结构。

42.图9为本实施例提供的半导体器件的制造方法中各个步骤对应结构的电性变化情况。参阅图9,随着工艺步骤的正常进行,湿法刻蚀的次数增加,所述半导体器件的测试电压并无明显的变化。对比图3和图9可见,本实施例所述的半导体器件的制造方法减少或避免了湿法刻蚀对氮化硅层造成损伤,从而确保半导体器件的电性稳定。本实施例中,所述半导体器件包括低压器件(lv device),且所述半导体器件的器件尺寸小于110nm,在本发明的其他实施例中,所述半导体器件的种类及尺寸可以根据实际需要进行调整,本发明对此不作限制。

43.综上所述,本发明提供一种半导体器件的制造方法,包括:提供衬底,所述衬底上形成有栅极,所述栅极的侧壁上依次形成有第一氧化层和氮化硅层;在所述氮化硅层的表面形成保护层;进行离子注入工艺,以在所述栅极两侧的衬底内分别形成第一离子注入区和第二离子注入区;以及,在所述保护层的表面形成第二氧化层,所述第一氧化层、所述氮化硅层、所述保护层和所述第二氧化层构成所述栅极的侧墙。本发明通过形成覆盖氮化硅层的保护层,减少或避免了多次湿法刻蚀对氮化硅层造成的损伤,从而确保半导体器件的电性稳定,提高了晶圆利用率。

44.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。