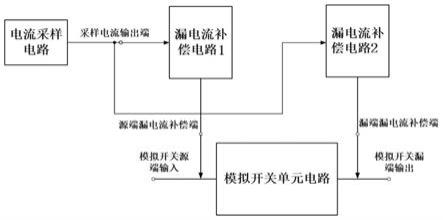

fvf结构开环型参考电压驱动电路

技术领域

1.本发明涉及参考电压驱动电路。

背景技术:

2.逐次逼近模拟-数字转换器(sar-adc)具有结构简单、功耗低、面积小和易于集成等特点,广泛应用于中等精度(8~16位)中等速度(《150msps)领域。

3.常规sar-adc的时钟控制都是同步方式,即外部接入一个时钟,而片内的采样、转换、存储、输出的每一个步骤都由外部时钟定义。外部时钟的精度要与sar-adc 的采样精度匹配。除了需要保证时钟源的纯净,还要对时钟到芯片内部各个环节的噪声都非常小心。此外,高速的时钟频率需要片内的逻辑门有很强的驱动能力,这意味着很大的功耗。对于高速 sar-adc 来说,做到 100ms/s 以上的速度,10 位以上的精度,采用同步控制是非常的不经济,难度也非常大。

4.异步时钟控制是近年来 sar-adc 提速的最重要的系统级解决方案。sar-adc 自身有一些特点,比如采样对时钟精度要求高,但转换对时钟精度几乎没有要求,刚好给异步时钟提供了发挥优势的空间。控制电路需要的脉冲自己产生,异步时钟控制放弃了同步时钟的分频操作,而是采用跟采样频率一样的外部时钟,把时钟分割成采样和转换两阶段。转换时系统对操作时钟边沿没有要求,把转换做成异步触发,用比较器触发 sar 逻辑,sar 逻辑带动数字-模拟转换阵列(dac array)的方式完成n次比较。最后 n 个依次完成但未对齐时钟的数据通过同步方式输出结果。

5.异步sar-adc的基本结构如图2所示,外部时钟信号经过时钟发生电路产生采样时钟clk

sample

。采样时钟对输入差分信号inp、 inn进行采样后,由高速比较器比较,并通过异或产生ready信号输入到多相位时钟发生器和逐次逼近逻辑组成的高速数字电路,一方面产生一个时钟信号通过延迟链给比较器提供比较时钟,另一方面经过dac控制电路对sar-adc的开关电容阵列进行控制。

6.dac的参考电压由外部带隙基准源(bg)经过参考电压驱动器(vref buf)产生。由于带隙基准源的驱动能力往往很弱,无法直接驱动dac的参考电压,异步sar-adc内部时钟远远高于同步sar-adc的工作频率,为了减小dac参考电压的稳定时间(settling time),需要一个具有很强驱动能力的参考电压驱动器。fvf结构(flipped voltage follower,翻转电压跟随器)是一种常用的驱动方式,由于它的输出级工作在局部闭环模式(主极点在极高频),它具有很低的输出阻抗,具有很强的驱动能力。

7.传统的异步逐次逼近模拟-数字转换器(sar-adc)所用的fvf(flipped voltage follower,翻转电压跟随器)参考电压驱动器结构如图3所示,vin是参考电压的输入,来源于带隙基准源(bgr),因此vin随工艺、电源电压、温度的变化幅度很小。由运放opa和mos管m13组成的参考电压闭环通路使mos管m13源极电压输出能够稳定的跟随vin,电容c1是环路稳定补偿电容。mos管m13、m14组成翻转电压跟随器结构,可以使mos管m13源极输出阻抗很小。mos管m15、m16是m13、m14相同结构的fvf复制电路,因此vref_out作为整个驱动器的输

出与vin保持一致。

8.mos管m17与mos管m18、m19组成镜像电流源,mos管m17的偏置i2来自于外部恒定的电流源, mos管m19的尺寸是mos管m18的n倍大小,mos管m16、m15的尺寸也是mos管m14、m13尺寸的n倍大小,n≥1。由于fvf结构的输出阻抗足够低,带宽足够大,所以能够对驱动sar-adc电容数字-模拟转换阵列(cdac)参考电压的高速切换带来极大的好处。但是当此电路运用于深亚微米工艺的集成电路,电源电压变低(小于1.2v),而输出的参考电压需要接近电源电压的时候(例如0.9v),mos管m14、m16会工作在接近亚阈值区域,mos管m14、m16的vgs(栅源电压)不会很大,从而mos管m13、m15的状态会逼近线性区,造成传统的fvf架构驱动器很难工作在低电源电压、高输出参考电压的应用环境,输出驱动电压的电源抑制比也较差。

技术实现要素:

9.本发明的目的在于提供fvf结构开环型参考电压驱动电路,能够在低电源电压供电的工作情况下,提供具有很强驱动能力的参考电压,有利于逐次逼近模拟-数字转换器中电容数字-模拟转换阵列(cdac)参考电压的高速切换,使cdac参考电压的稳定时间(settling time)得到极大的节省,提高异步逐次逼近模拟-数字转换器的工作速度。

10.实现上述目的的技术方案是:一种fvf结构开环型参考电压驱动电路,包括:第一运算放大器、第一pmos(p型场效应管)管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管、第一恒定电流源、第二恒定电流源、第一nmos(n型场效应管)管、第二nmos管、第三nmos管、第四nmos管、第五nmos管、第六nmos管、第一电阻和第一电容,其中,所述第一运算放大器的反相输入端外接参考电压输入,同相输入端连接第三pmos管的漏极;所述第一pmos管的源极外接电源,栅极连接所述第一运算放大器的输出端,漏极连接所述第二pmos管的源极;所述第二pmos管的栅极和漏极相接,栅极通过串接的第一电阻和第一电容接地,漏极连接所述第四nmos管的漏极;所述第三nmos管、第四nmos管、第五nmos管和第六nmos管各自的源极接地,各自的栅极相接;所述第三nmos管的栅极连接漏极,漏极接收偏置电流;所述第一电阻和第一电容的相接端连接所述第四pmos管和第六pmos管各自的栅极;所述第三pmos管的源极连接电源,栅极连接所述第一nmos管的漏极,漏极连接所述第四pmos管的源极;所述第四pmos管漏极连接所述第五nmos管的漏极;所述第一nmos管的漏极通过所述第一恒定电流源连接电源,源极连接所述第五nmos管的漏极;所述第五pmos管的源极连接电源,栅极连接所述第二nmos管的漏极,漏极连接所述第六pmos管的源极并作为输出端;所述第二nmos管通过第二恒定电流源连接电源,源极连接所述第六nmos管的漏

极;所述第六pmos管的漏极连接所述第六nmos管的漏极;所述第一nmos管和第二nmos管各自的栅极外接直流电压偏置vb1。

11.优选的,还包括:第一补偿电容、第二补偿电容和第三补偿电容,其中,所述第一补偿电容的一端外接电源,另一端连接所述第一运算放大器的输出端;所述第二补偿电容两端连接所述第三pmos管的源极和栅极;所述第三补偿电容两端连接所述第五pmos管的源极和栅极。

12.优选的,所述第一运算放大器包括:第七pmos管、第八pmos管、第九pmos管、第十pmos管、第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第七nmos管、第八nmos管、第九nmos管和第十nmos管,其中,所述第七pmos管、第九pmos管和第十pmos管各自的源极接电源;所述第七pmos管的栅极接电流镜直流偏置vb4,漏极接所述第八pmos管的源极;所述第八pmos管的栅极接电流镜直流偏置vb5,漏极连接所述第十三pmos管和第十四pmos管各自的源极;所述第十三pmos管和第十四pmos管各自的栅极接参考电压输入;所述第九pmos管和第十pmos管各自的栅极连接所述第十一pmos管的漏极;所述第十一pmos管的源极连接所述第九pmos管的漏极,栅极接电流镜直流偏置vb5;所述第十二pmos管的源极连接所述第十pmos管的漏极,栅极接电流镜直流偏置vb5;所述第七nmos管和第八nmos管各自的栅极接vb3;所述第七nmos管的漏极接所述第十一pmos管的漏极,源极连接所述第十四pmos管的漏极和所述第九nmos管的漏极;所述第八nmos管的漏极连接所述第十二pmos管的漏极并作为输出端,源极连接所述第十三pmos管的漏极和第十nmos管的漏极;所述第九nmos管和第十nmos管各自的栅极接直流偏置vb2,各自的源极接地。

13.本发明的一种fvf结构开环型参考电压驱动电路,包括:第二运算放大器、第十五pmos管、第十六pmos管、第十七pmos管、第十八pmos管、第十九pmos管、第二十pmos管、第三恒定电流源、第四恒定电流源、第十一nmos管、第十二nmos管、第十三nmos管、第十四nmos管、第十五nmos管、第十六nmos管、第二电阻和第二电容,其中,所述第二运算放大器的反相输入端外接参考电压输入,同相输入端连接第十五nmos管的漏极;所述第十四nmos管的源极接地,栅极连接所述第二运算放大器的输出端,漏极连接所述第十一nmos管的源极;所述第十一nmos管的栅极和漏极相接,栅极通过串接的第二电阻和第二电容接地,漏极连接所述第十六pmos管的漏极;所述第十五pmos管、第十六pmos管、第十七pmos管、第十八pmos管各自的源极接电源,各自的栅极相接;所述第十五pmos管的栅极连接漏极,漏极接收偏置电流;

所述第二电阻和第二电容的相接端连接所述第十二nmos管和第十三nmos管各自的栅极;所述第十五nmos管的源极接地,栅极连接所述第十九pmos管的漏极,漏极连接所述第十二nmos管的源极;所述第十二nmos管漏极连接所述第十七pmos管的漏极;所述第十九pmos管的漏极通过所述第三恒定电流源连接接地,源极连接所述第十七pmos管的漏极;所述第十六nmos管的源极连接地,栅极连接所述第二十pmos管的漏极,漏极连接所述第十三nmos管的源极并作为输出端;所述第二十pmos管通过第四恒定电流源连接地,源极连接所述第十八pmos管的漏极;所述第十三nmos管的漏极连接所述第十八pmos管的漏极;所述第十九pmos管和第十三nmos管各自的栅极外接直流电压偏置vb1。

14.本发明的有益效果是:本发明与传统的参考电压驱动电路相比较,本专利采用经过改进的fvf(flipped voltage follower,翻转电压跟随器)结构,本发明能够在低电源供电的工作情况下,提供具有很强驱动能力的参考电压,有利于逐次逼近模拟-数字转换器中电容数字-模拟转换阵列(cdac)参考电压的高速翻转,使cdac参考电压的稳定时间(settling time)得到极大的节省。本发明能够提高sar-adc的工作速度,改善adc的线性度和信号-失真噪声比(sndr),提高深亚微米cmos工艺异步逐次逼近模拟-数字转换器(sar-adc)集成电路大规模量产的良率。

附图说明

15.图1是本发明的一种fvf结构开环型参考电压驱动电路的电路图;图2是异步sar-adc的基本结构;图3是传统的fvf结构开环型参考电压驱动电路的电路图;图4是本发明中带频率补偿的改进型fvf结构开环型参考电压驱动电路的电路图;图5是本发明中第一运算放大器的折叠式运放电路图;图6是本发明的n型mos管驱动的fvf结构开环型参考电压驱动电路的电路图。

具体实施方式

16.下面将结合附图对本发明作进一步说明。

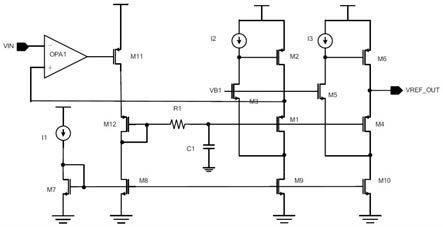

17.请参阅图1、4、5、6,本发明的fvf结构开环型参考电压驱动电路,包括:第一运算放大器opa1、第一pmos管m11、第二pmos管m12、第三pmos管m2、第四pmos管m1、第五pmos管m6、第六pmos管m4、第一恒定电流源i2、第二恒定电流源i3、第一nmos管m3、第二nmos管m5、第三nmos管m7、第四nmos管m8、第五nmos管m9、第六nmos管m10、第一电阻r1和第一电容c1。图1为p型mos管驱动的fvf结构开环型参考电压驱动电路。

18.其中,第一运算放大器opa1的反相输入端外接参考电压输入,同相输入端连接第三pmos管m2的漏极。第一pmos管m11的源极外接电源,栅极连接第一运算放大器opa1的输出端,漏极连接第二pmos管m12的源极。第二pmos管m12的栅极和漏极相接,栅极通过串接的第

一电阻r1和第一电容c1接地,漏极连接第四nmos管m8的漏极。第三nmos管m7、第四nmos管m8、第五nmos管m9和第六nmos管m10各自的源极接地,各自的栅极相接。第三nmos管m7的栅极连接漏极,漏极接收偏置电流。第一电阻r1和第一电容c1的相接端连接第四pmos管m1和第六pmos管m4各自的栅极。第三pmos管m2的源极连接电源,栅极连接第一nmos管m3的漏极,漏极连接第四pmos管m1的源极。第四pmos管m1漏极连接第五nmos管m9的漏极。第一nmos管m3的漏极通过第一恒定电流源i2连接电源,源极连接第五nmos管m9的漏极。第五pmos管m6的源极连接电源,栅极连接第二nmos管m5的漏极,漏极连接第六pmos管m4的源极并作为输出端。第二nmos管m5通过第二恒定电流源i3连接电源,源极连接第六nmos管m10的漏极。第六pmos管m4的漏极连接第六nmos管m10的漏极。第一nmos管m3和第二nmos管m5各自的栅极外接直流电压偏置vb1。

19.在第三pmos管m2的栅极和第四pmos管m1的漏极之间插入了一个第一nmos管m3做cascode(级联)隔离,这样第四pmos管m1的工作状况将不受第三pmos管m2的vgs和较高的参考电压输出值的限制,避免第四pmos管m1在低电压的情况下工作在接近线性区,因此使用这种结构能够在较低的工作的电压下,提供较高的参考电压驱动输出。第一恒定电流源i2为第一nmos管m3提供电流偏置,直流电压偏置vb1将第一nmos管m3偏置在合适的工作区。第五pmos管m6、第二nmos管m5、第六pmos管m4、第二恒定电流源i3、第六nmos管m10是第三pmos管m2、第一nmos管m3、第四pmos管m1、第一恒定电流源i2、第五nmos管m9的开环复制结构,它能够提供参考驱动电压vref_out,摆脱了第一运算放大器opa1与第一pmos管m11、第二pmos管m12、第四pmos管m1组成的低频跟踪环路对输出带宽的影响。输出驱动级工作在局部闭环模式(主极点在极高频),具有很低的输出阻抗,具有很强的驱动能力。第六nmos管m10与第五nmos管m9成倍数关系,当第六nmos管m10是第五nmos管m9的n倍尺寸时候,第五pmos管m6、第二nmos管m5、第六pmos管m4、第二恒定电流源i3也是第三pmos管m2、第一nmos管m3、第四pmos管m1、第一恒定电流源i2的n倍尺寸,n≥1,从而输出级能提供n倍的参考电压驱动能力。fvf结构中第六pmos管m4、第二nmos管m5、第五pmos管m6构成一个共栅极输入的折叠级联cascode运算放大器,迫使第六pmos管m4的栅极电压跟随输出参考驱动电压vref_out变化,这个运放环路具有很高的带宽(高频主极点),从而对sar-adc的cdac高速变化具有很大的驱动能力。偏置电流i1和二极管连接的电流源m7向m9、m10提供镜像电流,同时也向m8提供固定偏置。输入电压vin(即参考电压输入)经过第一运算放大器opa1、第一pmos管m11组成的电压-电流转换结构转换成电流,再通过pmos管接成的二极管连接提供第四pmos管m1、第六pmos管m4的电压。第四pmos管m1的源级通过第一运算放大器opa1、第一pmos管m11、第二pmos管m12、第四pmos管m1构成的低频环路跟随vin的变化。当第二pmos管m12与第四pmos管m1、第六pmos管m4尺寸成比例的话,第二pmos管m12的源级电压与vin的电压相同,第四pmos管m1、第六pmos管m4的源级电压也与它相同。第一电阻r1和第一电容c1组成一个低通滤波器滤除来自vin的噪声。

20.图4是带频率补偿的fvf结构开环型参考电压驱动电路,在图1所示的电路加上相关的频率补偿机制,改进环路的稳定性,提高了相位裕度。c2是闭环低频环路的补偿电容。c3和c4分别是m1、m2、m3和m4、m5、m6组成的fvf电路的补偿电容,增强高频稳定性。具体地,第一补偿电容c2的一端外接电源,另一端连接第一运算放大器opa1的输出端;第二补偿电容c3两端连接第三pmos管m2的源极和栅极;第三补偿电容c4两端连接第五pmos管m6的源极

和栅极。

21.图5是p管输入的折叠式运放电路,电流镜直流偏置vb4、电流镜直流偏置vb5在pm5、pm3上提供主电流源,同时电流镜直流偏置vb5也为m27、m28提供偏置电压。m20、m21是opa1的输入对管,一般取较大的尺寸,使其工作在亚阈值区,具有较大的跨导和很小的噪声。直流偏置vb2偏置m22、m23管,其流过电流是主电流源和pmos电流镜m29、m30之和。vout是运放输出电压端口,它的输出阻抗很高。具体地,第一运算放大器opa1包括:第七pmos管pm5、第八pmos管pm3、第九pmos管m29、第十pmos管m30、第十一pmos管m27、第十二pmos管m28、第十三pmos管m20、第十四pmos管m21、第七nmos管m24、第八nmos管m25、第九nmos管m22和第十nmos管m23。

22.第七pmos管pm5、第九pmos管m29和第十pmos管m30各自的源极接电源;第七pmos管pm5的栅极接电流镜直流偏置vb4,漏极接第八pmos管pm3的源极;第八pmos管pm3的栅极接电流镜直流偏置vb5,漏极连接第十三pmos管m20和第十四pmos管m21各自的源极;第十三pmos管m20和第十四pmos管m21各自的栅极接参考电压输入;第九pmos管m29和第十pmos管m30各自的栅极连接第十一pmos管m27的漏极;第十一pmos管m27的源极连接第九pmos管m29的漏极,栅极接电流镜直流偏置vb5;第十二pmos管m28的源极连接第十pmos管m30的漏极,栅极接电流镜直流偏置vb5;第七nmos管m24和第八nmos管m25各自的栅极接vb3;第七nmos管m24的漏极接第十一pmos管m27的漏极,源极连接第十四pmos管m21的漏极和第九nmos管m22的漏极;第八nmos管m25的漏极连接第十二pmos管m28的漏极并作为输出端,源极连接第十三pmos管m20的漏极和第十nmos管m23的漏极;第九nmos管m22和第十nmos管m23各自的栅极接直流偏置vb2,各自的源极接地。

23.图6是n型mos管驱动的fvf结构开环型参考电压驱动电路,它是由图1所示的电路转变而来。区别在于低频输入参考电压vin跟踪环路修改为主要由nmos管构成。同时,fvf开环输出驱动电路也改由nmos管构成,它的特点在于可以提供一个接近地的输出参考电压驱动后级cdac的切换。

24.具体地,fvf结构开环型参考电压驱动电路,包括:第二运算放大器opa2、第十五pmos管m40、第十六pmos管m41、第十七pmos管m42、第十八pmos管m43、第十九pmos管m36、第二十pmos管m39、第三恒定电流源i5、第四恒定电流源i6、第十一nmos管m44、第十二nmos管m34、第十三nmos管m37、第十四nmos管m45、第十五nmos管m35、第十六nmos管m38、第二电阻r3和第二电容c3。

25.第二运算放大器opa2的反相输入端外接参考电压输入,同相输入端连接第十五nmos管m35的漏极;第十四nmos管m45的源极接地,栅极连接第二运算放大器opa2的输出端,漏极连接第十一nmos管m44的源极;第十一nmos管m44的栅极和漏极相接,栅极通过串接的第二电阻r3和第二电容c3接地,漏极连接第十六pmos管m41的漏极;第十五pmos管m40、第十六pmos管m41、第十七pmos管m42、第十八pmos管m43各自的源极接电源,各自的栅极相接;第十五pmos管m40的栅极连接漏极,漏极接收偏置电流i4;第二电阻r3和第二电容c3的相接端连接第十二nmos管m34和第十三nmos管m37各自的栅极;第十五nmos管m35的源极接地,栅极连接第十九pmos管m36的漏极,漏极连接第十二nmos管m34的源极;第十二nmos管m34漏极连接第十七pmos管m42的漏极;第十九pmos管m36的漏极通过第三恒定电流源i5连接接地,源极连接第十七pmos管m42的漏极;第十六nmos管m38的源极连接地,栅极连接第二十pmos管

m39的漏极,漏极连接第十三nmos管m37的源极并作为输出端;第二十pmos管m39通过第四恒定电流源i6连接地,源极连接第十八pmos管m43的漏极;第十三nmos管m37的漏极连接第十八pmos管m43的漏极;第十九pmos管m36和第十三nmos管m37各自的栅极外接直流电压偏置vb1。

26.综上,本发明能够在低电源电压供电的工作情况下,提供具有很强驱动能力的参考电压,提高异步逐次逼近模拟-数字转换器的工作速度。

27.以上实施例仅供说明本发明之用,而非对本发明的限制,有关技术领域的技术人员,在不脱离本发明的精神和范围的情况下,还可以作出各种变换或变型,因此所有等同的技术方案也应该属于本发明的范畴,应由各权利要求所限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。