1.本发明属于半导体集成电路领域,进一步来说涉及半导体模拟集成电路领域,具体来说,涉及一种带超低漏电流补偿技术的模拟开关。

背景技术:

2.现有技术中的开关电路常采用互补开关电路:cmos[complementary metal oxide semiconductor:互补金属氧化物半导体]互补模拟开关,电路结构如图1所示,该结构由两部分构成,一个互补开关pmos晶体管p1和一个互补nmos晶体管n1。互补模拟开关中,p1、n1管的栅极控制信号5和6电位通常是互补反相信号,且栅极控制信号5和6电位的高低还决定了模拟开关的开启和关断。

[0003]

该电路单元电位接法如图1所示,即,pmos晶体管衬底4为n阱,一般情况下,该电位接到最高电位vdd上,nmos晶体管衬底3为psub,其电位始终接到最低电位vss。在实际电路设计中,晶体管p1和晶体管n1的尺寸与其本身的漏电大小是不同的,虽然p1和n1管衬底到源漏端所产生的pn结漏电流极性相反,但不能完全抵消,模拟开关漏电流会影响信号输出端的信号保持精度,输出信号应用于信号采样电路时,过大的漏电流会使得输出信号的精度极大降低,从而影响采样电路的采样精度,因此如何解决互补模拟开关的漏电流这一问题亟待解决。

[0004]

有鉴于此,特提出本发明。

技术实现要素:

[0005]

本发明的目的是:解决现有cmos互补模拟开关漏电流过大,造成输出信号精度极大降低,影响采样电路采样精度的问题。

[0006]

本发明的发明构思是:采用漏电流补偿电路,实现超低漏电流的模拟开关,提高输出信号保持精度。

[0007]

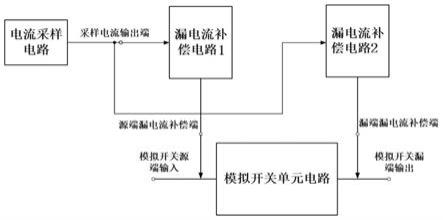

为此,本发明提供一种带超低漏电流补偿技术的模拟开关,原理框图示意图如图2所示。

[0008]

包括:模拟开关单元电路、电流采样单元电路、漏电流补偿单元电路1、漏电流补偿单元电路2。

[0009]

其中,漏电流补偿单元电路1的漏电流补偿端与模拟开关单元电路的输入端连接,漏电流补偿单元电路2的漏电流补偿端与模拟开关单元电路的输出端连接,电流采样单元电路的采样电流输出端连接到漏电流补偿单元电路1的输入端和漏电流补偿单元电路2的输入端。

[0010]

所述电流采样单元电路用于采样模拟开关单元电路产生的漏电流,所述漏电流补偿电路用于按比例漏电流采样电路的电流值并补偿模拟开关单元电路产生的漏电流。

[0011]

如图1所示,所述模拟开关单元电路为cmos互补模拟开关,由互补开关pmos晶体管p1、互补开关noms晶体管n1组成。所述互补开关pmos晶体管p1的源极和互补开关nmos管n1

的源极相连接,且作为模拟开关的模拟输入端1,所述互补开关pmos晶体管p1的漏极与所述互补开关nmos管n1的漏极相连接,且作为模拟开关的模拟输出端2,所述互补开关pmos晶体管p1的栅极连接时钟控制信号ck1,所述互补开关nmos管n1的栅极连接时钟控制信号ck2,所述互补开关pmos晶体管p1的衬底接高电平vdd,所述互补开关开关nmos晶体管n1的衬底接低电平vss,图中电流i

ps1

为晶体管p1衬底到源端的pn结漏电流,图中电流i

ns1

为晶体管n1源端到衬底的pn结漏电流,图中电流i

pd1

为晶体管p1衬底到漏端的pn结漏电流,图中电流i

nd1

为晶体管n1漏端到衬底的pn结漏电流;

[0012]

如图3所示,所述电流采样单元电路用于采样互补开关pmos晶体管p1和互补开关noms晶体管n1产生的漏电流。包含电流采样pmos晶体管p2和电流采样nmos晶体管n2,所述电流采样pmos晶体管p2的源极、漏极和栅极相连接,所述电流采样nmos管n2的源极、漏极和栅极相连接,所述电流采样pmos晶体管p2的源极、漏极和栅极所述电流采样nmos管n2的源极、漏极和栅极相连接,所述电流采样pmos晶体管p2的衬底接高电位vdd,所述电流采样nmos晶体管n2的衬底接低电位vss,图中电流i

p2

为晶体管p2衬底到源、漏端的pn结漏电流之和,图中电流i

n2

为晶体管n2源、漏端到衬底的pn结漏电流,p2、n2晶体管所采样的pn结漏电流之和ic(ic=i

p2

i

n2

)作为采样电流输出到采样电流输出端;

[0013]

如图4所示,所述漏电流补偿电路包含源端漏电流补偿单元电路1和漏端漏电流补偿单元电路2,所述漏电流补偿单元电路1、漏电流补偿单元电路2分别用于按比例漏电流采样电路的电流值并补偿互补开关pmos晶体管p1和互补开关noms晶体管n1衬底到源漏端产生的pn结漏电流。

[0014]

所述的漏电流补偿单元电路1,包含pmos晶体管p3和pmos晶体管p4,所述pmos晶体管p3和pmos晶体管p4的源极和衬底接高电位,所述pmos晶体管p3的漏极和栅极相接,所述pmos晶体管p4的栅极与所述pmos晶体管p3的栅极相接,所述pmos晶体管p4的漏极与所述互补开关nmos管n1的源极相连接;

[0015]

如图5所示,所述的漏电流补偿单元电路2包含pmos晶体管p3和pmos晶体管p5,所述pmos晶体管p3和pmos晶体管p5的源极和衬底接高电位,所述pmos晶体管p3的漏极和栅极相接,所述pmos晶体管p5的栅极与所述pmos晶体管p3的栅极相接,所述pmos晶体管p5的漏极与所述互补开关nmos管n1的源极相连接;

[0016]

所述漏电流补偿电路1中所述pmos晶体管p4的漏极与所述采样pmos晶体管p2的栅极相接,所述漏电流补偿电路2中所述pmos晶体管p5的漏极与所述采样pmos晶体管p2的栅极相接。

[0017]

本发明的有益效果在于:与传统互补cmos模拟开关相比,本发明提供了一种带开关漏电流补偿技术的优化方法,通过采用电流采样和漏电流补偿电路,极大地降低了模拟开关的漏电流,提高了模拟信号传输信号的保持能力,并且避免了漏电流过大造成采样电路采样输出信号出现精度过低的问题。广泛应用于高精度开关电路技术领域。

附图说明

[0018]

图1是现有模拟开关单元电路结构示意图。

[0019]

图2是本发明模拟开关原理框图示意图。

[0020]

图3是本发明模拟开关电流采样单元电路结构示意图。

[0021]

图4是本发明模拟开关漏电流补偿单元电路结构示意图。

[0022]

图5是本发明模拟开关电路结构示意图。

具体实施方式

[0023]

结合图1-图5,对本发明的具体实施例详细如下:

[0024]

如图1所示,该模拟开关采用pmos和nmos晶体管互补开关结构,包含互补开关pmos晶体管p1和互补开关nmos晶体管n1,p1的源端和n1的源端相连接且作为模拟开关的模拟输入端1,p1的漏端和n1的漏端相连接且作为模拟开关的模拟输出端2,p1的栅端接时钟控制信号ck1,n1的栅端接时钟控制信号ck2,ck1和ck2互为反相时钟信号,用于控制模拟开关的开启和关断,p1的衬底接最高电位vdd,n1的衬底接最低电位vss,保证开关电路在整个动态传输范围内p1、n1源衬不会正向导通,保证动态信号的全范围传输。采用互补cmos模拟开关的优势在于,通过调节p1和n1晶体管的尺寸,能够在模拟动态传输范围内保持一个相对平稳的低导通电阻,图中电流i

ps1

为晶体管p1衬底到源端的pn结漏电流,图中电流i

ns1

为晶体管n1源端到衬底的pn结漏电流,图中电流i

pd1

为晶体管p1衬底到漏端的pn结漏电流,图中电流i

nd1

为晶体管n1漏端到衬底的pn结漏电流。

[0025]

如图2所示,本发明原理基于将电流采样电路所采样的衬底与源漏端间的pn结漏电流输出到漏电流补偿电路,按采样电流与模拟开关电路开关管衬底与源漏端间pn结漏电流的比例进行电流补偿,从而达到零漏电流补偿提高输出信号保持精度的设计目的。

[0026]

如图3所示,该电流采样电路由电流采样pmos晶体管p2和电流采样nmos晶体管n2构成,p2晶体管的栅极、源极与漏极相连接,并与n2晶体管的栅极、源极与漏极连接,图中电流i

p2

为晶体管p2衬底到源、漏端的pn结漏电流之和,图中电流i

n2

为晶体管n2源、漏端到衬底的pn结漏电流,p2、n2晶体管所采样的pn结漏电流之和ic(ic=i

p2

i

n2

)作为采样电流输出到采样电流输出端。。

[0027]

如图4所示,该电路由镜像pmos晶体管p3和补偿pmos晶体管p4构成,晶体管p3的栅极和漏极相接,并且与晶体管p4的栅极相连,采样电流ic经晶体管p3和晶体管p4按比例镜像为βic到漏电流补偿端以达到漏电流补偿的目的。

[0028]

镜像放大倍数β计算方式如下:

[0029][0030]

通过电流比例得到放大倍数β,从而可以得到漏电流补偿电路中p3和p4的晶体管尺寸比例,具体比例关系如下(式2中w为mos晶体管的沟道宽度,l为mos晶体管沟道长度):

[0031][0032]

如图5所示,该电路由图3和图4所述电流采样单元电路和漏电流补偿单元电路与图1所述互补cmos模拟开关单元电路构成。采样电流晶体管p2的衬底接到最高电位vdd,采样电流晶体管n2的衬底接到最低电位vss,晶体管p3、p4和p5的衬底和源端均接到最高电位vdd,晶体管p2和电流采样nmos晶体管n2构成,p2晶体管的栅极、源极与漏极相连接,并与n2

晶体管的栅极、源极与漏极连接,p2、n2晶体管所采样的电流作为采样电流输出到采样电流输出端,即晶体管p3的漏极,p3的漏极和栅极相连接,且与p4、p5的栅极相接,通过p4、p5和p3晶体管的宽长比比例,将采样电流按比例镜像到p4、p5的漏端分别作为模拟开关的源端漏电流补偿和漏端漏电流补偿。该电路中,p1、p2、p3、p4、p5使用相同类型的pmos晶体管,n1与n2采用相同nmos晶体管。

[0033]

通过采样电流单元电路采集p2、n2的衬底到源漏端的pn结漏电流之和与p1、n1衬底与源漏端间的pn结漏电流之和进行比较,得出比值β,然后通过漏电流补偿电路按同样比例补偿到模拟开关的源端和漏端,实现模拟开关的漏电流补偿,进而实现模拟开关的超低漏电。

[0034]

最后说明的是,以上实施案例仅用于说明本发明的技术方案而非限制,尽管该实施案例已经对本发明进行了详细地描述,但本领域的技术人员应当理解,可以在结构上和细节上作出不同的改变,而不偏离本发明权利要求书所限定的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。